# 國立臺灣師範大學科技與工程學院電機工程學系 碩士論文

Department of Electrical Engineering

College of Technology and Engineering

National Taiwan Normal University

Master's Thesis

應用於高速電路之靜電放電防護設計 ESD Protection Design of High-Speed Circuit

> 戴子鈞 Zih-Jyun Dai

指導教授:林群祐 博士

Advisor: Chun-Yu Lin, Ph.D.

中華民國 110 年 10 月 October 2021

## Acknowledgement

能完成這篇論文,我要感謝我的媽媽,不辭辛勞將我拉拔長大,在大學研究所階段供我生活、求學,也很支持我做的每個決定,讓我更沒有畏懼。也感謝家人們的陪伴與關心,讓我感受到親情的溫暖。

感謝我的研究所指導教授林群祐老師,不管是在專業問題上的討論,還是 論文編撰時的嚴謹,都讓我受益良多,很感謝老師在我碩士班時對我的指導。

感謝義全、日彦、冠綸、智永、范姜、震浩、柏永等眾多兄弟們,在研究 所這段日子有你們情義相挺一起走過無數的困難。

感謝實驗室的學長姐國倫、柏維、玉瑄、鈺凱,給我許多專業上的教學討 論與經驗分享,讓我的碩士班研究工作更順利進行。也謝謝實驗室的學弟妹 們,幫忙處理許多實驗室的雜務,讓實驗室營運的更好。

感謝雅璇,在我研究所時期不離不棄的陪伴,陪我度過寫論文最黑暗的時期,與我分享生活大小事,充當我精神上的支柱。

謝謝國家晶片中心所提供的晶片下線與量測服務;也謝謝國立陽明交通大學電子工程學系借用實驗室及量測儀器,也謝謝榮堃學長每次預約量測時幫忙開門及協助排解量測遇到的問題;謝謝口試委員國立陽明交通大學電子工程學系的柯明道教授及國立台灣科技大學電子工程學系的張勝良教授,針對我的碩士論文提供許多意見與建議,讓我的碩士論文內容更加完整。

戴子鈞 謹誌於師大 中華民國一一零年十月

## 應用於高速電路之靜電放電防護設計

學生: 戴子鈞 指導教授: 林群祐 博士

#### 國立臺灣師範大學電機工程學系碩士班

## 摘 要

本論文旨在研究應用於高速積體電路之全晶片靜電放電防護設計,在 CMOS 製程下實作,以低電容元件搭配分散式電路的設計,並與既有二極體及電晶體元件的設計相比較。

隨著內部電路的操作頻率不斷提升,寄生電容造成的訊號損耗嚴重影響電路高頻性能,本篇論文利用兩級分散式電路架構的方式,將單級的防護元件以小尺寸分散至兩級來設計防護電路,以降低每級的元件寄生電容,並在兩級之間以匹配元件降低訊號通過時的損耗,形成π型架構的設計。傳統的π型架構設計使用的是二極體或電晶體元件,本論文提出利用其他低電容矽控整流器元件如堆疊二極體內嵌矽控整流器 (SDSCR) 及電阻觸發式矽控整流器 (RTSCR) 搭配π型架構,組成π-SDSCR 與π-RTSCR,來與π型連接的傳統元件進行比較。由實驗結果可知,在 20GHz 時,創新設計π-SDSCR 在單位插入損耗 (S<sub>21</sub>) 下所達到的二次崩潰電流 (I<sub>12</sub>) 為傳統設計的 1.76 倍,π-RTSCR 則為傳統設計的 1.62 倍,相較於傳統架構,本文提出的設計具備更高的 ESD 防護能力及更低的寄生電容,更適用於高速電路。

最後,為了驗證與比較防護電路的性能,本論文也設計了一應用於高速的轉 阻放大器 (Trans-impedance amplifier, TIA),分別搭配傳統π型二極體設計與本論 文所提出的防護電路,並進行電路的量測,驗證實際的防護效果及對電路性能的影響。由實驗結果可知,創新設計與傳統設計都能為 TIA 電路提供 4kV 的 HBM ESD 耐受度,且 $\pi$ -SDSCR 在 17GHz 時的插入損耗僅傳統設計的 0.83 倍, $\pi$ -RTSCR 則為傳統設計的 0.9 倍,顯示創新設計在提供足夠 ESD 耐受度的同時,對電路高頻性能影響更低。

關鍵字:全晶片靜電放電防護、π型架構、轉阻放大器

ESD Protection Design of High-Speed Circuit

Student: Zih-Jyun Dai

Advisor: Chun-Yu Lin, Ph.D.

Department of Electrical Engineering

National Taiwan Normal University

**ABSTRACT**

This thesis is to study a whole-chip electrostatic discharge (ESD) protection design

for high-speed circuits. In CMOS process, the low-capacitance device is designed with

distributed circuit in comparison with traditional design by diode and MOS.

As the operating frequency of the internal circuit increases, the signal loss caused by

parasitic capacitance seriously affects the high-frequency performance of the circuit. A

two-stage distributed circuit architecture is used in this thesis to divide a single-stage

protection device into two stages in a small size which can reduce the parasitic capacitance

of the device in each stage. The matching element is added between two stages and formed

$\pi$ -structure to reduce the signal loss. Diode or MOS is used in traditional  $\pi$ -model design.

This thesis proposes to use other innovative low-capacitance silicon-controlled rectifier

(SCR) such as stacked diodes with embedded silicon-controlled rectifier (SDSCR) and

resistor-triggered SCR (RTSCR) with the  $\pi$ -model to compare with the  $\pi$ -connected

traditional devices. From the experiment result, the secondary breakdown current (I<sub>t2</sub>)

provided by proposed  $\pi$ -SDSCR per unit insertion loss (S<sub>21</sub>) at 20GHz is 1.76 times

higher than that of the traditional design. That value provided by proposed  $\pi$ -RTSCR is

1.62 times higher than that of the traditional design. As compare with traditional structure,

iv

proposed designs have higher ESD protection ability and lower parasitic capacitance

which are more suitable for high-speed circuits.

In order to verify and compare the performance of the protection circuits, this thesis

designed a high-speed trans-impedance amplifier (TIA), which has added the traditional

$\pi$ -diode and the proposed  $\pi$ -SCR in this paper as ESD protection. The circuits were

measured to verify the protection ability and the influence on the circuit performance.

From the experiment result, both traditional and proposed designs provide 4kV HBM

ESD robustness for the TIA circuit. However, the degradation of insertion loss ( $\Delta S_{21}$ ) of

TIA with  $\pi$ -SDSCR at 17GHz is only 0.83 times of that of TIA with traditional design.

The value of TIA with  $\pi$ -RTSCR is 0.9 times of that of TIA with traditional design. It

shows that as compare with traditional structure, proposed designs have lower impact on

the high frequency performance of the circuit, while also providing sufficient ESD

tolerance.

Keyword: whole-chip ESD protection,  $\pi$ -structure, TIA

## **Contents**

| Acknow    | ledgement                                                     | i    |

|-----------|---------------------------------------------------------------|------|

| Abstrac   | t (Chinese)                                                   | ii   |

| Abstrac   | t (English)                                                   | iv   |

| Content   | S                                                             | vi   |

| List of T | Tables                                                        | viii |

| List of F | Figures                                                       | ix   |

| Chapter   | 1 Introduction                                                | 1    |

| 1.1       | Motivation                                                    | 1    |

| 1.2       | Background of ESD.                                            | 2    |

| 1.3       | ESD Test Standards                                            | 2    |

| 1.4       | Design Concepts of ESD Protection                             | 5    |

| 1.5       | Organization of This Thesis                                   | 7    |

| Chapter   | 2 Studies of ESD Protection Designs for High-Speed Applicatio | ns8  |

| 2.1       | Consideration of ESD Protection Design at High-Speed circuits | 8    |

| 2.2       | ESD Protection Designs for High-Speed Application             | 11   |

|           | 2.2.1 Capacitive ESD Protection Circuit                       | 11   |

|           | 2.2.2 Distributed ESD Protection Circuit (DESD)               | 14   |

| Chapter   | 2 Design of π-Model SCR (π-SCR)                               | 16   |

| 3.1       | Design Concepts of Distributed Circuit                        | 16   |

| 3.2       | Traditional $\pi$ -Model Diode ( $\pi$ -Diode)                | 18   |

| 3.3       | Traditional π-Model MOS (π-MOS)                               | 22   |

| 3.4       | Proposed π-Model SCR (π-SCR)                                  | 26   |

|           | 3.4.1 $\pi$ -Model SDSCR ( $\pi$ -SDSCR)                      | 29   |

|           | 3.4.2 $\pi$ -Model RTSCR ( $\pi$ -RTSCR)                      | 33   |

| 3 5       | Simulation Results                                            | 37   |

|      | 3.6   | Meas   | urement Results                       | 41 |

|------|-------|--------|---------------------------------------|----|

|      |       | 3.6.1  | High-Frequency Performance            | 42 |

|      |       | 3.6.2  | TLP I-V Curves                        | 45 |

|      |       | 3.6.3  | HBM Test                              | 58 |

|      |       | 3.6.4  | Very Fast TLP Test                    | 60 |

|      | 3.7   | Comp   | parison                               | 61 |

|      | 3.8   | Sumn   | nary                                  | 66 |

| Cha  | pter  | 4 Re   | alization of Proposed Design with TIA | 67 |

|      | 4.1   | Introd | duction                               | 67 |

|      | 4.2   | Struct | ture of TIA                           | 67 |

|      | 4.3   | Simul  | lation Results of TIA                 | 68 |

|      |       | 4.3.1  | TIA w/o Protection                    | 68 |

|      |       | 4.3.2  | TIA with Traditional π-Diode          | 70 |

|      |       | 4.3.3  | TIA with Proposed π-SDSCR             | 71 |

|      |       | 4.3.4  | TIA with Proposed $\pi$ -RTSCR        | 73 |

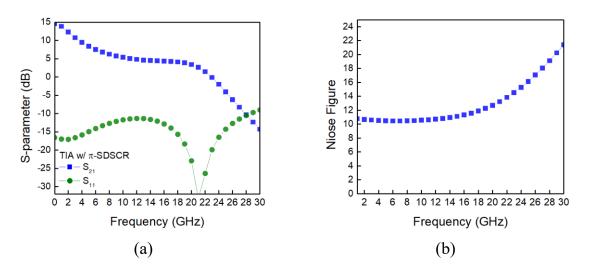

|      | 4.4   | Meas   | urement Results of TIA                | 74 |

|      |       | 4.4.1  | High-frequency Performance            | 75 |

|      |       | 4.4.2  | TLP I-V Curves                        | 78 |

|      |       | 4.4.3  | HBM Test                              | 79 |

|      |       | 4.4.4  | Very Fast TLP Test                    | 84 |

|      | 4.5   | Comp   | parison and Discussion                | 85 |

|      | 4.6   | Sumn   | nary                                  | 90 |

| Cha  | pter  | 5 Co   | onclusion and Future Work             | 91 |

|      | 5.1   | Conc   | lusion                                | 91 |

|      | 5.2   | Futur  | e Work                                | 92 |

| Refe | erenc | e      |                                       | 95 |

## **List of Tables**

| Table 1.1.  | The target level of HBM                                         | 3  |

|-------------|-----------------------------------------------------------------|----|

| Table 1.2.  | The target level of CDM                                         | 4  |

| Table 3.1.  | The test cell of $\pi$ -diode                                   | 20 |

| Table 3.2.  | The test cell of $\pi$ -MOS                                     | 24 |

| Table 3.3.  | The test cell of $\pi$ -SDSCR                                   | 32 |

| Table 3.4.  | The test cell of $\pi$ -RTSCR                                   | 36 |

| Table 3.5.  | Simulated S-parameter at 20GHz                                  | 40 |

| Table 3.6.  | Measured S-parameter at 20GHz                                   | 45 |

| Table 3.7.  | Measured I <sub>t2</sub> results                                | 56 |

| Table 3.8.  | Measured $I_{t2}/ S_{21} $ results                              | 57 |

| Table 3.9.  | HBM test results                                                | 59 |

| Table 3.10. | VF-TLP test results                                             | 60 |

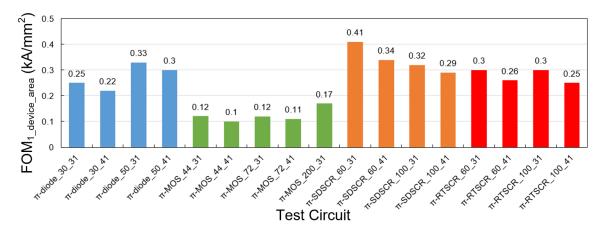

| Table 3.11. | Comparison table of FOM <sub>1_device_area</sub>                | 52 |

| Table 3.12. | Comparison table of FOM <sub>2_device_S21</sub>                 | 64 |

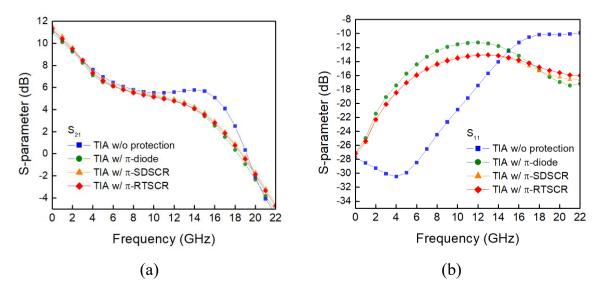

| Table 4.1.  | Measured S-parameter at 17GHz                                   | 77 |

| Table 4.2.  | Measured $V_{Clamp\_TLP}$ of each test circuit under four modes | 79 |

| Table 4.3.  | VF-TLP test results                                             | 84 |

| Table 4.4.  | Comparison of high-frequency applications                       | 85 |

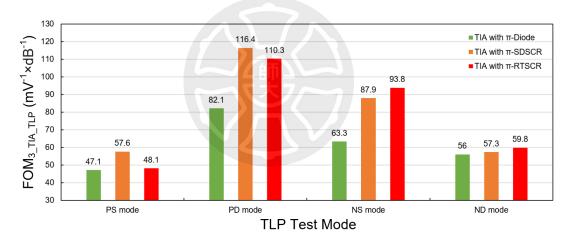

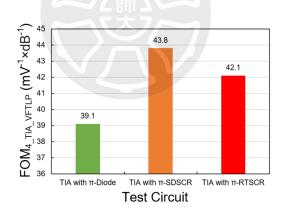

| Table 4.5.  | Comparison table of FOM <sub>3_TIA_TLP</sub>                    | 87 |

| Table 4.6.  | Comparison table of FOM <sub>4_TIA_VFTLP</sub>                  | 88 |

| Table 4.7.  | Comparison with circuits in literature                          | 89 |

## **List of Figures**

| Fig. 1.1.  | The equivalent circuit of HBM.                                        |

|------------|-----------------------------------------------------------------------|

| Fig. 1.2.  | The equivalent circuit of CDM.                                        |

| Fig. 1.3.  | Whole-chip ESD protection design.                                     |

| Fig. 1.4.  | ESD design window.                                                    |

| Fig. 1.5.  | Whole-chip ESD protection design with corresponding path              |

| Fig. 2.1.  | Signal loss at high frequencies.                                      |

| Fig. 2.2.  | The I-V curve of diode.                                               |

| Fig. 2.3.  | The I-V curve of NMOS.                                                |

| Fig. 2.4.  | The I-V curve of SCR10                                                |

| Fig. 2.5.  | ESD protection design of dual diodes [19].                            |

| Fig. 2.6.  | ESD protection design of dual SDSCR [20]                              |

| Fig. 2.7.  | ESD protection design of dual SDSCR [21]                              |

| Fig. 2.8.  | ESD protection design of two-section distributed circuit [22]1        |

| Fig. 2.9.  | ESD protection design of multi-section distributed circuit [22]1      |

| Fig. 3.1.  | High-frequency equivalent circuit of $\pi$ -model circuit             |

| Fig. 3.2.  | (a) $S_{21}$ (b) $S_{11}$ simulation results of $\pi$ -structure      |

| Fig. 3.3.  | Cross-sectional view of symmetrical (a) P-type and (b) N-type diode18 |

| Fig. 3.4.  | Layout top view of symmetrical (a) P-type and (b) N-type diode19      |

| Fig. 3.5.  | Whole-chip ESD protection circuit with traditional $\pi$ -diode       |

| Fig. 3.6.  | Layout top view of (a) $\pi$ -diode_30_31 (b) $\pi$ -diode_30_412     |

| Fig. 3.7.  | Layout top view of (a) $\pi$ -diode_50_31 (b) $\pi$ -diode_50_412     |

| Fig. 3.8.  | Cross-sectional view of (a) GDPMOS and (b) GGNMOS22                   |

| Fig. 3.9.  | Layout top view of (a) GDPMOS and (b) GGNMOS22                        |

| Fig. 3.10. | Whole-chip ESD protection circuit with traditional $\pi$ -MOS         |

| Fig. 3.11. | Layout top view of $\pi$ -MOS_200_31                                       | 25         |

|------------|----------------------------------------------------------------------------|------------|

| Fig. 3.12. | Layout top view of (a) $\pi$ -MOS_44_31 (b) $\pi$ -MOS_44_41               | 25         |

| Fig. 3.13. | Layout top view of (a) $\pi$ -MOS_72_31 (b) $\pi$ -MOS_72_41               | 25         |

| Fig. 3.14. | (a) Equivalent circuit and (b) cross-sectional view of SCR                 | 26         |

| Fig. 3.15. | Equivalent circuit of (a) stacked diode with embedded SCR (SDSCF           | <b>R</b> ) |

|            | (b) resistor-triggered SCR (RTSCR)                                         | 27         |

| Fig. 3.16. | Equivalent circuit of proposed (a) $\pi$ -SDSCR and (b) $\pi$ -RTSCR       | 28         |

| Fig. 3.17. | The top view of matching inductor                                          | 28         |

| Fig. 3.18. | The structure of matching inductor.                                        | 29         |

| Fig. 3.19. | Cross-sectional view of (a) P-type SDSCR and (b) N-type SDSCR              | 30         |

| Fig. 3.20. | Layout top view of symmetrical (a) P-type and (b) N-type SDSCR             | 30         |

| Fig. 3.21. | Whole-chip ESD protection circuit with proposed $\pi$ -SDSCR               | 31         |

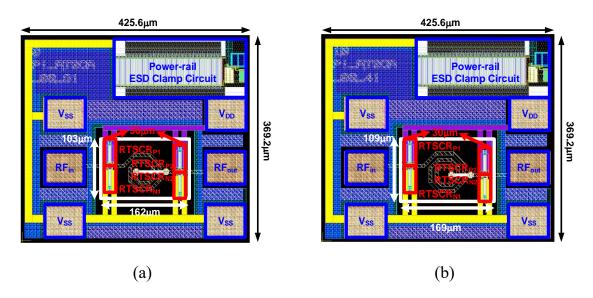

| Fig. 3.22. | Layout top view of (a) $\pi$ -SDSCR_60_31 (b) $\pi$ -SDSCR_60_41           | 32         |

| Fig. 3.23. | Layout top view of (a) $\pi$ -SDSCR_100_31 (b) $\pi$ -SDSCR_100_41         | 33         |

| Fig. 3.24. | Cross-sectional view of (a) P-type RTSCR and (b) N-type RTSCR              | 34         |

| Fig. 3.25. | Layout top view of symmetrical (a) P-type and (b) N-type RTSCR             | 34         |

| Fig. 3.26. | Whole-chip ESD protection circuit with proposed $\pi$ -RTSCR               | 35         |

| Fig. 3.27. | Layout top view of (a) $\pi$ -STSCR_60_31 (b) $\pi$ -RTSCR_60_41           | 36         |

| Fig. 3.28. | Layout top view of (a) $\pi$ -RTSCR_100_31 (b) $\pi$ -RTSCR_100_41         | 37         |

| Fig. 3.29. | The simulated S-parameter of $\pi$ -diode_30_31, $\pi$ -MOS_44_31, $\pi$ - |            |

|            | SDSCR_60_31 and π-RTSCR_60_31                                              | 38         |

| Fig. 3.30. | The simulated S-parameter of $\pi$ -diode_30_41, $\pi$ -MOS_44_41, $\pi$ - |            |

|            | SDSCR_60_41 and π-RTSCR_60_41                                              | 39         |

| Fig. 3.31. | The simulated S-parameter of $\pi$ -diode_50_31, $\pi$ -MOS_72_31, $\pi$ - |            |

|            | MOS_200_31, π-SDSCR_100_31 and π-RTSCR_100_31                              | 39         |

| Fig. 3.32. | The simulated S-parameter of $\pi$ -diode_50_41, $\pi$ -MOS_72_41, $\pi$ - |            |

|            | SDSCR_100_41 and π-RTSCR_100_41                                           | .39 |

|------------|---------------------------------------------------------------------------|-----|

| Fig. 3.33. | The chip photograph of test device                                        | .41 |

| Fig. 3.34. | The setup of high-frequency measurement system [27]                       | .42 |

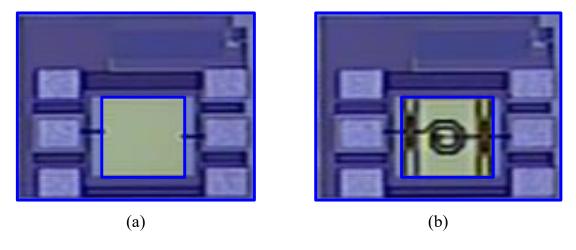

| Fig. 3.35. | The photograph of (a) de-embedding pad and (b) test device                | .42 |

|            |                                                                           |     |

| Fig. 3.36. | The measured S-parameter of $\pi$ -diode_30_31, $\pi$ -MOS_44_31, $\pi$ - |     |

|            | SDSCR_60_31 and π-RTSCR_60_31                                             | .43 |

| Fig. 3.37. | The measured S-parameter of $\pi$ -diode_30_41, $\pi$ -MOS_44_41, $\pi$ - |     |

|            | SDSCR_60_41 and π-RTSCR_60_41                                             | .43 |

| Fig. 3.38. | The measured S-parameter of $\pi$ -diode_50_31, $\pi$ -MOS_72_31, $\pi$ - |     |

|            | MOS_200_31, π-SDSCR_100_31 and π-RTSCR_100_31                             | .44 |

| Fig. 3.39. | The measured S-parameter of $\pi$ -diode_50_41, $\pi$ -MOS_72_41, $\pi$ - |     |

|            | SDSCR_100_41 and π-RTSCR_100_41                                           | .44 |

| Fig. 3.40. | Transmission-line pulsing (TLP) system [30]                               | .46 |

| Fig. 3.41. | TLP I-V curves of power-rail ESD clamp circuit                            | .47 |

| Fig. 3.42. | TLP I-V curves of test devices under PD mode                              | .48 |

| Fig. 3.43. | TLP I-V curves of test devices under PD mode after normalized by          |     |

|            | insertion loss at 20GHz                                                   | .49 |

| Fig. 3.44. | TLP I-V curves of test devices under PS mode                              | .50 |

| Fig. 3.45. | TLP I-V curves of test devices under PS mode after normalized by          |     |

|            | insertion loss at 20GHz                                                   | .51 |

| Fig. 3.46. | TLP I-V curves of test devices under ND mode                              | .52 |

| Fig. 3.47. | TLP I-V curves of test devices under ND mode after normalized by          |     |

|            | insertion loss at 20GHz                                                   | .53 |

| Fig. 3.48. | TLP I-V curves of test devices under NS mode                              | .54 |

| Fig. 3.49. | TLP I-V curves of test devices under NS mode after normalized by          |     |

|            | insertion loss at 20GHz55                                                  |

|------------|----------------------------------------------------------------------------|

| Fig. 3.50. | HBM tester [30]58                                                          |

| Fig. 3.51. | (a) VF-TLP I-V curves of test devices under PD mode. (b) VF-TLP I-         |

|            | V curves of test devices under PD mode after normalized by                 |

|            | insertion loss at 20GHz60                                                  |

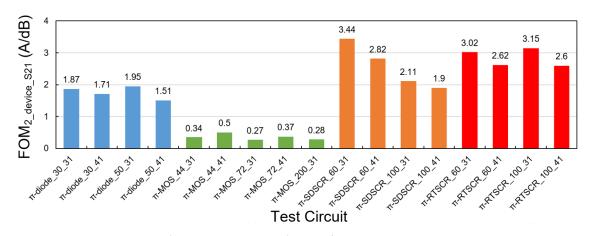

| Fig. 3.52. | Comparison of FOM <sub>1_device_area</sub> 63                              |

| Fig. 3.53. | Comparison of FOM <sub>2_device_S21</sub> 65                               |

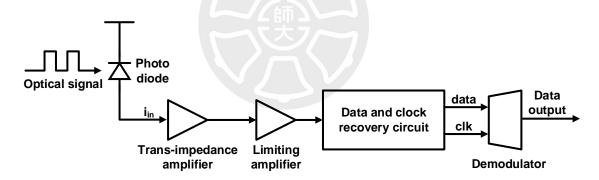

| Fig. 4.1.  | The architecture of optical receiver system67                              |

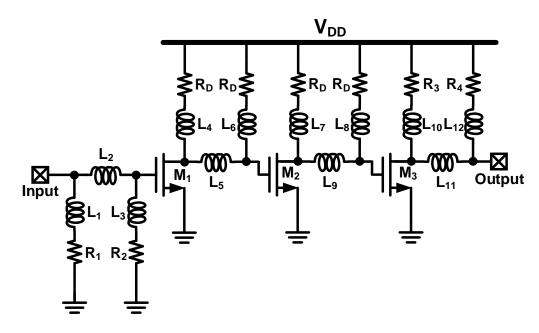

| Fig. 4.2.  | The architecture of TIA circuit                                            |

| Fig. 4.3.  | The architecture of TIA w/o protection69                                   |

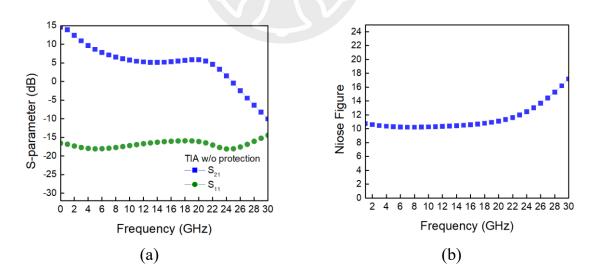

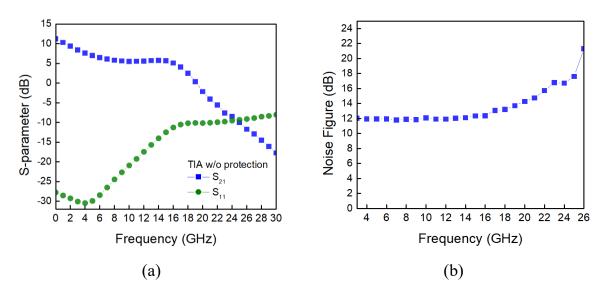

| Fig. 4.4.  | Simulated (a) S-parameter and (b) noise figure of TIA w/o protection.69    |

| Fig. 4.5.  | Layout top view of TIA w/o protection70                                    |

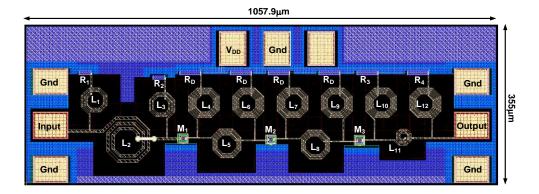

| Fig. 4.6.  | The architecture of TIA with $\pi$ -diode                                  |

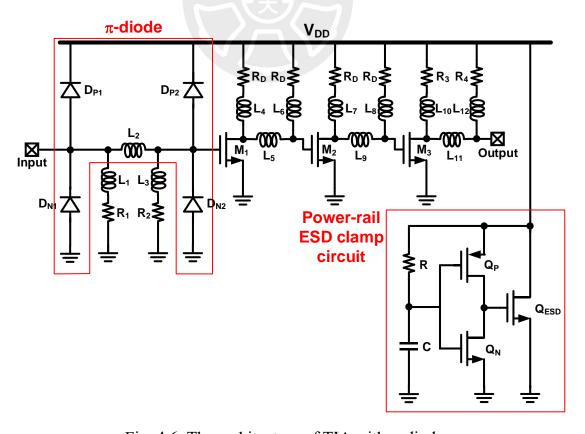

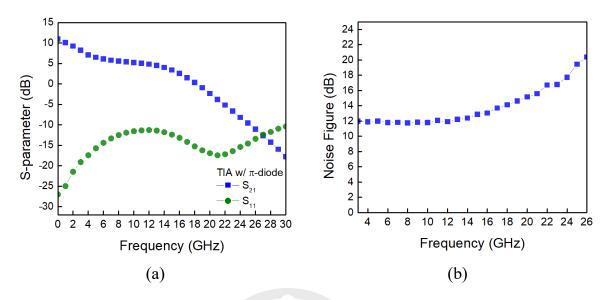

| Fig. 4.7.  | Simulated (a) S-parameter and (b) noise figure of TIA with $\pi$ -diode71  |

| Fig. 4.8.  | Layout top view of TIA with $\pi$ -diode                                   |

| Fig. 4.9.  | The architecture of TIA with $\pi$ -SDSCR72                                |

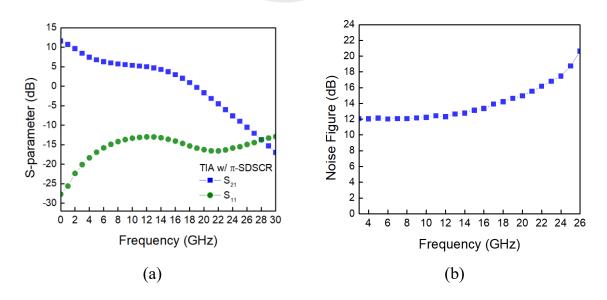

| Fig. 4.10. | Simulated (a) S-parameter and (b) noise figure of TIA with $\pi$ -SDSCR 72 |

| Fig. 4.11. | Layout top view of TIA with $\pi$ -SDSCR73                                 |

| Fig. 4.12. | The architecture of TIA with $\pi$ -RTSCR73                                |

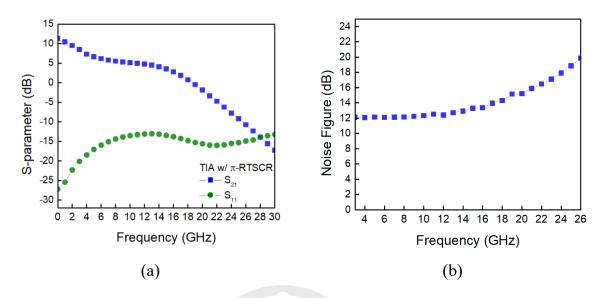

| Fig. 4.13. | Simulated (a) S-parameter and (b) noise figure of TIA with $\pi$ -RTSCR 74 |

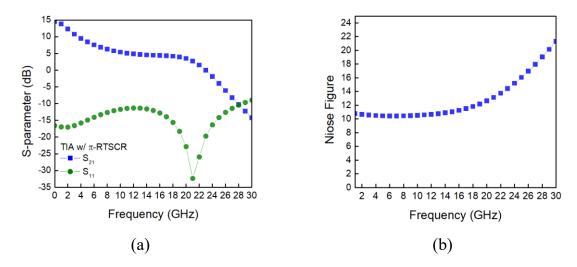

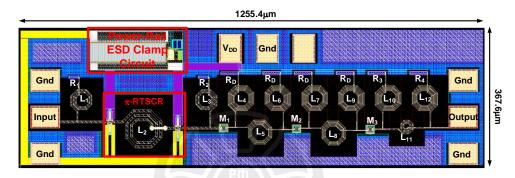

| Fig. 4.14. | Layout top view of TIA with $\pi$ -RTSCR77                                 |

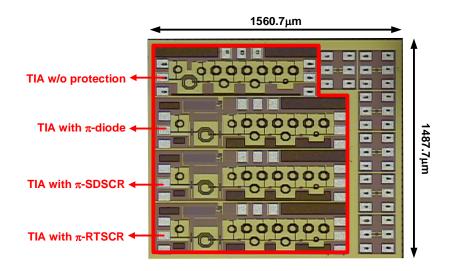

| Fig. 4.15. | The chip photograph of test TIA circuits                                   |

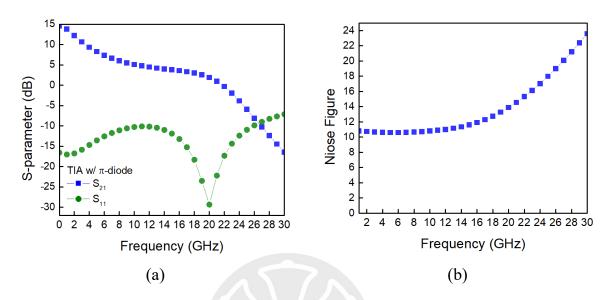

| Fig. 4.16. | Measured (a) S-parameter and (b) noise figure of TIA w/o protection .75    |

| Fig. 4.17. | Measured (a) S-parameter and (b) noise figure of TIA with $\pi$ -diode76   |

| Fig. 4.18. | Measured (a) S-parameter and (b) noise figure of TIA with $\pi$ -SDSCR 76  |

| Fig. 4.19. | Measured (a) S-parameter and (b) noise figure of TIA with $\pi$ -RTSCR.77  |

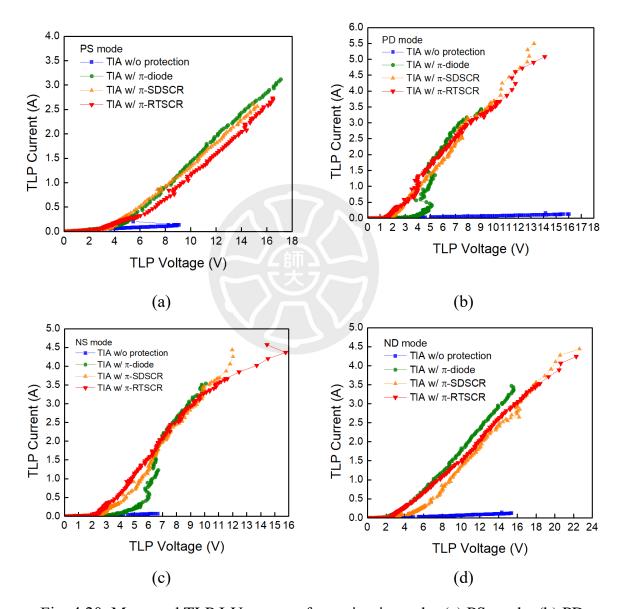

| Fig. 4.20. | Measured TLP I-V curves of test circuits under (a) PS mode, (b) PD                          |    |

|------------|---------------------------------------------------------------------------------------------|----|

|            | mode, (c) NS mode, and (d) ND mode                                                          | 78 |

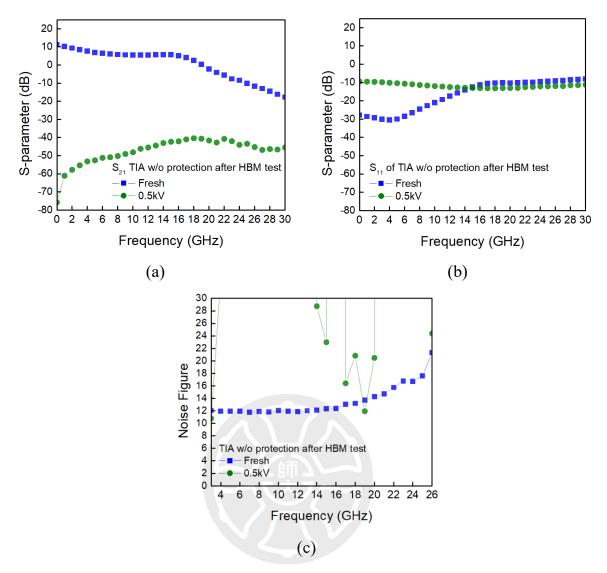

| Fig. 4.21. | Measured (a) S <sub>21</sub> and (b) S <sub>11</sub> (c) noise figure of TIA w/o protection |    |

|            | after HBM test                                                                              | 80 |

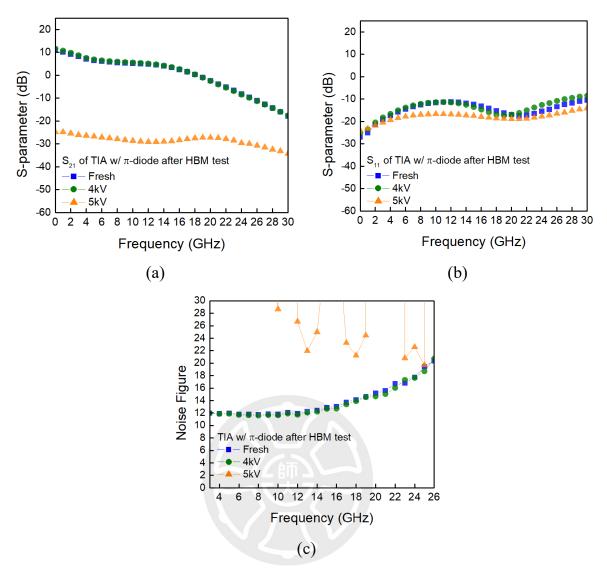

| Fig. 4.22. | Measured (a) $S_{21}$ (b) $S_{11}$ (c) noise figure of TIA with $\pi$ -diode after          |    |

|            | HBM test                                                                                    | 81 |

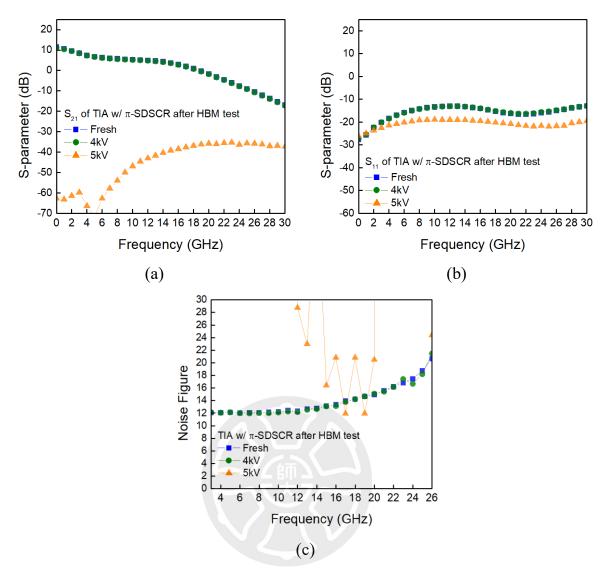

| Fig. 4.23. | Measured (a) $S_{21}$ (b) $S_{11}$ (c) noise figure of TIA with $\pi$ -SDSCR after          |    |

|            | HBM test                                                                                    | 82 |

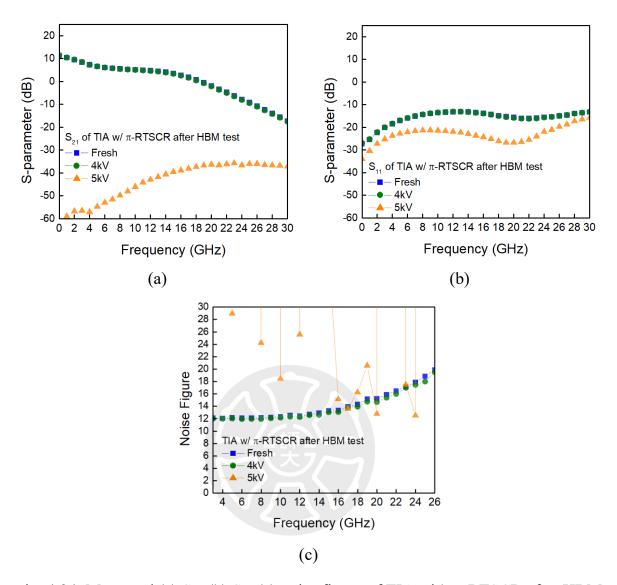

| Fig. 4.24. | Measured (a) $S_{21}$ (b) $S_{11}$ (c) noise figure of TIA with $\pi\text{-RTSCR}$ after    |    |

|            | HBM test                                                                                    | 83 |

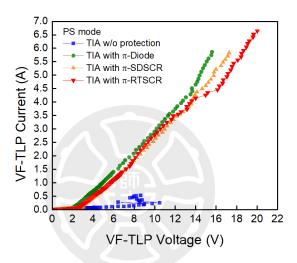

| Fig. 4.25. | VF-TLP I-V curves of test circuits under PS mode                                            | 84 |

| Fig. 4.26. | Measured (a) S <sub>21</sub> and (b) S <sub>11</sub> of test circuits                       | 86 |

| Fig. 4.27. | Comparison of FOM <sub>3_TIA_TLP</sub>                                                      | 87 |

| Fig. 4.28. | Comparison of FOM <sub>4_TIA_VFTLP</sub>                                                    | 88 |

| Fig. 4.29. | TIA circuit after ESD test                                                                  | 89 |

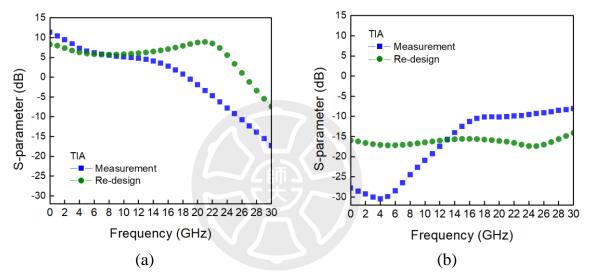

| Fig. 5.1.  | The measured and re-designed (a) S <sub>21</sub> and (b) S <sub>11</sub> of TIA             | 92 |

| Fig. 5.2.  | The scheme of LCSCR [34]                                                                    | 93 |

| Fig. 5.3.  | The cross-section view of LCSCR [34]                                                        | 93 |

| Fig. 5.4.  | The whole-chip ESD protection circuit with $\pi$ -LCSCR                                     | 94 |

| Fig. 5.5.  | The whole-chip ESD protection circuit with LCSCR and dual-                                  |    |

|            | SDSCR                                                                                       | 94 |

## **Chapter 1**

#### Introduction

#### 1.1 Motivation

In recent years, the demand for electronic products continues to increase. As the result, semiconductor industry becomes more and more important. However, electrostatic-discharge (ESD) events may cause great damage to integrated circuits [1]. Gross output value of IC products decreases due to the permanent failures caused by ESD stress. So that it is an effective way to enhance the production value of semiconductor industry to learn how to design ESD protection circuits. With the rapid development of processing technologies, the size of transistor is minimized to increase the operating speed and the gate oxide of transistor becomes thinner at the same time. A thin gate oxide may easily damage by the ESD stress [2]. Therefore, the robustness of electronic circuits decreases. However, there are still strict specifications for commercial IC products. There are more and more severe challenges about the reliability of integrated circuits in current semiconductor industry.

With the development of internet and communication technology, the demand for high-speed transmission products is gradually increasing. As the operating frequency of electronic circuits increases, it is more difficult to protect ICs from ESD damage effectively. The parasitic capacitance existing in protection elements causes signal loss on input signal. The high-frequency signal attenuation occurs when the ESD protection circuits are equipped [3]. In order not to degrade the high-frequency characteristics of internal circuit, the parasitic effect of protection device needs to be considered for different applications.

### 1.2 Background of ESD

ESD is a phenomenon that the charges transfer between different objects forming the discharging path. ESD current is up to several amperes (A) and can be generated in nanoseconds (ns). Some parts inside the circuit are unable to operate functionally when the large current flows into internal circuit instantly. As the result, IC products must be equipped with ESD protection circuit to ensure the reliability during operation. ESD problems have existed in electronics circuits since the semiconductor industry started to develop. Moreover, different kinds of ESD events are found as the process progresses.

#### 1.3 ESD Test Standards

For commercial IC products, reliability is an important issue. The electronic circuits during manufacturing have to pass related tests. Some associations such as US military standard (MIL-STD), Joint Electron Device Engineering Council (JEDEC), and Electrostatic Discharge Association (ESDA) built the standards for ESD tests. The components are required to take the ESD tests before assembled into the products. The tests for electronic components is defined as component-level test. Component-level tests are classified as human-body model (HBM), machine model (MM), and charged-device model (CDM) based on the cause of ESD and discharging method. However, the specific HBM level can ensure a minimum MM level. There is a reduction of MM test in recent years. The equivalent circuits and test standards of HBM and CDM are introduced in following part.

#### (1) Human-Body Model (HBM)

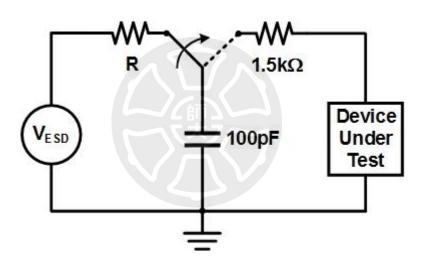

The human body will accumulate electric charges due to friction between the feet and the floor when walking. When the IC products are touched by people, the discharging path is formed. ESD current flows into IC instantly and causes damage to the IC. The model of HBM (MIL-STD-883C method 3015.7) is shown in Fig. 1.1. The equivalent capacitance of HBM is 100pF, and the equivalent resistance is  $1.5k\Omega$ . The human body is charged as a 100pF capacitor and discharges the charges to ground through IC as a  $1.5k\Omega$  resistor [4], [5]. The target level of HBM ESD is shown in Table 1.1 [6]. The components of commercial IC products are required to pass 2kV HBM test.

Fig. 1.1. The equivalent circuit of HBM.

Table 1.1. The target level of HBM

| HBM Level     | Impact on manufacturing environment              |  |  |  |

|---------------|--------------------------------------------------|--|--|--|

| 100V to <500V | Detailed ESD control method                      |  |  |  |

| 500V          |                                                  |  |  |  |

| 1kV           | Basic ESD control methods for safe manufacturing |  |  |  |

| 2kV           |                                                  |  |  |  |

#### (2) Charged-Device Model (CDM)

In the manufacturing process of IC, it may accumulate charges itself. Once the pin of IC contacts with ground, the discharging path is formed. The ESD current flowing from charged device leads to internal damage. The model of CDM is shown in Fig. 1.2 [7], [8]. The discharging time of CDM is much shorter than that of HBM and MM [9]. IC suffers permanent damage more easily. As shown in Table 1.2, the components of commercial IC products are required to pass 250V CDM test [10]. In this thesis, very fast TLP test is used with the pulse width in range of 1~10ns to simulate CDM ESD stress.

Fig. 1.2. The equivalent circuit of CDM.

Table 1.2. The target level of CDM

| CDM Level           | ESD Control Requirements                                |  |  |

|---------------------|---------------------------------------------------------|--|--|

|                     | Basic ESD control methods,                              |  |  |

| $V_{CDM}\!<\!200V$  | Process specific measures,                              |  |  |

|                     | Charging/discharging measurements at each process step. |  |  |

| $V_{CDM} \ge 200 V$ | Basic ESD control methods.                              |  |  |

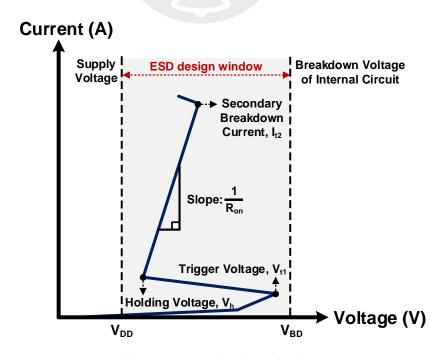

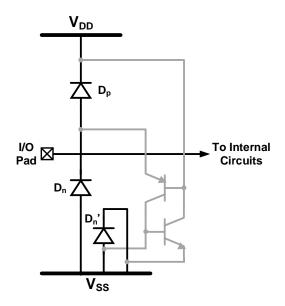

### 1.4 Design Concepts of ESD Protection

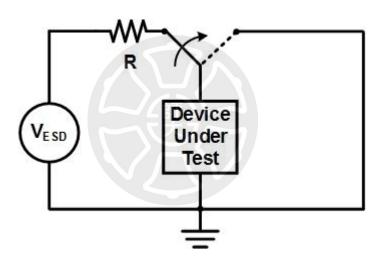

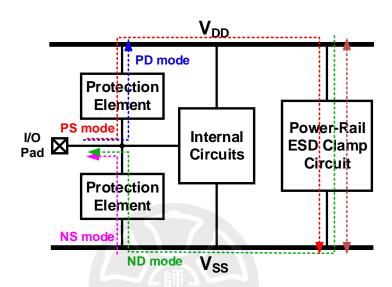

ESD event is very common in our daily lives and has serious impact on electronic products. It is necessary to design ESD protection circuits for IC products to prevent the damage of ESD stress. The I/O terminal is the most vulnerable to ESD damage from outside among all the pins in integrated circuits. The gate-oxide is generally controlled by the bias applied to input pad [11]. Therefore, to protect the thin gate-oxide in time before ESD current flows into internal circuit, ESD protection circuits are usually placed near I/O pad to discharge it. The protection circuits are also necessary between the power rails to prevent from ESD damage. The whole-chip ESD protection design is realized with I/O ESD protection circuit and power-rail ESD clamp circuit as shown in Fig. 1.3.

Fig. 1.3. Whole-chip ESD protection design.

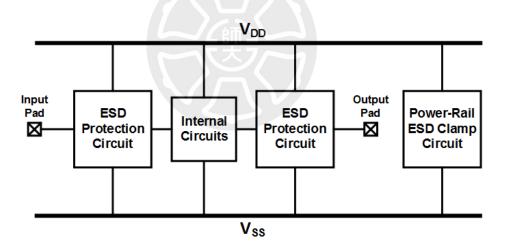

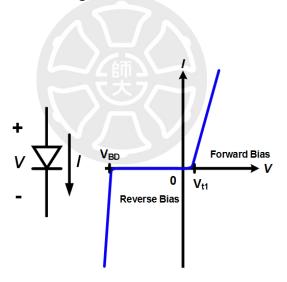

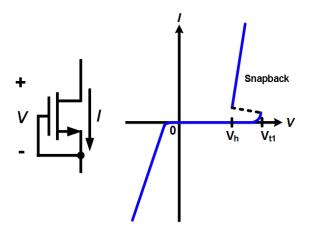

Fig. 1.4 shows a general ESD design window. ESD design window is defined as a guideline for designing protection circuits, where X-axis shows the measured voltage of device under test, and Y-axis shows the measured current value. ESD protection device is designed to operate in the range between supply voltage  $(V_{DD})$  which is the maximum voltage value and the internal circuit breakdown voltage  $(V_{BD})$ . Generally, the lower

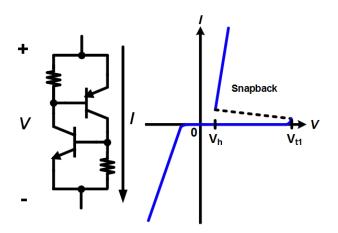

limit is  $1.1 \times V_{DD}$ , and the upper limit is  $0.9 \times V_{BD}$ . There are some properties of ESD protection circuit [12]. To reduce the power consumption, protection device must be kept off when internal circuit operates below  $V_{DD}$ . In addition, when internal circuit is during normal operation, ESD protection design should not affect circuit functions. ESD protection device has to turn on before the internal circuit breakdown when ESD stress hits. So that the trigger voltage  $(V_{t1})$  must be lower than  $V_{BD}$ . There is snapback phenomenon in some protection devices. The voltage cross the protection device drops a lot during conduction. Therefore, the power dissipation can be lower because of the lower holding voltage  $(V_h)$  and the device can conduct more ESD current before thermal breakdown. However,  $V_h$  must be higher than  $V_{DD}$  to prevent latch-up effect. The slope of I-V curve is defined as the reciprocal of on-resistance  $(R_{on})$ . The protection device turns on with lower  $R_{on}$  can discharge ESD current in lower clamping voltage. Protection device is destroyed permanently when ESD current is higher than the secondary breakdown current  $(I_{12})$ , as the result, the robustness is proportional to  $I_{12}$ .

Fig. 1.4. ESD design window.

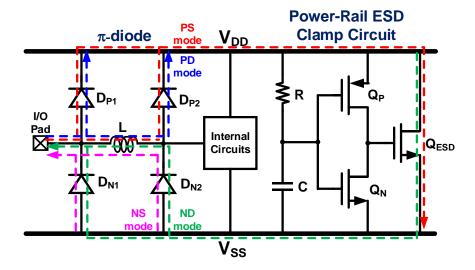

There are four pin-combinations which are positive I/O-to- $V_{SS}$  (PS mode), positive I/O-to- $V_{DD}$  (PD mode), negative I/O-to- $V_{SS}$  (NS mode), and negative I/O-to- $V_{DD}$  (ND mode). Equipped with power-rail ESD clamp circuit, the discharging path is shown in Fig. 1.5.

Fig. 1.5. Whole-chip ESD protection design with corresponding path.

## 1.5 Organization about This Thesis

There are five chapters in this thesis. The motivation of this research and the background of the reliability issue is introduced in chapter 1. Chapter 2 presented some studies of ESD protection designs for high-frequency applications. In chapter 3, the devices which are selected for traditional and proposed design are noted. The simulation data and measurement results are recorded at the end of this chapter. At last, the proposed ESD protection circuit is verified with a trans-impedance amplifier (TIA). There are the simulation and measurement results in chapter 4. Chapter 5 discussed the conclusion and future work.

## Chapter 2

## Studies of ESD Protection Designs for High-Speed Applications

#### 2.1 Consideration of ESD Protection Design at High-Speed Circuits

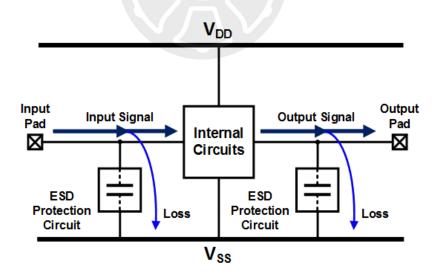

As the operating speed of IC increases, ESD protection circuit used for high-speed IC faces more severe challenges. The parasitic capacitance formed by ESD protection circuit at I/O pad is one of important design consideration for high-speed circuit [13]. As shown in Fig. 2.1, the parasitic capacitance of ESD protection circuit will cause the signal loss form I/O pad to ground and the performance of high-speed circuit will degenerate. It has to be considered as ESD protection circuit is applied.

Fig. 2.1. Signal loss at high frequencies.

ESD protection circuit must provide ICs with enough robustness against ESD stress.

The ESD level is proportional to the size of protection device. ESD protection device

must be large enough to provide sufficient ESD robustness. However, larger device size leads to higher parasitic capacitance which may cause undesirable signal loss. It is hard to design a ESD protection circuit for high-speed applications without distortion of input signal [14], [15]. There is a trade-off between ESD robustness and high-frequency performance when ESD protection circuit is designed for high-speed applications,

Diode, MOS, and silicon-controlled rectifier (SCR) are commonly used devices for ESD protection in CMOS process [16]. The I-V curve of diode is plotted in Fig. 2.2. Forward biased diode discharges high current and clamps the voltage at a low level. Diode is suitable for ESD protection because of its characteristics. Diode also discharges current when it reversely breaks down. However, the high breakdown voltage makes the heat during discharging is much higher.

Fig. 2.2. The I-V curve of diode.

MOS is also used as an ESD protection device with the gate of NMOS connected to ground and the gate of PMOS connected to  $V_{DD}$ . In order to reduce unnecessary power dissipation, the channel of MOS is kept off with gate connected to ground or  $V_{DD}$  under normal operation. The I-V curve of NMOS is plotted in Fig. 2.3. When ESD stress hits, the parasitic NPN inside NMOS turns on to discharge ESD current accompanied by the

slight snapback phenomenon. The trigger voltage of NMOS is higher than that of diode because it is conducted after the breakdown of P-N junction.

Fig. 2.3. The I-V curve of NMOS.

SCR is a p-n-p-n four-layer device composed of embedded NPN and PNP [17]. It turns on with the leakage current flowing through the resistance between the base and emitter. The I-V curve of SCR is plotted in Fig. 2.4. When SCR is conducted, there is a positive-feedback mechanism formed. As a result, SCR can discharge high current with strong snapback phenomenon [18].

Fig. 2.4. The I-V curve of SCR.

## 2.2 ESD Protection Designs for High-Speed Application

#### 2.2.1 Capacitive ESD Protection Circuit

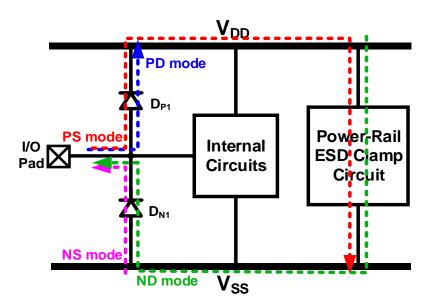

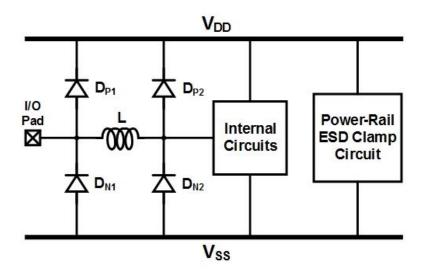

#### (1) Dual Diodes [19]

As shown in Fig. 2.5, a pair of diodes near I/O pad is a commonly used ESD protection circuit. The diode placed from I/O to  $V_{DD}$  ( $D_{Pl}$ ) form the path for positive I/O-to- $V_{DD}$  (PD mode) when positive ESD stress hits I/O pad. The diode placed from  $V_{SS}$  to I/O pad ( $D_{Nl}$ ) form the path for negative I/O-to- $V_{SS}$  (NS mode) when negative ESD stress hits I/O pad. In assistance with power-rail ESD clamp circuit, the whole-chip ESD protection can be realized. In series with power-rail ESD clamp circuit, the diode ( $D_{Pl}$ ) forms the path of the positive I/O-to- $V_{SS}$  (PS mode). The path of the negative I/O-to- $V_{DD}$  (ND mode) is formed by the diode ( $D_{Nl}$ ) in series with power-rail ESD clamp circuit. To reduce the parasitic effect, the size of diode is cut down to lower the capacitive load. However, the ESD robustness decreases with reducing size.

Fig. 2.5. ESD protection design of dual diodes [19].

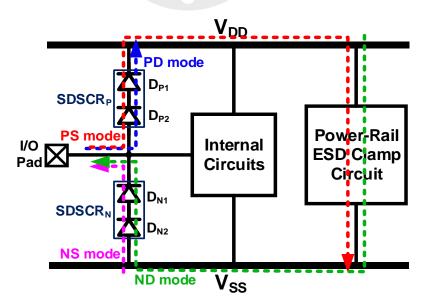

#### (2) Dual Stacked Diodes with Embedded SCR (SDSCR) [20]

For the high-speed applications, the parasitic capacitance of protection circuit has to be reduced to lower the signal loss. To solve this problem, there is an improved configuration proposed which is stacking diodes with embedded SCR (SDSCR). SCR is a useful ESD protection device in CMOS process due to high robustness. Moreover, the SCR device can be applied at high frequencies because of its low parasitic capacitance per layout area. With positive-feedback mechanism, the SCR device can discharge high ESD current.

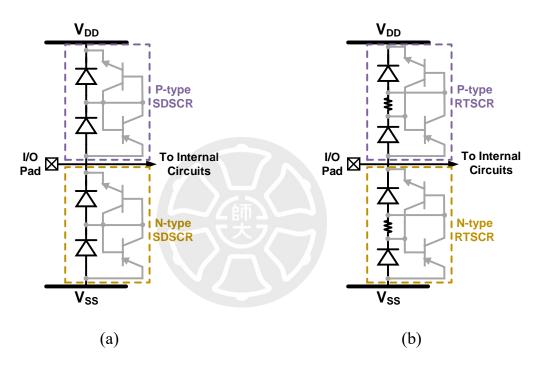

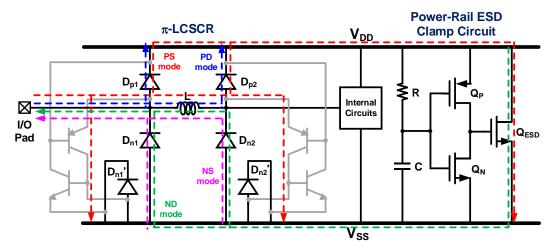

As shown in Fig. 2.6, two stacked diodes with embedded SCR are placed from  $V_{SS}$  to I/O pad ( $D_{N1}$ ,  $D_{N2}$ ) and I/O pad to  $V_{DD}$  ( $D_{P1}$ ,  $D_{P2}$ ). The discharging path of dual SDSCR is the same as the dual diodes. With the help of power-rail ESD clamp circuit, whole-chip ESD protection is realized. In this improved structure, the parasitic capacitance is reduced and the stacked diode also act as the trigger device of the embedded SCR to make it fast turn on.

Fig. 2.6. ESD protection design of dual SDSCR [20].

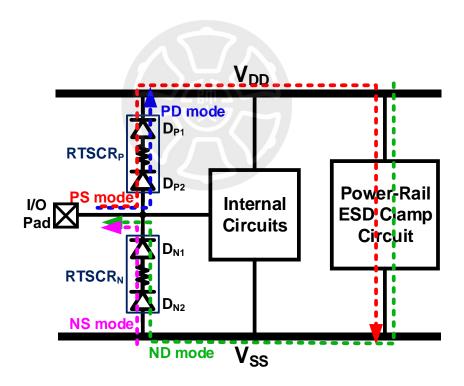

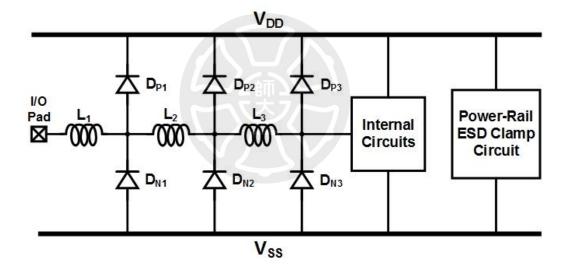

#### (3) Dual Resistor-Triggered SCR (RTSCR) [21]

By using a small resistor as the trigger element of SDSCR, the resistor-triggered SCR (RTSCR) is present. As shown in Fig. 2.7, the small resistor is inserted between each stacked diodes. Two resistor-trigger SCR are placed from  $V_{SS}$  to I/O pad ( $D_{N1}$ ,  $D_{N2}$ ) and I/O pad to  $V_{DD}$  ( $D_{P1}$ ,  $D_{P2}$ ). The discharging path of dual RTSCR is the same as the dual diodes. With the help of power-rail ESD clamp circuit, whole-chip ESD protection is realized. In this structure, the small resistor can limit the large ESD current flowing through the diode path so that the large ESD current can be discharge through the robust SCR path. The small resistor can reduce the overall parasitic capacitance seen at I/O as well.

Fig. 2.7. ESD protection design of dual SDSCR [21].

#### 2.2.2 Distributed ESD Protection Circuit (DESD)

The parasitic capacitance of ESD protection circuit near I/O pad will cause high-frequency performance degradation. To solve this problem, the size of protection device must be reduced. However, the size of protection device is proportional to the ESD robustness. Smaller device provides relatively lower ESD level.

Another way to design the ESD protection circuit for high-frequency applications is dividing ESD protection devices into many sections [22]. It is an effective way to maintain the ESD robustness without severe high-frequency degradation. To achieve good high-frequency performance, these parts of protection device are connected with matching elements such as inductor. The inductor can resonate with the parasitic capacitance of protection devices. Therefore, the high-frequency signal can be transmitted with less distorting.

As shown in Fig. 2.8, the distributed ESD protection circuit is composed of two sections ( $D_{P1}$ ,  $D_{N1}$  and  $D_{P2}$ ,  $D_{N2}$ ). An inductor (L) is used to sustain the broadband performance as the matching element. The diodes can provide the discharging path under forward bias for PD mode and NS mode. With the help of power-rail ESD clamp circuit, the ESD stress under PS mode and ND mode can also be discharged.

Another way to match the dual diodes is presented in Fig. 2.9. The ESD protection device is divided into three sections ( $D_{P1}$ ,  $D_{N1}$ ,  $D_{P2}$ ,  $D_{N2}$ , and  $D_{P3}$ ,  $D_{N3}$ ) and with three inductors ( $L_1$ ,  $L_2$ , and  $L_3$ ). Each part of protection device can be much smaller. However, with more inductors in use, the layout area is also increased. Both two structures can present great ESD robustness and achieve good broadband performance.

Fig. 2.8. ESD protection design of two-section distributed circuit [22].

Fig. 2.9. ESD protection design of multi-section distributed circuit [22].

## Chapter 3

## Design of $\pi$ -Model SCR ( $\pi$ -SCR)

## 3.1 Design Concepts of Distributed Circuit

In recent years, wireless communication technology has been flourishing and the demand for high-speed transmission products is gradually increasing. The high transmission rate products need to be equipped a wider bandwidth to enable faster signal changes. As products with high transmission rates become more and more popular, the requirements of broadband integrated circuits for ESD protection are also becoming stricter. The protection components must not affect the high frequency performance of the internal circuit as much as possible, and provide high ESD robustness at the same time. Therefore, traditional ESD protection designs applied to electronic circuits are no longer suitable for high-speed ICs. The parasitic capacitance of protection device near I/O pad may affect the input signal. The impedance of parasitic capacitor decreases as the operating frequency rises. It means that the protection device beside the input terminal causes the signal loss. To achieve high ESD level, the protection device has to be in large size. However, the parasitic capacitance affects the normal operation of internal circuit severely. Some methods are proposed to lower the parasitic effects, such as distributed ESD protection circuit [23], [24].

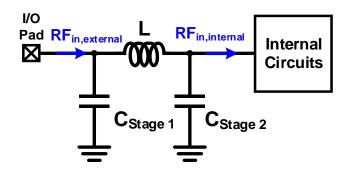

The protection device is divided into two smaller parts. One part is near the I/O pad, and the other part is close to internal circuits. Two parts of protection devices are connected by a matching element to sustain the high frequency performance. Matching element can resonate with the parasitic capacitance of two stages. Therefore, this distributed circuit can stand high ESD level with less signal loss. The parasitic

capacitance of the devices placed from  $V_{SS}$  to I/O and I/O to  $V_{DD}$  are parallel when analyzed in the ac state. As shown in Fig. 3.1, the high-frequency equivalent circuit is like a  $\pi$  shape.

Fig. 3.1. High-frequency equivalent circuit of  $\pi$ -model circuit.

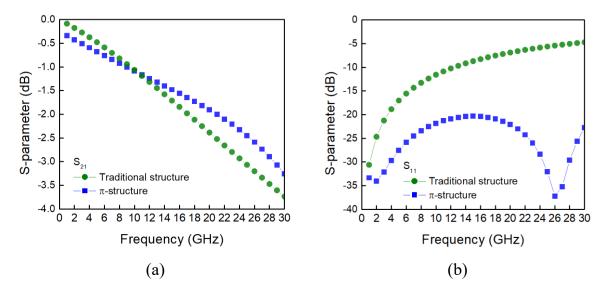

$C_{Stage1}$  and  $C_{Stage2}$  are from the protection element in two stages such as SCR and diode. The size of protection device decides the value of parasitic capacitance. According to the expected specification, the selected device is equipped to discharge the ESD current. Therefore, the size of the device has to be large enough. The PN junction and side-wall of protection element lead to parasitic capacitance. The junction capacitance increases with larger layout area. The longer perimeter of PN junction also makes the side-wall capacitance rise. Fig. 3.2 shows the high-frequency simulation results of traditional structure and  $\pi$ -structure. As compared with traditional structure,  $\pi$ -structure can provide lower insertion loss ( $S_{21}$ ) and return loss ( $S_{11}$ ).

Fig.3.2. (a)  $S_{21}$  (b)  $S_{11}$  simulation results of  $\pi$ -structure

## 3.2 Traditional $\pi$ -Model Diode ( $\pi$ -Diode)

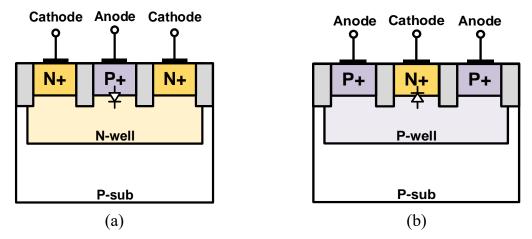

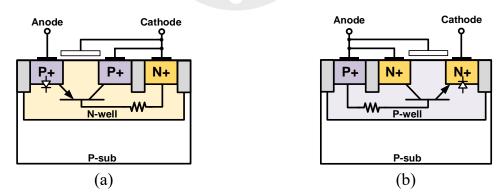

In CMOS technology, diode is a common ESD protection device. It consists of P-type and N-type semiconductor. There are two ways to realize p-n junction on chip. As shown in Fig. 3.3 (a), P-type diode has its P+ as anode and its N-well as cathode. As shown in Fig. 3.3 (b), the anode of N-type diode is P-well and the cathode of that is N+. The layout top view of symmetrical P-type and N-type diode is shown in Fig. 3.4.

Fig. 3.3. Cross-sectional view of symmetrical (a) P-type and (b) N-type diode.

Fig. 3.4. Layout top view of symmetrical (a) P-type and (b) N-type diode.

When diode is conducted under forward bias, it turns on and discharges current at low voltage. It can also discharge current under reverse bias, but the clamping voltage is higher than that of the forward biased diode. Diode has high ESD robustness because of low power dissipation. The characteristics like a switch make it suitable for ESD protection. Besides, it is also used as trigger device for SCR, MOSFET, and BJT.

Fig. 3.5. Whole-chip ESD protection circuit with traditional  $\pi$ -diode.

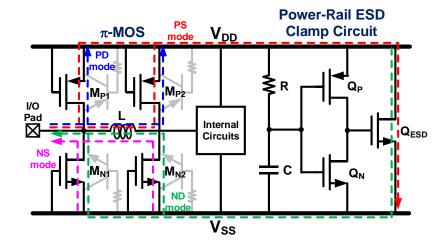

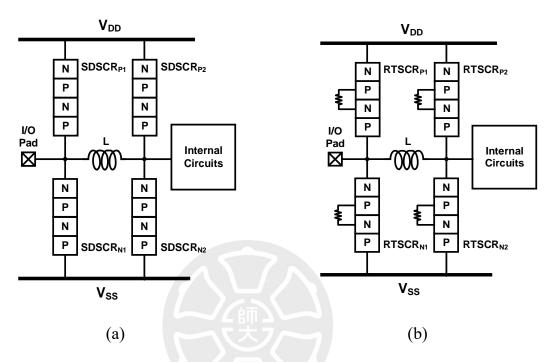

There is a two-section distributed circuit with diodes as device in traditional  $\pi$ -model diode ( $\pi$ -diode). The whole-chip ESD protection circuit with  $\pi$ -diode is shown in Fig. 3.5. Stage 1 is composed of diodes placed from  $V_{SS}$  to I/O ( $D_{N1}$ ) and from I/O to  $V_{DD}(D_{P1})$ , and stage 2 is composed of diodes placed from  $V_{SS}$  to I/O ( $D_{N2}$ ) and from I/O to  $V_{DD}(D_{P2})$ . The power-rail ESD clamp circuit is equipped to discharge the ESD current between  $V_{DD}$  and  $V_{SS}$ .

The ESD current under PD mode can be discharged by  $D_{P1}$  and  $D_{P2}$ . The ESD current under NS mode is discharged by  $D_{N1}$  and  $D_{N2}$ . The ESD current between  $V_{DD}$  and  $V_{SS}$  is discharged by the power-rail ESD clamp circuit. The ESD current under ND mode can be discharged by the power-rail ESD clamp circuit in series with  $D_{N1}$  and  $D_{N2}$ . The ESD current under PS mode is discharged by  $D_{P1}$  and  $D_{P2}$  in series with the power-rail ESD clamp circuit.

Table 3.1. The test cell of  $\pi$ -diode

| Cell Name             | Stage 1  |       | Stage 2         |       | Inductor |            |

|-----------------------|----------|-------|-----------------|-------|----------|------------|

| Cen Name              | Device   | Width | Device          | Width | Device   | Inductance |

| - diada 20 21         | $D_{P1}$ | 15µm  | $D_{P2}$        | 15µm  | L        | 0.31nH     |

| π-diode_30_31         | $D_{N1}$ | 15µm  | D <sub>N2</sub> | 15µm  |          |            |

| - diada 20 41         | $D_{P1}$ | 15μm  | $D_{P2}$        | 15µm  | L        | 0.41nH     |

| π-diode_30_41         | $D_{N1}$ | 15µm  | $D_{N2}$        | 15µm  |          |            |

| π-diode_50_31         | $D_{P1}$ | 25μm  | $D_{P2}$        | 25μm  | L        | 0.31nH     |

| <i>π</i> -drode_50_51 | $D_{N1}$ | 25μm  | $D_{N2}$        | 25μm  | L        | 0.31111    |

| 7 diada 50 41         | $D_{P1}$ | 25μm  | $D_{P2}$        | 25μm  | L        | 0.41nH     |

| π-diode_50_41         | $D_{N1}$ | 25μm  | D <sub>N2</sub> | 25μm  | L        | 0.411111   |

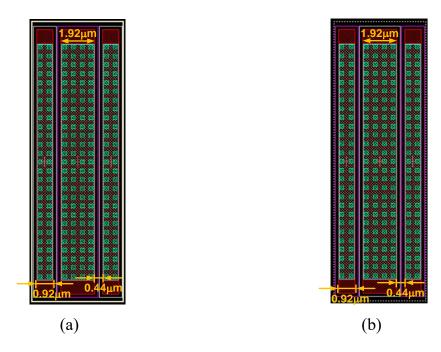

The test cells of whole-chip ESD protection circuit with  $\pi$ -diode are listed in Table 3.1. The layout top view of each cell is shown below. The width of diode used in  $\pi$ -diode is 15µm (as shown in Fig. 3.6) and 25µm (as shown in Fig. 3.7) respectively and there are two different matching inductor applied in each size.

Fig. 3.6. Layout top view of (a)  $\pi$ -diode\_30\_31 (b)  $\pi$ -diode\_30\_41

Fig. 3.7. Layout top view of (a)  $\pi$ -diode\_50\_31 (b)  $\pi$ -diode\_50\_41

### 3.3 Traditional $\pi$ -Model MOS ( $\pi$ -MOS)

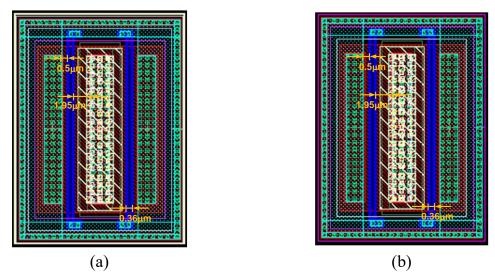

MOS transistor devices are also traditional ESD protection device in CMOS technology [25]. MOS transistors are the most common device in CMOS circuit design so that it is also used widely in ESD protection circuit. When a MOS transistor is connected as GGNMOS (gate-grounded NMOS) and GDPMOS (gate-V<sub>DD</sub> PMOS), it become a two-terminal device and there is a parasitic BJT formed between anode and cathode. As a result, ESD current can be discharge by the parasitic p-n-p and n-p-n junction. The cross-sectional view of MOS transistors is shown in Fig. 3.8. The anode of GDPMOS is its source terminal and GGNMOS has its source terminal as cathode. The layout top view of GDPMOS and GGNMOS is shown in Fig. 3.9. In order to comply with ESD design rules, the gate length of MOS is design as 0.36μm. The clearance from poly to contact on source of MOS is design as 0.5μm and that on drain side is design as 1.95μm. The silicide blocking is also used on the drain of MOS.

Fig. 3.8. Cross-sectional view of (a) GDPMOS and (b) GGNMOS.

Traditional  $\pi$ -model MOS ( $\pi$ -MOS) is a two-section distributed circuit with MOS transistors as device. The whole-chip ESD protection circuit with  $\pi$ -MOS is shown in Fig. 3.10. Stage 1 is composed of a GGNMOS placed from  $V_{SS}$  to I/O ( $M_{N1}$ ) and a GDPMOS placed from I/O to  $V_{DD}$  ( $M_{P1}$ ), and stage 2 is composed of a GGNMOS placed

$V_{SS}$  to I/O ( $M_{N2}$ ) and a GDPMOS placed from I/O to  $V_{DD}$  ( $M_{P2}$ ). The power-rail ESD clamp circuit is equipped to discharge the ESD current between  $V_{DD}$  and  $V_{SS}$ .

Fig. 3.9. Layout top view of (a) GDPMOS and (b) GGNMOS.

The ESD current under PD mode can be discharged by  $M_{P1}$  and  $M_{P2}$ . The ESD current under NS mode is discharged by  $M_{N1}$  and  $M_{N2}$ . The ESD current between  $V_{DD}$  and  $V_{SS}$  is discharged by the power-rail ESD clamp circuit. The ESD current under ND mode can be discharged by the power-rail ESD clamp circuit in series with  $M_{N1}$  and  $M_{N2}$ . The ESD current under PS mode is discharged by  $M_{P1}$  and  $M_{P2}$  in series with the power-rail ESD clamp circuit.

Fig. 3.10. Whole-chip ESD protection circuit with traditional  $\pi$ -MOS.

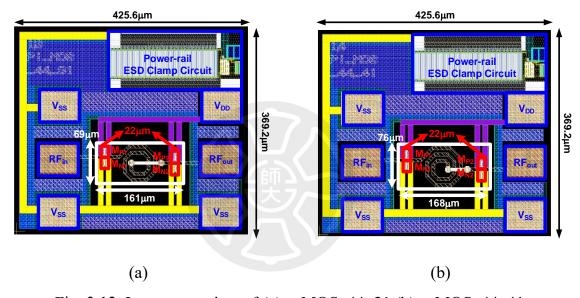

The test cells of whole-chip ESD protection circuit with  $\pi$ -MOS are listed in Table 3.2. The layout top view of each cell is shown below. The width of MOS transistors used in  $\pi$ -MOS is 100 $\mu$ m (as shown in Fig. 3.11), 22 $\mu$ m (as shown in Fig. 3.12), and 36 $\mu$ m (as shown in Fig. 3.13) respectively. In 22 $\mu$ m and 36 $\mu$ m these two case, there are two inductance of matching inductor are chosen to compare.

Table 3.2. The test cell of  $\pi$ -MOS

| Cell Name    | Stage 1      |       | Stage 2         |       | Inductor |            |

|--------------|--------------|-------|-----------------|-------|----------|------------|

|              | Device       | Width | Device          | Width | Device   | Inductance |

| - MOS 44 21  | $M_{P1}$     | 22μm  | $M_{P2}$        | 22μm  | T        | 0.31nH     |

| π-MOS_44_31  | $M_{\rm N1}$ | 22μm  | $M_{N2}$        | 22μm  | L        |            |

| π-MOS_44_41  | $M_{P1}$     | 22μm  | $M_{P2}$        | 22μm  | L        | 0.41nH     |

|              | $M_{N1}$     | 22μm  | $M_{N2}$        | 22μm  | L        |            |

| π-MOS_72_31  | $M_{P1}$     | 36µm  | $M_{P2}$        | 36µm  | L        | 0.31nH     |

|              | $M_{\rm N1}$ | 36µm  | M <sub>N2</sub> | 36µm  | L        |            |

| π-MOS_72_41  | $M_{P1}$     | 36µm  | $M_{P2}$        | 36µm  | L        | 0.41nH     |

|              | $M_{\rm N1}$ | 36µm  | $M_{N2}$        | 36µm  | L        |            |

| π-MOS_200_31 | $M_{P1}$     | 100µm | M <sub>P2</sub> | 100µm | L        | 0.31nH     |

|              | $M_{\rm N1}$ | 100µm | $M_{N2}$        | 100µm | L        | 0.311111   |

Fig. 3.11. Layout top view of  $\pi$ -MOS\_200\_31

Fig. 3.12. Layout top view of (a)  $\pi$ -MOS\_44\_31 (b)  $\pi$ -MOS\_44\_41

Fig. 3.13. Layout top view of (a)  $\pi$ -MOS\_72\_31 (b)  $\pi$ -MOS\_72\_41

# 3.4 Proposed $\pi$ -Model SCR ( $\pi$ -SCR)

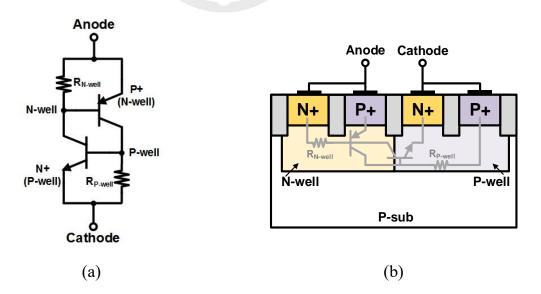

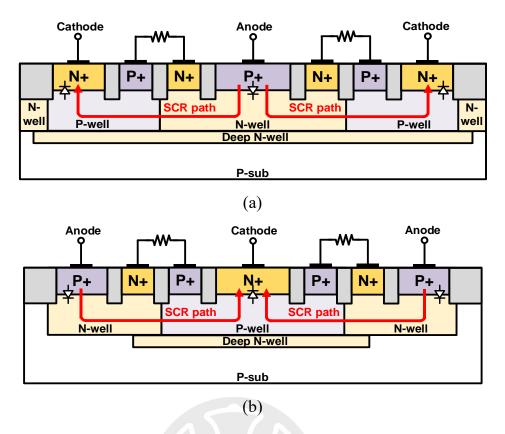

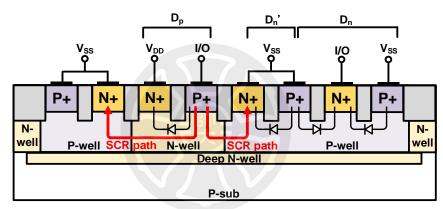

Silicon-controlled rectifier (SCR) is a four-layer semiconductor device which is composed of p-n-p-n (P+/N-well/P-well/N+) in CMOS technology. The equivalent circuit and the cross-sectional view of SCR is shown in Fig. 3.14. The P+/N-well/P-well formed the PNP, and the N-well/P-well/N+ formed the NPN inside SCR. The base of parasitic PNP is connected to the collector of parasitic NPN, and the base of parasitic NPN is connected to the collector of parasitic PNP. When SCR is fully conducted, it can discharge high current due to positive-feedback mechanism [26]. The voltage across SCR decreases rapidly during conduction. The snapback phenomenon of SCR reduces the power dissipation when ESD current flows. Therefore, SCR has high ESD robustness per unit layout area. Because of low clamping voltage, SCR cannot be turned off as internal circuit operates normally. The latch-up problems must be considered when ESD protection circuit is designed with SCR device.

Fig. 3.14. (a) Equivalent circuit and (b) cross-sectional view of SCR.

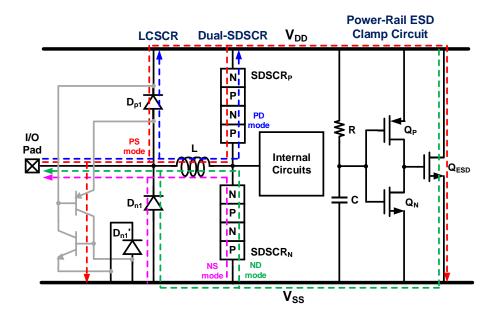

The integrated circuits operated in high-speed applications are very sensitive to the parasitic capacitance. In order to effectively protect the high-speed circuit and reduce the parasitic effects, several low-C SCR protection device designs such as stacked diode with embedded SCR (SDSCR) and resistor-triggered SCR (RTSCR) have been presented. As shown as Fig. 3.15, SCR devices are widely used to protect high-speed circuit.

Fig. 3.15. Equivalent circuit of (a) stacked diode with embedded SCR (SDSCR) (b) resistor-triggered SCR (RTSCR).

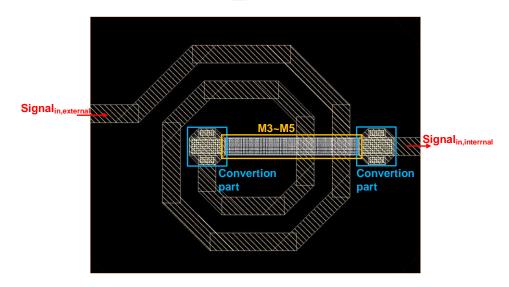

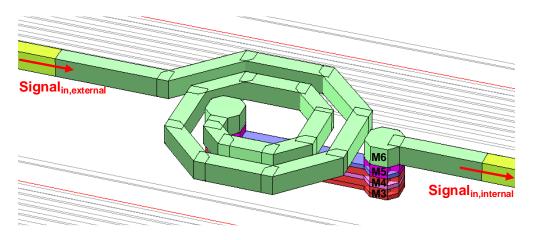

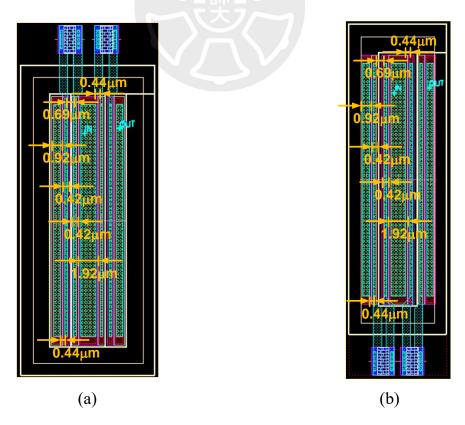

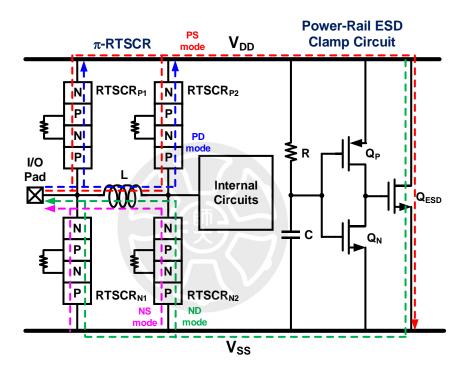

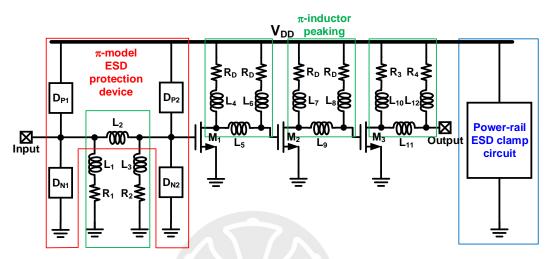

To further reduce the signal loss in high-speed applications, proposed  $\pi$ -model SCR ( $\pi$ -SCR) realizes SDSCR and RTSCR with two-section distributed circuit as shown in Fig. 3.16. By the use of matching inductor, the signal loss can be reduced. The octagonal spiral inductor is adopted as the matching element as shown in Fig. 3.17. The metal width of inductor is 6 $\mu$ m. The shape of the conversion between different layers is also octagonal in order not to reduce the cross-sectional area instantaneously. In addition,

three-layer metal (metal 3 to metal 5) is used together to increase the thickness. The structure of proposed matching inductor is shown in Fig. 3.18. In order to enhance the equivalent width, the SCR device can be realized in symmetrical structure.

Fig. 3.16. Equivalent circuit of proposed (a)  $\pi$ -SDSCR and (b)  $\pi$ -RTSCR.

Fig. 3.17. The top view of matching inductor.

Fig. 3.18. The structure of matching inductor.

## 3.4.1 $\pi$ -Model SDSCR ( $\pi$ -SDSCR)

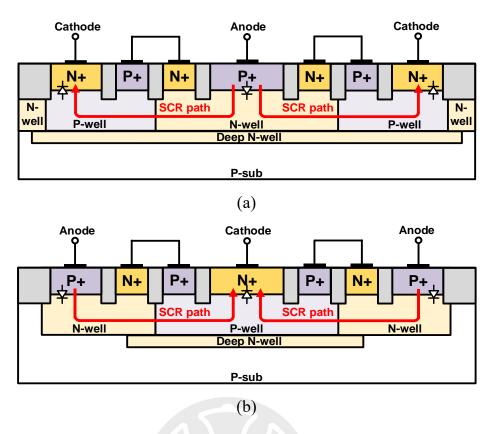

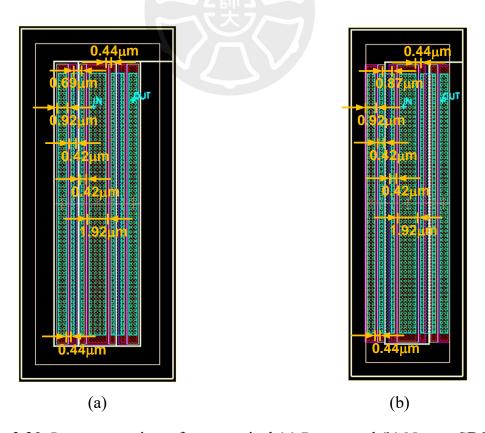

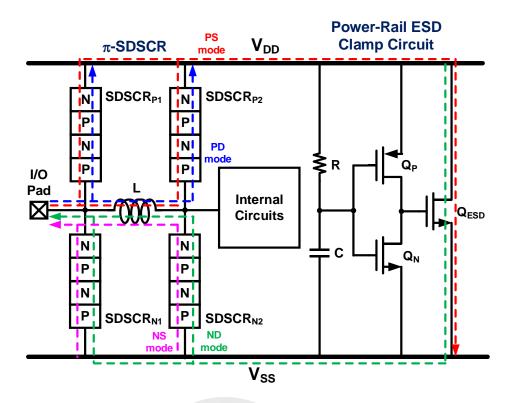

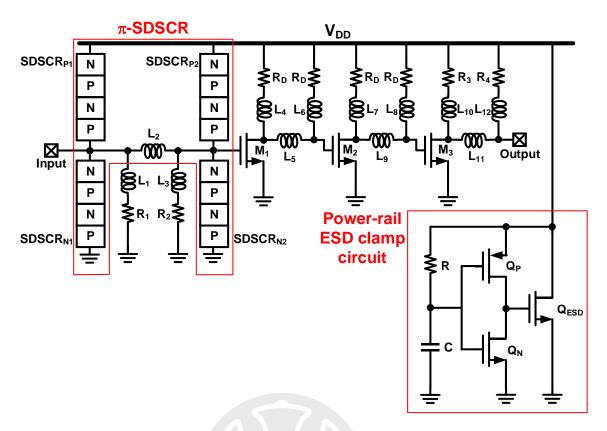

In  $\pi$ -model SDSCR ( $\pi$ -SDSCR), stage 1 near the I/O pad is composed of SDSCRs placed from  $V_{SS}$  to I/O (SDSCR<sub>N1</sub>) and from I/O to  $V_{DD}$  (SDSCR<sub>P1</sub>), and stage 2 near the internal circuit is composed of SDSCRs placed from  $V_{SS}$  to I/O (SDSCR<sub>N2</sub>) and from I/O to  $V_{DD}$  (SDSCR<sub>P2</sub>). The cross-sectional view of SDSCR is shown as Fig. 3.19. The layout top view of symmetrical P-type and N-type SDSCR is shown in Fig.3.20. There is a matching inductor between two stages. As shown in Fig. 3.21,  $\pi$ -SDSCR is equipped with power-rail ESD clamp circuit to realize the whole-chip ESD protection.

Fig. 3.19. Cross-sectional view of (a) P-type SDSCR and (b) N-type SDSCR.

Fig. 3.20. Layout top view of symmetrical (a) P-type and (b) N-type SDSCR.

Fig. 3.21. Whole-chip ESD protection circuit with proposed  $\pi$ -SDSCR.

The ESD current under PD mode can be discharged by  $SDSCR_{P1}$  and  $SDSCR_{P2}$ . The ESD current under NS mode is discharged by  $SDSCR_{N1}$  and  $SDSCR_{N2}$ . The ESD current between  $V_{DD}$  and  $V_{SS}$  is discharged by the power-rail ESD clamp circuit. The ESD current under ND mode can be discharged by the power-rail ESD clamp circuit in series with  $SDSCR_{N1}$  and  $SDSCR_{N2}$ . The ESD current under PS mode is discharged by  $SDSCR_{P1}$  and  $SDSCR_{P2}$  in series with the power-rail ESD clamp circuit.

The matching element between stage 1 and stage 2 is realized with an octagonal spiral inductor. It resonates with parasitic capacitance of SDSCRs. The impact of protection device on high-frequency signal can be reduced.

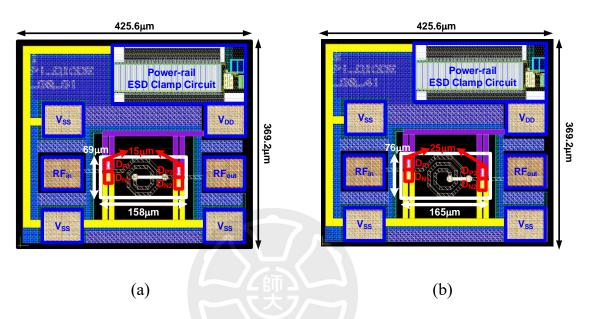

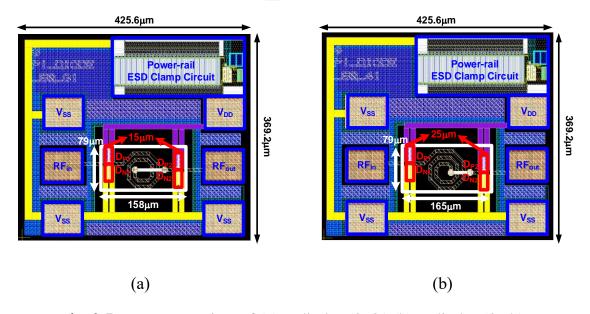

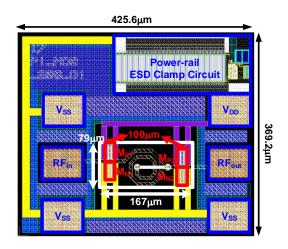

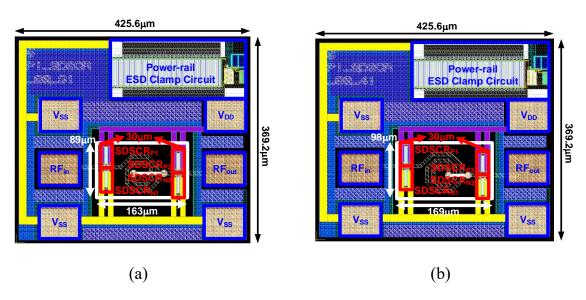

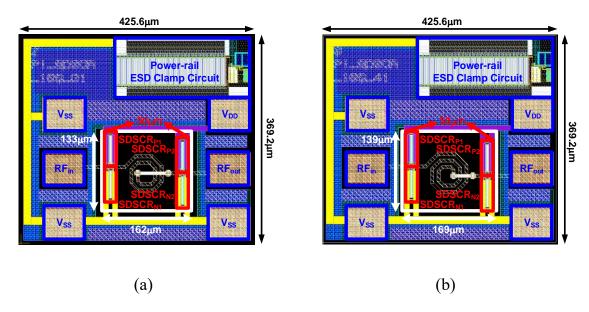

The test devices of  $\pi$ -SDSCR are listed in Table 3.3. The proposed design is fabricated in 0.18 $\mu$ m CMOS process. The width of SDSCR used in  $\pi$ -SDSCR\_60\_31 and  $\pi$ -SDSCR\_60\_41 is 30 $\mu$ m in symmetrical structure, the matching inductor is 0.31nH and 0.41nH respectively as shown in Fig. 3.22. The width of SDSCR used in  $\pi$ -

SDSCR\_100\_31 and  $\pi$ -SDSCR\_100\_41 is 50 $\mu$ m in symmetrical structure, the matching inductor is 0.31nH and 0.41nH respectively as shown in Fig. 3.23. The area of each test device is 425.6\* 369.2 $\mu$ m<sup>2</sup>.

Table 3.3. The test cell of  $\pi$ -SDSCR

| Cell Name      | Stage 1             |       | Stage 2             |       | Inductor |            |

|----------------|---------------------|-------|---------------------|-------|----------|------------|

|                | Device              | Width | Device              | Width | Device   | Inductance |

| - CDCCD (0.21  | SDSCR <sub>P1</sub> | 30µm  | SDSCR <sub>P2</sub> | 30µm  | L        | 0.31nH     |

| π-SDSCR_60_31  | SDSCR <sub>N1</sub> | 30µm  | SDSCR <sub>N2</sub> | 30µm  |          |            |

| π-SDSCR_60_41  | SDSCR <sub>P1</sub> | 30µm  | SDSCR <sub>P2</sub> | 30µm  | L        | 0.41nH     |

|                | SDSCR <sub>N1</sub> | 30µm  | SDSCR <sub>N2</sub> | 30µm  |          |            |

| π-SDSCR_100_31 | SDSCR <sub>P1</sub> | 50μm  | SDSCR <sub>P2</sub> | 50μm  | L        | 0.31nH     |

|                | SDSCR <sub>N1</sub> | 50μm  | SDSCR <sub>N2</sub> | 50μm  |          |            |

| π-SDSCR_100_41 | SDSCR <sub>P1</sub> | 50μm  | SDSCR <sub>P2</sub> | 50μm  | L        | 0.41nH     |

|                | SDSCR <sub>N1</sub> | 50μm  | SDSCR <sub>N2</sub> | 50μm  | L        | V.41NH     |

Fig. 3.22. Layout top view of (a)  $\pi$ -SDSCR\_60\_31 (b)  $\pi$ -SDSCR\_60\_41.

Fig. 3.23. Layout top view of (a)  $\pi$ -SDSCR\_100\_31 (b)  $\pi$ -SDSCR\_100\_41.

## 3.4.2 $\pi$ -Model RTSCR ( $\pi$ -RTSCR)

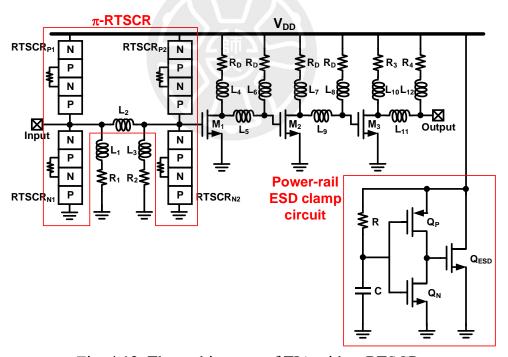

In  $\pi$ -model RTSCR ( $\pi$ -RTSCR), stage 1 near the I/O pad is composed of RTSCRs placed from  $V_{SS}$  to I/O (RTSCR<sub>N1</sub>) and from I/O to  $V_{DD}$  (RTSCR<sub>P1</sub>), and stage 2 near the internal circuit is composed of RTSCRs placed from  $V_{SS}$  to I/O (RTSCR<sub>N2</sub>) and from I/O to  $V_{DD}$  (RTSCR<sub>P2</sub>). The cross-sectional view of SDSCR is shown as Fig. 3.24. The layout top view of symmetrical P-type and N-type RTSCR is shown in Fig. 3.25. There is a matching inductor between two stages. As shown in Fig. 3.26,  $\pi$ -RTSCR is equipped with power-rail ESD clamp circuit to realize the whole-chip ESD protection.

Fig. 3.24. Cross-sectional view of (a) P-type RTSCR and (b) N-type RTSCR.

Fig. 3.25. Layout top view of symmetrical (a) P-type and (b) N-type RTSCR.

The ESD current under PD mode can be discharged by RTSCR<sub>P1</sub> and RTSCR<sub>P2</sub>. The ESD current under NS mode is discharged by RTSCR<sub>N1</sub> and RTSCR<sub>N2</sub>. The ESD current between  $V_{DD}$  and  $V_{SS}$  is discharged by the power-rail ESD clamp circuit. The ESD current under ND mode can be discharged by the power-rail ESD clamp circuit in series with RTSCR<sub>N1</sub> and RTSCR<sub>N2</sub>. The ESD current under PS mode is discharged by RTSCR<sub>P1</sub> and RTSCR<sub>P2</sub> in series with the power-rail ESD clamp circuit.

Fig. 3.26. Whole-chip ESD protection circuit with proposed  $\pi$ -RTSCR.

The matching element between stage 1 and stage 2 is realized with an octagonal spiral inductor. It resonates with parasitic capacitance of RTSCRs. The impact of protection device on high-frequency signal can be reduced.

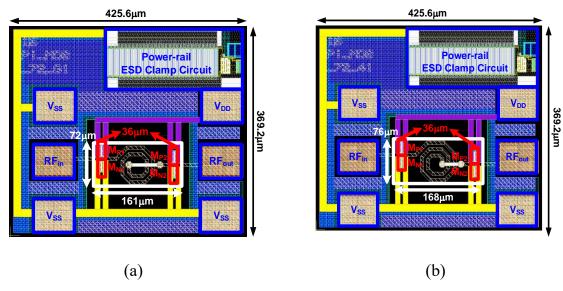

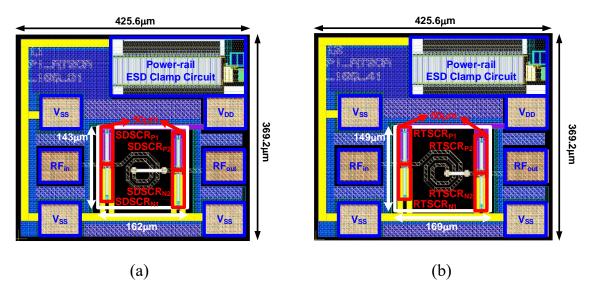

The test devices of  $\pi$ -RTSCR are listed in Table 3.4. The proposed design is fabricated in 0.18 $\mu$ m CMOS process. The width of RTSCR used in  $\pi$ -RTSCR\_60\_31 and  $\pi$ -RTSCR\_60\_41 is 30 $\mu$ m in symmetrical structure, the matching inductor is 0.31nH and 0.41nH respectively as shown in Fig. 3.27. The width of RTSCR used in  $\pi$ -

RTSCR\_100\_31 and  $\pi$ -RTSCR\_100\_41 is 50 $\mu$ m in symmetrical structure, the matching inductor is 0.31nH and 0.41nH respectively as shown in Fig. 3.28. The area of each test device is 425.6\* 369.2 $\mu$ m<sup>2</sup>.

Table 3.4. The test cell of  $\pi$ -RTSCR

| Cell Name      | Stage 1             |       | Stage 2             |       | Inductor |            |

|----------------|---------------------|-------|---------------------|-------|----------|------------|

|                | Device              | Width | Device              | Width | Device   | Inductance |

| π-RTSCR_60_31  | RTSCR <sub>P1</sub> | 30µm  | RTSCR <sub>P1</sub> | 30µm  | L        | 0.31nH     |

|                | RTSCR <sub>N1</sub> | 30µm  | RTSCR <sub>N1</sub> | 30µm  |          |            |

| π-RTSCR_60_41  | RTSCR <sub>P1</sub> | 30µm  | RTSCR <sub>P1</sub> | 30µm  | L        | 0.41nH     |

|                | RTSCR <sub>N1</sub> | 30µm  | RTSCR <sub>N1</sub> | 30µm  |          |            |

| π-RTSCR_100_31 | RTSCR <sub>P1</sub> | 50μm  | RTSCR <sub>P1</sub> | 50μm  | L        | 0.31nH     |

|                | RTSCR <sub>N1</sub> | 50μm  | RTSCR <sub>N1</sub> | 50μm  |          |            |

| π-RTSCR_100_41 | RTSCR <sub>P1</sub> | 50μm  | RTSCR <sub>P1</sub> | 50μm  | T        | 0.41nH     |

|                | RTSCR <sub>N1</sub> | 50μm  | RTSCR <sub>N1</sub> | 50μm  | L        |            |

Fig. 3.27. Layout top view of (a)  $\pi$ -RTSCR\_60\_31 (b)  $\pi$ -RTSCR\_60\_41.

Fig. 3.28. Layout top view of (a)  $\pi$ -RTSCR\_100\_31 (b)  $\pi$ -RTSCR\_100\_41.

## 3.5 Simulation Results

The high-frequency performance of traditional  $\pi$ -diode,  $\pi$ -MOS, proposed  $\pi$ -SDSCR and  $\pi$ -RTSCR are evaluated by S-parameter. By examining  $S_{21}$  and  $S_{11}$ , the impact of proposed ESD protection device on high-frequency applications is found out.

Larger  $S_{21}$  means that the signal is passed to another terminal with less loss. Smaller  $S_{11}$  means that the signal is delivered with less reflection. The proposed ESD protection device is designed to keep the  $S_{21}$  approach to 0 and make the  $S_{11}$  as smaller as possible.

Advanced design system (ADS) is used to simulate the S-parameter of all the protection device. The matching inductor is simulated with SONNET electromagnetic (EM) software. The simulation results of proposed design are compared with that of traditional design in similar parasitic capacitance.

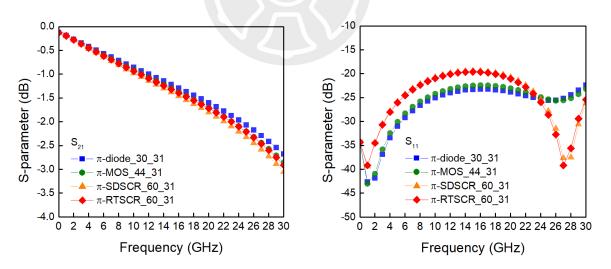

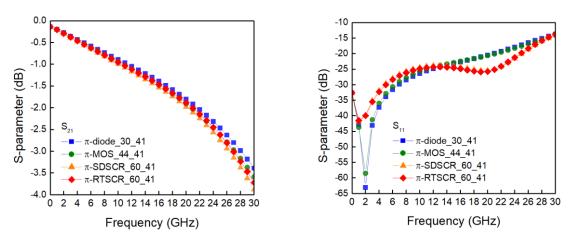

Simulated S-parameter of  $\pi$ -diode\_30\_31 is compared with that of  $\pi$ -MOS\_44\_31,  $\pi$ -SDSCR\_60\_31 and  $\pi$ -RTSCR\_60\_31 in Fig. 3.29. Simulated S-parameter of  $\pi$ -diode 30 41 is compared with  $\pi$ -MOS 44 41,  $\pi$ -SDSCR 60 41 and  $\pi$ -RTSCR 60 41

in Fig. 3.30. Simulated S-parameter of  $\pi$ -diode\_50\_31 is compared with that of  $\pi$ -MOS\_72\_31,  $\pi$ -MOS\_200\_31,  $\pi$ -SDSCR\_100\_31 and  $\pi$ -RTSCR\_100\_31 in Fig. 3.31. Simulated S-parameter of  $\pi$ -diode\_50\_41 is compared with that of  $\pi$ -MOS\_72\_41,  $\pi$ -SDSCR\_100\_41 and  $\pi$ -RTSCR\_100\_41 in Fig. 3.32. Simulated S-parameter at 10GHz is listed in Table 3.5.

There are two different sizes in each test devices. The parasitic capacitance of  $\pi$ -diode with 30µm width,  $\pi$ -MOS with 44µm width,  $\pi$ -SDSCR with 60µm width and  $\pi$ -RTSCR with 60µm width are similar. The parasitic capacitance of  $\pi$ -diode with 50µm width,  $\pi$ -MOS with 72µm width,  $\pi$ -SDSCR with 100µm width and  $\pi$ -RTSCR with 100µm width are similar. Therefore, test devices with similar parasitic capacitance use the same matching inductor to connect between two stages. From the simulation results, there is little difference between traditional device and proposed design. In addition, the  $S_{21}$  of all the smaller test cells at 20GHz is higher than -3dB.

Fig. 3.29. The simulated S-parameter of  $\pi$ -diode\_30\_31,  $\pi$ -MOS\_44\_31,  $\pi$ -SDSCR\_60\_31 and  $\pi$ -RTSCR\_60\_31.

Fig. 3.30. The simulated S-parameter of  $\pi$ -diode\_30\_41,  $\pi$ -MOS\_44\_41,  $\pi$ -SDSCR 60 41 and  $\pi$ -RTSCR 60 41.

Fig. 3.31. The simulated S-parameter of  $\pi$ -diode\_50\_31,  $\pi$ -MOS\_72\_31,  $\pi$ -MOS\_200\_31,  $\pi$ -SDSCR\_100\_31 and  $\pi$ -RTSCR\_100\_31.

Fig. 3.32. The simulated S-parameter of  $\pi$ -diode\_50\_41,  $\pi$ -MOS\_72\_41,  $\pi$ -SDSCR 100 41 and  $\pi$ -RTSCR 100 41.

Table 3.5. Simulated S-parameter at 20GHz

| Cell Name      | S <sub>21</sub> (dB) at 20GHz | S <sub>11</sub> (dB) at 20GHz |  |

|----------------|-------------------------------|-------------------------------|--|

| π-diode_30_31  | -1.60                         | -23.85                        |  |

| π-diode_30_41  | -1.80                         | -26.41                        |  |

| π-diode_50_41  | -2.29                         | -16.68                        |  |

| π-diode_50_41  | -2.47                         | -19.22                        |  |

| π-MOS_44_31    | -1.70                         | -23.05                        |  |

| π-MOS_44_41    | -1.91                         | -25.75                        |  |

| π-MOS_72_41    | -2.41                         | -16.52                        |  |

| π-MOS_72_41    | -2.61                         | -18.98                        |  |

| π-MOS_200_31   | -6.08                         | -10.43                        |  |

| π-SDSCR_60_31  | -1.80                         | -20.73                        |  |

| π-SDSCR_60_41  | -1.98                         | -24.40                        |  |

| π-SDSCR_100_41 | -2.45                         | -14.66                        |  |

| π-SDSCR_100_41 | -2.75                         | -16.17                        |  |

| π-RTSCR_60_31  | -1.72                         | -21.06                        |  |

| π-RTSCR_60_41  | -1.89                         | -24.90                        |  |

| π-RTSCR_100_41 | -2.45                         | -10.43                        |  |

| π-RTSCR_100_41 | -2.61                         | -16.29                        |  |

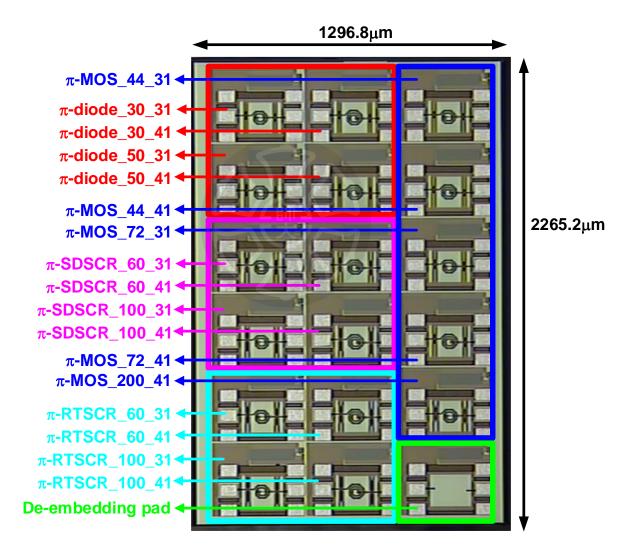

## 3.6 Measurement Results

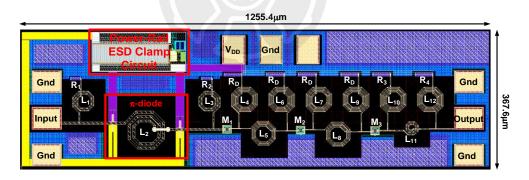

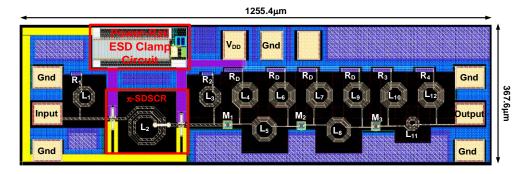

All the test devices are fabricated in 0.18 $\mu$ m CMOS process. The chip photograph is shown in Fig. 3.33. The width is 1296.8 $\mu$ m, and the length is 2265.2 $\mu$ m. There are four kinds of ESD protection devices,  $\pi$ -diode,  $\pi$ -MOS,  $\pi$ -SDSCR, and  $\pi$ -RTSCR in different size. The measurement results are introduced in following section.

Fig. 3.33. The chip photograph of test device.

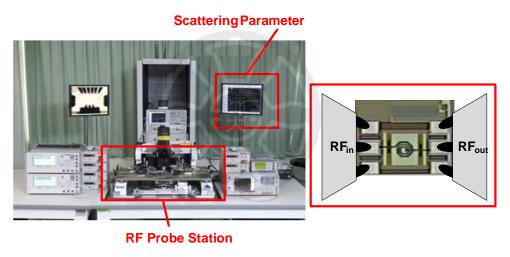

#### 3.6.1 High-Frequency Performance

As shown in Fig. 3.34, the S-parameter is measured by 67GHz RFIC parameter measurement system with 2-port GSG probes [27]. However, the effect of pad is included in measured S-parameter. The S-parameter of de-embedding pad is measured at first as a reference in Fig. 3.35 (a). Then the S-parameter of the test device is measured in Fig. 3.35 (b). The de-embedding technique is used to remove the effects of pad to extract the real characteristics of devices [28]. After the de-embedding technique is applied, the measured results are shown as follows.

Fig. 3.34. The setup of high-frequency measurement system. [27]

Fig. 3.35. The photograph of (a) de-embedding pad and (b) test device.

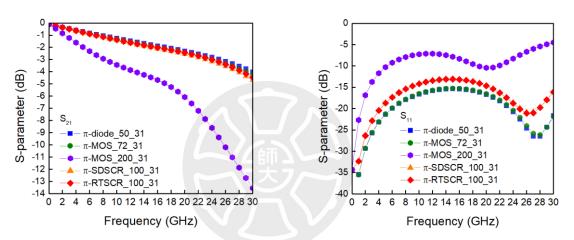

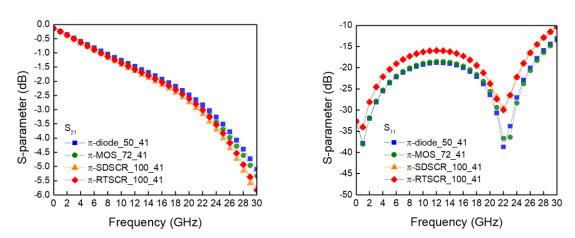

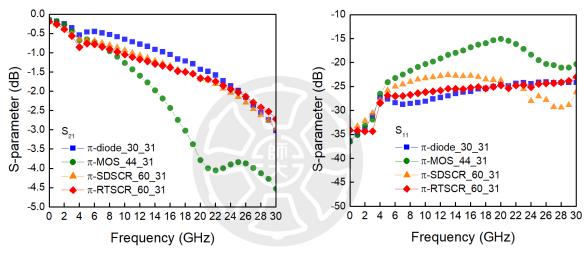

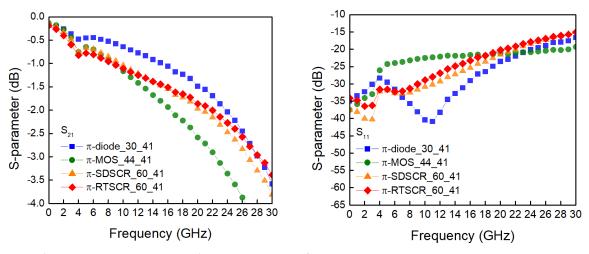

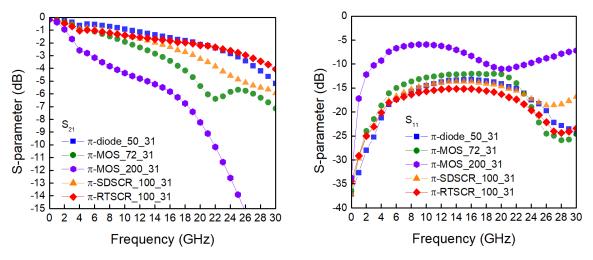

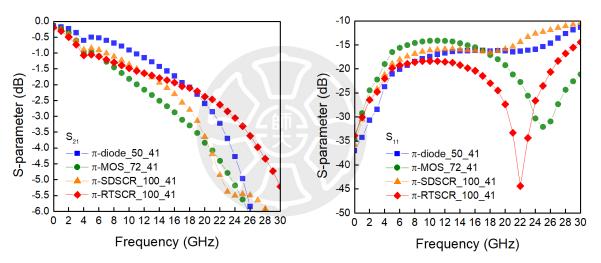

Measured S-parameter of  $\pi$ -diode\_30\_31 is compared with that of  $\pi$ -MOS\_44\_31,  $\pi$ -SDSCR\_60\_31 and  $\pi$ -RTSCR\_60\_31 in Fig. 3.36. Measured S-parameter of  $\pi$ -diode\_30\_41 is compared with that of  $\pi$ -MOS\_44\_41,  $\pi$ -SDSCR\_60\_41 and  $\pi$ -RTSCR\_60\_41 in Fig. 3.37. Measured S-parameter of  $\pi$ -diode\_50\_31 is compared with that of  $\pi$ -MOS\_72\_31,  $\pi$ -MOS\_200\_31,  $\pi$ -SDSCR\_100\_31 and  $\pi$ -RTSCR\_100\_31 in Fig. 3.38. Measured S-parameter of  $\pi$ -diode\_50\_41 is compared with that of  $\pi$ -MOS\_72\_41,  $\pi$ -SDSCR\_100\_41 and  $\pi$ -RTSCR\_100\_41 in Fig. 3.39. Measured S-parameters at 20GHz are listed in Table 3.6.

Fig. 3.36. The measured S-parameter of  $\pi$ -diode\_30\_31,  $\pi$ -MOS\_44\_31,  $\pi$ -SDSCR 60 31 and  $\pi$ -RTSCR 60 31.

Fig. 3.37. The measured S-parameter of  $\pi$ -diode\_30\_41,  $\pi$ -MOS\_44\_41,  $\pi$ -SDSCR\_60\_41 and  $\pi$ -RTSCR\_60\_41.

Fig. 3.38. The measured S-parameter of  $\pi$ -diode\_50\_31,  $\pi$ -MOS\_72\_31,  $\pi$ -MOS\_200\_31,  $\pi$ -SDSCR\_100\_31 and  $\pi$ -RTSCR\_100\_31.

Fig. 3.39. The measured S-parameter of  $\pi$ -diode\_50\_41,  $\pi$ -MOS\_72\_41,  $\pi$ -SDSCR 100 41 and  $\pi$ -RTSCR 100 41.

Table 3.6. Measured S-parameter at 20GHz

| Cell Name      | S <sub>21</sub> (dB) at 20GHz | S <sub>11</sub> (dB) at 20GHz |

|----------------|-------------------------------|-------------------------------|

| π-diode_30_31  | -1.43                         | -24.6                         |

| π-diode_30_41  | -1.58                         | -21.4                         |

| π-diode_50_31  | -2.13                         | -14.1                         |

| π-diode_50_41  | -2.59                         | -16.2                         |

| π-MOS_44_31    | -3.79                         | -15.0                         |

| π-MOS_44_41    | -2.58                         | -21.1                         |

| π-MOS_72_31    | -5.39                         | -12.1                         |

| π-MOS_72_41    | -3.83                         | -19.2                         |

| π-MOS_200_31   | -8.24                         | -11.0                         |

| π-SDSCR_60_31  | -1.68                         | -23.7                         |

| π-SDSCR_60_41  | -1.97                         | -21.5                         |

| π-SDSCR_100_31 | -3.27                         | -14.6                         |

| π-SDSCR_100_41 | -3.64                         | -15.8                         |

| π-RTSCR_60_31  | -1.66                         | -24.7                         |

| π-RTSCR_60_41  | -1.86                         | -20.1                         |

| π-RTSCR_100_31 | -2.20                         | -16.3                         |

| π-RTSCR_100_41 | -2.38                         | -27.4                         |

# 3.6.2 TLP I-V Curves

The characteristics of ESD protection devices are obtained by the transmission-line-pulsing (TLP) system. TLP systems generates high-energy pulse to simulate the current of ESD events. A set of voltage and current value is recorded for one pulse. All

of the data form the TLP I-V curves [29]. TLP system used in this work is shown in Fig. 3.40. [30]

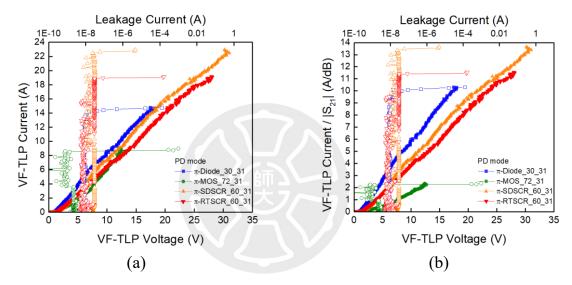

Trigger voltage ( $V_{t1}$ ), holding voltage ( $V_{h}$ ), turn-on resistance ( $R_{on}$ ), and the secondary breakdown current ( $I_{t2}$ ) can be observed from TLP I-V curves. The criterion to determine the failure of device in TLP measurement is that the leakage current changes by 30%. The devices are measured under PS mode, PD mode, NS mode, and ND mode respectively. The  $I_{t2}$  of all the test devices are recorded in Table 3.7. The TLP I-V curves are also normalized by insertion loss ( $S_{21}$ ) at 20GHz to tell the difference. The  $I_{t2}/|S_{21}|$  of all the test devices are recorded in Table 3.8.

Fig. 3.40. Transmission-line pulsing (TLP) system. [30]

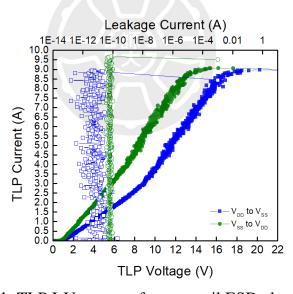

### (1) Power-Rail ESD Clamp Circuit

The power-rail ESD clamp circuit provides ESD current path between  $V_{DD}$  and  $V_{SS}$ . It is composed by an RC inverter as a trigger circuit and a NMOS as a discharging device. The length and width of the NMOS are 0.36  $\mu$ m and 50 $\mu$ m respectively, and the multiple is 60.

During normal operation, the supply voltage rises in several microseconds. The capacitor of RC inverter has enough time to be charged to a high level. Through the inverter, the voltage level of the gate of the NMOS is low and the channel of NMOS will keep off. When ESD stress hitting, the channel of NMOS is turned on by the RC inverter circuit. The parasitic NPN is triggered and turns on to discharge the ESD current from  $V_{DD}$  to  $V_{SS}$ . The parasitic diode inside NMOS also provides the ESD current path from  $V_{SS}$  to  $V_{DD}$ .

As shown in Fig.3.41, the TLP I-V curves of power-rail ESD clamp circuit of test cells are measured. From  $V_{DD}$  to  $V_{SS}$ , the power-rail ESD clamp circuit is triggered at 1.9V, and the  $I_{t2}$  is 8.9A. From  $V_{SS}$  to  $V_{DD}$ , the power-rail ESD clamp circuit is triggered at 0.6V, and the  $I_{t2}$  is 9.7A.

Fig. 3.41. TLP I-V curves of power-rail ESD clamp circuit

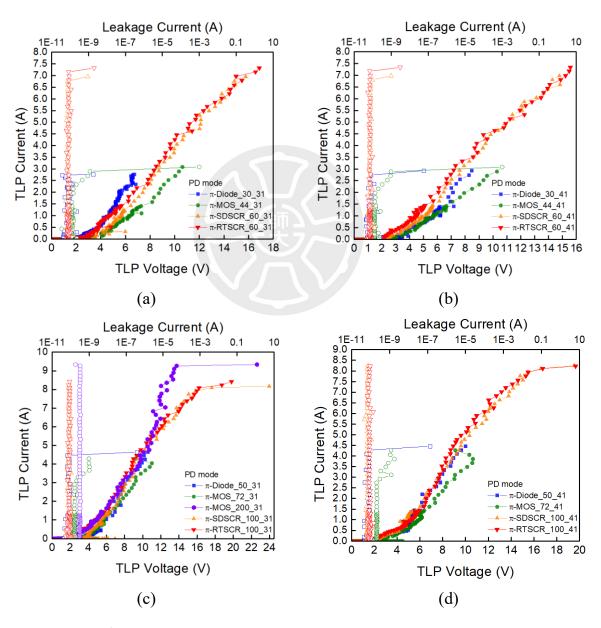

#### (2) PD Mode

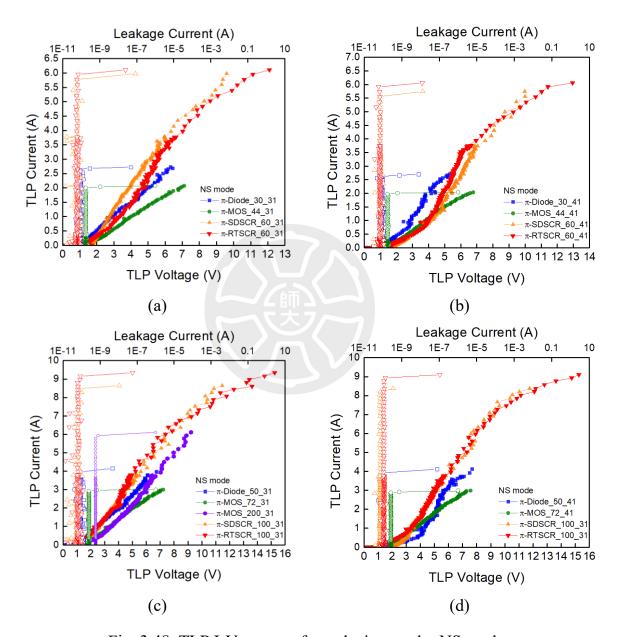

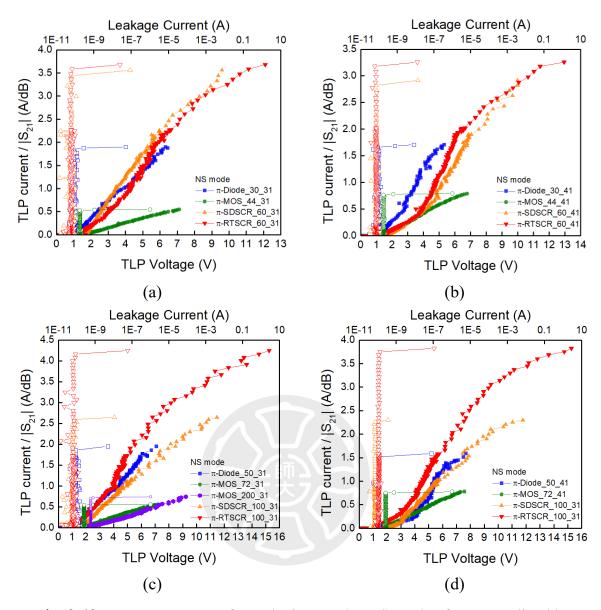

The test circuit discharges ESD current of PD mode through the devices placed from I/O pad to  $V_{DD}$ . The TLP I-V curve of  $\pi$ -diode\_30\_31 is compared with that of  $\pi$ -MOS 44 31,  $\pi$ -SDSCR 60 31 and  $\pi$ -RTSCR 60 31 in Fig. 3.42 (a). The TLP I-V

curve of  $\pi$ -diode\_30\_41 is compared with that of  $\pi$ -MOS\_44\_41,  $\pi$ -SDSCR\_60\_41 and  $\pi$ -RTSCR\_60\_41 in Fig. 3.42 (b). The TLP I-V curve of  $\pi$ -diode\_50\_31 is compared with that of  $\pi$ -MOS\_72\_31,  $\pi$ -MOS\_200\_31,  $\pi$ -SDSCR\_100\_31 and  $\pi$ -RTSCR\_100\_31 in Fig. 3.42 (c). The TLP I-V curve of  $\pi$ -diode\_50\_41 is compared with that of  $\pi$ -MOS\_72\_41,  $\pi$ -SDSCR\_100\_41 and  $\pi$ -RTSCR\_100\_41 in Fig. 3.42 (d). The TLP I-V curves after normalized by insertion loss (S<sub>21</sub>) at 20GHz are shown in Fig. 3.43.

Fig. 3.42. TLP I-V curves of test devices under PD mode

.

Fig. 3.43. TLP I-V curves of test devices under PD mode after normalized by insertion loss at 20GHz.

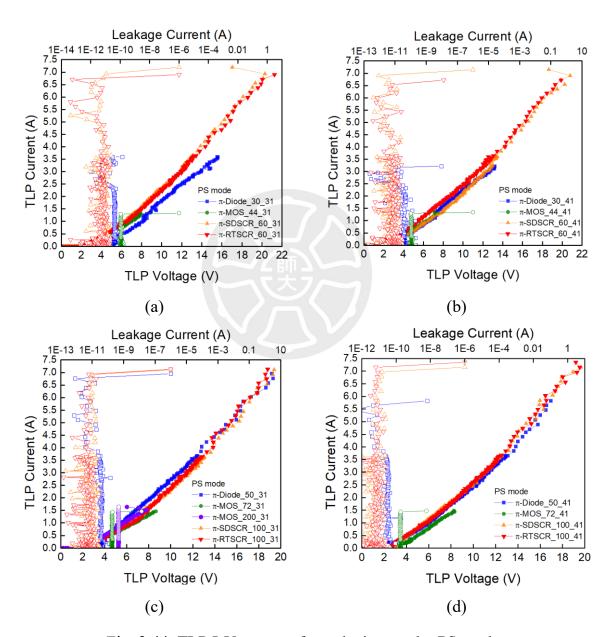

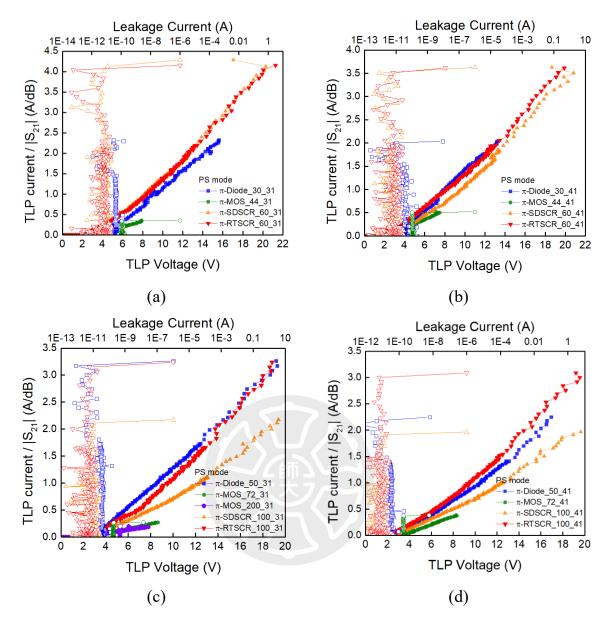

## (3) PS Mode

The test circuit discharges ESD current of PS mode through the devices placed from I/O pad to  $V_{DD}$  in series with the power-rail ESD clamp circuit. The TLP I-V curve of  $\pi$ -diode\_30\_31 is compared with that of  $\pi$ -MOS\_44\_31,  $\pi$ -SDSCR\_60\_31 and  $\pi$ -RTSCR\_60\_31 in Fig. 3.44 (a). The TLP I-V curve of  $\pi$ -diode\_30\_41 is compared with that of  $\pi$ -MOS\_44\_41,  $\pi$ -SDSCR\_60\_41 and  $\pi$ -RTSCR\_60\_41 in Fig. 3.44 (b). The

TLP I-V curve of  $\pi$ -diode\_50\_31 is compared with that of  $\pi$ -MOS\_72\_31,  $\pi$ -MOS\_200\_31,  $\pi$ -SDSCR\_100\_31 and  $\pi$ -RTSCR\_100\_31 in Fig. 3.44 (c). The TLP I-V curve of  $\pi$ -diode\_50\_41 is compared with that of  $\pi$ -MOS\_72\_41,  $\pi$ -SDSCR\_100\_41 and  $\pi$ -RTSCR\_100\_41 in Fig. 3.44 (d). The TLP I-V curves after normalized by insertion loss (S<sub>21</sub>) at 20GHz are shown in Fig. 3.45.

Fig. 3.44. TLP I-V curves of test devices under PS mode.

Fig. 3.45. TLP I-V curves of test devices under PS mode after normalized by insertion loss at 20GHz.

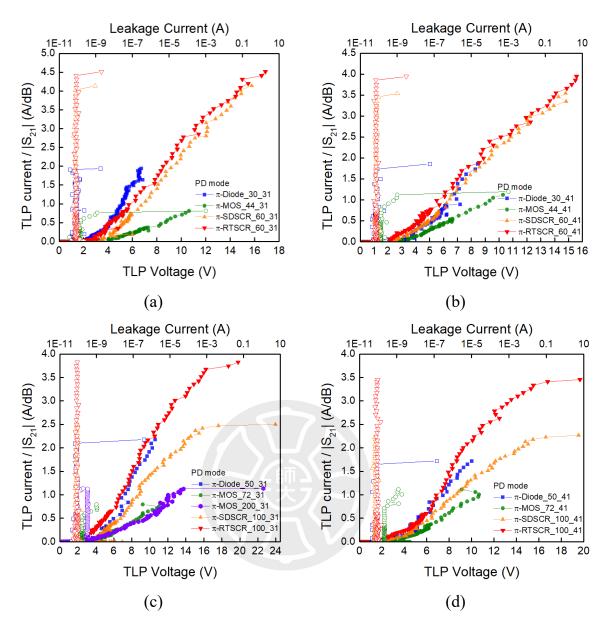

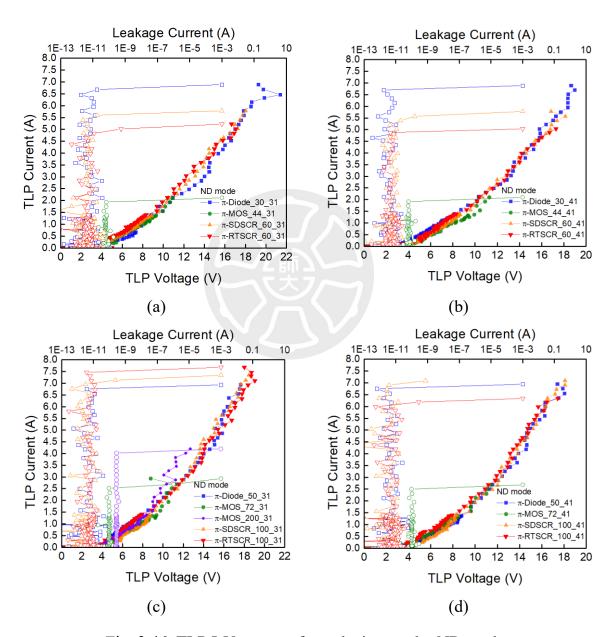

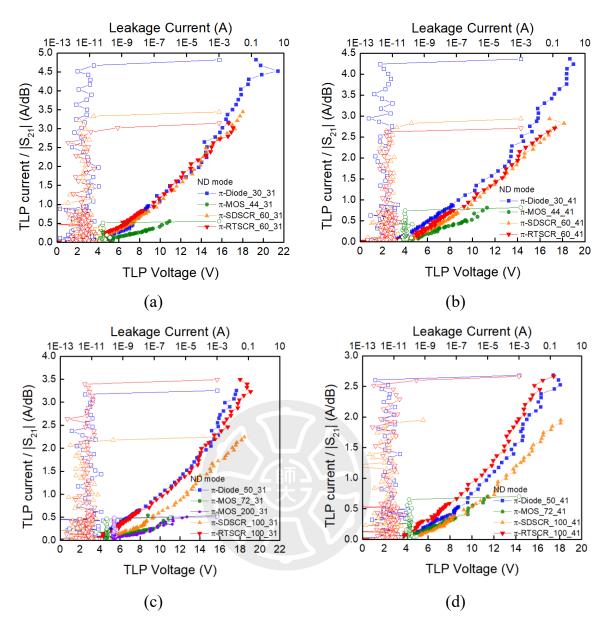

#### (4) ND Mode

The test circuit discharges ESD current under ND mode through the power-rail ESD clamp circuit and devices placed from  $V_{SS}$  to I/O pad. The TLP I-V curve of  $\pi$ -diode\_30\_31 is compared with that of  $\pi$ -MOS\_44\_31,  $\pi$ -SDSCR\_60\_31 and  $\pi$ -RTSCR\_60\_31 in Fig. 3.46 (a). The TLP I-V curve of  $\pi$ -diode\_30\_41 is compared with that of  $\pi$ -MOS\_44\_41,  $\pi$ -SDSCR\_60\_41 and  $\pi$ -RTSCR\_60\_41 in Fig. 3.46 (b). The

TLP I-V curve of  $\pi$ -diode\_50\_31 is compared with that of  $\pi$ -MOS\_72\_31,  $\pi$ -MOS\_200\_31,  $\pi$ -SDSCR\_100\_31 and  $\pi$ -RTSCR\_100\_31 in Fig. 3.46 (c). The TLP I-V curve of  $\pi$ -diode\_50\_41 is compared with that of  $\pi$ -MOS\_72\_41,  $\pi$ -SDSCR\_100\_41 and  $\pi$ -RTSCR\_100\_41 in Fig. 3.46 (d). The TLP I-V curves after normalized by insertion loss (S<sub>21</sub>) at 20GHz are shown in Fig. 3.47.

Fig. 3.46. TLP I-V curves of test devices under ND mode.

Fig. 3.47. TLP I-V curves of test devices under ND mode after normalized by insertion loss at 20GHz.

#### (5) NS Mode

The test circuit discharges ESD current of NS mode through the device placed from  $V_{SS}$  to I/O pad. The TLP I-V curve of  $\pi$ -diode\_30\_31 is compared with that of  $\pi$ -MOS\_44\_31,  $\pi$ -SDSCR\_60\_31 and  $\pi$ -RTSCR\_60\_31 in Fig. 3.48 (a). The TLP I-V curve of  $\pi$ -diode\_30\_41 is compared with that of  $\pi$ -MOS\_44\_41,  $\pi$ -SDSCR\_60\_41 and  $\pi$ -RTSCR\_60\_41 in Fig. 3.48 (b). The TLP I-V curve of  $\pi$ -diode\_50\_31 is compared

with that of  $\pi$ -MOS\_72\_31,  $\pi$ -MOS\_200\_31,  $\pi$ -SDSCR\_100\_31 and  $\pi$ -RTSCR\_100\_31 in Fig. 3.48 (c). The TLP I-V curve of  $\pi$ -diode\_50\_41 is compared with that of  $\pi$ -MOS\_72\_41,  $\pi$ -SDSCR\_100\_41 and  $\pi$ -RTSCR\_100\_41 in Fig. 3.48 (d). The TLP I-V curves after normalized by insertion loss (S<sub>21</sub>) at 20GHz are shown in Fig. 3.49.

Fig. 3.48. TLP I-V curves of test devices under NS mode.

Fig. 3.49. TLP I-V curves of test devices under NS mode after normalized by insertion loss at 20GHz.

Table 3.7. Measured  $I_{t2}$  results

| Call Name      | I <sub>t2</sub> (A) |          |         |         |  |  |

|----------------|---------------------|----------|---------|---------|--|--|

| Cell Name      | PS mode             | PD mode  | NS mode | ND mode |  |  |

| π-diode_30_31  | 3.59                | 2.73     | 2.68    | 6.89    |  |  |

| π-diode_30_41  | 3.17                | 2.74     | 2.70    | 6.89    |  |  |

| π-diode_50_31  | 6.76                | 4.64     | 4.15    | 6.93    |  |  |

| π-diode_50_41  | 5.64                | 4.46     | 3.92    | 6.94    |  |  |

| π-MOS_44_31    | 1.29                | 2.89     | 2.00    | 1.93    |  |  |

| π-MOS_44_41    | 1.30                | 2.89     | 2.00    | 1.91    |  |  |