# 國立臺灣師範大學科技與工程學院電機工程學系 碩士論文

Department of Electrical Engineering

College of Technology and Engineer

National Taiwan Normal University

Master's Thesis

應用於高頻輸入/出端與電源端之靜電放電防護設計 ESD Protection Design for High-Frequency Input/Output Terminal and Power Terminal Application

傅義全

Yi-Quan Fu

指導教授:林群祐 博士

Advisor: Chun-Yu Lin, Ph.D.

中華民國 110 年 10 月 October 2021 應用於高頻輸入/出端與電源端之靜電放電防護設計

學生: 傅義全 指導教授: 林群祐 博士

國立臺灣師範大學電機工程學系碩士班

摘 要

隨著 CMOS 製程越來越先進,電晶體尺寸微縮,使可操作於更高的工作頻率,但會使電晶體對於靜電越來越敏感,靜電放電是影響積體電路可靠度的主要因素,須設計出高耐受度的靜電放電防護電路,避免積體電路遭受靜電轟擊而損壞。

靜電放電防護通常設計於輸入/出端,當應用於高頻積體電路中,須具備較低的寄生電容,否則會影響高頻電路的特性,而傳統防護元件選擇簡單的二極體,但操作頻率越來越高時,造成高頻電路特性大幅衰減,因此本論文提出藉由電阻串並聯方式使二極體產生的負載減少,並採用 CMOS 製程實踐,透過各項量測證實在單位面積下有低的高頻訊號流失和擁有足夠高的靜電放電防護能力。

因靜電也會由電源端進內部電路,所以必須有電源箝制防護電路,而電源箝制防護電路中的觸發機制被用來判斷靜電是否發生,但當內部電路上電的時間常數與靜電相近時,電阻-電容充放電機制會使排放靜電的元件意外導通,造成電源端的訊號極大流失。因此,本論文使用 CMOS 製程實踐現有電源箝制電路,分析不同的靜電放電耐受度測試、正常上電與快速上電時的可行性。

關鍵字:靜電放電、高頻、寄生電容、靜電放電箝位電路、正常上電源、快速上電源

ESD Protection Design for High-Frequency Input/Output Terminal

and Power Terminal Application

Student: Yi-Quan Fu

Advisor: Chun-Yu Lin, Ph.D.

**Department Electrical Engineering**

National Taiwan Normal University

**ABSTRACT**

The manufacturing process becomes more advanced for high-frequency

applications than before. However, the transistor is sensitive to static electricity.

Therefore, it is necessary to design an electrostatic discharge (ESD) protection circuit

with high ESD robustness to prevent the integrated circuit from being damaged by ESD

current bombardment.

The ESD protection device is usually designed at the input/output pad. When the

internal circuits are operated at high frequency, the ESD protection device should have

low parasitic capacitance. Otherwise, the ESD protection device will affect the character

of the high-frequency circuit. Though the simple diodes are chosen as traditional

protection component, they will cause severe signal loss at higher frequency. Therefore,

the thesis proposed the RC-diode ESD protection device that is adopted CMOS process

to reduce signal loss through the resistor series and parallel method. As a result, the RC-

diode protection device has outstanding ESD robustness and low signal loss per unit

$\Pi$

area by various testing.

Because the static electricity will also enter the internal circuit from the power supply terminal, the power-rail ESD clamp circuit is essential. The trigger mechanism in power-rail ESD clamp circuit is used to determine whether the static electricity occurs. However, the time constant of the internal circuit power-on and static electricity is close, the resistor-capacitor inverter mechanism will accidentally trigger the components of discharge current to cause significant power loss at the power supply terminal. Therefore, this thesis has adopted the CMOS process to fabricate present power-rail ESD clamp circuits for internal circuit. These power-rail ESD clamp circuits are analyzed under different testing methods of ESD robustness and discussed for internal circuit of normal and fast power-on feasibility.

Keyword: electrostatic discharge (ESD), high-frequency, parasitic capacitance, power-rail ESD clamp circuit, normal power-on, fast power-on.

#### Acknowledgment

首先,我要感謝我的指導教授林群祐,從大學專題開始一路到研究所這幾年來不厭其煩的教導與協助,並且有良好的學習環境與資源提供我使用,不僅讓我在專業領域上的知識學習很多之外,也不斷鼓勵我參加許多國內外研討會,使我撰寫學術文章的能力大幅提升,還有老師您嚴謹的研究態度與積極處理事情的原則,深深影響了我在面對任何事情時較有效率做好且是做出有水準的作品,再次感謝老師您對我的栽培,我已經準備好邁向人生的下一階段,期許未來可以在電機相關領域有所成就。

謝謝國家晶片中心的協助,讓我可以進行晶片下線與晶片量測;謝謝陽明交通大學電子工程學系,提供儀器設備使我完成許多重要的實驗與分析;也感謝陽明交通大學電子工程學系的柯明道教授與國立臺灣科技大學電子工程學系的張勝良教授,撥冗前來我的碩士論文口試,給予我許多寶貴的建議,使論文內容更加完整與充裕。

還有,也要謝謝研究群中已經畢業的每位學長姐,彥璉、偉豪、冠儀、國倫、孟霆、鈺凱、玉瑄、柏維、俊宇,以及同屆一起共患難同進退的子鈞,從大學到研究所曾經的陪伴、討論專業的問題、傳授專業的相關知識,讓我在研究過程中成功克服一個個難題與困惑,並且順利完成,還有學弟妹們健群、俊捷、庭炘、俊成、群榮、洋守、欣慈、湘縈使得整個實驗室成為一個溫馨的大家庭。

最後,感謝林芫醇小姐在研究所一路上的支持與幫助,當我遇到挫折時都會 適時的給予建議與鼓勵,使我更加有動力與信心完成。我也要感謝我的親愛的家 人們,父親傅啟明先生、母親黃鈺臻女士、哥哥傅鼎成先生與姊姊傅琬婷女士, 不僅不斷給予滿滿的愛與支持外,求學過程中讓我也無虞地致力研究,未來我會 更加努力不會辜負你們的期待。

> 傅義全 謹誌於師大 中華民國一一零年十月

## **Contents**

| Chapter 1 Introduction                                                  |

|-------------------------------------------------------------------------|

| 1.1 Motivation                                                          |

| 1.2 Background of ESD                                                   |

| 1.3 Component-Level Test Standards of ESD                               |

| 1.3.1 Human-Body Model (HBM)                                            |

| 1.3.2 Charged-Device Model (CDM)                                        |

| 1.4 Consideration of Designing Whole-Chip ESD Protection Circuits       |

| 1.4.1 ESD Protection Design Window                                      |

| 1.5 ESD Protection Components for High-Frequency Application            |

| 1.5.1 Dual Diodes [16]                                                  |

| 1.5.2 Dual Stacked Diodes [17]                                          |

| 1.5.3 LC Tanks [18]1                                                    |

| 1.6 Power-Rail ESD Clamp Circuits                                       |

| 1.6.1 Power-Rail ESD Circuit with Resistor-Capacitor Inverter Mechanism |

| [19]1                                                                   |

| 1.6.2 Power-Rail ESD Circuit with Diode-Trigger Mechanism [20]1         |

| 1.6.3 Power-Rail ESD Circuit with Positive-Feedback Mechanism [21]1     |

| 1.6.4 Power-Rail ESD Circuit with Double-Detector Mechanism [22]1       |

| 1.7 Organization of This Dissertation                                   |

| Chapter 2 Resistance-Capacitance Diode for High-Frequency Application1  |

| 2.1 Traditional Dual-Diode Design                                       |

| 2.2 Traditional LC-Tank Design                                          |

| 2.3 Proposed RC-Diode Design                                            |

|     | 2.4 Measurement Results                                        | 35 |

|-----|----------------------------------------------------------------|----|

|     | 2.4.1 High-Frequency Performance                               | 36 |

|     | 2.4.2 Transmission-line pulsing (TLP) Measurement              | 41 |

|     | 2.4.3 HBM Robustness                                           | 48 |

|     | 2.4.4 Very-Fast Transmission-line pulsing (VF-TLP) Measurement | 50 |

|     | 2.5 Comparison and Discussion of This Test Chip                | 52 |

|     | 2.6 Comparison of Proposed RC Diode and Literature             | 58 |

|     | 2.7 Summary                                                    | 59 |

| Cha | apter 3 ESD Clamp Circuits for Power Terminal Application      | 60 |

|     | 3.1 Power-Rail ESD Clamp Circuits                              | 60 |

|     | 3.1.1 Resistor-Capacitor Inverter Mechanism [19]               | 61 |

|     | 3.1.2 Diode-Trigger Mechanism [20]                             | 63 |

|     | 3.1.3 Positive-Feedback Mechanism [21]                         | 65 |

|     | 3.1.4 Double-Detector Mechanism [22]                           | 68 |

|     | 3.2 Simulation Results                                         | 70 |

|     | 3.2.1 ESD-like waveform condition                              | 70 |

|     | 3.2.2 Normal Power-on Condition                                | 75 |

|     | 3.2.3 Fast Power-on Condition                                  | 77 |

|     | 3.3 Measurement Methods and Results                            | 79 |

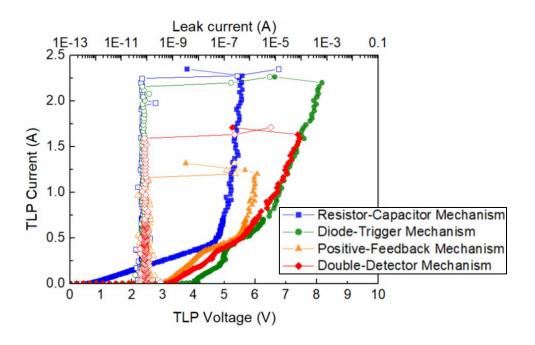

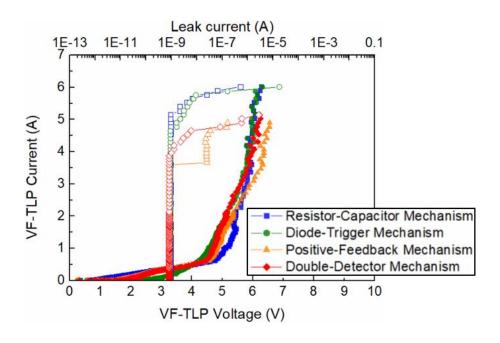

|     | 3.3.1 Transmission-line pulsing (TLP) Measurement              | 80 |

|     | 3.3.2 Very-Fast Transmission-line pulsing (VF-TLP) Measurement | 81 |

|     | 3.3.3 ESD Robustness                                           | 82 |

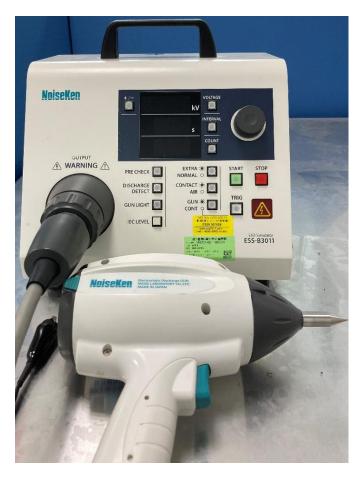

|     | 3.3.4 Power Loss under Fast Power-on Event                     | 84 |

|     | 3.4 Comparison of This Test Chip                               | 85 |

|     | 3.5 Discussion of This Test Chip                               | 87 |

|     | 3.6 Summary                                                    | 90 |

| Chapter 4 Conclusion and Future Work |    |

|--------------------------------------|----|

| 4.1 Conclusion                       | 91 |

| 4.2 Future Work                      | 93 |

| Reference                            | 96 |

## **List of Tables**

| Table 1.1. The protection level classification of HBM                              | 3   |

|------------------------------------------------------------------------------------|-----|

| Table 1.2. The protection level classification of CDM.                             | 4   |

| Table 2.1. The parameter of ESD protection circuit with dual diode                 | .22 |

| Table 2.2. The parameter of ESD protection circuit with LC tank                    | .27 |

| Table 2.3. The parameter of ESD protection circuit with RC diode                   | .34 |

| Table 2.4. The measured results of S-parameter.                                    | .40 |

| Table 2.5. The measured results of secondary breakdown current (I <sub>t2</sub> )  | .47 |

| Table 2.6. The HBM test results.                                                   | .49 |

| Table 2.7. The comparison of traditional and proposed designs under PS mode        | .52 |

| Table 2.8. The comparison of traditional and proposed designs under PD mode        | .53 |

| Table 2.9. The comparison of traditional and proposed designs under NS mode        | .54 |

| Table 2.10. The comparison of traditional and proposed designs under ND mode       | .55 |

| Table 2.11. The comparison results of traditional and proposed designs             | .57 |

| Table 2.12. The comparison of ESD protection design for high-frequency application | 1.  |

|                                                                                    | .58 |

| Table 3.1. The parameter of power-rail ESD clamp circuit with resistor-capacitor   |     |

| inverter mechanism.                                                                | .62 |

| Table 3.2. The parameter of power-rail ESD clamp circuit with diode-trigger        |     |

| mechanism.                                                                         | .64 |

| Table 3.3. The parameter of power-rail ESD clamp circuit with positive-feedback    |     |

| mechanism.                                                                         | .67 |

| Table 3.4. The parameter of power-rail ESD clamp circuit with double-detector      |     |

| mechanism.                                                                         | .69 |

| Table 3.5. The test results of ESD robustness.                                     | .83 |

| Table 3.6. | The comparison | of these power-rail | ESD clamp | circuits86 |

|------------|----------------|---------------------|-----------|------------|

|            |                | F                   |           |            |

# **List of Figures**

| Fig. 1.1. The equivalent circuit of HBM.                                                         | 3         |

|--------------------------------------------------------------------------------------------------|-----------|

| Fig. 1.2. The equivalent circuit of CDM.                                                         | 4         |

| Fig. 1.3. Typical whole-chip ESD protection design.                                              | 5         |

| Fig. 1.4. ESD protection design window.                                                          | 6         |

| Fig. 1.5. RF signal loss at RF <sub>IN</sub> /RF <sub>OUT</sub> pads with ESD protection devices | 7         |

| Fig. 1.6. ESD Protection design with dual diodes.                                                | 8         |

| Fig. 1.7. ESD Protection design with dual stacked diodes                                         | 9         |

| Fig. 1.8. ESD Protection design with LC tanks.                                                   | 10        |

| Fig. 1.9. Power-rail ESD clamp circuit with transient mechanism circuit                          | 12        |

| Fig. 1.10. Power-rail ESD clamp circuit with resistor-capacitor inverter                         | 13        |

| Fig. 1.11. Power-rail ESD clamp circuit with diode trigger.                                      | 14        |

| Fig. 1.12. Power-rail ESD clamp circuit with positive feedback                                   | 15        |

| Fig. 1.13. Power-rail ESD clamp circuit with double detector                                     | 16        |

| Fig. 2.1. The whole-chip ESD protection circuit with traditional dual diode                      | 19        |

| Fig. 2.2. The cross-sectional view of the (a) P-type and (b) N-type diode                        | 20        |

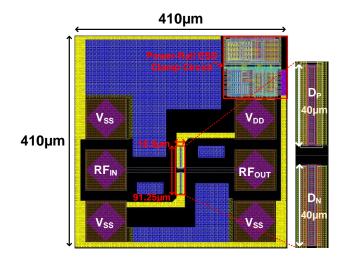

| Fig. 2.3. The layout top views of Dual-Diode_20µm                                                | 21        |

| Fig. 2.4. The layout top views of Dual-Diode_40µm                                                | 21        |

| Fig. 2.5. The layout top views of Dual-Diode_60µm                                                | 21        |

| Fig. 2.6. The whole-chip ESD protection circuit with traditional LC tank                         | 24        |

| Fig. 2.7. The cross-sectional view of the (a) P-type diode with L <sub>P</sub> and (b) N-type    | ype diode |

| with L <sub>N</sub> .                                                                            | 25        |

| Fig. 2.8. The layout top views of LC-tank_20µm                                                   | 26        |

| Fig. 2.9. The layout top views of LC-tank_40µm                                                   | 26        |

| Fig. 2.10. The layout ton views of LC-tank. 60um                                                 | 26        |

| Fig. 2.11. The whole-chip ESD protection circuit with proposed RC diode                        | 29 |

|------------------------------------------------------------------------------------------------|----|

| Fig. 2.12. The calculation results of the $R_{P(N)}$ and the parasitic capacitance at 10GHz    | z, |

| 14GHz and 20GHz.                                                                               | 30 |

| Fig. 2.13. The cross-sectional view of the (a) P-type diode with R <sub>P</sub> and (b) N-type |    |

| diode with R <sub>N</sub> .                                                                    | 31 |

| Fig. 2.14. The layout top views of RC-Diode_ $100\Omega_20\mu m$ .                             | 32 |

| Fig. 2.15. The layout top views of RC-Diode_ $100\Omega_40\mu m$ .                             | 32 |

| Fig. 2.16. The layout top views of RC-Diode_ $100\Omega_60\mu m$ .                             | 32 |

| Fig. 2.17. The layout top views of RC-Diode_ $200\Omega_20\mu m$ .                             | 33 |

| Fig. 2.18. The layout top views of RC-Diode_ $200\Omega_40\mu m$ .                             | 33 |

| Fig. 2.19. The layout top views of RC-Diode_ $200\Omega_60\mu m$ .                             | 33 |

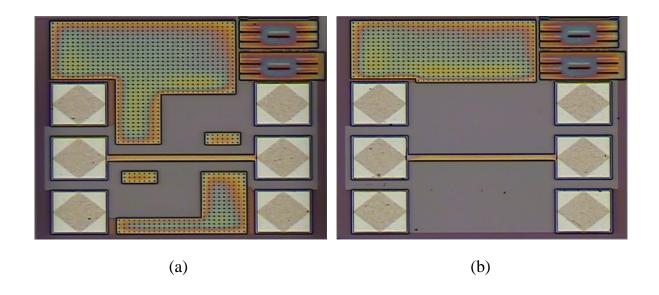

| Fig. 2.20. The chip micrograph of all ESD protection circuits.                                 | 35 |

| Fig. 2.21. The picture of high-frequency measurement system [23]                               | 36 |

| Fig. 2.22. The de-embedding pad for test circuit of (a) dual diode, RC diode and (b)           | )  |

| LC tank.                                                                                       | 37 |

| Fig. 2.23. Measured S-parameters of Dual-Diode_20μm, LC-tank_20μm, RC-                         |    |

| Diode_ $100\Omega_20\mu m$ and RC-Diode_ $200\Omega_20\mu m$                                   | 37 |

| Fig. 2.24. Measured S-parameters of Dual-Diode_40μm, LC-tank_40μm, RC-                         |    |

| Diode_ $100\Omega_40\mu m$ and RC-Diode_ $200\Omega_40\mu m$                                   | 38 |

| Fig. 2.25. Measured S-parameters of Dual-Diode_60μm, LC-tank_60μm, RC-                         |    |

| Diode_ $100\Omega_60\mu m$ and RC-Diode_ $200\Omega_60\mu m$                                   | 38 |

| Fig. 2.26. The picture of transmission-line pulse (TLP) measurement system                     | 41 |

| Fig. 2.27. The TLP I-V curves of traditional and proposed designs under PS mode                | 42 |

| Fig. 2.28. The TLP I-V curves of traditional and proposed designs under PD mode.               | 43 |

| Fig. 2.29. The TLP I-V curves of traditional and proposed designs under NS mode.               | 44 |

| Fig. 2.30. The TLP I-V curves of traditional and proposed designs under ND mode.               | 45 |

| Fig. 2.31. The TLP I-V curves of power-rail ESD clamp circuit under (a) $V_{DD}$ to $V_{SS}$          |

|-------------------------------------------------------------------------------------------------------|

| and (b) $V_{SS}$ to $V_{DD}$ .                                                                        |

| Fig. 2.32. The picture of HBM tester.                                                                 |

| Fig. 2.33. The very-fast transmission-line pulse (VF-TLP) measured system [26]50                      |

| Fig. 2.34. The VF-TLP I-V curves and transient waveform at 3A of traditional and                      |

| proposed designs under PD mode                                                                        |

| Fig. 3.1. The power-rail ESD clamp with resistor-capacitor inverter mechanism61                       |

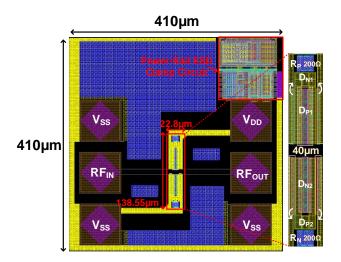

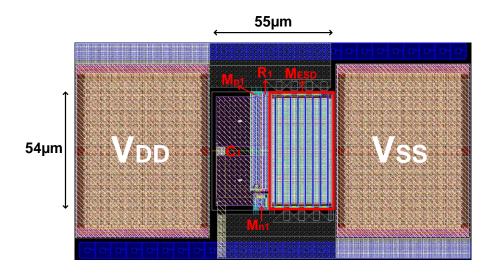

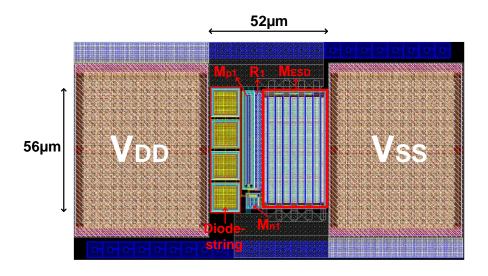

| Fig. 3.2. The layout top view of resistor-capacitor inverter mechanism                                |

| Fig. 3.3. The power-rail ESD clamp with diode-trigger mechanism                                       |

| Fig. 3.4. The layout top view of diode-trigger mechanism.                                             |

| Fig. 3.5. The power-rail ESD clamp with positive-feedback mechanism66                                 |

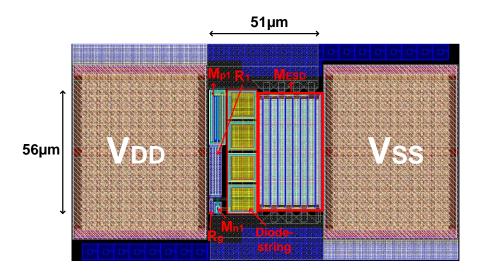

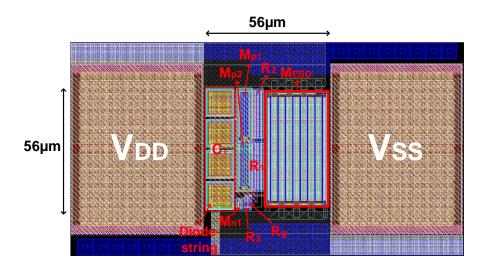

| Fig. 3.6. The layout top views of positive-feedback mechanism                                         |

| Fig. 3.7. The power-rail ESD clamp with double-detector mechanism68                                   |

| Fig. 3.8. The layout top views of double-detector mechanism                                           |

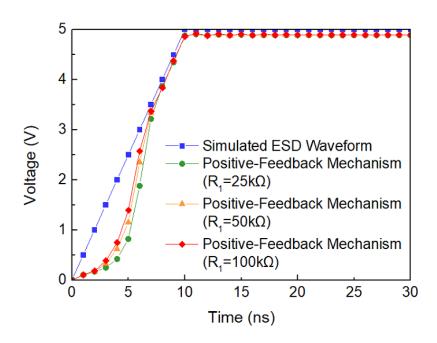

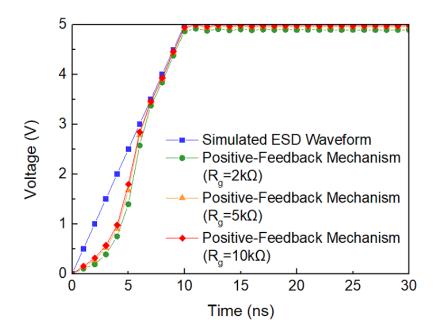

| Fig. 3.9. The simulated result of the $V_{g\_PF}$ with three different resistor ( $R_1$ ) value under |

| ESD stress event. 72                                                                                  |

| Fig. 3.10. The simulated result of the $V_{g\_PF}$ with three different resistor ( $R_g$ ) value      |

| under ESD stress event                                                                                |

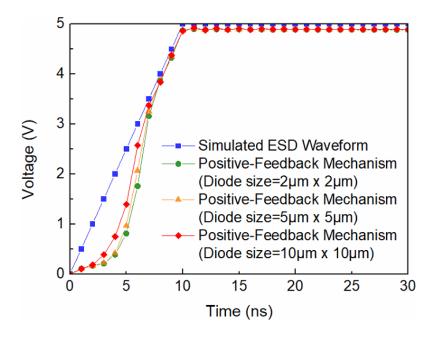

| Fig. 3.11. The simulated result of the $V_{g\_PF}$ with three different diode sizes under ESD         |

| stress event                                                                                          |

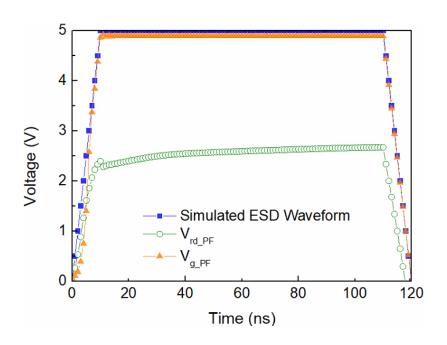

| Fig. 3.12. Each node voltage level of the positive-feedback mechanism power-rail                      |

| ESD clamp circuit under ESD stress event74                                                            |

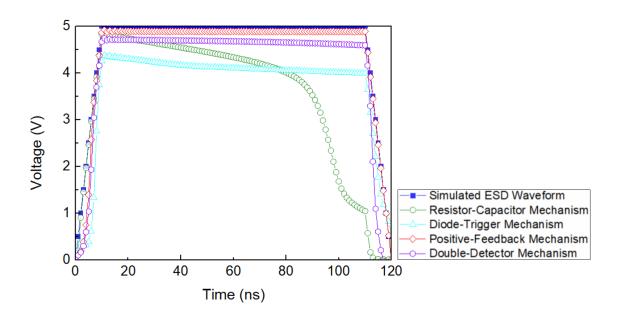

| Fig. 3.13. The voltage level of these power-rail ESD clamp circuit on the gate of $M_{\text{ESD}}$    |

| under ESD stress event74                                                                              |

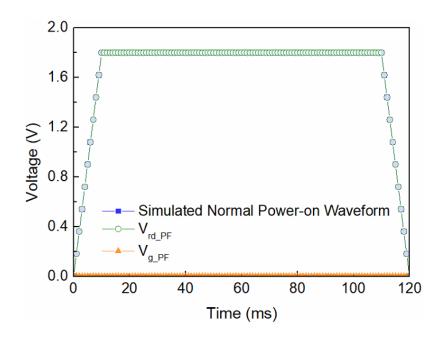

| Fig. 3.14. Each node voltage level of the positive-feedback mechanism power-rail                      |

| FSD clamp circuit under normal power-on event                                                         |

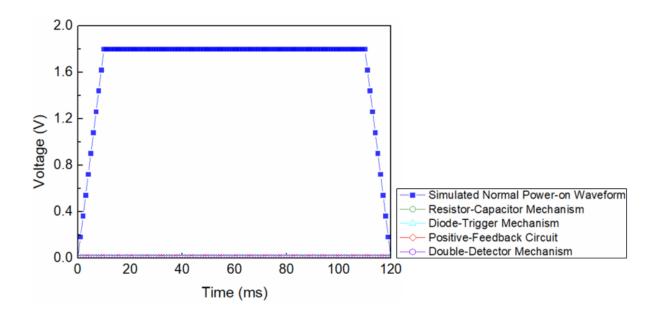

| Fig. 3.15. The voltage level of these power-rail ESD clamp circuit on the gate of M <sub>ESD</sub>            |

|---------------------------------------------------------------------------------------------------------------|

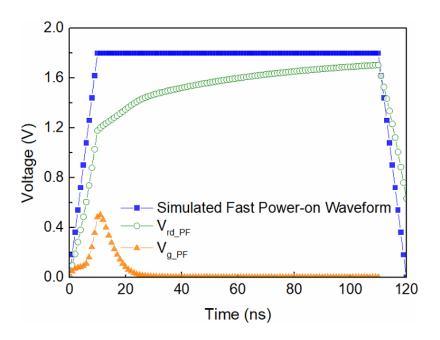

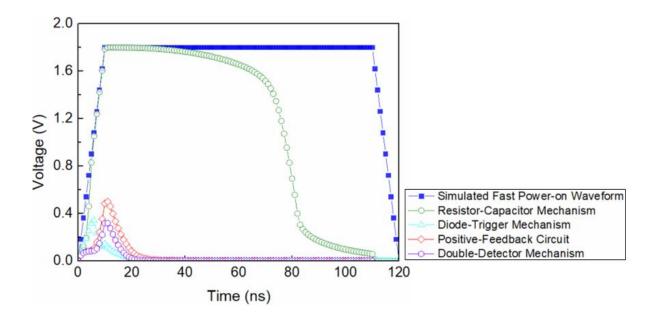

| under normal power-on event                                                                                   |

| Fig. 3.16. Each node voltage level of the positive-feedback mechanism power-rail                              |

| ESD clamp circuit under fast power-on event                                                                   |

| Fig. 3.17. The voltage level of these power-rail ESD clamp circuit on the gate of $M_{\text{ESD}}$            |

| under fast power-on event                                                                                     |

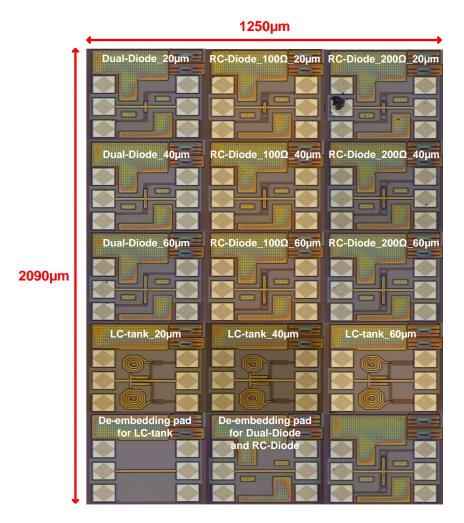

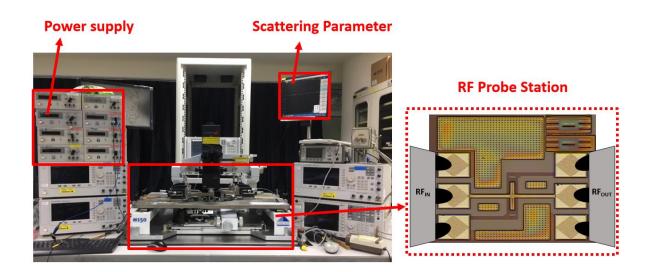

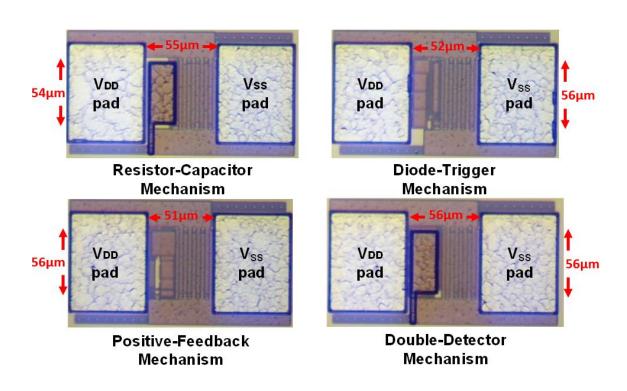

| Fig. 3.18. The chip micrograph of all power-rail ESD clamp circuits79                                         |

| Fig. 3.19. The TLP I-V curves of these power-rail ESD clamp circuits80                                        |

| Fig. 3.20. The VF-TLP I-V curves of these power-rail ESD clamp circuits81                                     |

| Fig. 3.21. The ESD simulator ESS-B3011 measurement system                                                     |

| Fig. 3.22. The measured voltage of power-rail ESD clamp circuits under fast power-on                          |

| event                                                                                                         |

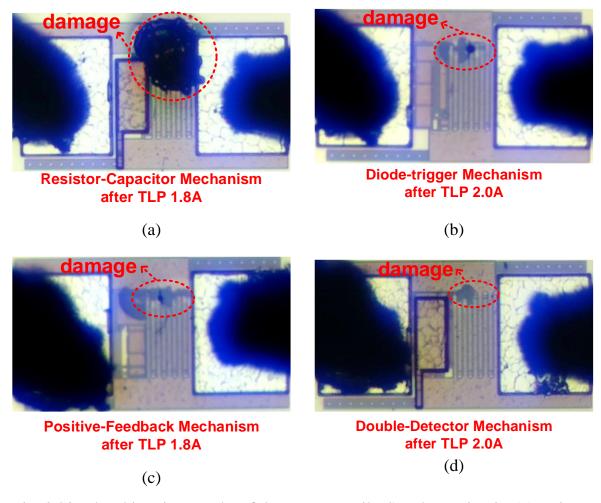

| Fig. 3.23. The chip micrographs of these power-rail ESD clamp circuits (a) resistor-                          |

| capacitor mechanism, (b) diode-trigger mechanism, (c) positive-feedback                                       |

| mechanism and (d) double-detector mechanism with $M_{\text{ESD}}$ after the TLP test.                         |

| 88                                                                                                            |

| Fig. 3.24. The power-rail ESD clamp of positive-feedback mechanism with clamping                              |

| diodes string89                                                                                               |

| Fig. 4.1. The whole-chip ESD protection design with traditional dual diode and                                |

| positive-feedback ESD transient mechanism. 94                                                                 |

| Fig. 4.2. The whole-chip ESD protection design with proposed RC diode and positive-                           |

| feedback ESD transient mechanism94                                                                            |

| Fig. 4.3. Simulated S-parameter of traditional dual diode and proposed RC diode95                             |

| Fig. 4.4. The simulated voltage level of $V_{g\_Dual\ Diode}$ and $V_{g\_RC\ Diode}$ on the gate of $M_{ESD}$ |

| under power-on event95                                                                                        |

| Fig. 4.5. The simulated voltage level of $V_{g\_Dual\ Diode}$ and $V_{g\_RC\ Diode}$ on the gate of $M_{ESD}$ |

| under ESD stress event | 95 |

|------------------------|----|

|------------------------|----|

## Chapter 1

#### Introduction

#### 1.1 Motivation

As semiconductor technology advances to the nanometer regime, the short channel length and shallow junction make the transistor achieve high frequency and low power consumption [1]. Unfortunately, the electrostatic discharge (ESD) protection ability has become one of the critical concerns on the reliability of integrated circuit products [2], [3]. With the development of electronic communication products, CMOS technologies have been used to implement radio-frequency integrated circuits (RFICs). However, static electricity usually occurs in input/output terminals. ESD protection circuits are essential to prevent overvoltage problem [4], [5]. When operating frequency increases gradually, the ESD protection device can cause significant signal loss [6]. In order to avoid attenuating the high-frequency characteristics, the parasitic capacitance effects must be considered for different applications such as low-noise amplifier (LNA) circuit and RF power amplifier (PA) circuit [7].

Besides, to keep an excellent whole-chip ESD protection for internal circuits, it is also required to design the power-rail ESD clamp circuits for power location. This ESD clamp circuit should not be accidentally turned on when the internal circuit is work, and it should be operated when static electricity occurs [8].

Therefore, the ESD protection design is a severe challenge for nanoscale complementary metal-oxide-semiconductor (CMOS) technology. The thesis proposes ESD protection devices for high-frequency circuits and studies power-rail ESD clamp circuits for various situations.

## 1.2 Background of ESD

When the electric potential of the objects is unbalanced and contacted on the surface, a phenomenon happens that the electric charge transfers between two different objects. ESD current generates high current about several amperes (A) in nanoseconds immediately. With the advantage of nanoscale CMOS technology, such as scaling-down feature size, improving circuit performance and reliability of IC products have been the ultimate task in the IC industry. However, the electronic equipment and semiconductor devices can cause permanent damage because the ESD owns powerful electricity. When the IC is affected by the ESD event, the temperature of the IC rises to lead to metal and silicon burned out. So, the integrated circuits are susceptible to ESD stress, and ESD protection circuits play an important role in solving high ESD current issues [9].

## 1.3 Component-Level Test Standards of ESD

Nowadays, before commercial electronic products are exhibited, they must be tested for ESD tolerance. Therefore, manufacturers are necessary to comply with the standard [10], [12]. Some related organizations, such as Joint Electron Device Engineering Council (JEDEC), Automotive Electronics Council (AEC), and US Military Standard (MIL-STD), have constructed standards for the ESD tests. According to the different discharge methods of ESD, component-level tests include Human-Body Model (HBM), Machine Model (MM), and Charged-Device Model (CDM). Since the HBM test and the MM test have a positive correlation, the MM has not attended in recent years. The following is equivalent circuit diagram and detailed description of HBM and CDM.

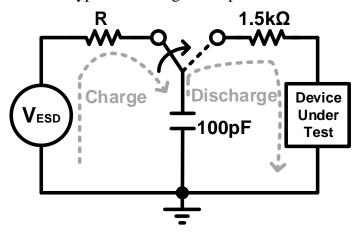

#### 1.3.1 Human-Body Model (HBM)

The model of HBM is shown in Fig. 1.1. The equivalent circuit consists of 100pF capacitor and  $1.5k\Omega$  resistor. During the HBM test, the 100pF capacitor will be charged and then discharge through a  $1.5k\Omega$  resistor into the device under test. The standard simulates the human body rubs against the ground, and it causes static electricity storage on the human body. Then, the body comes into contact with the device, and there will be a discharge path and risk of damage to it. The ANSI/ESD STM5.1 of the ESD Association classifies three types according to the protection level in Table 1.1 [10].

Fig. 1.1. The equivalent circuit of HBM.

Table 1.1. The protection level classification of HBM.

| Class | Voltage Range  |

|-------|----------------|

| 0     | 250V           |

| 1A    | 250V to 500V   |

| 1B    | 500V to 1000V  |

| 1C    | 1000V to 2000V |

| 2     | 2000V to 4000V |

| 3A    | 4000V to 8000V |

| 3B    | 8000V          |

#### 1.3.2 Charged-Device Model (CDM)

The integrated circuits are rubbed to generate static electricity during the manufacturing process and transportation. Once an external ground touches the pin of the IC, the stored charge of the IC will be discharged from the inside of the IC to the outside ground [11]. The model of CDM is shown in Fig. 1.2. The CDM event is more difficult to reproduce through a tester than the HBM and MM events. The ANSI/ESD STM5.3.1 of ESD Association is classified based on the ESD protection level in Table 1.2 [12].

Fig. 1.2. The equivalent circuit of CDM.

Table 1.2. The protection level classification of CDM.

| Class | Voltage Range  |

|-------|----------------|

| C1    | 150V           |

| C2    | 150V to 250V   |

| C3    | 250V to 500V   |

| C4    | 500V to 1000V  |

| C5    | 1000V to 1500V |

| C6    | 1500V to 2000V |

| C7    | 2000V          |

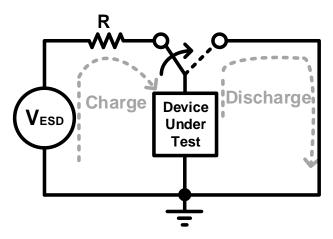

## 1.4 Consideration of Designing Whole-Chip ESD Protection Circuits

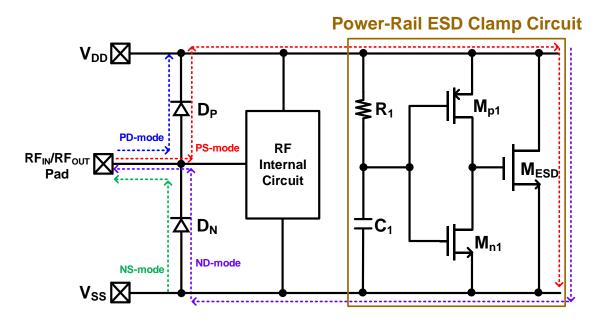

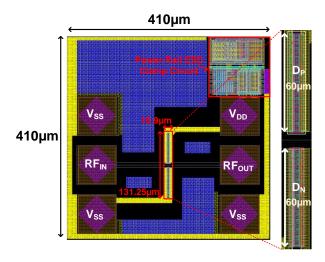

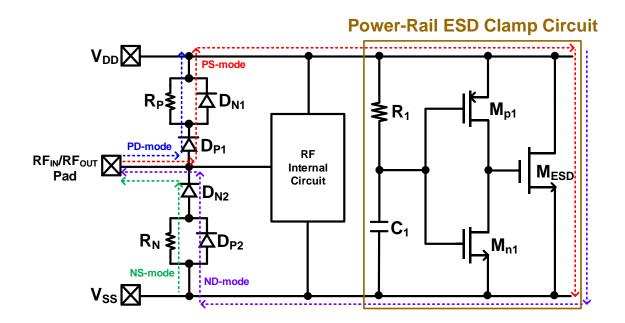

Electrostatic discharge (ESD) protection circuit is mainly used to prevent external ESD stress for IC products. Because the pins of integrate circuits are quickly struck by external static electricity, the ESD protection circuit is placed around the input and output (I/O) pads to discharge the ESD current. There are four discharge path such as positive I/O-to-V<sub>SS</sub> (PS-mode), positive I/O-to-V<sub>DD</sub> (PD-mode), negative I/O-to-V<sub>SS</sub> (NS-mode), and negative I/O-to-V<sub>DD</sub> (ND-mode). The power bus lines are also pretty crucial for overall ESD immunity. Therefore, the power-rail ESD clamp circuit between V<sub>DD</sub> and V<sub>SS</sub> effectively is used to provide an ESD discharge path before ESD current flows internal circuit. As noted above, the traditional ESD protection architecture will be detailed to introduce in the next section. The typical whole-chip ESD protection proposal is demonstrated with the power-rail ESD clamp circuit in Fig. 1.3 [13].

Fig. 1.3. Typical whole-chip ESD protection design.

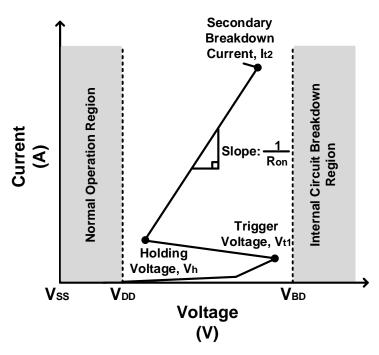

#### 1.4.1 ESD Protection Design Window

When the ESD protection circuit is designed, it is essential to realize the working specification. Therefore, the design window of the ESD protection circuit is established in Fig. 1.4. The internal circuit operates typically between the power supply voltage  $(V_{DD})$  and ground  $(V_{SS})$ , and the boundaries of the ESD protection circuit must turn on between  $V_{DD}$  and gate-oxide breakdown voltage  $(V_{BD})$ . Besides, the trigger voltage  $(V_{t1})$  of protection circuit must be lower than the breakdown voltage. Otherwise, the internal circuit causes failure by ESD current before the protection circuit is operated. Some previous protection circuits have a snapback phenomenon. The holding voltage  $(V_h)$  must be higher than  $V_{DD}$  to avoid occurring latch-up. The turn-on resistance  $(R_{on})$  of the protection circuit will expect to minimize power accumulation. Finally, secondary breakdown current  $(I_{t2})$  means that maximum ESD current the protection circuit can withstand [14].

Fig. 1.4. ESD protection design window.

## 1.5 ESD Protection Components for High-Frequency Application

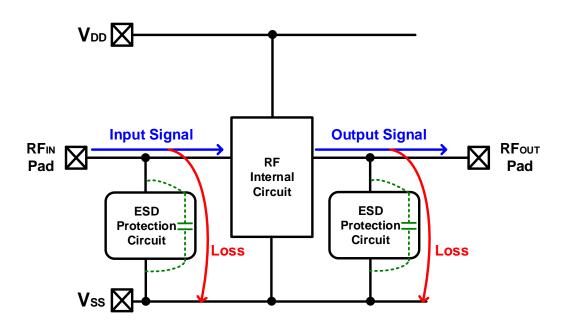

In recent years, commercial mobile and wireless applications develop fast, which leads to operating frequencies increase. The RF circuits are susceptible to ESD in CMOS technologies that causes circuits failure. As shown in Fig. 1.5, the ESD protection circuits are connected to the RF<sub>IN</sub> pad and RF<sub>OUT</sub> pad against ESD damages. However, the additional ESD protection circuit makes the performance of RF internal circuits attenuate. Because the ESD protection circuit has parasitic capacitance, parts of the RF signal are transferred to the ground (Vss) at high frequency. Moreover, the parasitic capacitance also changes the input matching network condition. Consequently, designing an ESD protection device needs special design consideration [15]. The following is introduction that common ESD protection circuits apply to high frequency.

Fig. 1.5. RF signal loss at RF<sub>IN</sub>/RF<sub>OUT</sub> pads with ESD protection devices.

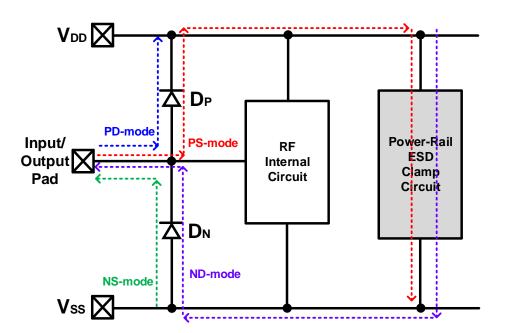

#### **1.5.1 Dual Diodes [16]**

The forward-biased diodes play good capabilities of ESD protection. As shown in Fig. 1.6, it is double-diode topology that consists of P-type diode ( $D_P$ ) and N-type diode ( $D_N$ ). In addition, the power-rail ESD clamp circuit assists in preventing ESD current to RF internal circuit. Therefore, under positive static electricity occurs at input or output pad with grounded  $V_{DD}$ , ESD current is discharged through the P-type diode (PD-mode). On the other hand, when negative static electricity emerges at input or output pad with grounded  $V_{SS}$ , the N-type diode provides a discharge path (NS-mode). Furthermore, ESD current is discharged from the input or output pad through a P-type diode and power-rail ESD clamp circuit to  $V_{SS}$  (PS-mode). Similarly, ESD current flows path from the  $V_{DD}$  through power-rail ESD clamp circuit and N-type diode to input or output pad (ND-mode). However, this structure is suitable for small ESD robustness level because the dimension of diode affects the performance of RF internal circuit.

Fig. 1.6. ESD Protection design with dual diodes.

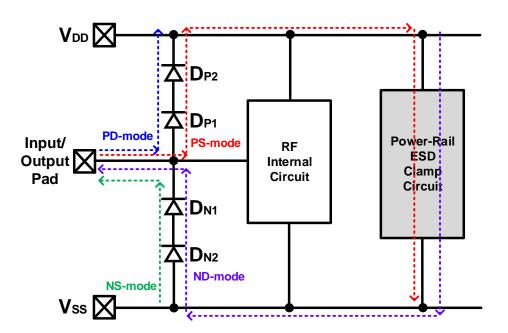

#### 1.5.2 Dual Stacked Diodes [17]

In order to reduce the parasitic capacitance of ESD protection devices without sacrificing ESD tolerance level, the ESD protection circuit is presented by stacked configuration. As a result, the equivalent parasitic capacitance theoretically becomes only half of each ESD protection device. As shown in Fig. 1.7, the two P-type diodes  $(D_{P1} \text{ and } D_{P2})$  are placed between the input or output pad and  $V_{DD}$  in series. The two N-type diodes  $(D_{N1} \text{ and } D_{N2})$  are similarly placed between  $V_{SS}$  and input or output pad in series. With a power-rail ESD clamp circuit, the whole discharge paths are the same as those of the above dual-diodes structure. The architecture leads to more significant parasitic capacitance reduction. However, the diodes cannot be stacked unlimited because this technique can increase the turn-on resistance  $(R_{on})$  and trigger voltage  $(V_{t1})$  of the ESD protection circuit. If the ESD protection circuit cannot turn on in time, the RF internal circuit may be burned out by static electricity.

Fig. 1.7. ESD Protection design with dual stacked diodes.

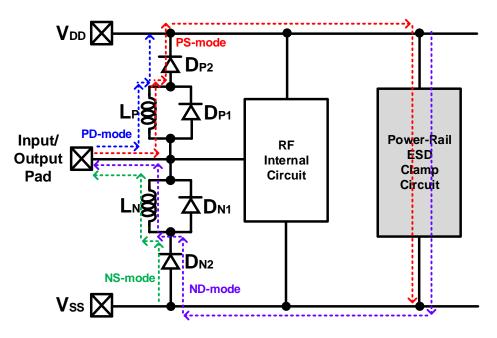

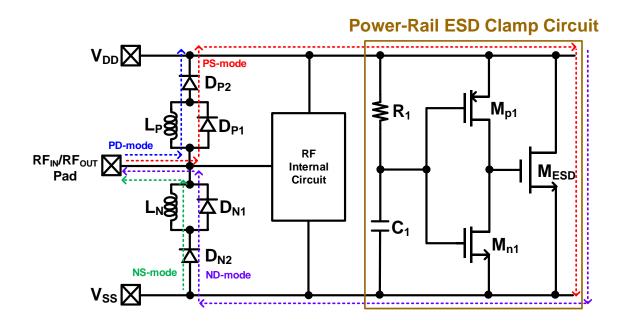

#### 1.5.3 LC Tanks [18]

As shown in Fig. 1.8, the ESD protection circuit is placed in the input or output pad. The LC-tanks ESD protection circuit is consisted of the inductor ( $L_P$  and  $L_N$ ), the parasitic capacitance of the diode ( $D_{P1}$  and  $D_{N1}$ ), and the ESD diode ( $D_{P2}$  and  $D_{N2}$ ). Adding a power-rail ESD clamp circuit forms a whole-chip ESD protection circuit. The technique reduces the parasitic capacitance by using LC parallel resonator theorem. At the resonant frequency, the ESD protection circuit makes signal loss is ideally zero, which means the equivalent parasitic capacitance is zero. Furthermore, the inductor can mitigate the impact on the RF internal circuit and provide an ESD protection device. Nevertheless, the LC-tanks ESD protection circuit applies to commercial products that will cause higher costs because the inductor occupies a more extensive layout area than dual-diode architecture and dual-stacked diodes architecture.

Fig. 1.8. ESD Protection design with LC tanks.

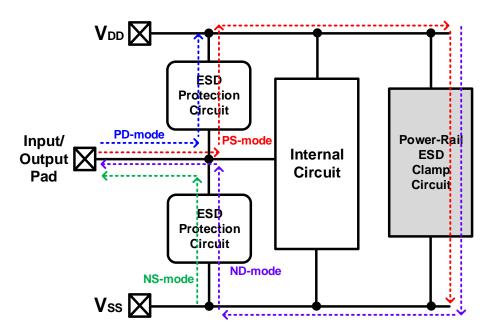

## 1.6 Power-Rail ESD Clamp Circuits

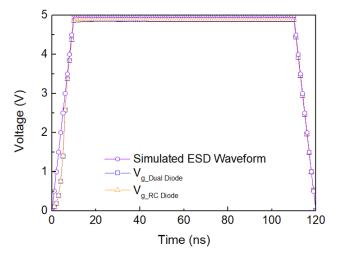

Because electrostatic discharge consists of a spiked current of several amperes in a short time about nanoseconds, ESD has become a significant reliability issue in the modern integrated circuits industry. The ESD protection component is placed around the input or output pad that is incomplete. As shown in Fig. 1.9, to provide the practical whole-chip ESD protection circuit for the internal circuit, the power-rail ESD clamp circuit plays a vital role between the power lines pad (V<sub>DD</sub>) and ground pad (V<sub>SS</sub>). The principal discharge component of the power-rail ESD clamp circuit usually chooses NMOS of a large size (M<sub>ESD</sub>). Before the internal circuit is damaged, the M<sub>ESD</sub> should be turned on by the ESD transient mechanism circuit. The ESD transient mechanism circuit can detect the ESD event and convey high-level voltage to the gate of M<sub>ESD</sub>. When the normal operating voltage provides to the V<sub>DD</sub> pad, this gate of M<sub>ESD</sub> should obtain low-level voltage from ESD transient mechanism.

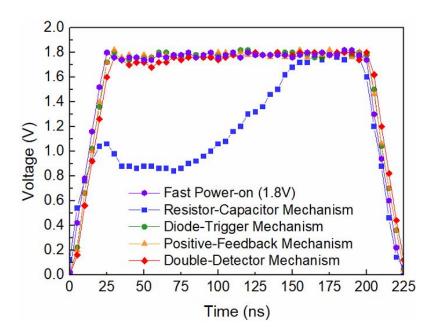

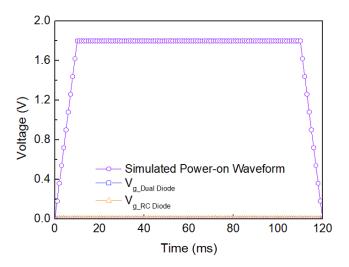

The rise time of normal power-supply voltage is about milliseconds during regular operation. The ESD transient mechanism of the present power-rail ESD clamp circuit architectures judges the rise time of normal operating voltage and static discharge voltage differently to control the gate of M<sub>ESD</sub>. However, in some conditions, such as a hot plug-in, the rise time is as quick as static electricity about nanoseconds called the fast power-on event. Some design methods will cause the problem of M<sub>ESD</sub> false triggering and great power dissipation. This research will analyze four power-rail ESD clamp circuit architectures in detail in Chapter 3.

#### **VDD-Vss Power-Rail ESD Clamp Circuit** V<sub>DD</sub> ESD current discharge path ESD Protection Circuit Input/ Output 2 **ESD** Internal transient MESD Circuit mechanism circuit **ESD** Protection Circuit Vss 🔀

Fig. 1.9. Power-rail ESD clamp circuit with transient mechanism circuit.

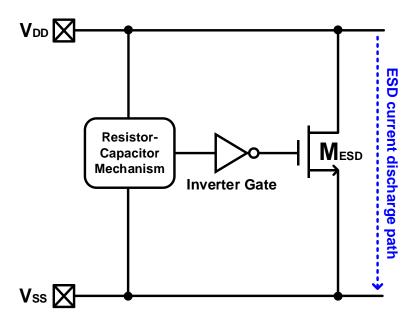

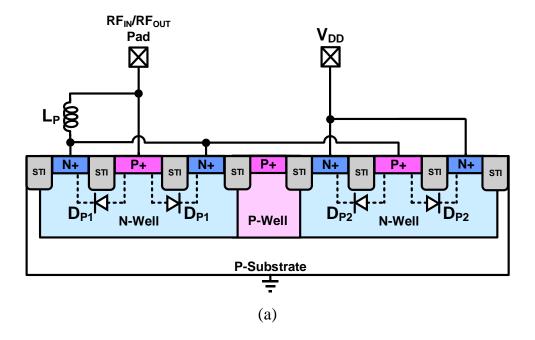

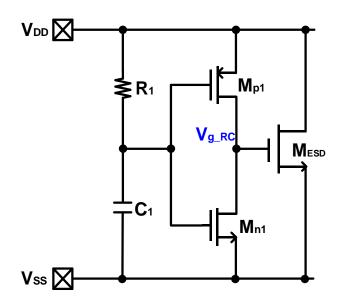

#### 1.6.1 Power-Rail ESD Circuit with Resistor-Capacitor Inverter Mechanism [19]

A typical power-rail ESD clamp circuit with resistor-capacitor inverter mechanism is shown in Fig. 1.10. The power-rail ESD clamp circuit is formed with a control circuit of resistor-capacitor mechanism, an inverter gate, and a large-size NMOS transistor ( $M_{ESD}$ ). During the positive ESD voltage applied to the  $V_{DD}$  node, the ESD clamp NMOS transistor is commanded to turn on. The turn-on time of the ESD clamp NMOS can be adjusted by the RC-time constant of the resistor-capacitor mechanism. As a result, to reach the desired operation, the RC-time constant's rise time is designed approximately microseconds ( $\mu$ s). However, the rising time of the operating voltage on the  $V_{DD}$  node may like the rising time of the ESD to cause some mis-triggered on the ESD clamp NMOS transistor. The mis-triggered event will affect the function and reliability of internal circuits. In order to overcome the problem, another solution method is presented in the next part.

Fig. 1.10. Power-rail ESD clamp circuit with resistor-capacitor inverter.

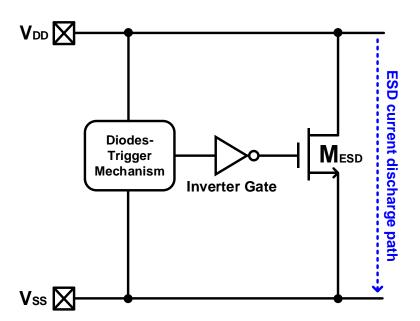

#### 1.6.2 Power-Rail ESD Circuit with Diode-Trigger Mechanism [20]

As shown in Fig. 1.11, the power-rail ESD clamp circuit consists of the diodetrigger control circuit, inverter gate, and a large-size NMOS transistor ( $M_{\rm ESD}$ ). The diode-trigger mechanism of the power-rail ESD clamp circuit was used to detect the voltage level of the  $V_{\rm DD}$  node. When the voltage on the  $V_{\rm DD}$  node is larger than the turn-on voltage level of the diode-trigger control mechanism, the diode-trigger mechanism can output a low voltage. At the same time, the gate of the NMOS transistor ( $M_{\rm ESD}$ ) can be converted to high level by the inverter gate, and then the  $M_{\rm ESD}$  is trigged to discharge ESD current. During normal operating conditions, the operating voltage level on the  $V_{\rm DD}$  node must be lower than the turn-on voltage of the diodes-trigger control mechanism to let the  $M_{\rm ESD}$  in the OFF state. Though the power-rail ESD clamp circuit cannot happen mis-triggering at the fast power-on event, the diode string often suffered a leakage issue in the high-temperature environment.

Fig. 1.11. Power-rail ESD clamp circuit with diode trigger.

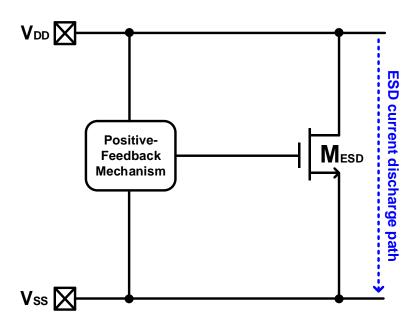

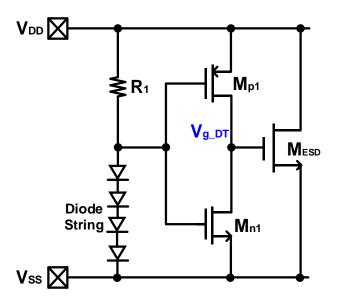

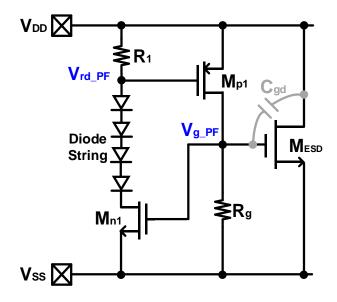

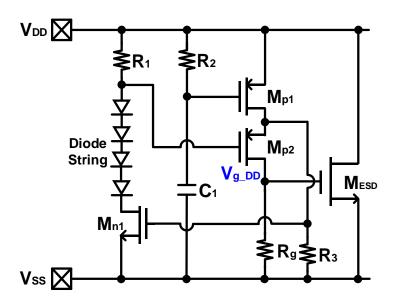

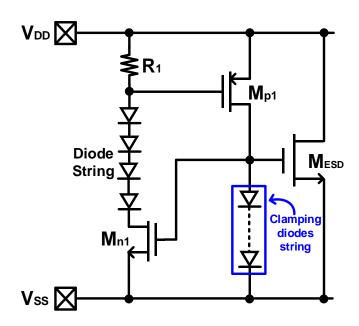

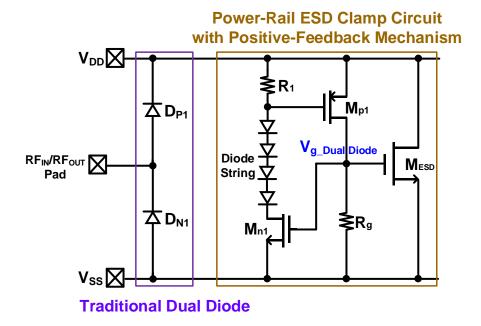

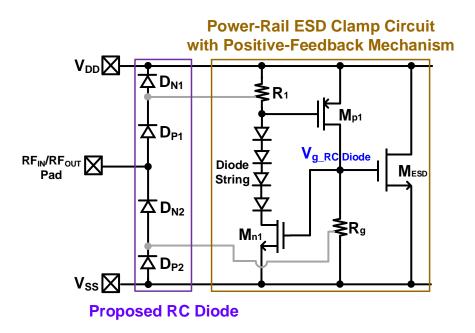

#### 1.6.3 Power-Rail ESD Circuit with Positive-Feedback Mechanism [21]

As shown in Fig. 1.12, the power-rail ESD clamp circuit consists of a positive-feedback control circuit and a large-size NMOS transistor (MESD). The positive-feedback control circuit with feedback technique is assembled by the diode, resistance, PMOS transistor, and NMOS transistor. The ESD clamp NMOS transistor is necessary to be turned on when the positive ESD voltage occurs at V<sub>DD</sub> node. The ESD current flows through the drain-gate parasitic capacitance (C<sub>gd</sub>) of the large-size NMOS transistor to cause voltage upward of the NMOS transistor (MESD) gate. By the positive-feedback control circuit, the voltage level of NMOS transistor (MESD) gate can be continuously elevated during ESD event. Therefore, the NMOS transistor (MESD) is turned on to discharge the ESD current. Under the normal operating condition, the positive-feedback control circuit that is designed to apply different operating voltages can make the ESD clamp NMOS transistor (MESD) turn off. In the essay, this architecture is selected to design the parameter of device and compares with the others. This detailed production process is presented in Chapter 3.

Fig. 1.12. Power-rail ESD clamp circuit with positive feedback.

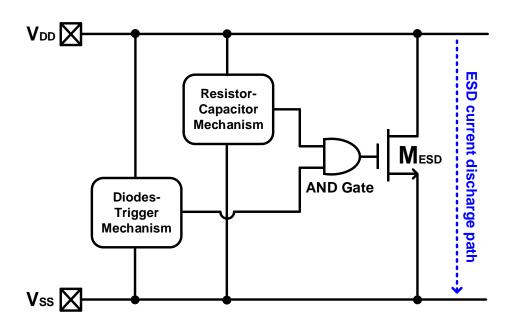

#### 1.6.4 Power-Rail ESD Circuit with Double-Detector Mechanism [22]

In order to make the M<sub>ESD</sub> accurate triggering against false trigger under normal operating voltage event, the power-rail ESD clamp circuit of the double-detector mechanism was created in Fig. 1.13. The power-rail ESD clamp circuit is divided into four parts: diodes-triggered mechanism, resistor-capacitor mechanism, AND gate, and M<sub>ESD</sub> of the large width. The diode numbers of the diodes-trigger mechanism are decided to refer to the normal power-on voltage level. The RC-time constant of the resistor-capacitor mechanism is usually designed to approximate microseconds. Even though the power-rail ESD clamp circuit with double-detector mechanism can enhance immunity against the false trigger during normal and fast power-on event, the power-rail ESD clamp circuit is complex to occupy much area.

Fig. 1.13. Power-rail ESD clamp circuit with double detector.

## 1.7 Organization of This Dissertation

The thesis consists of four chapters. In Chapter 1, there is the motivation for designing the ESD protection circuit, testing method, background, and applications containing some traditional ESD protection circuits that will be structured to apply for the high-frequency and the power-rail ESD clamp circuit with different triggering mechanisms. In Chapter 2, the ESD protection circuit will be proposed with resistance and diode, including interpreting design steps and measurement results. In Chapter 3, these present power-rail ESD clamp circuits are analyzed to apply the internal circuit of normal power-on and fast power-on events, including parameter selection flow and measurement results. Finally, Chapter 4 summarizes all research and future work.

## Chapter 2

# Resistance-Capacitance Diode for High-Frequency Application

The ESD protection circuit of resistance-capacitance diode (RC-diode) is proposed to apply to high frequency in the chapter. The resistor can be used to reduce the parasitic capacitance of ESD protection circuit. Therefore, the RC diode can diminish the severe high-frequency signal loss and have small layout area. All ESD protection circuits with traditional dual diode, traditional LC tank, and proposed resistance-capacitance diode are fabricated in CMOS process.

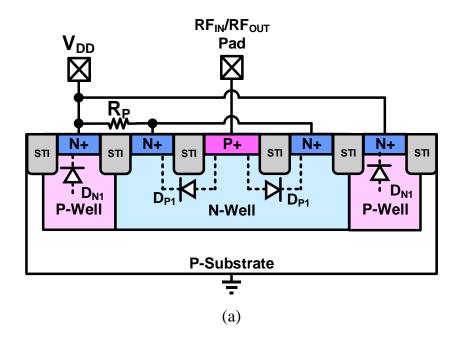

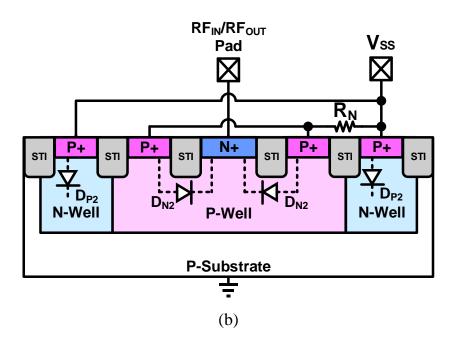

## 2.1 Traditional Dual-Diode Design

It is universal that the diode is used to compose ESD protection circuit in CMOS technology. As shown in Fig. 2.1, the whole-chip ESD protection circuit is composed of a P-type diode (D<sub>P</sub>) placed from RF<sub>IN</sub>/RF<sub>OUT</sub> pad to V<sub>DD</sub>, N-type diode (D<sub>N</sub>) placed from RF<sub>IN</sub>/RF<sub>OUT</sub> pad to V<sub>SS</sub>, and the power-rail ESD clamp circuit placed from V<sub>DD</sub> to V<sub>SS</sub>. Additionally, the ESD current can be discharged by different diodes under four modes. First of all, the ESD current can be discharged by a P-type diode under PD mode. Then, a P-type diode and power-rail ESD clamp circuit can discharge the ESD current under the PS mode. Next, an N-type diode can discharge the ESD current by an N-type diode and power-rail ESD clamp circuit.

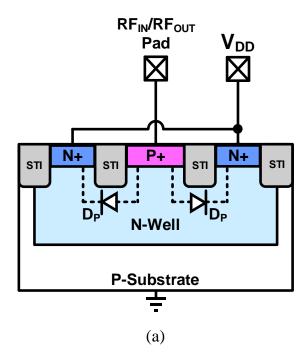

Furthermore, the traditional dual-diode ESD protection circuit comprises a  $D_P$ , a  $D_N$  and power-rail ESD clamp circuit. As shown in Fig. 2.2 (a), P+ diffusion is connected to the  $RF_{IN}/RF_{OUT}$  pad as the anode, while N+ diffusion can be a cathode when connects to the  $V_{DD}$ . As shown in Fig. 2.2 (b), the  $RF_{IN}/RF_{OUT}$  pad is connected to N+ diffusion as cathode, and the  $V_{SS}$  is connected to P+ diffusion as the anode.

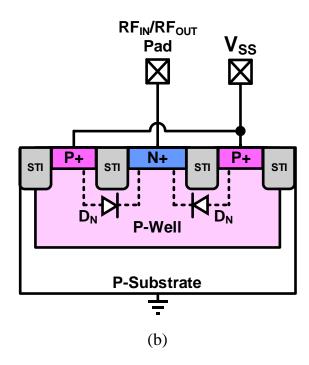

These test parameters of the traditional dual-diode ESD protection circuit with  $D_P$  and  $D_N$  are listed in Table 2.1. The thesis makes dual-diode ESD protection circuit with fixed 1.9 $\mu$ m length and different widths including 20 $\mu$ m, 40 $\mu$ m, and 60 $\mu$ m in order to compare the value of signal loss and ESD robustness. Fig. 2.3 shows the layout top view contains a  $D_P$  of 20 $\mu$ m width and a  $D_N$  of 20 $\mu$ m width. The layout top view contains a  $D_P$  of 40 $\mu$ m width and a  $D_N$  of 40 $\mu$ m width is shown in Fig. 2.4. Fig. 2.5 shows the layout top view contains a  $D_P$  of 60 $\mu$ m width and a  $D_N$  of 60 $\mu$ m width.

Fig. 2.1. The whole-chip ESD protection circuit with traditional dual diode.

Fig. 2.2. The cross-sectional view of the (a) P-type and (b) N-type diode.

Fig. 2.3. The layout top views of Dual-Diode\_20 $\mu m$

Fig. 2.4. The layout top views of Dual-Diode\_40 $\mu m$

Fig. 2.5. The layout top views of Dual-Diode\_60µm

Table 2.1. The parameter of ESD protection circuit with dual diode.

| Cell Name       | Device      | Width (μm) | Length (µm) |  |

|-----------------|-------------|------------|-------------|--|

| Dual Diada 200m | $D_P$       | 20         | 1.0         |  |

| Dual-Diode_20μm | $D_{N}$     | 20         | 1.9         |  |

| Dual-Diode_40μm | $D_P$       | 40         | 1.9         |  |

|                 | $D_N$       | 40         |             |  |

| Dual-Diode_60µm | $D_P$       | 60         | 1.0         |  |

| Duai-Diode_60µm | $D_{\rm N}$ | 00         | 1.9         |  |

# 2.2 Traditional LC-Tank Design

Though the dual-diode design parameter chooses big dimension to provide high ESD robustness, the equivalent parasitic capacitance will increase to cause signal loss appropriately at high frequency. In order to eliminate the equivalent parasitic capacitance, the designed method can use extra inductor to resonate. Aforementioned technique can design traditional LC-tank ESD protection circuit. It is called the impedance cancellation that using parallel LC reduces the parasitic capacitance. As shown in equation 2.1, the inductor value ( $L_{EXTRA}$ ) and parasitic capacitance value of ESD protection device ( $C_{ESD}$ ) can decide resonant frequency ( $\omega_0$ ). The resonant frequency is designed operating frequency of the RF internal circuit by the inductor.

$$\omega_0 = \frac{1}{\sqrt{L_{Extra} * C_{ESD}}} \tag{2.1}$$

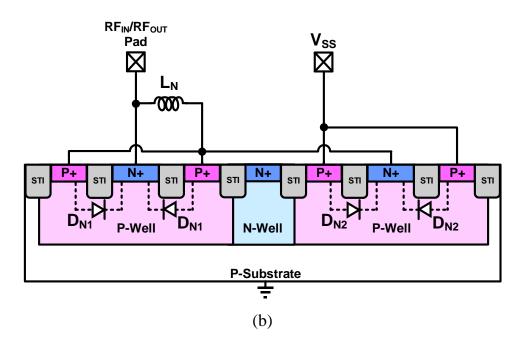

As shown in Fig. 2.6, the whole-chip ESD protection circuit consists of two pairs of LC tank, P-type diode ( $D_{P2}$ ), N-type diode ( $D_{N2}$ ) and power-rail ESD clamp circuit. The LC tank is composed of the inductor ( $L_P$ ) and the parasitic capacitance of ESD protection diode ( $D_{P1}$ ) placed from  $RF_{IN}/RF_{OUT}$  pad to ESD protection diode ( $D_{P2}$ ). Another LC tank is composed of the inductor ( $L_N$ ) and the parasitic capacitance of ESD protection diode ( $D_{N1}$ ) placed from  $RF_{IN}/RF_{OUT}$  pad to ESD protection diode ( $D_{N2}$ ). The power-rail ESD clamp circuit placed between  $V_{DD}$  and  $V_{SS}$ .

The ESD current can be discharged by the inductor  $(L_P)$  and ESD protection diode  $(D_{P1}$  and  $D_{P2})$  under PD mode. The ESD current can be discharged by the inductor  $(L_P)$ , ESD protection diode  $(D_{P1}$  and  $D_{P2})$ , and power-rail ESD clamp circuit under PS mode. The ESD current can be discharged by the inductor  $(L_N)$  and ESD protection diode  $(D_{N1}$  and  $D_{N2})$  under NS mode. The ESD current can be discharged by the inductor  $(L_N)$ , ESD protection diode  $(D_{N1}$  and  $D_{N2})$ , and power-rail ESD clamp circuit under ND mode. Under the normal circuit operating condition, the ESD protection diode of  $D_{P2}$  and  $D_{N2}$  can be used to isolate the steady current from  $V_{DD}$  to  $V_{SS}$ . As shown in Fig. 2.7 (a), the RF<sub>IN</sub>/RF<sub>OUT</sub> pad is connected to P+ diffusion and inductor  $(L_P)$ . The ESD protection diode  $(D_{P1})$ . The  $V_{DD}$  is connected to N+ diffusion. As shown in Fig. 2.7 (b), the RF<sub>IN</sub>/RF<sub>OUT</sub> pad is connected to N+ diffusion and inductor  $(L_N)$ . The ESD protection diode  $(D_{N2})$  is connected to LC tank of inductor  $(L_N)$ . The ESD protection diode  $(D_{N2})$  is connected to LC tank of inductor  $(L_N)$  and ESD protection diode  $(D_{N1})$ . The  $V_{SS}$  is connected to P+ diffusion.

The test parameters of the LC-tank ESD protection circuit with P-type diode (D<sub>P1</sub>

and  $D_{P2}$ ) and N-type diode ( $D_{N1}$  and  $D_{N2}$ ) are listed in Table 2.2. The thesis makes LC-tank ESD protection circuit with fixed 1.9 $\mu$ m length and inductor value ( $L_P$  and  $L_N$ ). The widths include 20 $\mu$ m, 40 $\mu$ m and 60 $\mu$ m to compare value of signal loss and ESD robustness. The layout top view contains  $D_{P1}$  and  $D_{P2}$  of 20 $\mu$ m width and  $D_{N1}$  and  $D_{N2}$  of 20 $\mu$ m width are shown in Fig. 2.8. The layout top view contains  $D_{P1}$  and  $D_{P2}$  of 40 $\mu$ m width and  $D_{N1}$  and  $D_{N2}$  of 40 $\mu$ m width are shown in Fig. 2.9. The layout top view contains  $D_{P1}$  and  $D_{P2}$  of 60 $\mu$ m width and  $D_{N1}$  and  $D_{N2}$  of 60 $\mu$ m width are shown in Fig. 2.10.

Fig. 2.6. The whole-chip ESD protection circuit with traditional LC tank.

Fig. 2.7. The cross-sectional view of the (a) P-type diode with  $L_P$  and (b) N-type diode with  $L_N$ .

Fig. 2.8. The layout top views of LC-tank\_20µm

Fig. 2.9. The layout top views of LC-tank\_40µm

Fig. 2.10. The layout top views of LC-tank $_60\mu m$

Table 2.2. The parameter of ESD protection circuit with LC tank.

| Cell Name      | Device                              | Width (μm) | Length (µm) |  |

|----------------|-------------------------------------|------------|-------------|--|

| I C touly 20mm | D <sub>P1</sub> and D <sub>P2</sub> | 20         | 1.0         |  |

| LC-tank_20µm   | $D_{N1}$ and $D_{N2}$               | 20         | 1.9         |  |

| I C tank 10um  | $D_{P1}$ and $D_{P2}$               | 40         | 1.9         |  |

| LC-tank_40µm   | $D_{N1}$ and $D_{N2}$               | 40         |             |  |

| I C tank 60um  | $D_{P1}$ and $D_{P2}$               | 60         | 1.9         |  |

| LC-tank_60μm   | $D_{N1}$ and $D_{N2}$               | 00         | 1.9         |  |

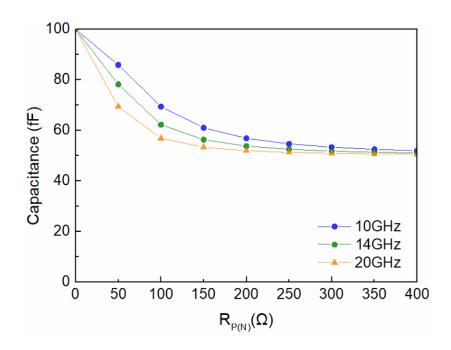

## 2.3 Proposed RC-Diode Design

As shown in Fig. 2.11, the novel RC-diode ESD protection circuit is proposed in the thesis. The RC-diode ESD protection circuit combines with P-type diode (D<sub>P1</sub>), N-type diode (D<sub>N2</sub>), and two pairs of RD-tanks. In order to achieve a whole-chip ESD protection circuit, the power-rail ESD clamp circuit is incorporated into the RC-diode ESD protection circuit. The RD tank is consisted of the resistor (R<sub>P</sub>) and the ESD protection diode (D<sub>N1</sub>) placed from the ESD protection diode (D<sub>P1</sub>) to V<sub>DD</sub>. Another RD tank is consisted of the resistor (R<sub>N</sub>) and the ESD protection diode (D<sub>P2</sub>) placed from ESD protection diode (D<sub>N2</sub>) to V<sub>SS</sub>. In addition, the power-rail ESD clamp circuit is placed between V<sub>DD</sub> and V<sub>SS</sub>. If these diodes (D<sub>P1</sub>, D<sub>N1</sub>, D<sub>N2</sub>, and D<sub>P2</sub>) are regarded as capacitors (C<sub>DP1</sub>, C<sub>DN1</sub>, C<sub>DN2</sub>, and C<sub>DP2</sub>), the equations (2.2) and (2.3) can be used to calculate the equivalent parasitic capacitance from RF<sub>IN</sub>/RF<sub>OUT</sub> pad to V<sub>DD</sub> and V<sub>SS</sub>, respectively. The Y<sub>RFIN/RFOUT-to-VDD</sub> and Y<sub>RFIN/RFOUT-to-VSS</sub>, which denoted the admittance,

are seen from  $RF_{IN}/RF_{OUT}$  pad to  $V_{DD}$  and  $V_{SS}$ . As shown in Fig. 2.12, if the parasitic capacitance of each diode is 100fF and the operating frequency are 10GHz, 14GHz, and 20GHz, the parasitic capacitance can be reduced through increasing the  $R_P$  and  $R_N$ , and then the signal loss can also be reduced.

The ESD current can be discharged by ESD protection diode ( $D_{P1}$  and  $D_{N1}$ ) and the resistor ( $R_P$ ) under PD mode. The ESD current can be discharged by ESD protection diode ( $D_{P1}$  and  $D_{N1}$ ), the resistor ( $R_P$ ), and power-rail ESD clamp circuit under PS mode. The ESD current can be discharged by ESD protection diode ( $D_{N2}$  and  $D_{P2}$ ) and the resistor ( $R_N$ ) under NS mode. The ESD current can be discharged by ESD protection diode ( $D_{N2}$  and  $D_{P2}$ ), the resistor ( $R_N$ ), and power-rail ESD clamp circuit under ND mode. The ESD protection diode of  $D_{P1}$  and  $D_{N2}$  can be used to isolate the steady current from  $V_{DD}$  to  $V_{SS}$  under the normal circuit operating condition. As shown in Fig. 2.13 (a), the  $RF_{IN}/RF_{OUT}$  pad is connected to  $P_{P1}$  diffusion. The ESD protection diode ( $D_{P1}$ ) is connected to resistor ( $R_P$ ) and ESD diode ( $D_{N1}$ ). As shown in Fig. 2.13 (b), the  $RF_{IN}/RF_{OUT}$  pad is connected to  $N_{P1}$  diffusion. The ESD protection diode ( $D_{N2}$ ) is connected to resistor ( $R_N$ ) and ESD diode ( $D_{P2}$ ).

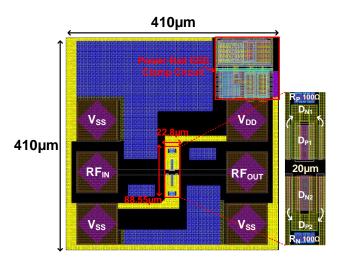

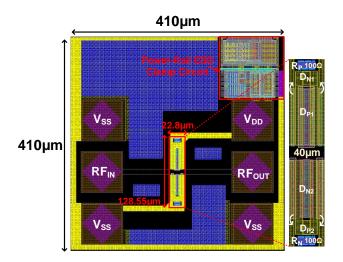

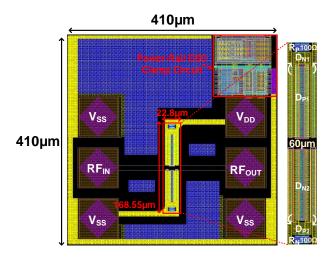

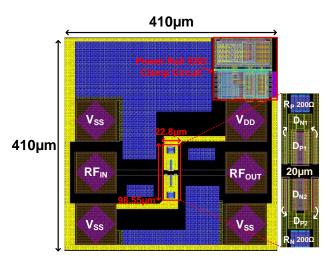

The test sizes of RC-diode ESD protection circuit with P-type diode ( $D_{P1}$  and  $D_{P2}$ ) and N-type diode ( $D_{N1}$  and  $D_{N2}$ ) are listed in Table 2.3. The proposed RC-diode ESD diode length is fixed to 1.9 $\mu$ m. The proposed RC-diode ESD diode widths include 20 $\mu$ m, 40 $\mu$ m, and 60 $\mu$ m, respectively. The proposed RC-diode resistance value is 100ohms and 200ohms, respectively. The different ESD diode widths and resistance values are used to compare the values of signal loss and ESD robustness. The layout top view contains a 100ohms resistor value, P-type diode ( $D_{P1}$  and  $D_{P2}$ ), and N-type diode ( $D_{N1}$  and  $D_{N2}$ ) of 20 $\mu$ m width are shown in Fig. 2.14. The layout top view contains a 100ohms resistor value, P-type diode ( $D_{P1}$  and  $D_{P2}$ ), and N-type diode ( $D_{N1}$  and  $D_{N2}$ ) of 40 $\mu$ m width are shown in Fig. 2.15. The layout top view contains a 100ohms resistor value, P-type diode

$(D_{P1} \text{ and } D_{P2})$ , and N-type diode  $(D_{N1} \text{ and } D_{N2})$  of 60μm width are shown in Fig. 2.16. The layout top view contains a 200ohms resistor value, P-type diode  $(D_{P1} \text{ and } D_{P2})$ , and N-type diode  $(D_{N1} \text{ and } D_{N2})$  of 20μm width are shown in Fig. 2.17. The layout top view contains a 200ohms resistor value, P-type diode  $(D_{P1} \text{ and } D_{P2})$ , and N-type diode  $(D_{N1} \text{ and } D_{N2})$  of 40μm width are shown in Fig. 2.18. The layout top view contains a 200ohms resistor value, P-type diode  $(D_{P1} \text{ and } D_{P2})$ , and N-type diode  $(D_{N1} \text{ and } D_{N2})$  of 60μm width are shown in Fig. 2.19.

Fig. 2.11. The whole-chip ESD protection circuit with proposed RC diode.

$$C_{RF_{IN}/RF_{OUT}-to-V_{DD}} = \frac{Im(Y_{RF_{IN}/RF_{OUT}-to-V_{DD}})}{\omega} = \frac{Im(Y_{RF_{IN}/RF_{OUT}-to-V_{DD}})}{\omega} = \frac{\frac{1}{j\omega C_{D_{N_{1}}} + \frac{1}{R_{P}}} + \frac{1}{j\omega C_{D_{P_{1}}}}}{\omega}$$

$$= \frac{\omega^{2}R_{P}^{2}C_{D_{N_{1}}}C_{D_{P_{1}}}(C_{D_{N_{1}}} + C_{D_{P_{1}}}) + C_{D_{P_{1}}}}{\omega^{2}R_{P}^{2}(C_{D_{N_{1}}} + C_{D_{P_{1}}})^{2} + 1}$$

(2.2)

$$C_{\text{RF}_{\text{IN}}/\text{RF}_{\text{OUT}}-\text{to}-V_{SS}} = \frac{Im\left(Y_{\text{RF}_{\text{IN}}/\text{RF}_{\text{OUT}}-\text{to}-V_{SS}}\right)}{\omega} = \frac{Im\left(\frac{1}{j\omega C_{D_{P2}} + \frac{1}{R_{N}}} + \frac{1}{j\omega C_{D_{N2}}}\right)}{\omega}$$

$$= \frac{\omega^{2}R_{N}^{2}C_{D_{N2}}C_{D_{P2}}(C_{D_{N2}} + C_{D_{P2}}) + C_{D_{N2}}}{\omega^{2}R_{N}^{2}(C_{D_{N2}} + C_{D_{P2}})^{2} + 1}$$

(2.3)

Fig. 2.12. The calculation results of the  $R_{P(N)}$  and the parasitic capacitance at 10GHz, 14GHz and 20GHz.

Fig. 2.13. The cross-sectional view of the (a) P-type diode with  $R_P$  and (b) N-type diode with  $R_N$ .

Fig. 2.14. The layout top views of RC-Diode\_ $100\Omega_20\mu m$ .

Fig. 2.15. The layout top views of RC-Diode\_100 $\Omega_40\mu m$ .

Fig. 2.16. The layout top views of RC-Diode\_100 $\Omega$ \_60 $\mu$ m.

Fig. 2.17. The layout top views of RC-Diode\_200 $\Omega$ \_20 $\mu$ m.

Fig. 2.18. The layout top views of RC-Diode\_200 $\Omega$ \_40 $\mu$ m.

Fig. 2.19. The layout top views of RC-Diode\_200 $\Omega$ \_60 $\mu$ m.

Table 2.3. The parameter of ESD protection circuit with RC diode.

| Cell Name                     | Device                              | Width<br>(µm) | Length (µm) | Resistor (Ω)   |  |

|-------------------------------|-------------------------------------|---------------|-------------|----------------|--|

|                               | D <sub>P1</sub> and D <sub>P2</sub> | 20            | 1.0         | 27/4           |  |

| RC-Diode_ $100\Omega_20\mu m$ | D <sub>N1</sub> and D <sub>N2</sub> | 20            | 1.9         | N/A            |  |

|                               | R <sub>P</sub> and R <sub>N</sub>   | 6.2           | 11.8        | 100            |  |

|                               | D <sub>P1</sub> and D <sub>P2</sub> | 40            | 1.0         | 27/4           |  |

| RC-Diode_100Ω_40μm            | D <sub>N1</sub> and D <sub>N2</sub> | 40            | 1.9         | N/A            |  |

|                               | R <sub>P</sub> and R <sub>N</sub>   | 6.2           | 11.8        | 100            |  |

|                               | D <sub>P1</sub> and D <sub>P2</sub> | <b>60</b>     | 1.0         | DI/A           |  |

| RC-Diode_100Ω_60μm            | D <sub>N1</sub> and D <sub>N2</sub> | 60            | 1.9         | N/A            |  |

|                               | $R_P$ and $R_N$                     | 6.2           | 11.8        | 100            |  |

|                               | D <sub>P1</sub> and D <sub>P2</sub> | 20            | 1.0         | NI/A           |  |

| RC-Diode_200Ω_40μm            | D <sub>N1</sub> and D <sub>N2</sub> | 20            | 1.9         | N/A            |  |

|                               | $R_P$ and $R_N$                     | 11.2          | 11.8        | 200            |  |

|                               | D <sub>P1</sub> and D <sub>P2</sub> | 40            | 1.0         | NI/A           |  |

| RC-Diode_200Ω_40μm            | D <sub>N1</sub> and D <sub>N2</sub> | 40            | 1.9         | N/A            |  |

|                               | $R_P$ and $R_N$                     | 11.2          | 11.8        | 200            |  |

|                               | D <sub>P1</sub> and D <sub>P2</sub> | <b>70</b>     | 1.0         | <b>N</b> T / A |  |

| RC-Diode_200Ω_60μm            | D <sub>N1</sub> and D <sub>N2</sub> | 60            | 1.9         | N/A            |  |

|                               | R <sub>P</sub> and R <sub>N</sub>   | 11.2          | 11.8        | 200            |  |

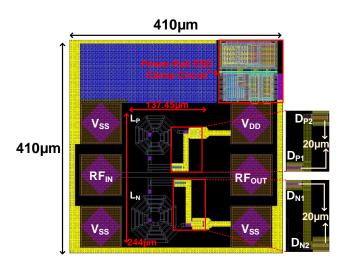

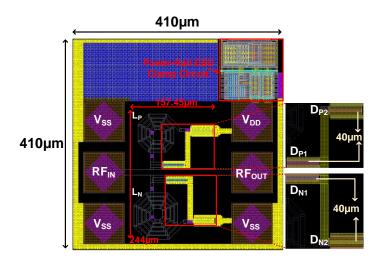

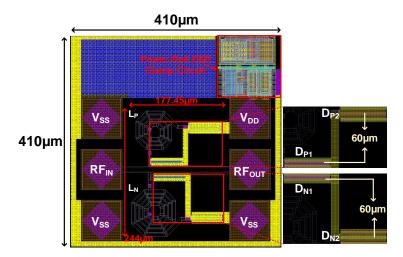

### 2.4 Measurement Results

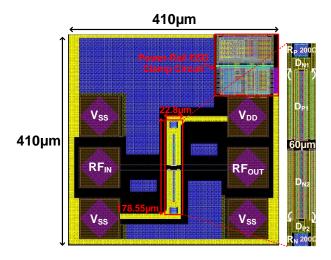

These traditional and proposed ESD test circuits are fabricated in a 350nm CMOS process, and the length and width of the chip are 1250µm and 2090µm. As shown in Fig. 2.20, the chip micrograph of ESD protection circuits is containing three types of circuits: traditional dual diode, traditional LC tank, and proposed RC diode. These ESD test circuits are intended to measure the two-port S-parameter of high frequency, TLP measurement, VF-TLP measurement, and Human-Body Model (HBM) robustness measurement. The measurement method and results are introduced in the following section.

Fig. 2.20. The chip micrograph of all ESD protection circuits.

### **2.4.1 High-Frequency Performance**

As shown in Fig. 2.21, these test circuits of ESD protection are measured by the high-frequency measurement system [23]. The vector network analyzer uses a two-port ground-signal-ground (G-S-G) probe to get the high-frequency two-port S-parameter characteristic of each test circuit. When the voltage difference of the PN junction in the diode is 0V, the diode can be extracted the maximum parasitic capacitance. So, the V<sub>DD</sub>, RF<sub>IN</sub> / RF<sub>OUT</sub> and V<sub>SS</sub> terminals are provided bias voltage of 0V. Moreover, the high-frequency measurement results of these test circuits include the parasitic effect of the G-S-G test pad, these test circuits should be adopted the de-embedding technique to extract the precision of the test circuits' measured results. The de-embedding technique is used to extract intrinsic characteristics of these test circuits at high-frequency [24], [25]. It is necessary to measure the effect of de-embedding G-S-G pads as a reference in Fig. 2.22 (a) and Fig. 2.22 (b). Finally, these test circuits are carried out de-embedding technique into practice as following measured results.

Fig. 2.21. The picture of high-frequency measurement system [23].

Fig. 2.22. The de-embedding pad for test circuit of (a) dual diode, RC diode and (b) LC tank.

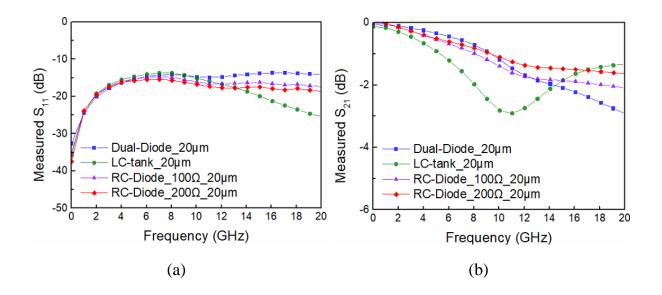

Fig. 2.23. Measured S-parameters of Dual-Diode\_20 $\mu$ m, LC-tank\_20 $\mu$ m, RC-Diode\_100\Omega\_20\mu and RC-Diode\_200\Omega\_20\mu m.

Fig. 2.24. Measured S-parameters of Dual-Diode\_40 $\mu$ m, LC-tank\_40 $\mu$ m, RC-Diode 100 $\Omega$  40 $\mu$ m and RC-Diode 200 $\Omega$  40 $\mu$ m.

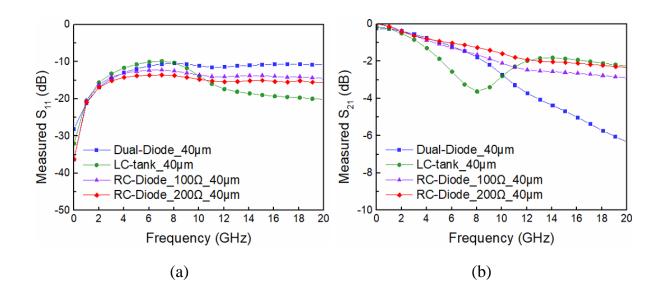

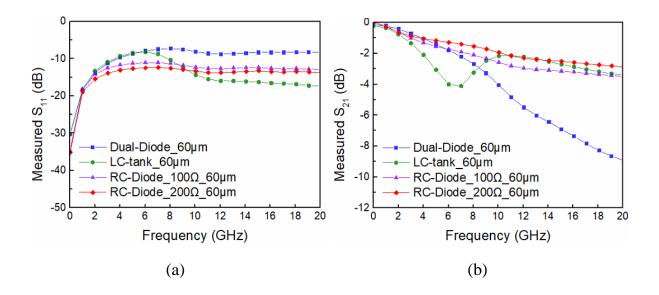

Fig. 2.25. Measured S-parameters of Dual-Diode\_60 $\mu$ m, LC-tank\_60 $\mu$ m, RC-Diode 100 $\Omega$  60 $\mu$ m and RC-Diode 200 $\Omega$  60 $\mu$ m.

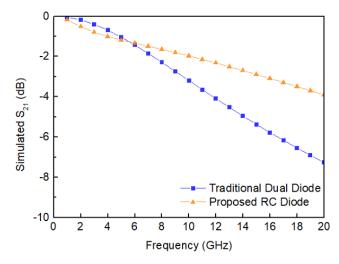

As shown in Fig. 2.23, the measured S-parameters of RC-Diode\_ $100\Omega_20\mu m$  and RC-Diode\_ $200\Omega_20\mu m$  are compared with those of Dual-Diode\_ $20\mu m$  and LC-tank\_ $20\mu m$ . As shown in Fig. 2.24, the measured S-parameters of RC-Diode\_ $100\Omega_40\mu m$  and RC-Diode\_ $200\Omega_40\mu m$  are compared with those of Dual-Diode\_ $40\mu m$  and LC-tank\_ $40\mu m$ . As shown in Fig. 2.25, the measured S-parameters of RC-Diode\_ $100\Omega_60\mu m$  and RC-Diode\_ $200\Omega_60\mu m$  are compared with those of Dual-Diode\_ $60\mu m$  and LC-tank\_ $60\mu m$ . The smaller width such as RC-Diode\_ $100\Omega_20\mu m$ , RC-Diode\_ $200\Omega_20\mu m$ , LC-tank\_ $20\mu m$  and Dual-Diode\_ $20\mu m$  are displayed the better high-frequency performance at same ESD protection architecture.

The measured S-parameters of these traditional and proposed designs are listed in Table 2.4. The  $S_{21}$  of proposed RC diode is obviously degraded than the  $S_{21}$  of the traditional dual diode at the same diode width. Though the  $S_{21}$  of the traditional LC tank and proposed RC diode are about -2dB, traditional LC tank need a large layout area to place matching inductor. Except for Dual-Diode\_60 $\mu$ m, the  $S_{11}$  of the other test circuits are lower than -10dB.

Table 2.4. The measured results of S-parameter.

| Cell Name          | Frequency<br>(GHz) | S <sub>11</sub> (dB) | S <sub>21</sub> (dB) |  |

|--------------------|--------------------|----------------------|----------------------|--|

| Dual-Diode_20μm    | 20                 | -14.1                | -2.9                 |  |

| LC-tank_20µm       | 20                 | -25.5                | -1.3                 |  |

| RC-Diode_100Ω_20μm | 20                 | -17.4                | -2.0                 |  |

| RC-Diode_200Ω_20μm | 20                 | -18.6                | -1.6                 |  |

| Dual-Diode_40μm    | 14                 | -11.0                | -4.3                 |  |

| LC-tank_40µm       | 14                 | -18.5                | -1.8                 |  |

| RC-Diode_100Ω_40μm | 14                 | -13.8                | -2.5                 |  |

| RC-Diode_200Ω_40μm | 14                 | -15.2                | -1.9                 |  |

| Dual-Diode_60μm    | 10                 | -8.1                 | -4.0                 |  |

| LC-tank_60µm       | 10                 | -14.3                | -2.2                 |  |

| RC-Diode_100Ω_60μm | 10                 | -12.2                | -2.5                 |  |

| RC-Diode_200Ω_60μm | 10                 | -13.3                | -1.9                 |  |

### 2.4.2 Transmission-line pulsing (TLP) Measurement

The transmission-line pulsing (TLP) generator measured system can investigate and characterize the performance of each ESD protection circuit under the testing. The TLP measured system can provide high energy pulse such as an electrostatic discharge (ESD) event. When a voltage pulse is inputted, a current value is recorded. The TLP I-V curve is formed with all voltage values and current values [26]. As shown in Fig. 2.26, the TLP system is used to acquire the data of this study. There are several significant parameters, including trigger voltage ( $V_{t1}$ ), secondary breakdown current ( $I_{t2}$ ), and turnon resistance ( $R_{on}$ ) from observing the I-V curve. Deciding failure criterion of these ESD protection devices is defined the leakage current shifting 30% from its initial curve after each TLP level testing. Four ESD current paths are shown, including PS mode, PD mode, NS mode, and ND mode. The  $I_{t2}$  results of these ESD discharges are summarized in Table 2.5.

Fig. 2.26. The picture of transmission-line pulse (TLP) measurement system.

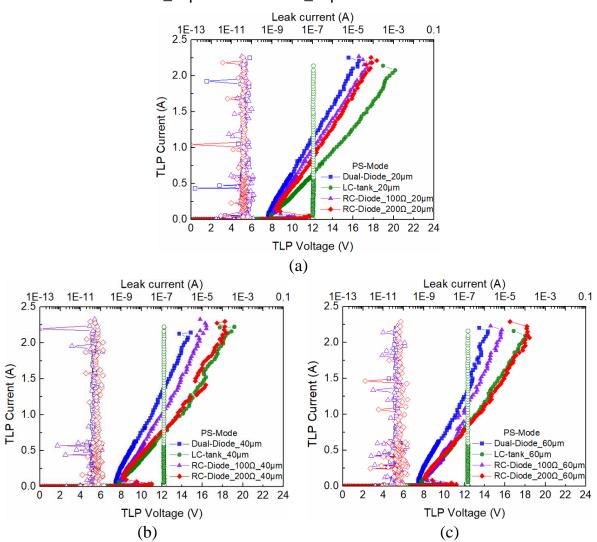

### (1) Positive to V<sub>SS</sub> (PS-mode)

The PS-mode discharge path of these traditional and proposed ESD protection circuits is through the diode from the I/O pad to the  $V_{DD}$  and power-rail ESD clamp circuit in series. Fig. 2.27 (a) shows that the TLP I-V curves of RC-Diode\_ $100\Omega_20\mu m$  and RC-Diode\_ $200\Omega_20\mu m$  are compared with the TLP I-V curves of Dual-Diode\_ $20\mu m$  and LC-tank\_ $20\mu m$ . Fig. 2.27 (b) shows that the TLP I-V curves of RC-Diode\_ $100\Omega_40\mu m$  and RC-Diode\_ $200\Omega_40\mu m$  are compared with the TLP I-V curves of Dual-Diode\_ $40\mu m$  and LC-tank\_ $40\mu m$ . Fig. 2.27 (c) show that the TLP I-V curves of RC-Diode\_ $100\Omega_60\mu m$  and RC-Diode\_ $200\Omega_60\mu m$  are compared with the TLP I-V curves of Dual-Diode\_ $60\mu m$  and RC-Diode\_ $200\Omega_60\mu m$  are compared with the TLP I-V curves of Dual-Diode\_ $60\mu m$  and LC-tank\_ $60\mu m$ .

Fig. 2.27. The TLP I-V curves of traditional and proposed designs under PS mode.

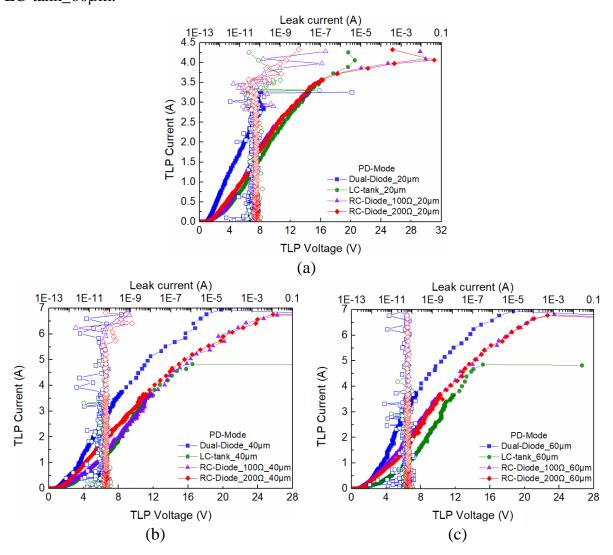

### (2) Positive to $V_{DD}$ (PD-mode)

The PD-mode discharge path of these traditional and proposed ESD protection circuits is through the diode from the I/O pad to  $V_{DD}$ . Fig. 2.28 (a) shows that the TLP I-V curves of RC-Diode\_100 $\Omega$ \_20 $\mu$ m and RC-Diode\_200 $\Omega$ \_20 $\mu$ m are compared with the TLP I-V curves of Dual-Diode\_20 $\mu$ m and LC-tank\_20 $\mu$ m. Fig. 2.28 (b) shows that the TLP I-V curves of RC-Diode\_100 $\Omega$ \_40 $\mu$ m and RC-Diode\_200 $\Omega$ \_40 $\mu$ m are compared with the TLP I-V curves of Dual-Diode\_40 $\mu$ m and LC-tank\_40 $\mu$ m. Fig. 2.28 (c) shows that the TLP I-V curves of RC-Diode\_100 $\Omega$ \_60 $\mu$ m and RC-Diode\_200 $\Omega$ \_60 $\mu$ m are compared with the TLP I-V curves of Dual-Diode\_60 $\mu$ m and LC-tank\_60 $\mu$ m.

Fig. 2.28. The TLP I-V curves of traditional and proposed designs under PD mode.

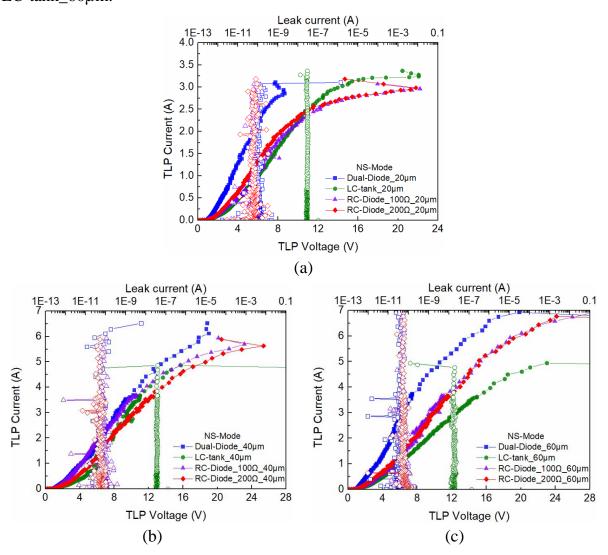

### (3) Negative to $V_{SS}$ (NS-mode)

The NS-mode discharge path of these traditional and proposed ESD protection circuits is through the diode located from the I/O pad to  $V_{SS}$ . Fig. 2.29 (a) shows that the TLP I-V curves of RC-Diode\_100 $\Omega$ \_20 $\mu$ m and RC-Diode\_200 $\Omega$ \_20 $\mu$ m are compared with the TLP I-V curves of Dual-Diode\_20 $\mu$ m and LC-tank\_20 $\mu$ m. Fig. 2.29 (b) shows that the TLP I-V curves of RC-Diode\_100 $\Omega$ \_40 $\mu$ m and RC-Diode\_200 $\Omega$ \_40 $\mu$ m are compared with the TLP I-V curves of Dual-Diode\_40 $\mu$ m and LC-tank\_40 $\mu$ m. Fig. 2.29 (c) shows that the TLP I-V curves of RC-Diode\_100 $\Omega$ \_60 $\mu$ m and RC-Diode\_200 $\Omega$ \_60 $\mu$ m are compared with the TLP I-V curves of Dual-Diode\_60 $\mu$ m and LC-tank\_60 $\mu$ m.

Fig. 2.29. The TLP I-V curves of traditional and proposed designs under NS mode.

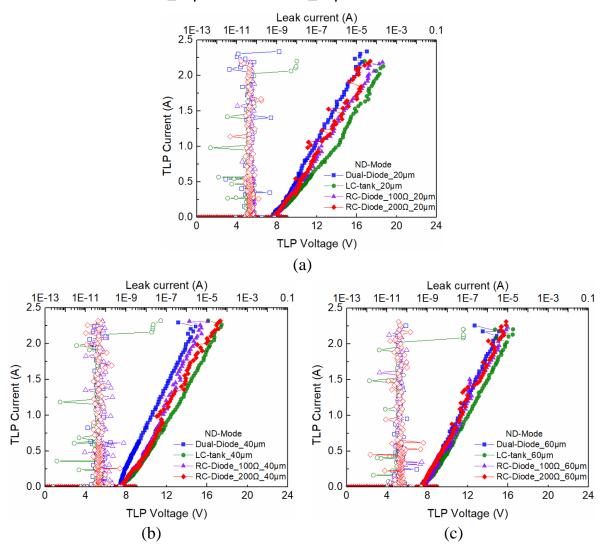

### (4) Negative to V<sub>DD</sub> (ND-mode)

The ND-mode discharge path of these traditional and proposed ESD protection circuits is through the diode located from the I/O pad to Vss and power-rail ESD clamp circuit in series. Fig. 2.30 (a) shows that the TLP I-V curves of RC-Diode\_ $100\Omega_20\mu m$  and RC-Diode\_ $200\Omega_20\mu m$  are compared with the TLP I-V curves of Dual-Diode\_ $20\mu m$  and LC-tank\_ $20\mu m$ . Fig. 2.30 (b) shows that the TLP I-V curves of RC-Diode\_ $100\Omega_40\mu m$  and RC-Diode\_ $200\Omega_40\mu m$  are compared with the TLP I-V curves of Dual-Diode\_ $40\mu m$  and LC-tank\_ $40\mu m$ . Fig. 2.30 (c) shows that the TLP I-V curves of RC-Diode\_ $100\Omega_60\mu m$  and RC-Diode\_ $200\Omega_60\mu m$  are compared with the TLP I-V curves of Dual-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  are compared with the TLP I-V curves of Dual-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  are compared with the TLP I-V curves of Dual-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  are compared with the TLP I-V curves of Dual-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  are compared with the TLP I-V curves of Dual-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  are compared with the TLP I-V curves of Dual-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  are compared with the TLP I-V curves of Dual-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  are compared with the TLP I-V curves of Dual-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  are compared with the TLP I-V curves of Dual-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  are compared with the TLP I-V curves of Dual-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  are compared with the TLP I-V curves of Dual-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  are compared with the TLP I-V curves of RC-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  are compared with the TLP I-V curves of RC-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  are compared with the TLP I-V curves of RC-Diode\_ $40\mu m$  and RC-Diode\_ $40\mu m$  are compared with the TLP I-V curves OI-V c

Fig. 2.30. The TLP I-V curves of traditional and proposed designs under ND mode.

### (5) Power-Rail ESD Clamp Circuit

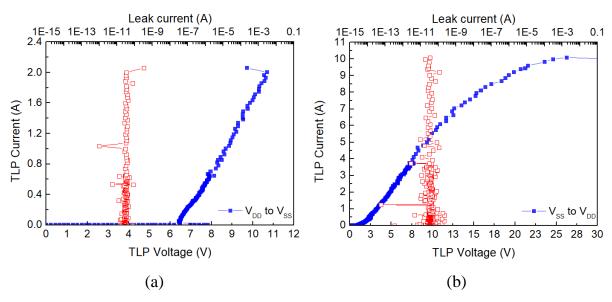

The power-rail ESD clamp circuit can discharge ESD current from  $V_{DD}$  to  $V_{SS}$  when an ESD event occurred on the  $V_{DD}$  pad. An NMOS device with an RC network control circuit forms the primary ESD discharge path. The inside parasitic diode of NMOS also provides an ESD discharge path from  $V_{SS}$  to  $V_{DD}$ .

As shown in Fig. 2.31, the TLP I-V curves of the power-rail ESD clamp circuit is measured. The trigger voltage of the power-rail ESD clamp circuit is 7.8V, and the power-rail ESD clamp circuit can withstand ESD current ( $I_{t2}$ ) of 2A from  $V_{DD}$  to  $V_{SS}$ . The trigger voltage of the power-rail ESD clamp circuit is 0.7V, and the power-rail ESD clamp circuit can withstand ESD current ( $I_{t2}$ ) of 10.2A from  $V_{SS}$  to  $V_{DD}$ .

Fig. 2.31. The TLP I-V curves of power-rail ESD clamp circuit under (a)  $V_{DD}$  to  $V_{SS}$  and (b)  $V_{SS}$  to  $V_{DD}$ .

Table 2.5. The measured results of secondary breakdown current ( $I_{t2}$ ).

| It2 (A)            |         |         |         |         |  |  |  |  |

|--------------------|---------|---------|---------|---------|--|--|--|--|

| Cell Name          | PS-mode | PD-mode | NS-mode | ND-mode |  |  |  |  |

| Dual-Diode_20µm    | 2.2     | 2.8     | 2.9     | 2.1     |  |  |  |  |

| LC-tank_20μm       | 2.0     | 3.3     | 3.2     | 2.0     |  |  |  |  |

| RC-Diode_100Ω_20μm | 2.0     | 3.9     | 3.0     | 2.0     |  |  |  |  |

| RC-Diode_200Ω_20μm | 2.1     | 3.6     | 3.0     | 2.0     |  |  |  |  |

| Dual-Diode_40µm    | 2.0     | 6.9     | 6.1     | 2.1     |  |  |  |  |

| LC-tank_40μm       | 2.1     | 4.8     | 4.8     | 2.0     |  |  |  |  |

| RC-Diode_100Ω_40μm | 2.0     | 6.7     | 5.7     | 2.0     |  |  |  |  |

| RC-Diode_200Ω_40μm | 2.0     | 6.2     | 5.6     | 2.0     |  |  |  |  |

| Dual-Diode_60µm    | 2.1     | 6.9     | 6.9     | 2.1     |  |  |  |  |

| LC-tank_60μm       | 2.1     | 4.9     | 4.8     | 2.0     |  |  |  |  |

| RC-Diode_100Ω_60μm | 2.0     | 6.8     | 6.9     | 2.0     |  |  |  |  |

| RC-Diode_200Ω_60μm | 1.9     | 6.8     | 6.8     | 2.0     |  |  |  |  |

#### 2.4.3 HBM Robustness

As shown in Fig. 2.32, the human-body model (HBM) test is implemented to obtain HBM ESD robustness of traditional and proposed architecture by compact ESD simulator HCE-5000 in the thesis. The HBM tester is regulated the stress from 0.5kV to 8kV and one step 0.5kV during the measurement process. In order to ascertain these traditional and proposed ESD protection circuits are broken, the standard is defined as leakage current shifting more than 30%. The HBM level results of these traditional and proposed ESD protection circuits are consolidated in Table 2.6.

Fig. 2.32. The picture of HBM tester.

Table 2.6. The HBM test results.

|                    | HBM (kV) |         |         |         |  |  |  |  |  |

|--------------------|----------|---------|---------|---------|--|--|--|--|--|

| Cell Name          | PS-mode  | PD-mode | NS-mode | ND-mode |  |  |  |  |  |

| Dual-Diode_20µm    | 3.5      | 4.5     | 4.5     | 3.5     |  |  |  |  |  |

| LC-tank_20µm       | 3.5      | 5.5     | 5.5     | 3.5     |  |  |  |  |  |

| RC-Diode_100Ω_20μm | 3.5      | 5.5     | 5.5     | 3.5     |  |  |  |  |  |

| RC-Diode_200Ω_20μm | 3.5      | 5.5     | 5.5     | 3.5     |  |  |  |  |  |

| Dual-Diode_40μm    | 3.5      | >8      | >8      | 3.5     |  |  |  |  |  |

| LC-tank_40µm       | 3.5      | >8      | >8      | 3.5     |  |  |  |  |  |

| RC-Diode_100Ω_40μm | 3.5      | >8      | >8      | 3.5     |  |  |  |  |  |

| RC-Diode_200Ω_40μm | 3.5      | >8      | >8      | 3.5     |  |  |  |  |  |

| Dual-Diode_60µm    | 3.5      | >8      | >8      | 3.5     |  |  |  |  |  |

| LC-tank_60µm       | 3.5      | >8      | >8      | 3.5     |  |  |  |  |  |

| RC-Diode_100Ω_60μm | 3.5      | >8      | >8      | 3.5     |  |  |  |  |  |

| RC-Diode_200Ω_60μm | 3.5      | >8      | >8      | 3.5     |  |  |  |  |  |

### 2.4.4 Very-Fast Transmission-line pulsing (VF-TLP) Measurement

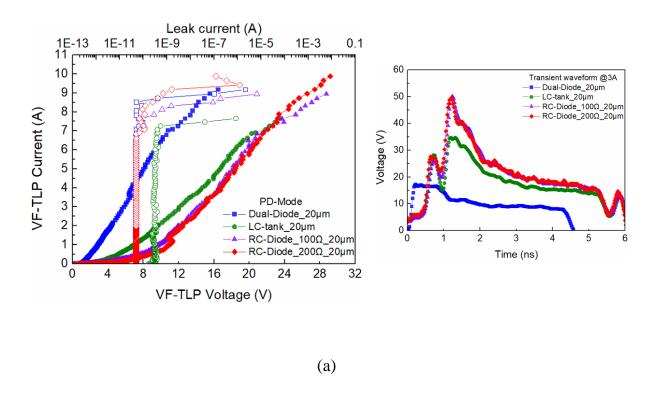

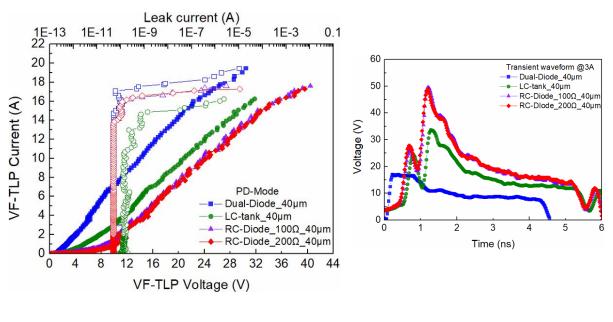

As shown in Fig. 2.33, the very-fast TLP (VF-TLP) measured system is used to investigate the effectiveness of these ESD protection devices in the time domain of a Charged-device model (CDM) ESD event [27], [28]. The VF-TLP is set with a rise time of 200ps and a pulse width of 5ns to evaluated the turn-on behavior of the traditional and proposed designs under CDM-like fast-transient conditions. Fig. 2.34 (a) shows the measured VF-TLP I-V curves and transient waveforms at 3A of Dual-Diode\_20 $\mu$ m, LC-tank\_20 $\mu$ m, RC-Diode\_100\Omega\_20 $\mu$ m, and RC-Diode\_200\Omega\_20 $\mu$ m under PD mode. Fig. 2.34 (b) shows the measured VF-TLP I-V curves and transient waveforms at 3A of Dual-Diode\_40 $\mu$ m, LC-tank\_40 $\mu$ m, RC-Diode\_100\Omega\_40 $\mu$ m, and RC-Diode\_200\Omega\_40 $\mu$ m under PD mode.

Fig. 2.33. The very-fast transmission-line pulse (VF-TLP) measured system [26].

Fig. 2.34. The VF-TLP I-V curves and transient waveform at 3A of traditional and proposed designs under PD mode.

(b)

## 2.5 Comparison and Discussion of This Test Chip

As shown in Table 2.7, these ESD protection circuits are measured under PS mode. The trigger voltage ( $V_{t1}$ ) that is about 10V is defined as the current value of TLP measured results is more than 1mA. The turn-on resistance ( $R_{on}$ ) is about 4~6 $\Omega$  when they are becoming a conductor. The secondary breakdown current ( $I_{t2}$ ) of these ESD protection circuits is similar. When operating at 1.8V, the leakage current of the traditional LC tank is about 130nA, and others are less than 0.1nA.

Table 2.7. The comparison of traditional and proposed designs under PS mode.

|                    | PS-mode             |                     |                        |             |                            |  |  |  |

|--------------------|---------------------|---------------------|------------------------|-------------|----------------------------|--|--|--|

| Cell Name          | V <sub>t1</sub> (V) | I <sub>t2</sub> (A) | $R_{ m on}$ $(\Omega)$ | HBM<br>(kV) | Leakage current (nA) @1.8V |  |  |  |

| Dual-Diode_20μm    | 9.4                 | 2.2                 | 4.1                    | 3.5         | <0.1                       |  |  |  |

| LC-tank_20µm       | 9.6                 | 2.0                 | 6.3                    | 3.5         | 101                        |  |  |  |

| RC-Diode_100Ω_20μm | 10.2                | 2.0                 | 4.5                    | 3.5         | <0.1                       |  |  |  |

| RC-Diode_200Ω_20μm | 11.8                | 2.1                 | 4.7                    | 3.5         | <0.1                       |  |  |  |

| Dual-Diode_40μm    | 9.3                 | 2.0                 | 4.3                    | 3.5         | <0.1                       |  |  |  |

| LC-tank_40µm       | 9.4                 | 2.1                 | 6.5                    | 3.5         | 130                        |  |  |  |

| RC-Diode_100Ω_40μm | 10.3                | 2.0                 | 4.4                    | 3.5         | <0.1                       |  |  |  |

| RC-Diode_200Ω_40μm | 11.0                | 2.0                 | 6.3                    | 3.5         | <0.1                       |  |  |  |

| Dual-Diode_60µm    | 9.2                 | 2.1                 | 4.5                    | 3.5         | <0.1                       |  |  |  |