# ESD Protection Design for Differential Low-Noise Amplifier With Cross-Coupled SCR

Chun-Yu Lin<sup>1</sup>, Ming-Dou Ker<sup>1,2</sup>, and Yuan-Wen Hsiao<sup>1</sup>

Abstract—A new electrostatic discharge (ESD) protection scheme for differential low-noise amplifier (LNA) was proposed in this paper. The new ESD protection scheme, which evolved from the conventional double-diode ESD protection scheme without adding any extra device, was realized with cross-coupled silicon-controlled rectifier (SCR). With the new ESD protection scheme, the pin-to-pin ESD robustness can be improved, which was the most critical ESD-test pin combination for differential input pads. Experimental results had shown that differential LNA with cross-coupled-SCR ESD protection scheme can achieve excellent ESD robustness and good RF performances.

#### I. Introduction

As the feature size of MOS transistor in CMOS technology is continuously scaled down to improve the high-frequency characteristics, the advanced nanoscale CMOS technology is more attractive to implement radio-frequency (RF) circuits. In an RF front-end, the low-noise amplifier (LNA) plays a very important role because it is the first stage in the RF receiver. In LNA design, differential configuration is popular because the differential LNA has the advantages of better common-mode noise rejection, as well as less sensitivity to substrate noise, supply noise, and bond-wire inductance variation [1], [2]. In addition, the differential output signals of the differential LNA can be directly connected to the differential inputs of the double balanced mixer.

With the evolution of CMOS technology, the electrostatic discharge (ESD) protection design in nanoscale CMOS process becomes more challenging [3]. The ESD protection design should be taken into consideration during the design phase of RF circuits to achieve satisfactory ESD robustness without seriously degrading circuit performances [4]. Since the LNA is usually connected to the external of the RF receiver chip such as the off-chip antenna, on-chip ESD protection circuits are needed for all input pads of the LNA. However, applying ESD protection circuits at the input pads

inevitably introduce some impacts from parasitics to RF performance. There are several ESD protection designs reported for RF front-end circuits to optimize RF performance and ESD robustness [5]-[7]. Some ESD protection designs have been presented to improve ESD robustness of LNA under pin-to-pin ESD stresses, since the pin-to-pin ESD stress was one of the most critical ESD events for differential input pads [5].

In this paper, a new ESD protection design is proposed to protect the differential LNA in a 130-nm CMOS process. The pin-to-pin ESD robustness is substantially improved by the new proposed ESD protection scheme in this work.

## II. CONVENTIONAL DOUBLE-DIODE ESD PROTECTION SCHEME

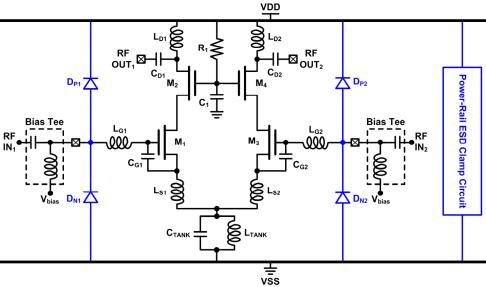

The conventional double-diode ESD protection scheme for differential LNA is shown in Fig. 1. The P+/N-well diodes ( $D_P$ ) are connected between each input pads and VDD, while the N+/P-well diodes ( $D_N$ ) are connected between each input pads and VSS. To co-design the input matching network of LNA with ESD protection diodes, the source inductors ( $L_{S1}$  and  $L_{S2}$ ) and gate inductors ( $L_{G1}$  and  $L_{G2}$ ) are adjusted to achieve impedance match at the operating frequency.

Besides ESD protection diodes, the power-rail ESD clamp circuit is used to provide ESD current paths between VDD and VSS under ESD stresses. The power-rail ESD clamp circuit is placed between VDD and VSS, so it does not contribute any parasitic effects to input pads. During positive-to-VDD-mode (PD-mode) and negative-to-VSS-mode (NS-mode) ESD stresses, ESD current is discharged through the forward-biased D<sub>P</sub> and D<sub>N</sub>, respectively. During positive-to-VSS-mode (PSmode) ESD stress, ESD current is discharged from the RF IN pad through the D<sub>P</sub> and the power-rail ESD clamp circuit to VSS. Similarly, during negative-to-VDD-mode (ND-mode) ESD stress, ESD current is discharged from the VDD through the power-rail ESD clamp circuit and the D<sub>N</sub> to the RF IN pad. Under pin-to-pin ESD stress, ESD current is discharged from the RF  $IN_1$  (RF  $IN_2$ ) pad through the  $D_{P1}$  ( $D_{P2}$ ), the power-rail ESD clamp circuit, and the  $D_{N2}$  ( $D_{N1}$ ) to RF IN<sub>2</sub> (RF IN<sub>1</sub>) pad.

<sup>&</sup>lt;sup>1</sup> Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan

<sup>&</sup>lt;sup>2</sup> Department of Electronic Engineering, I-Shou University, Kaohsiung, Taiwan

This work was partially supported by "Aim for the Top University Plan" of the National Chiao-Tung University and Ministry of Education, Taiwan, R.O.C., and partially supported by National Science Council (NSC), Taiwan, under Contract of NSC98-2221-E-009-113-MY2.

Figure 1. Conventional double-diode ESD protection scheme for differential LNA.

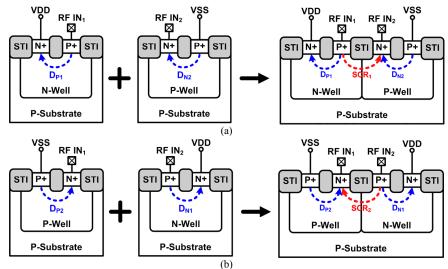

Figure 2. Establishing SCR paths from (a) RF IN<sub>1</sub> to RF IN<sub>2</sub>, and (b) RF IN<sub>2</sub> to RF IN<sub>1</sub>, by combining P+/N-well diodes with N+/P-well diodes.

This ESD protection scheme provides the corresponding current discharging paths for all ESD-test pin combinations.

## III. NEW CROSS-COUPLED-SCR ESD PROTECTION SCHEME

Fig. 2 illustrates the concept of the proposed ESD protection scheme. The four ESD protection diodes at the differential input pads in the double-diode ESD protection scheme are reserved in this new design, but the placement is changed. In this new ESD protection scheme, the siliconcontrolled rectifier (SCR) path is established directly from one differential input pad to the other differential input pad without adding any extra device. As illustrated in Fig. 2(a), by merging  $D_{P1}$  and  $D_{N2}$  together, an SCR path (SCR<sub>1</sub>) from RF IN<sub>1</sub> pad to RF IN<sub>2</sub> pad can be established for pin-to-pin ESD protection. Similarly,  $D_{P2}$  and  $D_{N1}$  can be merged together to form another SCR path (SCR<sub>2</sub>) from RF IN<sub>2</sub> pad to RF IN<sub>1</sub>

pad, as illustrated in Fig. 2(b). The SCR path has very high ESD robustness due to its low clamping voltage under ESD stress conditions [8]. Since the pin-to-pin ESD path is established by SCR, the cross-coupled-SCR ESD protection scheme is expected to have high pin-to-pin ESD robustness. Under PD- PS-, ND-, and NS-mode ESD stresses, the ESD levels are not altered, since  $D_{P1}$ ,  $D_{N1}$ ,  $D_{P2}$ , and  $D_{N2}$  still exist.

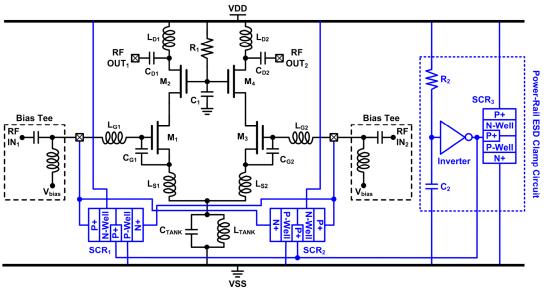

The circuit schematic of the differential LNA with the new proposed ESD protection scheme of cross-coupled SCR is shown in Fig. 3. The SCR<sub>1</sub> is placed close to the RF IN<sub>1</sub> pad to provide efficient pin-to-pin ESD current path from the RF IN<sub>1</sub> pad to the RF IN<sub>2</sub> pad. Similarly, the SCR<sub>2</sub> is placed close to the RF IN<sub>2</sub> pad to provide efficient ESD current path from the RF IN<sub>2</sub> pad to the RF IN<sub>1</sub> pad under pin-to-pin ESD stresses. To reduce the trigger voltage and increase the turn-on speed of the SCR under ESD stresses, the substrate-triggered technique is used [8]. The trigger port of SCR is connected to the ESD

Figure 5. New cross-coupled-SCR ESD protection scheme for differential LNA.

detection circuit in the power-rail ESD clamp circuit. Under pin-to-pin ESD stress, the ESD detection circuit outputs trigger current to the trigger port of  $SCR_1$  or  $SCR_2$ . As a result, the  $SCR_1$  or  $SCR_2$  is turned on to provide ESD current path between RF  $IN_1$  and RF  $IN_2$  pads. Under normal circuit operating conditions, the ESD detection circuit and the SCR are kept off.

The test circuits have been fabricated in a 130-nm CMOS process. The total parasitic capacitance from the cross-coupled SCR at each input pad is specified as 300 fF. To achieve the total parasitic capacitance of 300 fF at each differential input pad, the sizes of SCR<sub>1</sub> and SCR<sub>2</sub> are all drawn as 60  $\mu m \times 2.4$   $\mu m$  in layout. The source inductors ( $L_{S1}$  and  $L_{S2}$ ) and gate inductors ( $L_{G1}$  and  $L_{G2}$ ) are adjusted to achieve the input matching of LNA with the cross-coupled SCR.

### IV. EXPERIMENTIAL RESULTS

The human-body-model (HBM) and machine-model (MM) ESD levels of differential LNA with the proposed cross-coupled-SCR ESD protection scheme under different test pin combinations are listed in Table I. The ESD test results show that the differential LNA with cross-coupled-SCR ESD protection scheme can sustain pin-to-pin ESD stresses of over 8-kV HBM and 800-V MM. The proposed ESD-protected differential LNA in this work exhibits excellent ESD robustness, especially in the pin-to-pin ESD stresses.

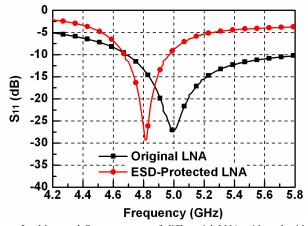

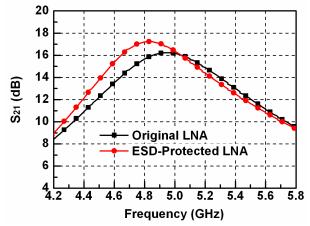

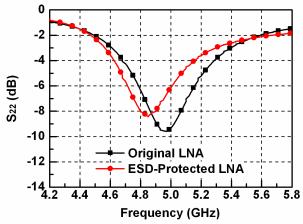

The measured RF performances of the differential LNA with cross-coupled-SCR ESD protection scheme are compared with those of the original differential LNA without ESD protection in Figs. 4~7. To compare the input matching conditions, the measured S<sub>11</sub>-parameters of these two differential LNAs are shown in Fig. 4. It is observed that the operating frequency of the differential LNA with cross-coupled-SCR ESD protection scheme is shifted from 5 GHz to 4.8 GHz. At 4.8-GHz, the measured S<sub>11</sub>-parameter is -26.3 dB. The shift in the operating frequency is due to the lack of RF model for SCR device in the given CMOS process. To more

Figure 3. Measured  $S_{\rm II}$ -parameters of differential LNA with and without cross-coupled-SCR ESD protection.

Figure 4. Measured S<sub>21</sub>-parameters of differential LNA with and without cross-coupled-SCR ESD protection.

Figure 6. Measured S<sub>22</sub>-parameters of differential LNA with and without cross-coupled-SCR ESD protection.

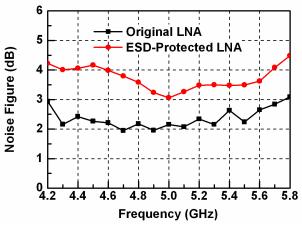

Figure 7. Measured noise figures of differential LNA with and without cross-coupled-SCR ESD protection.

precisely simulate the differential LNA with the cross-coupled-SCR ESD protection scheme, the parasitic effects of the SCR can be modeled by the diodes with P+/N-well, P-well/N-well, and N+/P-well junctions, rather than only the 300-fF capacitance. Fig. 5 compares the measured S<sub>21</sub>-parameters (power gains) of these two differential LNAs. At 4.8 GHz, the S<sub>21</sub>-parameter of differential LNA with cross-coupled-SCR ESD protection scheme is 17.2 dB. The S<sub>22</sub>-parameter of differential LNA with cross-coupled-SCR ESD protection scheme is -8 dB at 4.8 GHz, as shown in Fig. 6.

Fig. 7 shows the measured noise figures of these two differential LNAs. At 4.8 GHz, the noise figure of differential LNA with cross-coupled-SCR ESD protection scheme is 3.58 dB. The increase in the noise figure is attributed to the parasitic effects of ESD protection devices with the overlapped wide metal lines in layout, which are connected between the differential input pads and the cross-coupled SCR devices. These measured performances of the differential LNA with and without cross-coupled-SCR ESD protection scheme are also summarized in Table I.

TABLE I. COMPARISON BETWEEN FABRICATED DIFFERENTIAL LNAS

|                |                               | Original LNA    | ESD-Protected<br>LNA |

|----------------|-------------------------------|-----------------|----------------------|

| ESD Robustness | Positive to VSS<br>(HBM / MM) | < 50 V / < 10 V | 3.5 kV / 300 V       |

|                | Negative to VDD<br>(HBM / MM) | < 50 V / < 10 V | 3.5 kV / 350 V       |

|                | Pin to Pin<br>(HBM / MM)      | < 50 V / < 10 V | > 8 kV / 800 V       |

|                | VDD to Vss<br>(HBM / MM)      | 0.5 kV / < 10 V | > 8 kV / >1000 V     |

| RF Performance | Operating<br>Frequency        | 5 GHz           | 4.8 GHz              |

|                | Power Consumption             | 10.3 mW         | 10.3 mW              |

|                | S <sub>11</sub>               | -27.2 dB        | -26.3 dB             |

|                | S <sub>21</sub>               | 16.2 dB         | 17.2 dB              |

|                | Noise Figure                  | 2.16 dB         | 3.58 dB              |

#### V. CONCLUSION

The new ESD protection scheme of cross-coupled SCR is realized without adding any extra device, as compared with the conventional double-diode ESD protection scheme. The differential LNA with the new cross-coupled-SCR ESD protection scheme can improve the pin-to-pin ESD robustness, which was the most critical ESD-test pin combination for differential input pads. Verified in a 130-nm CMOS process, the pin-to-pin ESD robustness of the differential LNA with the proposed cross-coupled-SCR ESD protection scheme has been substantially improved. The proposed ESD protection scheme co-designed with the differential LNA can achieve good RF performances and high ESD robustness simultaneously.

## REFERENCES

- T. Chang, J. Chen, L. Rigge, and J. Lin, "ESD-protected wideband CMOS LNAs using modified resistive feedback techniques with chipon-board packaging," *IEEE Trans. Microw. Theory Tech.*, vol. 56, no. 8, pp. 1817–1826, Aug. 2008.

- [2] Y. Cao, V. Issakov, and M. Tiebout, "A 2kV ESD-protected 18GHz LNA with 4dB NF in 0.13μm CMOS," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, 2008, pp. 194–195.

- [3] S. Voldman, ESD: Circuits and Devices. New York: Wiley, 2006.

- [4] S. Voldman, ESD: RF Technology and Circuits. New York: Wiley, 2006

- [5] Y.-W. Hsiao and M.-D. Ker, "A 5-GHz differential low-noise amplifier with high pin-to-pin ESD robustness in a 130-nm CMOS process," *IEEE Trans. Microw. Theory Tech.*, vol. 57, no. 5, pp. 1044-1053, May 2009

- [6] D. Linten, S. Thijs, M. Natarajan, P. Wambacq, W. Jeamsaksiri, J. Ramos, A. Mercha, S. Jenei, S. Donnay, and S. Decoutere, "A 5-GHz fully integrated ESD-protected low-noise amplifier in 90-nm RF CMOS," *IEEE J. Solid-State Circuits*, vol. 40, no. 7, pp. 1434-1442, Jul. 2005.

- [7] S. Hyvonen and E. Rosenbaum, "Diode-based tuned ESD protection for 5.25 GHz CMOS LNAs," in *Proc. EOS/ESD Symp.*, 2005, pp. 9-17.

- [8] M.-D. Ker and K.-C. Hsu, "Overview of on-chip electrostatic discharge protection design with SCR-based devices in CMOS integrated circuits," *IEEE Trans. Device Mater. Reliab.*, vol. 5, no. 2, pp. 235-249, Jun. 2003.