# Impact of Shielding Line on CDM ESD Robustness of Core Circuits in a 65-nm CMOS Process

Ming-Dou Ker<sup>1,2</sup>, Chun-Yu Lin<sup>1</sup>, and Tang-Long Chang<sup>1</sup>

<sup>1</sup> Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan

Abstract — The charged-device-model (CDM) ESD robustness of core circuit with/without the shielding line was studied in a 65-nm CMOS process. Verified in silicon chip, the CDM ESD robustness of core circuit with the shielding line was degraded. The damage mechanism and failure location of the test circuits were investigated in this work.

Keywords - Charged-device model (CDM), ESD, shielding line.

# I. INTRODUCTION

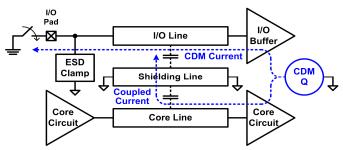

Adding the shielding lines near to the signal lines of highspeed circuits is an efficient method to limit the inductive coupling and to reduce the crosstalk noise between signal lines [1], [2]. The signal lines are generally shielded by the shielding lines which are biased at V<sub>DD</sub> or V<sub>SS</sub>. However, the coupling effect between the shielding and signal lines during chargeddevice-model (CDM) ESD event could induce large transient current to damage the core circuits. Among the chip-level ESD test standards (HBM, MM, and CDM), the CDM ESD events play major roles to cause failures in today's manufacturing and packaging environments [3], [4]. Therefore, several ESD protection designs against CDM ESD events have been reported to protect the input/output (I/O) buffers which are directly connected to the external pins [5]. Besides the I/O buffers, the core circuits would also suffer the dangers when the CDM events happened at the I/O buffers. As shown in Fig. 1, the coupling effect between I/O line and core line during CDM ESD event can induce large transient current to damage the core circuit, even if the shielding line is inserted. In this paper, the impact of shielding line on CDM ESD robustness of core circuit is investigated in a 65-nm CMOS process.

## **II. TEST CIRCUITS**

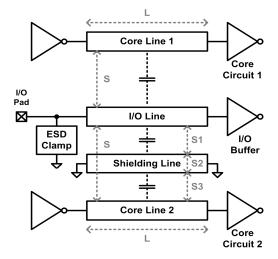

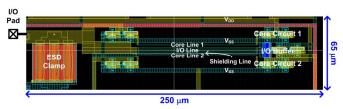

One set of test circuits is shown in Fig. 2. The I/O buffer realized with inverter is connected to the I/O pad through the I/O line with ESD clamp at the I/O pad. The ESD clamp is realized with the gate-grounded NMOS (GGNMOS) of 360μm/0.12μm (W/L). The core circuits without (with) inserting the shielding line between I/O line and core circuit 1 (core circuit 2) are arranged in parallel to the I/O buffer. The spacing between I/O line and core line is labeled as S, and the length of each line in layout with metal layer is labeled as L. The spacing between I/O line and the shielding line, the width of shielding metal, and the spacing between the shielding line and the core line are labeled as S1, S2, and S3, respectively. The split conditions of the test circuits with different L, S, S1, S2, and S3 are listed in Table I. The layout top view of one test circuit with 100-µm L and 0.78-µm S is shown in Fig. 3. All these circuits have been fabricated in a 65-nm CMOS process with the thin-gate oxide of  $\sim 20$  Å.

# III. MEASUREMENTS RESULTS AND FAILURE ANALYSIS

The test circuits with a die size of ~2x1.5 mm<sup>2</sup> have been assembled in DIP-40-pin packages. The CDM ESD stresses are applied by the field-induced CDM tester. The failure criterion

is 30% shift of the leakage current under 1-V  $V_{DD}$  bias from its original level. CDM ESD robustness among these test circuits are listed in Table I. The negative CDM ESD robustness of all core circuits exceeded -600 V. The positive CDM ESD robustness of some core circuits without inserting the shielding line exceeded 600 V. Even if the metal length (L) of core circuits without inserting shielding is reduced, which leads to the lower impedance and higher overshoot voltage, the positive CDM ESD robustness can still achieve 400 V. However, the positive CDM ESD robustness of core circuits with inserting the shielding line are seriously degraded to only 100 V.

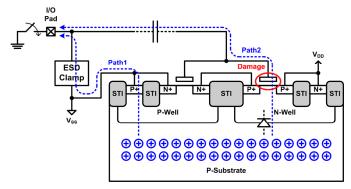

As shown in Fig. 4, there are two discharging paths (path1) and path2) from the core circuits to the grounded I/O pad during the CDM ESD stress. The CDM charges located around the p-substrate of core circuits can be conducted through the P+ pickup of core circuits into the V<sub>SS</sub> line, and then discharged through the ESD clamp device at the I/O pad to external ground, as the dashed line of path1 shown in Fig. 4. The CDM ESD event typically has a fast rise time of only ~0.2 ns. Such very fast transient ESD pulse will be inherently conducted by the displacement current of capacitor,  $i = C \times (dv/dt)$ , to the external ground through the path with capacitive structures. When the parasitic capacitance becomes larger due to inserting the shielding line between I/O line and core line in chip layout, some of CDM charges will be discharged by the displacement current, as the dashed line of path2 shown in Fig. 4. Since the positive charges located around the PMOS of core circuit can not be efficiently discharged through the P+ pickup and ESD clamp, the positive charges located around the PMOS can only be discharged through the gate oxide of PMOS (path2), which is a capacitive path with low impedance under fast transient. The ESD current discharged through the thin gate oxide of PMOS in the core circuit will cause damage on it.

The scanning-electron-microscope (SEM) photograph of the test circuit with 100-µm L and 0.78-µm S after 200-V CDM ESD test is shown in Fig. 5. The failure point is located only at the poly gate of PMOS transistor in core circuit 2, which fully agrees with aforementioned explanation in Fig. 4.

When the CDM charges stored in the P-substrate is negative, the high reverse breakdown voltage of the parasitic P-substrate/N-well diode will limit the CDM current being discharged through the path2 to external ground. Therefore, the negative CDM ESD robustness was not degraded by inserting the shielding line in chip layout, as compared in Table I.

# IV. CONCLUSION

After inserting the shielding line between I/O line and core signal line, the coupling effect during CDM ESD event has been found to induce large transient current to damage the core circuits. This mechanism has been practically verified in silicon chip. The experimental results of this work can help foundries or IC design houses to optimize their layouts for better CDM ESD protection.

<sup>&</sup>lt;sup>2</sup> Department of Electronic Engineering, I-Shou University, Kaohsiung, Taiwan

### REFERENCES

- Y. Ogasahara, M. Hashimoto, and T. Onoye, "Measurement and analysis of inductive coupling noise in 90 nm global interconnects," *IEEE J. Solid-State Circuits*, vol. 43, no. 3, pp. 718-728, Mar. 2008.

T. Chen, C. Ito, W. Loh, W. Wang, K. Doddapaneni, S. Mitra, and R.

- [2] T. Chen, C. Ito, W. Loh, W. Wang, K. Doddapaneni, S. Mitra, and R. Dutton, "Design methodology and protection strategy for ESD-CDM robust digital system design in 90-nm and 130-nm technologies," *IEEE Trans. Electron Devices*, vol. 56, no. 2, pp. 275-283, Feb. 2009.

- [3] J. Lee, J. Shih, S. Guo, D. Yang, J. Chen, D. Su, and K. Wu, "The study of sensitive circuit and layout for CDM improvement," in *Proc. IEEE International Physical and Failure Analysis of Integrated Circuits Symp.*, 2009, pp. 228-232.

- [4] A. Righter, J. Salcedo, A. Olney, and T. Weyl, "CDM ESD current characterization - package variability effects and comparison to die-level CDM," in *Proc. EOS/ESD Symp.*, 2009, pp. 173-182.

- CDM," in *Proc. EOS/ESD Symp.*, 2009, pp. 173-182.

C.-Y. Lin and M.-D. Ker, "CDM ESD protection design with initial-on concept in nanoscale CMOS process," in *Proc. IEEE International Physical and Failure Analysis of Integrated Circuits Symp.*, 2010, pp. 193-196.

Figure 1. CDM ESD issues at I/O buffer and core circuit.

Figure 2. Test circuit without (with) inserting shielding between I/O line and core circuit 1 (core circuit 2).

### ACKNOWLEDGEMENT

This work was supported by National Science Council, Taiwan, under Contract NSC 98-2221-E-009-113-MY2, and by Ministry of Economic Affairs, Taiwan, under Grant 99-EC-17-A-01-S1-104. The authors would also like to thank TSMC University Shuttle Program for providing chip fabrication.

Figure 3. Layout top view of one test circuit for fabrication in a 65-nm CMOS process with 1-V devices.

Figure 4. PMOS of core circuit suffers serious CDM damage during CDM ESD event with positive charges.

Figure 5. SEM photo of failure point in core circuit 2 after 200-V CDM test.

Table I. CDM ESD robustness of test circuits with/without inserting the shielding line between I/O line and core line.

| Core Circuit 1 (Without Shielding) |           |            |            |            |                                          |                                          | Core Circuit 2 (With Shielding) |           |            |            |            |                                          |                                          |

|------------------------------------|-----------|------------|------------|------------|------------------------------------------|------------------------------------------|---------------------------------|-----------|------------|------------|------------|------------------------------------------|------------------------------------------|

| L<br>(µm)                          | S<br>(µm) | S1<br>(µm) | S2<br>(μm) | S3<br>(µm) | Positive<br>CDM ESD<br>Robustness<br>(V) | Negative<br>CDM ESD<br>Robustness<br>(V) | L<br>(µm)                       | S<br>(µm) | S1<br>(µm) | S2<br>(μm) | S3<br>(µm) | Positive<br>CDM ESD<br>Robustness<br>(V) | Negative<br>CDM ESD<br>Robustness<br>(V) |

| 20                                 | 0.78      | N/A        | N/A        | N/A        | 400                                      | < -600                                   | 20                              | 0.78      | 0.3        | 0.18       | 0.3        | 100                                      | < -600                                   |

| 20                                 | 1.98      | N/A        | N/A        | N/A        | > 600                                    | <-600                                    | 20                              | 1.98      | 0.3        | 0.18       | 1.5        | 100                                      | <-600                                    |

| 50                                 | 0.78      | N/A        | N/A        | N/A        | 400                                      | <-600                                    | 50                              | 0.78      | 0.3        | 0.18       | 0.3        | 100                                      | <-600                                    |

| 50                                 | 1.98      | N/A        | N/A        | N/A        | > 600                                    | <-600                                    | 50                              | 1.98      | 0.3        | 0.18       | 1.5        | 100                                      | <-600                                    |

| 100                                | 0.78      | N/A        | N/A        | N/A        | > 600                                    | < -600                                   | 100                             | 0.78      | 0.3        | 0.18       | 0.3        | 100                                      | <-600                                    |

| 100                                | 1.98      | N/A        | N/A        | N/A        | > 600                                    | <-600                                    | 100                             | 1.98      | 0.3        | 0.18       | 1.5        | 100                                      | <-600                                    |

<sup>\*</sup> The CDM test voltage was increased in 100-V step.

IRPS11-718 EL.2.2