# New Design on 2×VDD-Tolerant Power-Rail ESD Clamp Circuit with Low Standby Leakage in 65nm CMOS Process

Chih-Ting Yeh<sup>1,2</sup> and Ming-Dou Ker<sup>2,3</sup>

<sup>1</sup> Information and Communications Research Laboratories, Industrial Technology Research Institute, Hsinchu, Taiwan.

Abstract-A 2×VDD-tolerant power-rail electrostatic discharge (ESD) clamp circuit with only thin gate oxide 1V devices and silicon-controlled rectifier (SCR) as main ESD clamp device has been proposed and verified in a 65nm CMOS process. The proposed power-rail ESD clamp circuit has an ultra-low standby leakage current by reducing the voltage drop across the gate oxide of the devices in the ESD detection circuit. From the measured results, the proposed design with SCR dimension of 50μm in width can achieve 6.5kV human-body-model (HBM), 300V machine-model (MM) ESD levels, and an ultra-low standby leakage current of 34.1nA at room temperature under the normal circuit operating condition with 1.8V bias.

#### I. INTRODUCTION

With the continuously progressed CMOS technology, the number of transistors in a chip is aggressively increasing. Therefore, the system-on-a-chip (SoC) has become popular. For SoC integration, the input/output (I/O) circuits may receive or drive high-voltage signals to communicate with other integrated circuits (ICs) in a microelectronic system. However, the nanoscale device with thinner gate oxide and shallower diffusion junction depth arises several serious problems when it is implemented in the I/O circuits with mixed-voltage interfaces [1]. These problems include the gate oxide reliability [2], [3] and the undesirable leakage current paths [4], [5].

In 45nm CMOS technologies and beyond, the high-K materials have gradually replaced the silicon dioxide to reduce the equivalent oxide thickness (EOT) and the gate leakage current [6], [7]. However, the 90nm and 65nm CMOS technologies, which currently do not use the high-K materials as gate oxide layer, still suffer enormous gate leakage current issue. In order to solve the gate oxide reliability in the ESD protection circuit for the mixed-voltage I/O interfaces, the stacked-MOS configuration has been reported [8]. Other design strategies on high-voltage-tolerant power-rail ESD clamp circuit were also revealed to reduce the standby leakage current in nanometer CMOS technologies [9], [10].

In this work, a new low-leakage 2×VDD-tolerant powerrail ESD clamp circuit realized with only thin gate oxide devices for mixed-voltage I/O applications is proposed and verified in a 65nm CMOS technology. According to the experimental results, the standby leakage current of the proposed design can achieve the order of nano-ampere under the normal circuit operating condition.

# II. NEW PROPOSED 2×VDD-TOLERANT POWER-RAIL ESD CLAMP CIRCUIT WITH LOW STANDBY LEAKAGE

# A. Gate Leakage Current in Nanoscale CMOS

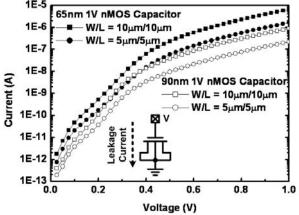

When the gate oxide thickness continuously scales down in advanced CMOS technology, the gate leakage current has become an inevitable issue. Based on the BSIM4 model [11] with the device parameters provided from foundry, the gate currents of the nMOS capacitors in 65nm and 90nm CMOS technologies are compared in Fig. 1. The gate currents of the nMOS capacitors with W/L of 5µm/5µm and 10µm/10µm are 217nA and 878nA (1.61µA and 6.48µA) at 1V in 90nm (65nm) technology, respectively. The gate current of the nMOS capacitor is directly dependent on the poly-gate area and the gate oxide thickness. Therefore, the gate leakage issue in 65nm CMOS technology is much worse than that in 90nm CMOS technology due to thinner gate oxide.

Fig. 1. Simulated gate currents of the nMOS capacitors in 65nm and 90nm CMOS technologies.

# B. Design Concept of New Proposed 2×VDD-Tolerant Power-Rail ESD Clamp Circuit

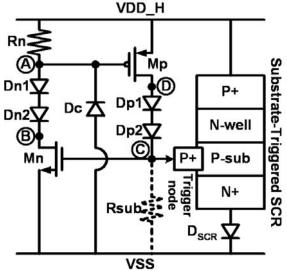

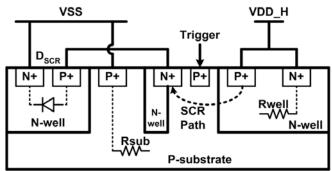

The proposed 2×VDD-tolerant power-rail ESD clamp circuit with the substrate-triggered SCR device [12] as the main ESD clamp device is shown in Fig. 2. The cross-sectional view of the substrate-triggered SCR device is also illustrated in Fig. 3. The SCR device without the poly-gate structure has very small leakage current. The ESD detection circuit is necessary to improve the turn-on speed of the SCR device under ESD stress condition. Therefore, the proposed ESD detection circuit with only thin gate oxide 1V devices for

<sup>&</sup>lt;sup>2</sup> Department of Electronics Engineering & Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan.

<sup>3</sup> Department of Electronic Engineering, I-Shou University, Kaohsiung, Taiwan.

2×VDD-tolerant applications has to be designed with considerations of gate oxide reliability. The main design concept is to reduce the voltage drop across the gate oxide of the devices in the ESD detection circuit. By following this main design concept, the gate leakage currents of the nMOS and pMOS in the ESD detection circuit can be well controlled to minimize the total standby leakage current.

Fig. 2. The proposed low-leakage 2×VDD-tolerant power-rail ESD clamp circuit with the substrate-triggered SCR as the ESD clamp device.

Fig. 3. Cross-sectional view of the ESD clamp device composed of the substrate-triggered SCR device with the cascode diode D<sub>SCR</sub>.

In Fig. 2, the Mp is used to generate the substrate-triggered current into the trigger node (node C in Fig. 2) of the SCR device during the ESD stress event. Under the normal circuit operating condition, the Mp is kept off and the trigger node is kept at VSS through the parasitic p-substrate resistor Rsub. Therefore, the SCR device is turned off during the normal circuit operating condition. The RC-based ESD-transient detection mechanism is realized by the Rn and the reversebiased diode Dc, which can distinguish the ESD stress event from the normal power-on condition. Compared to the thin gate oxide of MOS in the traditional RC circuit, the reversebiased diode Dc in the ESD detection circuit has no gate leakage current issue. The cascode diode D<sub>SCR</sub> is used to increase the holding voltage of the ESD clamp device to avoid the transient-induced latchup issue. The other diodes, Dn1, Dn2, Dp1, and Dp2, are used to reduce the voltage drop across the gate oxide of the Mn and Mp in the ESD detection circuit.

# C. Operation under the Normal Circuit Operating Condition

During the normal circuit operating condition with VDD\_H of 1.8V and grounded VSS, the gate voltage of Mp is biased at 1.8V through the resistor Rn. The gate voltage of Mn is biased at 0V through the p-substrate resistor Rsub of the SCR device. Because Mp is turned off, no trigger current is generated into the trigger node of the SCR device. By inserting the diode strings into the ESD detection circuit, the drain-to-gate and drain-to-source voltages of Mp and Mn can be less than 1V to effectively reduce the standby leakage current. Therefore, all 1V devices in the proposed ESD detection circuit are free from the gate oxide reliability issue under the normal circuit operating condition.

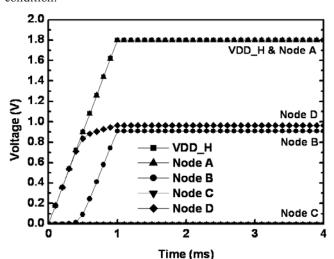

According to the device dimensions listed in Table I, the simulated voltage waveforms of the proposed ESD detection circuit during the normal power-on transition are shown in Fig. 4. VDD\_H is powered on from 0V to 1.8V with a rise time of 1ms. In Fig. 4, the gate-to-drain and drain-to-source voltages of all devices do not exceed the 1×VDD 1V range. Therefore, the proposed ESD detection circuit would not suffer the gate oxide reliability issue under the normal circuit operating condition.

Fig. 4. Simulated voltage waveforms at the nodes of the ESD detection circuit under the normal power-on condition with VDD\_H of 1.8V and a rise time of 1ms.

Table I Design Parameters of the Proposed Power-Rail ESD Clamp Circuit

| Design Parameters                      |               |    |    |  |

|----------------------------------------|---------------|----|----|--|

| $\operatorname{Rn}\left(\Omega\right)$ | 25k           |    |    |  |

| Mp (W/L)                               | 40μm / 0.12μm |    |    |  |

| Mn (W/L)                               | 8μm / 0.12μm  |    |    |  |

| Dp1 & Dp2 (μm²)                        | 24.40         |    |    |  |

| Dn1 & Dn2 (μm²)                        | 1.14          |    |    |  |

| De (μm²)                               | 156.75        |    |    |  |

| Widths of $D_{\text{SCR}}$ ( $\mu m$ ) | 30            | 40 | 50 |  |

| Widths of SCR (µm)                     | 30            | 40 | 50 |  |

# D. Operation under the ESD Transient Event

When a positive ESD-like transient voltage is applied to VDD\_H with grounded VSS, the *RC* time delay keeps the node A at a relatively low voltage level as compared with that at VDD H. Mp can be quickly turned on to generate the

trigger current into the trigger node (node C in Fig. 2) of the SCR device.

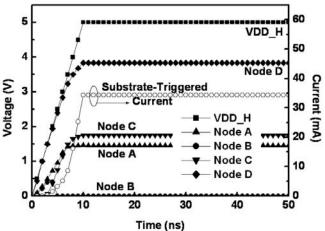

In order to simulate the transient edge of the HBM ESD event before the breakdown on the ESD protection devices, a 5V voltage pulse with a rise time of 10ns is applied to VDD\_H. The simulated transient voltage and the trigger current of the ESD detection circuit during the ESD transition are illustrated in Fig. 5. In the figure, Mp can be successfully turned on to generate the trigger current into the SCR device. Finally, the SCR device can be turned on to discharge the ESD current from VDD H to VSS.

Fig. 5. Simulated voltage waveforms at all nodes and the trigger current of the ESD detection circuit under the ESD-like transition condition with VDD H of 5V and a rise time of 10ns.

# III. EXPERIMENTAL RESULTS

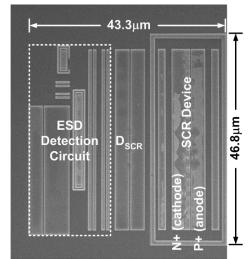

The new proposed 2×VDD-tolerant power-rail ESD clamp circuits have been fabricated in a 65nm fully silicided CMOS process by using only 1V devices. In order to avoid the ESD failure location occurring at  $D_{SCR}$ , the junction width of  $D_{SCR}$  and the width of SCR are the same. The microphotograph of the fabricated 2×VDD-tolerant power-rail ESD clamp circuit with the SCR device of  $40\mu m$  in width is shown in Fig. 6.

Fig. 6. The microphotograph of the fabricated 2×VDD-tolerant power-rail ESD clamp circuit with the SCR device of 40μm in width.

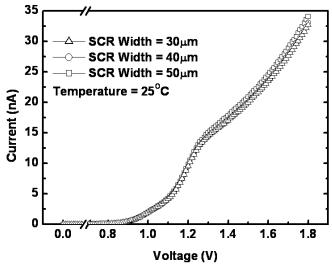

#### A. DC I-V Measurement

The DC I-V characteristic of the fabricated  $2\times VDD$ -tolerant power-rail ESD clamp circuit is shown in Fig. 7. At 1.8V normal operating voltage, the leakage currents of the proposed  $2\times VDD$ -tolerant power-rail ESD clamp circuits are 32.7, 33.1, and 34.1nA for the SCR widths of 30, 40, and 50 $\mu$ m, respectively, at the room temperature. In Fig. 7, the SCR device obviously contributes very small part to the total leakage current. In addition, the leakage current of the ESD detection circuit is reduced to the order of nano-ampere because the voltage drop across the gate oxide has been reduced by inserting the diode strings.

Fig. 7. The measured DC I-V curves of the 2×VDD-tolerant power-rail ESD clamp circuit with different SCR widths.

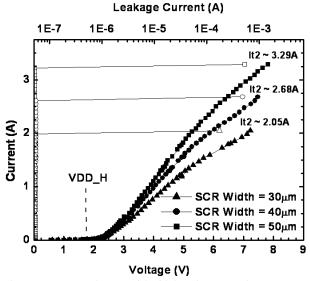

## B. TLP Measurement and ESD Robustness

The transmission line pulsing (TLP) generator [13] with a pulse width of 100ns and a rise time of ~2ns is used to measure the second breakdown current (It2) of the fabricated  $2\times VDD$ -tolerant power-rail ESD clamp circuit. The measured results are shown in Fig. 8. The power-rail ESD clamp circuit with the SCR device of  $50\mu m$  in width achieves the It2 value of 3.29A. In Fig. 8, the measured curves rise up after 2.1V, which is higher than the normal operating voltage VDD\_H of 1.8V. Therefore, the proposed  $2\times VDD$ -tolerant power-rail ESD clamp circuit has no latchup issue.

The It2, HBM, and MM ESD levels of the fabricated 2×VDD-tolerant power-rail ESD clamp circuit are listed in Table II. The proposed design with the SCR device of 50µm in width can achieve 6.5kV HBM and 300V MM ESD levels.

Table II ESD Robustness of the Fabricated Proposed Power-Rail ESD Clamp Circuit with Different SCR Widths

| Circuit With Billerent Scie Within |                |      |      |  |

|------------------------------------|----------------|------|------|--|

| 2×VDD-Tolerant<br>Power-Rail ESD   | SCR Width (μm) |      |      |  |

| Clamp Circuit                      | 30             | 40   | 50   |  |

| It2 (A)                            | 2.05           | 2.68 | 3.29 |  |

| HBM ESD Level (kV)                 | 3.5            | 5.0  | 6.5  |  |

| MM ESD Level (V)                   | 150            | 250  | 300  |  |

Fig. 8. TLP-measured curves of the fabricated 2×VDD-tolerant power-rail ESD clamp circuit with different SCR widths.

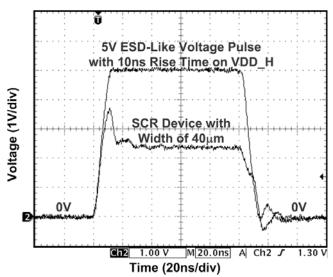

### C. Turn-On Verification

In order to observe the turn-on efficiency of the proposed power-rail ESD clamp circuit, an ESD-like voltage pulse with a rise time of 10ns and a pulse height of 5V is applied to the VDD H with the grounded VSS to simulate the rising edge of the HBM ESD pulse. The ESD detection circuit would be started to trigger on the SCR device. The triggered-on SCR device can provide a low impedance path from VDD H to VSS. The measured voltage waveforms on VDD H power line under ESD-like stress condition are shown in Fig. 9. In Fig. 9, the applied 5V voltage pulse is quickly clamped down to a low voltage level of  $\sim 2.4$ V. The turn-on time is  $\sim 5$ ns, which is estimated from the maximum voltage peak to the clamped low voltage level in Fig. 9. According to the measured voltage waveforms, the fabricated 2×VDD-tolerant power-rail ESD clamp circuit has been successfully verified with high turn-on efficiency during the ESD stress event.

Fig. 9. Measured voltage waveforms of the 2×VDD-tolerant ESD clamp circuit under ESD-like condition with 5V voltage pulse and 10ns rise time.

# IV. CONCLUSION

New design of 2×VDD-tolerant power-rail ESD clamp circuit with low standby leakage current has been proposed and successfully verified in a 65nm fully-silicided CMOS technology. The new proposed ESD detection circuit is realized with only 1V devices without suffering the gate oxide reliability issue under 1.8V (2×VDD) applications. According to the measured results, the proposed 2×VDD-tolerant power-rail ESD clamp circuit with the consideration of gate leakage current demonstrates a very small standby leakage current of only 34.1nA for the SCR device with a width of 50µm under 1.8V bias at 25°C. Moreover, the proposed power-rail ESD clamp circuit also performs excellent turn-on efficiency. The new proposed 2×VDD-tolerant power-rail ESD clamp circuit with low standby leakage current is considerably suitable for on-chip ESD protection in the mixed-voltage I/O interfaces.

### REFERENCES

- M.-D. Ker and S.-L. Chen, "Design of mixed-voltage I/O buffer by using NMOS-blocking technique," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 10, pp. 2324-2333, Oct. 2006.

- [2] B. Kaczer, R. Degraeve, M. Rasras, K. Van de Mieroop, P. J. Roussel, and G. Groeseneken, "Impact of MOSFET gate oxide breakdown on digital circuit operation and reliability," *IEEE Trans. on Electron Devices*, vol. 49, no. 3, pp. 500-506, Mar. 2002.

- [3] Y. Luo, D. Nayak, D. Gitlin, M.-Y. Hao, C.-H. Kao, and C.-H. Wang, "Oxide reliability of drain engineered I/O NMOS from hot carrier injection," *IEEE Electron Device Letters*, vol. 24, no. 11, pp. 686-688, Nov. 2003.

- [4] C.-T. Wang and M.-D. Ker, "Design of power-rail ESD clamp circuit with ultra-low standby leakage current in nanoscale CMOS technology," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 3, pp. 956-964, Mar. 2009

- [5] P.-Y. Chiu, M.-D. Ker, F.-Y. Tsai, and Y.-J. Chang, "Ultra-low-leakage power-rail ESD clamp circuit in nanoscale low-voltage CMOS process," in *Proc. IEEE Int. Rel. Phys. Symp.*, 2009, pp. 750-753.

- [6] Y.-Y. Fan, Q. Xiang, J. An, L. F. Register, and S. K. Banerjee, "Impact of interfacial layer and transition region on gate current performance for high-K gate dielectric stack: Its tradeoff with gate capacitance," *IEEE Trans. on Electron Devices*, vol. 50, no. 2, pp. 433-439, Feb. 2003.

- [7] J. Huang, P. D. Kirsch, J. Oh, S. H. Hoon, P. Majhi, H. R. Harris, D. C. Gilmer, G. Bersuker, D. Heh, C. S. Park, C. Park, H.-H. Tseng, and R. Jammy, "Mechanisms limiting EOT scaling and gate leakage of high-k/metal gate stacks directly on SiGe," *IEEE Electron Device Letters*, vol. 30, no. 3, pp. 285-287, Mar. 2009.

- [8] M.-D. Ker and W.-J. Chang, "ESD protection design with on-chip ESD bus and high-voltage-tolerant ESD clamp circuit for mixed-voltage I/O buffers," *IEEE Trans. on Electron Devices*, vol. 55, no. 6, pp. 1409-1416, Jun. 2008.

- [9] C.-T. Wang and M.-D. Ker, "Design of 2xVDD-tolerant power-rail ESD clamp circuit with consideration of gate leakage current in 65-nm CMOS technology," *IEEE Trans. on Electron Devices*, vol. 57, no. 6, pp. 1460-1465, Jun. 2010.

- [10]M.-D. Ker and C.-Y. Lin, "High-voltage-tolerant ESD clamp circuit with low standby leakage in nanoscale CMOS process," *IEEE Trans. on Electron Devices*, vol. 57, no. 7, pp. 1636-1641, Jul. 2010.

- [11] BSIM Model, Berkeley Short-Channel IGFET Model. [Online]. Available: http://www-device.eecs.berkeley.edu/~bsim3/bsim4.html

- [12]M.-D. Ker and K.-C. Hsu, "Latchup-free ESD protection design with complementary substrate-triggered SCR devices," *IEEE Journal of Solid-State Circuits*, vol. 38, no. 8, pp. 1380-1392, Aug. 2003.

- State Circuits, vol. 38, no. 8, pp. 1380-1392, Aug. 2003.

[13]T. J. Maloney and N. Khurana, "Transmission line pulsing techniques for circuit modeling of ESD phenomena," in *Proc. of EOS/ESD Symp.*, 1985, pp. 49-54.