# On-Chip ESD Protection Designs in RF Integrated Circuits for Radio and Wireless Applications

Ming-Dou Ker and Chun-Yu Lin

Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan

Abstract — CMOS technology has been used to implement the radio and wireless integrated circuits. However, the thinner gate oxide in nanoscale CMOS technology seriously degrades the electrostatic discharge (ESD) robustness. Therefore, on-chip ESD protection designs must be added at all input/output pads in CMOS chip. To minimize the impacts from ESD protection design on circuit performances, ESD protection at input/output pads must be carefully designed. A review on ESD protection designs with low parasitic capacitance for radio and wireless applications is presented in this paper. The comparisons among these ESD protection designs are also discussed.

*Index Terms* — Electrostatic discharge (ESD), low capacitance, radio-frequency (RF).

#### I. INTRODUCTION

All wireless communication products must meet the reliability specifications during mass production. Electrostatic discharge (ESD), which was one of the most important reliability issues during mass production, must be taken into consideration [1]. All integrated circuits used in the wireless communication products need to be equipped with ESD protection designs. However, ESD protections cause radiofrequency (RF) performance degradation with several undesired effects. Parasitic capacitance is one of the most important design considerations for RF ICs. A typical specification for an RF circuit on human-body-model (HBM) ESD robustness and the maximum parasitic capacitance of ESD protection device are 2 kV and 200 fF, respectively [2], [3]. As the operating frequencies of RF circuits increase, the parasitic capacitance was more strictly limited.

In this paper, several ESD protection designs on ICs with very low parasitic capacitance for wireless communication applications are reviewed and compared.

# II. ESD PROTECTION DESIGNS WITH LOW PARASITIC CAPACITANCE

#### A. ESD Protection Diodes

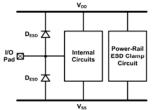

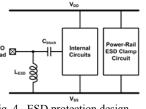

Fig. 1 shows the ESD protection scheme with diodes ( $D_{ESD}$ ) at I/O pad and the power-rail ESD clamp circuit between  $V_{DD}$  and  $V_{SS}$  [4]. Under positive-to- $V_{DD}$  (PD) or negative-to- $V_{SS}$  (NS) ESD stresses, ESD current is discharged through the forward-biased  $D_{ESD}$ . During positive-to- $V_{SS}$  (PS) ESD stress, ESD current is discharged from the I/O pad through the forward-biased  $D_{ESD}$  to  $V_{DD}$ , and discharged to the grounded  $V_{SS}$  through the power-rail ESD clamp circuit. Similarly,

during negative-to- $V_{DD}$  (ND) ESD stress, ESD current is discharged from the  $V_{DD}$  through the power-rail ESD clamp circuit and the forward-biased  $D_{ESD}$  to the I/O pad. However, the parasitic capacitance of the ESD protection diodes is directly contributed at the I/O pad, which may be too large to be tolerated for RF circuits.

#### B. Stacked ESD Protection Diodes

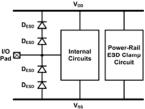

The ESD protection diodes in stacked configuration had been presented, as shown in Fig. 2 [5]. With two stacked ESD protection diodes, the overall parasitic capacitance theoretically becomes half. More stacked ESD diodes leads to more significant parasitic capacitance reduction. However, this technique is adverse to ESD protection because the turnon resistance and the clamping voltage of the stacked ESD protection diodes during ESD stresses are increased as well.

#### C. Parallel LC Resonator

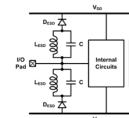

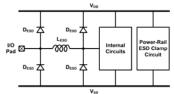

The parallel LC resonator can be realized as shown in Fig. 3 [6]. The inductor ( $L_{\rm ESD}$ ) can resonate with the parasitic capacitance of  $D_{\rm ESD}$ . The inductor also serves as an ESD protection device between I/O pad and  $V_{\rm DD}$ . The placement of the inductor and the ESD protection diode can be interchanged to provide the same function. Since the inductor is dc short, a dc blocking capacitor ( $C_{\rm block}$ ) is required to provide a separated dc bias for the internal circuits.

### D. ESD Protection Inductor

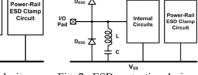

ESD protection design for RF circuits by using inductor as the ESD protection device had been reported, as shown in Fig. 4 [7]. Since the frequency component of ESD current is much lower than that of the RF signal, the inductor can pass the ESD current while block the RF signal. To efficiently sink the ESD current, the metal width of the  $L_{\rm ESD}$  should be wide enough to enhance the current handling capability. Besides, a dc blocking capacitor ( $C_{\rm block}$ ) is needed to provide a separated dc bias for the internal circuits.

### E. Series LC Resonator

ESD protection design utilizing the series LC resonator is shown in Fig. 5 [8]. At high frequencies, the  $L_{\rm ESD}$  dominates the impedance of the series resonator. Thus, wideband ESD protection can be achieved by designing the application band of the series LC resonator to cover the frequency band of the RF signal. During ESD stresses, the ESD current can be discharged through the  $L_{\rm ESD}$  and  $D_{\rm ESD}$ . However, the transient

Fig. 1. ESD protection design by diodes.

Fig. 2. ESD protection design by stacked diodes.

Fig. 5. ESD protection design by series LC resonator.

Fig. 6. ESD protection design by LC-tank.

Fig. 7. ESD protection design by modified LC-tank.

Fig. 3. ESD protection design

by parallel LC resonator.

Fig. 4. ESD protection design by inductor.

Fig. 8. Distributed ESD protection scheme.

voltage across the series L<sub>ESD</sub> and D<sub>ESD</sub> should be reduced to improve the ESD robustness.

#### F. LC-Tank

As shown in Fig. 6, a pair of the LC-tanks is placed at the I/O pad [9]. At the resonant frequency of the LC-tank, there is ideally infinite impedance from the signal path to the ESD protection diodes. Consequently, the parasitic capacitances of the ESD diodes are isolated, which can mitigate the parasitic effects from the ESD protection diodes. However, the transient voltage across the LC-tank ESD protection circuit should be reduced to improve the ESD robustness.

## G. Modified LC-Tank

Fig. 7 shows the circuit design of modified LC-tank ESD protection [10]. The series LC is designed to resonate at low frequency. At the frequency above the resonant frequency, the inductance dominates the impedance of the series LC, and then the inductance can eliminate the parasitic capacitance of the ESD protection diodes.

# H. Distributed ESD Protection Diodes

The distributed ESD protection scheme had been presented, as shown in Fig. 8 [11]. With the ESD protection diodes divided into small sections and matched by the inductor, such a distributed ESD protection scheme can achieve wideband impedance matching. The number of ESD protection diodes can be varied to optimize the performance.

# III. CONCLUSION

A comprehensive review in the field of ESD protection design with low parasitic capacitance for RF integrated circuits is presented. The on-chip ESD protection designs for RF circuits will continuously be an important design task, as the operating frequencies of RF circuits increase.

#### ACKNOWLEDGEMENT

This work was supported by National Science Council, Taiwan, under Contract NSC 101-2221-E-009-141, and by the "Aim for the Top University Plan" of National Chiao Tung University and Ministry of Education, Taiwan.

#### REFERENCES

- [1] S. Voldman, ESD: RF Technology and Circuits, John Wiley & Sons,

- D. Linten et al., "A 5-GHz fully integrated ESD-protected low-noise amplifier in 90-nm RF CMOS," IEEE J. Solid-State Circuits, vol. 40, no. 7, pp. 1434-1442, Jul. 2005.

- C. Richier et al., "Investigation on different ESD protection strategies devoted to 3.3 V RF applications (2 GHz) in a 0.18 µm CMOS process," J. Electrostatics, vol. 54, no. 1, pp. 55-71, Jan. 2002.

- [4] M. Tsai et al., "A wideband low noise amplifier with 4 kV HBM ESD protection in 65 nm RF CMOS," IEEE Microwave and Wireless Components Letters, vol. 19, no. 11, pp. 734-736, Nov. 2009.

- M.-D. Ker et al., "ESD protection design for CMOS RF integrated circuits," in Proc. EOS/ESD Symp., 2001, pp. 346-354.

- S. Hyvonen et al., "Comprehensive ESD protection for RF inputs," [6] Microelectronics Reliability, vol. 45, no. 2, pp. 245-254, Feb. 2005.

- K. Raczkowski et al., "50-to-67GHz ESD-protected power amplifiers in digital 45nm LP CMOS," in IEEE International Solid-State Circuits Conf. Dig. Tech. Papers, 2009, pp. 382-383.

- [8] B. Huang et al., "Design and analysis for a 60-GHz low-noise amplifier with RF ESD protection," IEEE Trans. Microwave Theory and Techniques, vol. 57, no. 2, pp. 298-305, Feb. 2009.

- M.-D. Ker et al., "A novel LC-tank ESD protection design for giga-Hz RF circuits," in Proc. IEEE Radio Frequency Integrated Circuits Symp., 2003, pp. 115-118.

- [10] C.-Y. Lin et al., "Modified LC-tank ESD protection design for 60-GHz RF applications," in Proc. European Conference on Circuit Theory and Design, 2011, pp. 57-60.

- [11] C.-Y. Lin et al., "Self-matched ESD cell in CMOS technology for 60-GHz broadband RF applications," in Proc. IEEE Radio Frequency Integrated Circuits Symp., 2010, pp. 573-576.