# ESD Protection Design with Low-Leakage Consideration for Silicon Chips of IoT Applications

Ming-Dou Ker<sup>1</sup>, Chun-Yu Lin<sup>2</sup>, Yi-Han Wu<sup>1</sup>, and Wen-Tai Wang<sup>3</sup>

<sup>1</sup> Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan

<sup>2</sup> Department of Electrical Engineering, National Taiwan Normal University, Taipei, Taiwan

<sup>3</sup> Global Unichip Corporation, Hsinchu, Taiwan

Abstract—On-chip electrostatic discharge (ESD) protection design with low-leakage consideration for the silicon chips of IoT applications is presented. The proposed ESD protection design uses the fast turn-on silicon-controlled rectifier (SCR) device to implement the power-rail ESD clamp circuit. Experimental results verified in TSMC 28nm CMOS process have shown that the proposed design has advantages of low leakage current (2~3nA), low trigger voltage (~2V), high ESD robustness (>8kV), and free to latchup issue.

Kevwords— CMOS; electrostatic discharge (ESD); ESD protection; low-leakage.

#### I. Introduction

The low-power integrated circuits (ICs) are needed for the internet of things (IoT) applications. Therefore, the electrostatic discharge (ESD) protection circuits with the feature of low leakage / low power are needed for the silicon chips of IoT applications [1]. However, the ICs are very sensitive to ESD events, especially those fabricated by the advanced nanoscale CMOS technology [2]. To provide the required ESD robustness for silicon chips of IoT applications, where the IoT environments would be the fields without any ESD control, the ESD protection circuits should be equipped at all pads of a chip which may be stressed by ESD pulses.

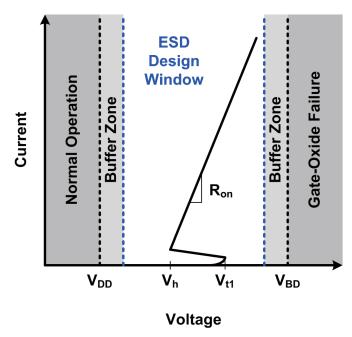

The ESD protection circuit should be carefully designed into an ESD design window, as shown in Fig. 1 [3]. The ESD design window is defined by the power-supply voltage (V<sub>DD</sub>) and the gate-oxide breakdown voltage  $\left(V_{BD}\right)$  of MOSFET with typically 10~20% buffer zones. Therefore, the trigger voltage  $(V_{t1})$  and holding voltage  $(V_h)$  of ESD protection circuit must be lower than  $0.8x\sim0.9x~V_{BD}$  to prevent the internal circuits from damage before the ESD protection circuit is turned on during ESD stresses. Besides, the Vt1 and the Vh must be higher than  $1.1x \sim 1.2x \ V_{DD}$  to prevent the ESD protection circuit from being mis-triggered under normal-circuit-operating conditions. Moreover, the turn-on resistance (Ron) of ESD protection circuit should be minimized to reduce the joule heat generated in the ESD protection circuit and the clamping voltage of the ESD protection circuit during ESD stresses. For a 28nm CMOS technology, the ESD design window should be within  $\sim 1 \text{ V}$  and  $\sim 5 \text{ V}$  [4].

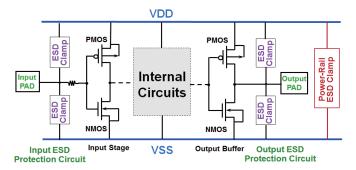

To achieve effective ESD protection, the typical whole-chip ESD protection design for silicon chips is shown in Fig. 2, where the power-rail ESD clamp circuit is the key circuit to

achieve whole-chip ESD protection [5]. In addition, with the advantages of high ESD robustness, compact layout area, and latchup free in low-voltage applications, the silicon-controlled rectifier (SCR) device has been reported to be a useful component for on-chip ESD protection in CMOS ICs [6]. The conventional SCR device in CMOS processes consists of a P+ region, N-well, P-well, and N+ region. To efficiently discharge the ESD current from anode to cathode through the SCR device, several gate-bounded SCR devices had been reported [7]-[9]. The ability of SCR device that can be quickly triggered on to clamp the overstress voltage to a safe low voltage level is one of the major important design considerations for on-chip ESD protection in the advanced CMOS processes. Thus, an effective design to reduce the trigger voltage of SCR device is needed.

In this work, two fast turn-on SCR devices with low trigger voltage, low leakage current, free to latchup, and fully process-compatible to general CMOS processes are proposed. Such fast turn-on SCR devices are used in the power-rail ESD clamp circuits to sustain high ESD stress in the IoT field applications.

Fig. 1. ESD design window defined by the power-supply voltage  $(V_{\text{DD}})$  and the gate-oxide breakdown voltage  $(V_{\text{BD}})$  with 10~20% buffer zones.

Fig. 2. Whole-chip ESD protection with I/O and power-rail ESD clamp circuits

#### II. CONVENTIONAL SCR DEVICE FOR ESD PROTETION

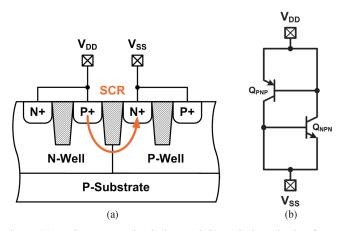

The device structure of the conventional SCR device used between V<sub>DD</sub> and V<sub>SS</sub> is illustrated in Fig. 3(a). The V<sub>DD</sub> pad is connected to the first P+ and the pickup N+, which are formed in the N-well. The V<sub>SS</sub> pad is connected to the second N+ and the pickup P+, which are formed in the nearby P-well. The SCR path between V<sub>DD</sub> and V<sub>SS</sub> consists of P+, N-well, P-well, and N+. The equivalent circuit of the SCR consists of a PNP BJT (Q<sub>PNP</sub>) and an NPN BJT (Q<sub>NPN</sub>), as shown in Fig. 3(b). The Q<sub>PNP</sub> is formed by the P+, N-well, and P-well, and the Q<sub>NPN</sub> is formed by the N-well, P-well, and N+. As ESD zapping from V<sub>DD</sub> to V<sub>SS</sub>, the positive-feedback regenerative mechanism of Q<sub>PNP</sub> and Q<sub>NPN</sub> results in the SCR device highly conductive to make SCR very robust against ESD stresses. Under normal circuit -operating conditions, the SCR path remain off to prevent from leakage. However, SCR has some drawbacks, such as higher trigger voltage and slower turn-on speed. To reduce the trigger voltage of an SCR device, the trigger signal can be sent into the base terminal of Q<sub>NPN</sub> to enhance the turnon speed. The voltage level of the trigger port is in reverse proportion to the trigger voltage of the SCR device. Therefore, some circuit design techniques are reported to enhance the turn-on efficiency of SCR devices [7]-[20]. However, an SCR device with a low trigger voltage, low leakage current, and which requires no additional process step for ESD protection is still needed.

Fig. 3. (a) Device cross-sectional view, and (b) equivalent circuit, of SCR device used between  $\rm V_{DD}$  and  $\rm V_{SS}.$

# III. PROPOSED LOW-LEAKAGE-CURRENT AND FAST-TURN-ON SCR DEVICE FOR ESD PROTETION

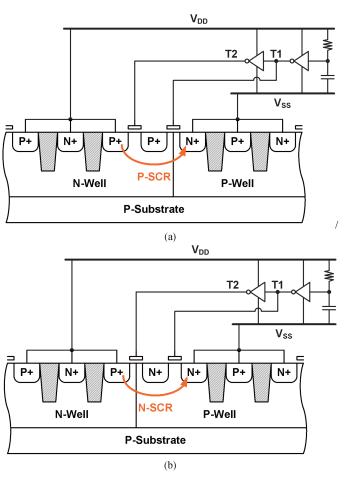

Two low-leakage-current and fast-turn-on SCR devices (P-SCR and N-SCR) are presented in this work. In each fast turnon SCR device, two gates are embedded into device structure to separate its anode and cathode. One gate lies on the N-well/Pwell junction, and the other lies on the N-well (P-well) to form a PMOS (NMOS) in the P-SCR (N-SCR) device, as shown in Figs. 4(a) and 4(b), respectively. To reduce the turn-on voltage of the P-SCR (N-SCR) device under ESD stress conditions, the gates in P-SCR (N-SCR) device are controlled by the ESD detection circuit. As shown in Fig. 4, both ESD detection circuits consist of a resistor-capacitor (R-C) timer and two inverters to generate the trigger voltages at the nodes of T1 and T2. The trigger mechanism of both P-SCR and N-SCR devices are similar. When ESD pulse is zapping to  $V_{DD}$  with  $V_{SS}$ grounded, the T1 is initially kept at high voltage to induce the N-type channel, and T2 is initially kept at low voltage to induce the P-type channel. These two induced channels form the trigger currents to trigger SCR on. The turned-on SCR can discharge ESD current efficiently to protect the internal circuits inside the silicon chip. Under the normal circuit-operating conditions, the voltage levels of T1 and T2 nodes remain at V<sub>SS</sub> and V<sub>DD</sub>, respectively, those keep SCR off. The leakage current through the SCR in off state is very small.

Fig. 4. Proposed ESD protection design with (a) P-SCR and (b) N-SCR.

#### IV. EXPERIMENTAL RESULTS

Both power-rail ESD clamp circuits designed with P-SCR and N-SCR devices have been fabricated in a TSMC 28nm CMOS process. The dimension (width) of each SCR device is drawn as 120 $\mu$ m in layout, the RC time constant is 100ns, and the width of PMOS (NMOS) in each inverter is 14 $\mu$ m (6 $\mu$ m).

The human-body-model (HBM) ESD robustness of each circuit is tested. Both the circuits with P-SCR and N-SCR have been double confirmed to pass the HBM ESD test of 8kV.

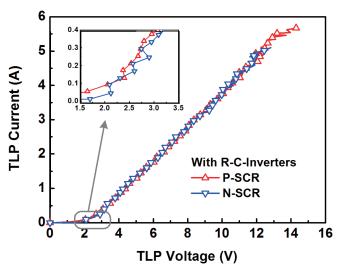

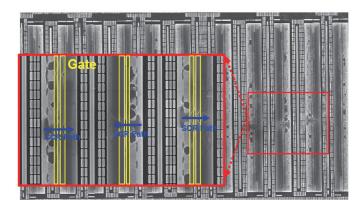

A transmission-line-pulsing (TLP) system with 10-ns rise time and 100-ns pulse width is used to investigate the I-V characteristics of the test devices. Figure 5 shows the TLP-measured I-V curves of both ESD circuits. The P-SCR and N-SCR can be triggered on at ~2V. After TLP tests, the scanning electron microscope (SEM) was used to find the failure locations. Figure 7 shows the SEM photographs of P-SCR device after TLP tests. The failure points are located at the SCR paths.

Fig. 5. TLP-measured I-V curves of the proposed ESD protection design with P-SCR or N-SCR.

Fig. 6. SEM photo of P-SCR after TLP tests.

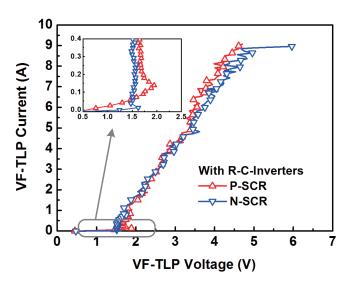

Another very-fast TLP (VF-TLP) system with 0.2-ns rise time and 5-ns pulse width is used to evaluate the effectiveness of the proposed devices in faster ESD -transient events (charged-device-model, CDM). Figure 7 shows the VF-TLP-measured I-V curves of both ESD circuits, where both P-SCR and N-SCR can be turned on fast enough to provide CDM ESD protection.

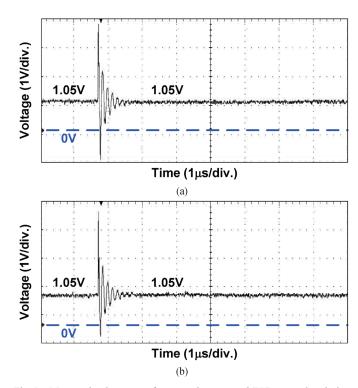

The P-SCR (N-SCR) has a holding voltage of  $\sim\!1.7V~(1.5V)$  that prevent the latchup issue in the given 28nm CMOS process with  $V_{DD}$  of 1.05V for normal circuit operations. To verify latchup immunity, the fabricated ESD protection circuits are tested by the transient-induced latchup (TLU) method [21]. Figure 8 shows the measured transient voltage waveforms of the ESD circuits under TLU test with a charging voltage of 10V. After the TLU tests, the voltage across the ESD circuits are still stayed at 1.05V ( $V_{DD}$ ). Based on the TLU test results, the proposed ESD circuits with P-SCR (N-SCR) are confirmed to immune from the latchup issue.

Under normal circuit operating conditions with  $V_{DD}$  of 1.05V, the leakage current of the fabricated ESD circuit with PSCR (N-SCR) is measured and listed in Table I, which is very small of only 3.1nA (2.5nA).

Fig. 7. VF-TLP-measured I-V curves of the proposed ESD protection design with P-SCR or N-SCR.

| TABLE I. DEVICE DIMENSIONS AND TEST RESULTS OF |

|------------------------------------------------|

| PROPOSED ESD CIRCUITS.                         |

| ESD Protection Design               | with P-SCR | with N-SCR |

|-------------------------------------|------------|------------|

| Device Width                        | 120µm      | 120µm      |

| HBM ESD Robustness                  | >8kV       | >8kV       |

| TLP I <sub>t2</sub>                 | 5.62A      | 5.05A      |

| VF-TLP I <sub>t2</sub>              | 8.98A      | 8.89A      |

| Leakage at 1.05V (V <sub>DD</sub> ) | 3.1nA      | 2.5nA      |

Fig. 8. Measured voltage waveforms on the proposed ESD protection design with (a) P-SCR, and (b) N-SCR, under TLU tests.

#### V. CONCLUSION

On-chip ESD protection designs with P-SCR or N-SCR devices to achieve low leakage current, low trigger voltage, fast turn-on speed, high ESD level, and free to latchup are presented and successfully verified in a 28nm CMOS process. The proposed ESD protection solution is highly suitable for the silicon chips of IoT applications in nanoscale CMOS process.

## ACKNOWLEDGMENT

This work was supported in part by Global Unichip Corporation, Taiwan, and in part by Ministry of Science and Technology, Taiwan, under Contracts of MOST 105-2221-E-009-166 and MOST 106-2622-8-009-007-TE1.

## REFERENCES

- [1] P. Magarshack, "Breakthrough technologies and reference designs for new IoT applications," in *VLSI Circuits Digest of Technical Papers*, 2015, pp. C42-C43.

- [2] C. Duvvury, "ESD qualification changes for 45nm and beyond," in *IEDM Technical Digest*, 2008, pp. 337-340.

- [3] Y. Yang, R. Gauthier, K. Chatty, J. Li, R. Mishra, S. Mitra, and D. Ioannou, "Degradation of high-k metal gate nMOSFETs under ESD-like stress in a 32-nm technology," *IEEE Trans. Device and Materials Reliability*, vol. 11, no. 1, pp. 118-125, Mar. 2011.

- [4] C.-Y. Lin, M.-D. Ker, P.-H. Chang, and W.-T. Wang, "Study on the ESD-induced gate-oxide breakdown and the protection solution in 28nm high-k metal-gate CMOS technology," in *Proc. IEEE Nanotechnology*

- Materials and Devices Conference, 2015, pp. 63-66.

- [5] M.-D. Ker, "Whole-chip ESD protection design with efficient VDD-to-VSS ESD clamp circuit for submicron CMOS VLSI," *IEEE Trans. Electron Devices*, vol. 46, no.1, pp. 173-183, Jan. 1999.

- [6] M.-D. Ker and K.-C. Hsu, "Overview of on-chip electrostatic discharge protection design with SCR-based devices in CMOS integrated circuits," *IEEE Trans. Device and Materials Reliability*, vol. 5, no. 2, pp. 235-249, Jun. 2005.

- [7] T. Chang, Y. Hsu, T. Tsai, J. Tseng, J. Lee, and M. Song, "High-k metal gate-bounded silicon controlled rectifier for ESD protection," in *Proc.* EOS/ESD Symp., 2012.

- [8] S. Parthasarathy, J. Salcedo, and J. Hajjar, "A low leakage poly-gated SCR device for ESD protection in 65nm CMOS process," in *Proc. IEEE International Reliability Physics Symp.*, 2013.

- [9] C.-Y. Lin, Y.-H. Wu, and M.-D. Ker, "Low-leakage and low-trigger-voltage SCR device for ESD protection in 28-nm high-k metal gate CMOS process," *IEEE Electron Device Letters*, vol. 37, no. 11, pp. 1387-1390, Nov. 2016.

- [10] S. Jang, M. Gau, and J. Lin, "Novel diode-chain triggering SCR circuits for ESD protection," *Solid-State Electronics*, vol. 44, no. 7, pp 1297-1303, Jul. 2000.

- [11] S. Jang, L. Lin, S. Li, and H. Chen, "Dynamic triggering characteristics of SCR-type electrostatic discharge protection circuits," *Solid-State Electronics*, vol. 45, no. 7, pp. 1091-1097, Jul. 2001.

- [12] J. Lee, Y. Wu, K. Peng, R. Chang, T. Yu, and T. Ong "The embedded SCR NMOS and low capacitance ESD protection device for selfprotection scheme and RF application," in *Proc. IEEE Custom Integrated Circuits Conf.*, 2002, pp. 93-96.

- [13] M. Mergens, C. Russ, K. Verhaege, J. Armer, P. Jozwiak, R. Mohn, B. Keppens, and C. Trinh, "Speed optimized diode-triggered SCR (DTSCR) for RF ESD protection of ultra-sensitive IC nodes in advanced technologies," *IEEE Trans. Device and Materials Reliability*, vol. 5, no. 3, pp. 532-542, Sep. 2005.

- [14] M.-D. Ker and K.-H. Lin, "ESD protection design for I/O cells with embedded SCR structure as power-rail ESD clamp device in nanoscale CMOS technology," *IEEE J. Solid-State Circuits*, vol. 40, no. 11, pp. 2329-2338, Nov. 2005.

- [15] W.-Y. Chen, E. Rosenbaum, and M.-D. Ker, "Diode-triggered siliconcontrolled rectifier with reduced voltage overshoot for CDM ESD protection," *IEEE Trans. Device and Materials Reliability*, vol. 12, no. 1, pp. 10-14, Mar. 2012.

- [16] C.-Y. Lin, L.-W. Chu, and M.-D. Ker, "ESD protection design for 60-GHz LNA with inductor-triggered SCR in 65-nm CMOS process," *IEEE Trans. Microwave Theory and Techniques*, vol. 60, no. 3, pp. 714-723, Mar. 2012.

- [17] R. Sun, Z. Wang, M. Klebanov, W. Liang, J. Liou, and D. Liu, "Silicon-controlled rectifier for electrostatic discharge protection solutions with minimal snapback and reduced overshoot voltage," *IEEE Electron Device Letters*, vol. 36, no. 5, pp. 424-426, May 2015.

- [18] C.-Y. Lin and R.-K. Chang, "Design of ESD protection device for K/Kaband applications in nanoscale CMOS process," *IEEE Trans. Electron Devices*, vol. 62, no. 9, pp. 2824-2829, Sep. 2015.

- [19] F. A. Altolaguirre and M.-D. Ker, "Low-leakage bidirectional SCR with symmetrical trigger circuit for ESD protection in 40-nm CMOS process," *IEEE Trans. on Device and Materials Reliability*, vol. 16, no. 4, pp. 549-555, Dec. 2016.

- [20] C.-Y. Lin and C.-Y. Chen, "Resistor-triggered SCR device for ESD protection in high-speed I/O interface circuits," *IEEE Electron Device Letters*, vol. 38, no. 6, Jun. 2017.

- [21] M.-D. Ker and S.-F. Hsu, "Component-level measurement for transient-induced latchup in CMOS ICs under system-level ESD considerations," *IEEE Trans. on Device and Materials Reliability*, vol. 6, no. 3, pp. 461-472, Sep. 2006.