# Study on the ESD-Induced Gate-Oxide Breakdown and the Protection Solution in 28nm High-K Metal-Gate CMOS Technology

Chun-Yu Lin<sup>1</sup>, Ming-Dou Ker<sup>2</sup>, Pin-Hsin Chang<sup>2</sup>, and Wen-Tai Wang<sup>3</sup>

<sup>1</sup>Department of Electrical Engineering, National Taiwan Normal University, Taiwan <sup>2</sup>Institute of Electronics, National Chiao Tung University, Taiwan <sup>3</sup>Global Unichip Corporation, Taiwan

Abstract—To protect the IC chips against the electrostatic discharge (ESD) damages in 28nm high-k metal-gate (HKMG) CMOS technology, the ESD protection consideration was studied in this work. The ESD design window was found to be within 1V and 5.1V in 28nm HKMG CMOS technology. An ESD protection device of PMOS with embedded silicon-controlled rectifier (SCR) was investigated to be suitable for ESD protection in such narrow ESD design window.

*Index Terms*—CMOS, electrostatic discharge (ESD), high-k metal-gate (HKMG), silicon-controlled rectifier (SCR).

# I. INTRODUCTION

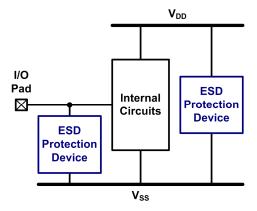

As CMOS technologies keep scaling down, the thin oxide thickness of MOS transistors has made the integrated circuits to be sensitive to the electrostatic discharge (ESD) [1]. A typical specification for IC chips on human-body-model (HBM) ESD robustness is 2kV [2]. In order to protect the IC chips against the ESD damages, on-chip ESD protection devices must be equipped for the pads that may be stressed by ESD. The typical on-chip ESD protection design is shown in Fig. 1, which consists of the ESD protection devices between input/output (I/O) pad and V<sub>DD</sub>/V<sub>SS</sub>, and between V<sub>DD</sub> and V<sub>SS</sub> [3]. Although the high-k metal-gate has been introduced in sub-50nm CMOS technologies, the MOS transistors are still sensitive to ESD [4]. Moreover, because the average cost of a die in sub-50nm technologies is expensive, it is important to optimize ESD protection devices to have a high ESD robustness within limited cell area.

To discharge the high ESD energy without causing damage to internal circuits, the typical ESD protection devices include the diode, MOS, and silicon-controlled rectifier (SCR) [5]-[7]. The SCR device has been reported to be useful for ESD protection due to its high ESD robustness, small device size, and excellent clamping capabilities (low holding voltage and small turn-on resistance) [7]. Besides, the SCR device can be safely used without latchup danger in advanced CMOS technologies with the low supply voltage [8]. Moreover, a PMOS with embedded SCR device has been presented to have low trigger voltage [9]. In this work, the PMOS with embedded SCR device is further investigated.

Fig. 1. On-chip ESD protection against ESD damages.

# II. ESD-INDUCED GATE-OXIDE BREAKDOWN

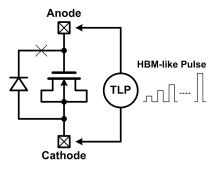

To investigate the gate-oxide breakdown voltage, an NMOS was fabricated in the 28nm high-k metal-gate CMOS process. When a metal wire contacted to the transistor gate, it can charge up to a voltage sufficient to zap the thin gate oxide. In order to protect the gate-oxide from damage during the metal wire contacted to the transistor gate, the NMOS with a protection diode was fabricated in the same time, and then the protection diode was removed by using the focused ion beam (FIB). After the protection diode was removed, the breakdown voltage of intrinsic gate oxide can be evaluated, as shown in Fig. 2.

Fig. 2. Test device to evaluate the gate-oxide breakdown voltage of the MOSFET.

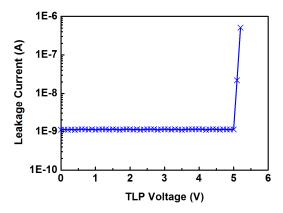

A transmission-line-pulsing (TLP) system with a 10ns rise time and a 100ns pulse width is used to evaluate the gate-oxide breakdown voltage in the time domain of HBM ESD event. Fig. 3 shows the measured leakage current under 0.9V bias of the test device after TLP test. As indicated by the leakage-current evolution of the stressed gate oxide, the damage occurs at the breakdown voltage of 5.1V.

Fig. 3. Measured leakage current under 0.9V bias of test device after TLP test.

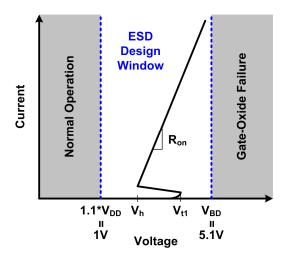

Fig. 4. ESD design window defined by the power-supply voltage with 10% variation (1.1\* $V_{DD}$ ) and the gate-oxide breakdown voltage ( $V_{BD}$ ) of the MOSFET.

# III. ESD DESIGN WINDOW

To achieve effective ESD protection, the ESD protection device should be carefully designed. Fig. 4 shows the ESD design window of an IC [10], which is defined by the power-supply voltage with 10% variation  $(1.1*V_{DD})$  and the gate-oxide breakdown voltage  $(V_{BD})$  of MOSFET. First, the trigger voltage  $(V_{t1})$  and holding voltage  $(V_h)$  of ESD protection device must be lower than the gate-oxide breakdown voltage of MOSFET to prevent the internal circuits from damage before the ESD protection device is turned on during ESD stresses. Second, the trigger voltage and holding voltage of the ESD protection device must be higher than the power-supply voltage of the IC to prevent the ESD protection devices from

being mis-triggered under normal circuit operating conditions. Moreover, the turn-on resistance ( $R_{on}$ ) of ESD protection device should be minimized to reduce the joule heat generated in the ESD protection device and the clamping voltage of the ESD protection device during ESD stresses. In the given 28nm high-k metal-gate CMOS technology of this work, the ESD design window is within 1V ( $V_{DD} = 0.9V$ ) and 5.1V.

# IV. PMOS WITH EMBEDDED SCR DEVICE FOR ESD PROTECTION

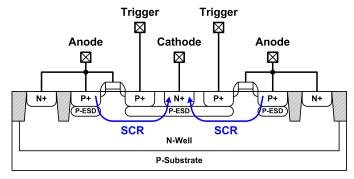

The PMOS with embedded SCR is used as ESD protection device. The device cross-sectional view of the PMOS with embedded SCR is shown in Fig. 5, where the P-ESD denotes the p-type ESD implantation [11]. This implantation was typically used to improve the turn-on ability of ESD protection NMOS. The SCR path consists of P+, N-well, P-ESD, and N+. The equivalent circuit of the SCR consists of a PNP BJT and a NPN BJT. The PNP is formed by the P+, N-well, and P-ESD, and the NPN is formed by the N-well, P-ESD, and N+. The P-ESD layer at anode side is used to enlarge the SCR path. At cathode side, the silicide blocking is used between N+ and P+. Beside, the P-ESD layer at cathode side is used to isolate the N-well and N+ region. As ESD zapping from anode to cathode, the positive-feedback regenerative mechanism of PNP and NPN results in the SCR device highly conductive to make SCR very robust against ESD stresses.

To reduce the trigger voltage of an SCR device, the trigger current can be sent into the base terminal of NPN in the SCR device. The trigger current is inversely related to the trigger voltage of the SCR device; therefore, some trigger techniques have been reported [7]. To investigate the relationship between the trigger current and the trigger voltage, the trigger pad is connected to the PMOS device with embedded SCR, as shown in Fig. 5.

Fig. 5. Cross-sectional view of PMOS with embedded SCR device.

# V. VERIFICATION IN SILICON

To verify the PMOS with embedded SCR device in silicon chip, a 28nm high-k metal-gate CMOS process is used in this work. The widths of the test devices are selected to be  $120\mu m$  and  $360\mu m$ .

#### A. ESD Robustness

The HBM ESD robustness is tested according to the ESDA/JEDEC joint standard [12]. The ESD energy is stressed from anode to cathode of the test devices. The trigger pad is kept floating during ESD tests. The failure criterion is defined as the I-V curve seen between test pads shifting over 30% from its original curve after ESD stressed at every ESD test level. According to the measurement results, the PMOS with embedded SCR with 120µm and 360µm widths can pass 5kV and 8kV HBM ESD tests, respectively.

#### B. TLP I-V Characteristics

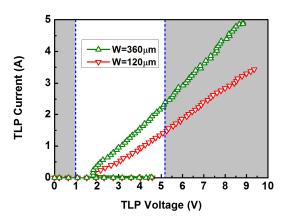

The TLP system with 10ns rise time and 100ns pulse width is used to evaluate the trigger voltage ( $V_{t1}$ ), holding voltage ( $V_h$ ), turn-on resistance ( $R_{on}$ ), and secondary breakdown current ( $I_{t2}$ ) of the test devices in the time domain of HBM ESD event. The ratio between HBM ESD robustness and  $I_{t2}$  is typically  $1.5k\Omega$ , because the peak HBM current is assumed to be equal to the HBM pre-charge voltage divided by  $1.5 k\Omega$  [13]. The TLP-measured I-V curves of the test devices without additional trigger current are shown in Fig. 6. The test devices with 120 $\mu$ m and 360 $\mu$ m widths can be triggered on at about 4.6V. The trigger voltage is lower than the gate-oxide breakdown voltage. The holding voltages of the test devices are about 1.7V, which is higher than the power-supply voltage and safe from the latchup issue. All measured characteristics of the test devices are listed in Table I.

Fig. 6. Measured TLP I-V curves.

Table I Summary on Measurement Results

|                       | PMOS with Embedded SCR |             |

|-----------------------|------------------------|-------------|

| Width                 | 120µm                  | 360µm       |

| HBM ESD<br>Robustness | 5kV                    | 8kV         |

| TLP V <sub>t1</sub>   | 4.58V                  | 4.55V       |

| TLP V <sub>h</sub>    | 1.66V                  | 1.74V       |

| TLP Ron               | $4.2\Omega$            | $1.5\Omega$ |

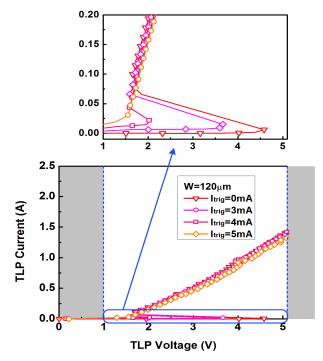

## C. Trigger Mechanism

The dc trigger current (I<sub>trig</sub>) was injected into the trigger pad of the test devices, as measuring the TLP I-V curves. Fig. 7 shows the TLP-measured I-V curves of the test device with 120µm width under different trigger currents. According to the measurement results, the trigger voltage of the test device can be further reduced with the larger trigger current. If the trigger current is continually increased, the trigger voltage of the proposed device will be reduced to a value close to its holding voltage. Besides, the trigger current will not degrade the holding voltage, and turn-on resistance of the test device.

Fig. 7. Measured TLP I-V curves of test device with  $120\mu m$  width under different trigger currents.

# D. Transient-Induced Latchup (TLU) Test

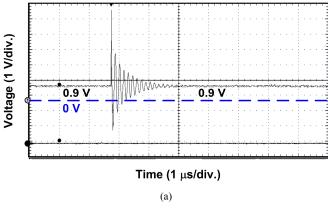

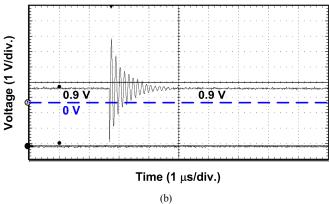

If the ESD protection device is used between V<sub>DD</sub> and V<sub>SS</sub>, the latchup immunity should be considered. To evaluate the latchup immunity of the proposed device, the transientinduced latchup (TLU) was tested [14]. A 200pF charging capacitor is used to store the charges as the TLU-triggering source, and then the stored charges are discharged to the test device through the relay. Figs. 8(a) and 8(b) show the measured transient voltage waveforms of the test device with 120µm width under the TLU tests with charging voltage of +10V and -10V, respectively. Before the TLU tests, the voltage across the test device was 0.9V, which is the V<sub>DD</sub> voltage in the given CMOS process. During the TLU tests, the measured voltage waveforms are influenced simultaneously by the underdamped sinusoidal voltage. After the TLU tests, the voltage across the test device was returned to 0.9V. From the TLU test results, the test device can immune to the latchup.

Fig. 8. Measured voltage waveforms on test device with  $120\mu m$  width under TLU tests with charging voltage of (a) +10V and (b) -10V.

### VI. CONCLUSION

The ESD protection device of PMOS with embedded SCR has been designed, fabricated, and characterized in a 28nm high-k metal-gate CMOS process. This device combines P+/P-ESD, N-well, P-ESD, and N+ to form the embedded SCR path. Verified in silicon chip, the test device with  $120\mu\text{m}/360\mu\text{m}$  width has 5kV/8kV HBM ESD robustness, 4.58V/4.55V trigger voltage, 1.66V/1.74V holding voltage, and  $4.2\Omega/1.5\Omega$  turn-on resistance. Besides, the test device has been tested to be free from latchup event. Therefore, the PMOS with embedded SCR can be a better solution for ESD protection in 28nm HKMG CMOS process.

# ACKNOWLEDGMENT

This work was supported by Global Unichip Corporation (GUC), Taiwan, by Biomedical Electronics Translational Research Center, National Chiao Tung University, Taiwan, and by Ministry of Science and Technology, Taiwan, under Contract MOST 104-2220-E-009-004, MOST 103-2221-E-009-197-MY2, and MOST 104-2622-E-009-003. The authors would like to thank the employees of GUC for their great help in supporting the joint development project.

#### REFERENCES

- [1] J. Wu and E. Rosenbaum, "Gate oxide reliability under ESD-like pulse stress," *IEEE Trans. Electron Devices*, vol. 51, no. 7, pp. 1192-1196, Jul. 2004.

- [2] D. Linten, S. Thijs, M. Natarajan, P. Wambacq, W. Jeamsaksiri, J. Ramos, A. Mercha, S. Jenei, S. Donnay, and S. Decoutere, "A 5-GHz fully integrated ESD-protected low-noise amplifier in 90-nm RF CMOS," *IEEE J. Solid-State Circuits*, vol. 40, no. 7, pp. 1434-1442, Jul. 2005.

- [3] M.-D. Ker, "Whole-chip ESD protection design with efficient VDD-to-VSS ESD clamp circuit for submicron CMOS VLSI," *IEEE Trans. Electron Devices*, vol. 46, no. 1, pp. 173-183, Jan. 1999.

- [4] Y. Yang, R. Gauthier, K. Chatty, J. Li, R. Mishra, S. Mitra, and D. Ioannou, "Degradation of high-k metal gate nMOSFETs under ESD-like stress in a 32-nm technology," *IEEE Trans. Device and Materials Reliability*, vol. 11, no. 1, pp. 118-125, Mar. 2011.

- [5] Y. Li, J. Liou, J. Vinson, and L. Zhang, "Investigation of LOCOS- and polysilicon-bound diodes for robust electrostatic discharge (ESD) applications," *IEEE Trans. Electron Devices*, vol. 57, no. 4, pp. 814-819, Apr. 2010.

- [6] S. Dong, X. Du, Y. Han, M. Huo, Q. Cui, and D. Huang, "Analysis of 65 nm technology grounded-gate NMOS for onchip ESD protection applications," *Electronics Letters*, vol. 44, no. 19, pp. 1129-1130, Sep. 2008.

- [7] C.-Y. Lin, L.-W. Chu, and M.-D. Ker, "ESD protection design for 60-GHz LNA with inductor-triggered SCR in 65-nm CMOS process," *IEEE Trans. Microwave Theory and Techniques*, vol. 60, no. 3, pp. 714-723, Mar. 2012.

- [8] G. Bosefli, V. Reddy, and C. Duvvury, "Latch-up in 65nm CMOS technology: a scaling perspective," in *Proc. IEEE International Reliability Physics Symp.*, 2005, 137-144.

- [9] C.-Y. Lin, P.-H. Chang, and R.-K. Chang, "Improving ESD robustness of PMOS device with embedded SCR in 28-nm high-k/metal gate CMOS process," *IEEE Trans. Electron Devices*, vol. 62, no. 4, pp. 1349-1352, Apr. 2015.

- [10] C. Duvvury, "ESD qualification changes for 45nm and beyond," in *IEEE Int. Electron Devices Meeting Dig. Tech. Papers*, 2008, pp. 337-340.

- [11] M.-D. Ker, C.-H. Chuang, and W.-Y. Lo, "ESD implantations for on-chip ESD protection with layout consideration in 0.18µm salicided CMOS technology," *IEEE Trans. Semiconductor Manufacturing*, vol. 18, no. 2, pp. 328-337, May 2005.

- [12] ANSI/ESD/JEDEC JS-001-2014, "For Electrostatic Discharge Sensitivity Testing – Human Body Model (HBM) - Component Level," ESDA & JEDEC, 2014.

- [13] J. Barth, K. Verhaege, L. Henry, and J. Richner, "TLP calibration, correlation, standards, and new techniques," *IEEE Trans. Electronics Packaging Manufacturing*, vol. 24, no. 2, pp. 99-108, Apr. 2001.

- [14] M.-D. Ker and S.-F. Hsu, "Component-level measurement for transient-induced latchup in CMOS ICs under system-level ESD considerations," *IEEE Trans. Device and Materials Reliability*, vol. 6, no. 3, pp. 461-472, Sep. 2006.