## 【19】中華民國 【12】專

【12】專利公報 (B)

【11】證書號數: I541976

【45】公告日: 中華民國 105 (2016) 年 07 月 11 日

[51] Int. Cl.: H01L25/04 (2014.01) H01L23/52 (2006.01)

發明 全5頁

【54】名 稱:三維積體電路封裝

THREE-DIMENSION (3D) INTEGRATED CIRCUIT (IC) PACKAGE

【21】申請案號:102147441 【22】申請日:中華民國 102 (2013) 年 12 月 20 日 【11】公開編號:201523833 【43】公開日期:中華民國 104 (2015) 年 06 月 16 日

【30】優先權: 2013/12/12 美國 14/104,251

【72】發 明 人: 柯明道 (TW) KER, MING DOU; 莊哲豪 (TW) CHUANG, CHE HAO 【71】申 請 人: 晶焱科技股份有限公司 AMAZING MICROELECTRONIC

CORP.

新北市中和區中正路 736 號 6 樓之 6

【74】代理人: 林火泉

【56】參考文獻:

TW 200818518A US 2007/0279824A1

US 2012/0182650A1

審查人員:劉守禮

## [57]申請專利範圍

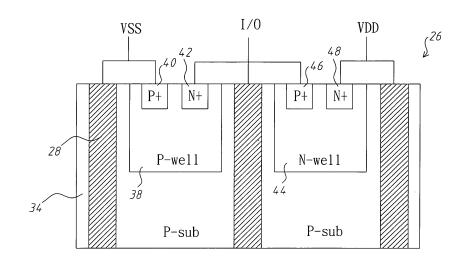

- 1. 一種三維積體電路封裝,包含:一封裝基板,其係具有一表面,且至少一積體電路(IC) 晶片與至少一暫態電壓抑制(TVS)晶片設於該表面上,且彼此電性連接,該積體電路晶片與該暫態電壓抑制晶片互相獨立;複數個導電栓,其係設於該暫態電壓抑制晶片中;複數個第一導電凸塊,其係設於該表面之導電區域上,且每一該第一導電凸塊分別位於每一該導電栓下方,該暫態電壓抑制晶片經由該些第一導電凸塊與該些導電栓電性連接該導電區域;以及複數個第二導電凸塊,每一該第二導電凸塊分別位於每一該導電栓上,且該積體電路晶片經由該些第一導電凸塊、該些第二導電凸塊與該些導電栓電性連接該導電區域與該暫態電壓抑制晶片;其中該暫態電壓抑制晶片更包含:一P型半導體基板,該些導電栓係設於該P型半導體基板中;一P型井區,其係設於該P型半導體基板中,且一第一P型重摻雜區與一第一N型重摻雜區設於該P型井區中;以及一N型井區,其係設於該P型半導體基板中,且一第一P型重摻雜區與一第二N型重摻雜區設於該N型井區中,又該P型井區與該N型井區彼此獨立。

- 2. 如請求項1所述之三維積體電路封裝,其中該些第一導電凸塊與該些第二導電凸塊之材質為鉛或錫,該些導電栓之材質為銅。

- 3. 如請求項1所述之三維積體電路封裝,其中一該導電栓連接一高電壓端,另一該導電栓連接一低電壓端,其餘該導電栓連接輸入輸出接腳(I/O pins)。

## 圖式簡單說明

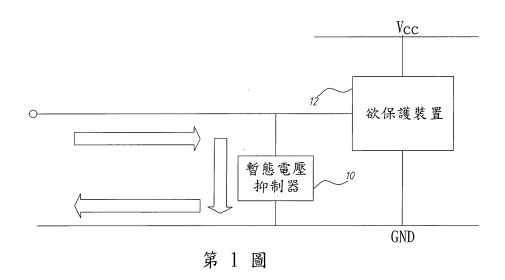

- 第1圖為先前技術之連接欲保護電路之暫態電壓抑制器的電路示意圖。

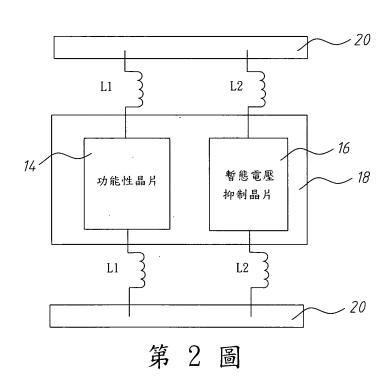

- 第2圖為先前技術之具有暫態電壓抑制器之二維系統封裝示意圖。

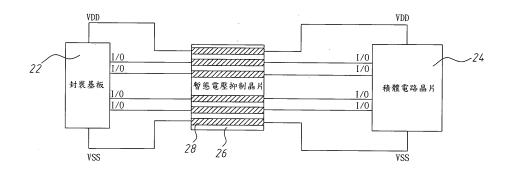

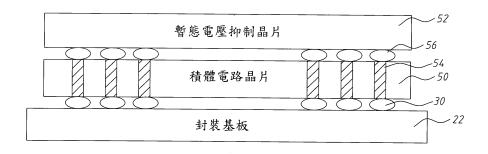

- 第3圖為本發明之第一實施例之結構示意圖。

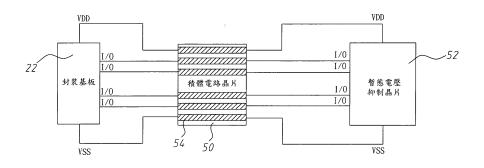

- 第 4 圖為本發明之第一實施例之三維積體電路封裝電性連接高電壓端、低電壓端與輸入輸出接腳之示意圖。

- 第5圖為本發明之第一實施例之暫態電壓抑制晶片之結構示意圖。

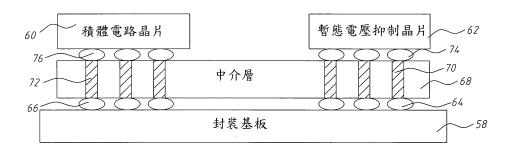

- 第6圖為本發明之第二實施例之結構示意圖。

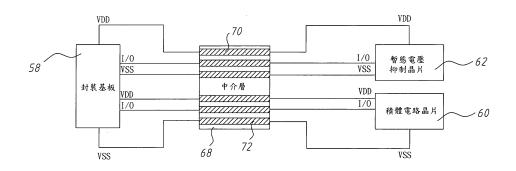

- 第7圖為本發明之第二實施例之三維積體電路封裝電性連接高電壓端、低電壓端與輸入輸出接腳之示意圖。

- 第8圖為本發明之第三實施例之結構示意圖。

- 第9圖為本發明之第三實施例之三維積體電路封裝電性連接高電壓端、低電壓端與輸入輸出接腳之示意圖。

第 3 圖

第 4 圖

第 5 圖

(4)

第6圖

第7圖

第 8 圖

第 9 圖