## 【19】中華民國

## 【12】專利公報 (B)

【11】證書號數: I594334

【45】公告日: 中華民國 106 (2017) 年 08 月 01 日

[51] Int. Cl.: H01L21/336 (2006.01) H01L29/36 (2006.01)

H01L29/772 (2006.01)

發明 全 10 頁

【54】名 稱:半導體裝置及其製造方法

SEMICONDUCTOR DEVICE AND METHOD OF MANUFACTURING THE

**SAME**

【21】申請案號:104137285 【22】申請日:中華民國104(2015)年11月12日

【11】公開編號:201717283 【43】公開日期: 中華民國 106 (2017) 年 05 月 16 日

【72】發明人: 尼迪 卡魯納 (IN) NIDHI, KARUNA; 艾 飛 (AR) ALTOLAGUIRRE,

FEDERICO AGUSTIN;柯明道(TW)KER, MING DOU;林耿立(TW)LIN,

**GEENG LIH**

【71】申 請 人: 世界先進積體電路股份有限公司 VANGUARD INTERNATIONAL

SEMICONDUCTOR CORPORATION

新竹縣新竹科學工業園區園區三路 123 號

【74】代理人: 洪澄文;顏錦順

【56】參考文獻:

TW 201131759A1 TW 201212208A1 WO 2006/053055A2 WO 2009/108311A2

審查人員:何立瑋

## 【57】申請專利範圍

- 1. 一種半導體裝置,包括:一基板;一井區,設於該基板中,且具有一第一導電型;一隔離結構,設於該基板中,且環繞該井區中的一主動區;一源極區,設於該主動區中及該井區中;一汲極區,設於該主動區中及該井區中;一汲極區,設於該主動區中及該井區中,且沿著該主動區之一邊緣設置,其中該第一導電型與該第二導電型不同;一第二導電型第二摻雜區,設於該井區中,且設於該源極區、該汲極區及該第二導電型第一摻雜區之下,其中該第二導電型第二摻雜區與該第二導電型第一摻雜區直接接觸;一源極電極,電性連接該源極區;一汲極電極,電性連接該汲極區;及一閘極電極,電性連接該第二導電型第一摻雜區。

- 2. 如申請專利範圍第1項所述之半導體裝置,其中該源極區與該汲極區並未直接接觸該第二導電型第二摻雜區。

- 3. 如申請專利範圍第1項所述之半導體裝置,其中該源極區與該汲極區直接接觸該第二導電型第二摻雜區。

- 4. 如申請專利範圍第1項所述之半導體裝置,其中該第二導電型第一摻雜區直接接觸該隔離結構。

- 5. 如申請專利範圍第1項所述之半導體裝置,其中該第二導電型第一摻雜區及該第二導電型第二摻雜區共同於該井區隔離出一隔離次井區(isolated sub-well region),其中該源極區與該汲極區係設於該隔離次井區中。

- 6. 如申請專利範圍第 5 項所述之半導體裝置,其中該隔離次井區包圍該源極區與該汲極區,且該第二導電型第一摻雜區包圍該隔離次井區。

- 7. 如申請專利範圍第5項所述之半導體裝置,其中該隔離次井區包括位於該源極區與該汲極區之間的一通道區,且該通道區之寬度小於該源極區之寬度與該汲極區之寬度。

- 8. 如申請專利範圍第7項所述之半導體裝置,其中該第二導電型第一摻雜區包括至少一閘 極區,該閘極區鄰接該通道區。

- 9. 如申請專利範圍第8項所述之半導體裝置,其中該第二導電型第一摻雜區包括兩個閘極區,其中個閘極區係設於該通道區之相反側,且該兩個閘極區鄰接該通道區。

- 10. 如申請專利範圍第8項所述之半導體裝置,其中該閘極電極係設於該閘極區之上。

- 11. 一種半導體裝置之製造方法,包括:提供一基板;形成一井區於該基板中,其中該井區 且具有一第一導電型;形成一隔離結構於該基板中,其中該隔離結構環繞該井區中的一 主動區;形成一源極區於該主動區中及該井區中;形成一汲極區於該主動區中及該井區 中;形成一第二導電型第一摻雜區於該井區中,其中該第二導電型第一摻雜區沿著該主 動區之一邊緣設置,其中該第一導電型與該第二導電型不同;形成一第二導電型第二摻 雜區於該井區中,且該第二導電型第二摻雜區係設於該源極區、該汲極區及該第二導電 型第一摻雜區之下,其中該第二導電型第二摻雜區與該第二導電型第一摻雜區直接接 觸;形成一源極電極,該源極電極電性連接該源極區;形成一汲極電極,該汲極電極電 性連接該汲極區;及形成一閘極電極,該閘極電極電性連接該第二導電型第一摻雜區。

- 12. 如申請專利範圍第 11 項所述之半導體裝置之製造方法,其中該源極區與該汲極區並未直接接觸該第二導電型第二摻雜區。

- 13. 如申請專利範圍第 11 項所述之半導體裝置之製造方法,其中該源極區與該汲極區直接接觸該第二導電型第二摻雜區。

- 14. 如申請專利範圍第 11 項所述之半導體裝置之製造方法,其中該第二導電型第一摻雜區直接接觸該隔離結構。

- 15. 如申請專利範圍第 11 項所述之半導體裝置之製造方法,其中該第二導電型第一摻雜區及該第二導電型第二摻雜區共同於該井區隔離出一隔離次井區(isolated sub-well region),其中該源極區與該汲極區係設於該隔離次井區中。

- 16. 如申請專利範圍第 15 項所述之半導體裝置之製造方法,其中該隔離次井區包圍該源極區 與該汲極區,且該第二導電型第一摻雜區包圍該隔離次井區。

- 17. 如申請專利範圍第 15 項所述之半導體裝置之製造方法,其中該隔離次井區包括位於該源極區與該汲極區之間的一通道區,且該通道區之寬度小於該源極區之寬度與該汲極區之 寬度。

- 18. 如申請專利範圍第 17 項所述之半導體裝置之製造方法,其中該第二導電型第一摻雜區包括至少一閘極區,該閘極區鄰接該通道區。

- 19. 如申請專利範圍第 18 項所述之半導體裝置之製造方法,其中該第二導電型第一摻雜區包括兩個閘極區,其中個閘極區係設於該通道區之相反側,且該兩個閘極區鄰接該通道區。

- 20. 如申請專利範圍第 18 項所述之半導體裝置之製造方法,置,其中該閘極電極係設於該閘極區之上。

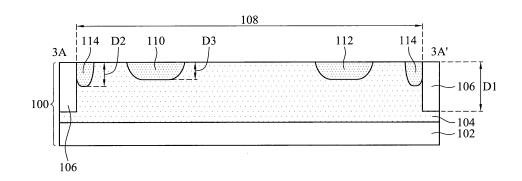

## 圖式簡單說明

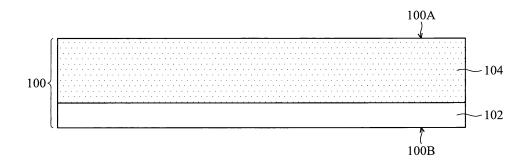

第1圖係顯示根據本揭露一些實施例所述之半導體裝置之製造方法其中一步驟之半導體 裝置之剖面圖。

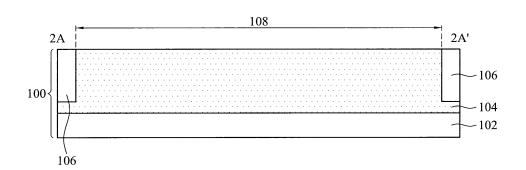

第 2A-2B 圖係顯示根據本揭露一些實施例所述之半導體裝置之製造方法其中一步驟之半導體裝置之剖面圖及上視圖。

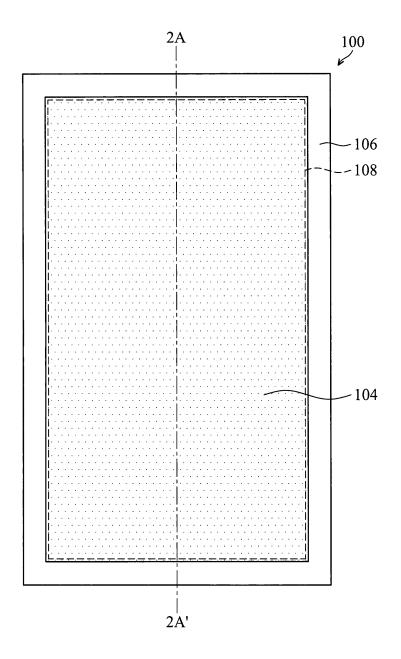

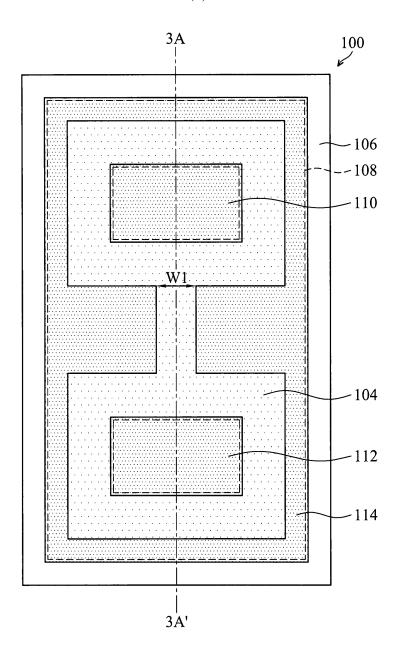

第 3A-3B 圖係顯示根據本揭露一些實施例所述之半導體裝置之製造方法其中一步驟之半導體裝置之剖面圖及上視圖。

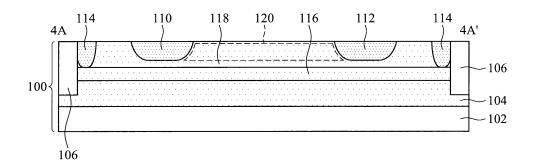

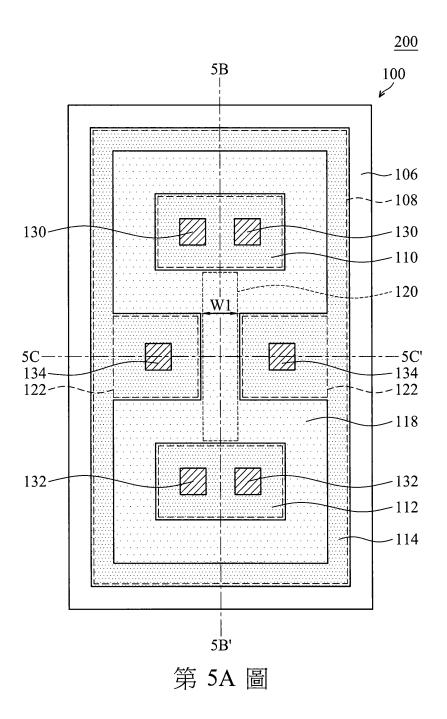

第 4A-4B 圖係顯示根據本揭露一些實施例所述之半導體裝置之製造方法其中一步驟之半導體裝置之剖面圖及上視圖。

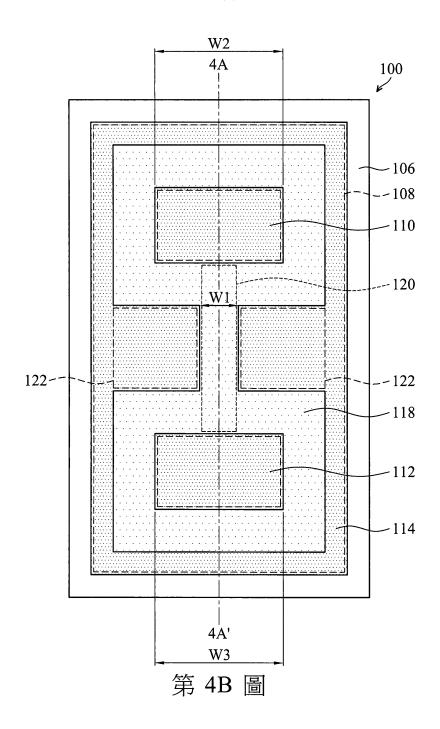

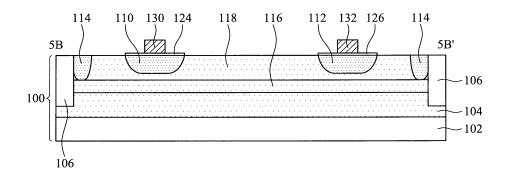

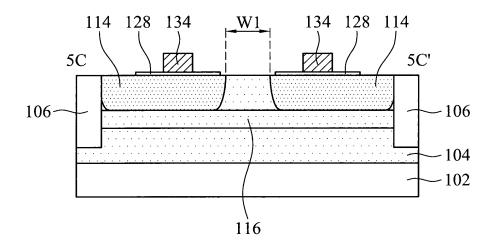

第 5A-5C 圖係顯示根據本揭露一些實施例所述之半導體裝置之製造方法其中一步驟之半導體裝置之剖面圖及上視圖。

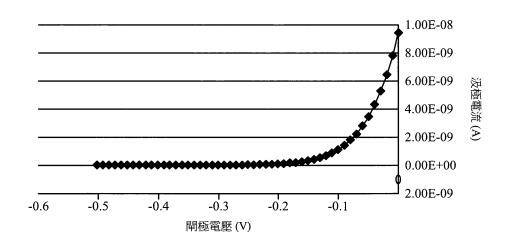

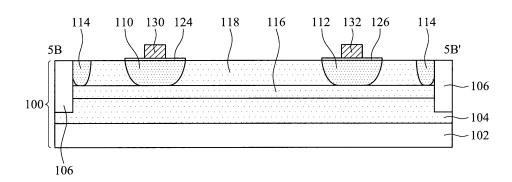

第6圖係顯示根據本揭露一些實施例所述之半導體裝置之閘極電壓對電流之分析圖。第7圖係本揭露另一實施例之半導體裝置之剖面圖。

第1圖

第 2A 圖

第 2B 圖

第 3A 圖

第 3B 圖

第 4A 圖

<u>200</u>

第 5B 圖

<u>200</u>

第 5C 圖

第6圖

<u>200</u>

第7圖