## 【19】中華民國

## 【12】專利公報 (B)

【11】證書號數:I319230

【45】公告日: 中華民國 99 (2010) 年 01 月 01 日 【51】Int. Cl.: *H01L23/60 (2006.01)*

發明 全 16 頁

【54】名 稱:用於晶片靜電放電防護之高速觸發矽控整流元件

INITIAL-ON SCR DEVICE FOR ON-CHIP ESD PROTECTION

【21】申請案號:095111817 【22】申請日:中華民國 95 (2006) 年 04 月 03 日 【11】公開編號:200705641 【43】公開日期:中華民國 96 (2007) 年 02 月 01 日

【30】優先權: 2005/07/21 美國 11/186,086

【72】發明人: 柯明道 (TW) KER, MING DOU; 陳世宏 (TW) CHEN, SHIH HUNG; 林昆

賢 (TW) LIN, KUN SHIEN

【71】申 請 人: 財團法人工業技術研究院 INDUSTRIAL TECHNOLOGY

RESEARCH INSTITUTE

新竹縣竹東鎮中興路 4 段 195 號

【74】代理人: 洪澄文;顏錦順

【56】參考文獻:

TW 224863 TW 437051 TW 561608 TW 1231032

US 6882009B2 US 2002/0122280 US 2004/0042143A1 US 2004/0100746A1

US 2004/0232492A1

## [57]申請專利範圍

- 1. 一種用於靜電放電(ESD)防護之半導體元件,其包括:一矽控整流器(SCR),其包括:一半導體基體;一形成於該基體中的第一井;一形成於該基體中的第二井;一形成於該第一井中以用作一陽極之第一,型區域;一形成於該第一井中的 p 型金屬氧化物半導體(PMOS)電晶體,其包括一閘極、一第一擴散區域及一與該第一擴散區域分開的第二擴散區域;一形成於該第一井中並電連接至該 PMOS 電晶體之該第一擴散區域的第二 p 型區域。

- 2. 如申請專利範圍第 1 項所述之元件,其中在一靜電放電事件發生之前,將該 PMOS 電晶體之該閘極保持於一參考電壓位準。

- 3. 如申請專利範圍第 1 項所述之元件,其中該 PMOS 電晶體之該閘極係電連接至一靜電放電偵測電路。

- 4. 如申請專利範圍第 3 項所述之元件,其中該靜電放電偵測電路包括一電阻器及一電容器。

- 5. 如申請專利範圍第 1 項所述之元件,其中該第二 n 型區域包括複數個形成於該第一井中的子區域。

- 6. 如申請專利範圍第 5 項所述之元件,其中該複數個子區域係藉由該 PMOS 電晶體之該第一擴散區域而彼此分開。

- 7. 如申請專利範圍第 1 項所述之元件,其中形成於該第一井中的該 PMOS 電晶體之該第二 擴散區域以及形成於該基體中的該第二 p 型區域係形成於一整體 p 型區域中。

- 8. 如申請專利範圍第 5 項所述之元件,其中該複數個子區域係藉由該 PMOS 電晶體之該第二擴散區域而彼此分開。

- 9. 如申請專利範圍第 8 項所述之元件,其中形成於該第一井中的該 PMOS 電晶體之該第二 擴散區域以及形成於該基體中的該第二 p 型區域係形成於一整體 p 型區域中。

- 10. 一種用於靜電放電(ESD)防護之半導體元件,其包括:一半導體基體;一形成於該基體中的 n 型井; 一形成於該 n 型井中的 p 型金屬氧化物半導體(PMOS)電晶體,其包括一閘極、一第一擴散區域及一與該第一擴散區域分開的第二擴散區域;一形成於該 n 型井中並電連接至該 PMOS 電晶體之該第一擴散區域的 n 型區域;以及一形成於該基體中並物理性連接至該 PMOS 電晶體之該第二擴散區域的 p 型區域,其中在一靜電放電事件發生之前,該 PMOS 電晶體之該閘極係保持於一參考電壓位準以將該 PMOS 電晶體保持於一開啟狀態。

- 11. 如申請專利範圍第 10 項所述之元件,其中該 PMOS 電晶體之該閘極係電連接至一靜電放電偵測電路。

- 12. 如申請專利範圍第 11 項所述之元件,其中該靜電放電偵測電路包括一電阻器及一電容器。

- 13. 如申請專利範圍第 10 項所述之元件,其中該 n 型區域包括複數個形成於該 n 型井中的子區域。

- 14. 如申請專利範圍第 13 項所述之元件,其中該複數個子區域係藉由該 PMOS 電晶體之該 第一擴散區域而彼此分開。

- 15. 如申請專利範圍第 10 項所述之元件,其中形成於該 n 型井中的該 PMOS 電晶體之該第二擴散區域以及形成 於該基體中的該 p 型區域係形成於一整體 p 型區域中。

- 16. 如申請專利範圍第 14 項所述之元件,其中該複數個子區域係藉由該 PMOS 電晶體之該 第二擴散區域而彼此分開。

- 17. 如申請專利範圍第 16 項所述之元件,其中形成於該 n 型井中的該 PMOS 電晶體之該第二擴散區域以及形成於該基體中的該 p 型區域係形成於一整體 p 型區域中。

- 18. 一種提供靜電放電(ESD)防護之方法,其包括:提供一矽控整流器(SCR),其包括一半導體基體以及一形成於該基體中的井;提供一形成於該矽控整流器之該井中的 p 型金屬氧化物半導體(PMOS)電晶體,其包括一閘極、一第一擴散區域及一與該第一擴散區域隔開的第二擴散區域;提供一形成於該井中並電連接至該 PMOS 電晶體之該第一擴散區域的 n 型區域;提供一形成於該基體中並物理性連接至該 PMOS 電晶體之該第二擴散區域的 p 型區域;以及在一靜電放電事件發生之前,將該 PMOS 電晶體保持於一開啟狀態。

- 19. 如申請專利範圍第 18 項所述之方法,其進一步包括響應一靜電放電事件而觸發該井中的一第一電流。

- 20. 如申請專利範圍第 29 項所述之方法,其進一步包括響應該第一電流而觸發該基體中的一第二電流。

- 21. 如申請專利範圍第 18 項所述之方法,其進一步包括在一靜電放電事件發生之前將該 PMOS 電晶體之該閘極保持於一參考電壓位準。

- 22. 一種提供靜電放電(ESD)防護之方法,其包括:提供一矽控整流器(SCR),其包括一半導體基體、一形成於該基體中的井、一形成於該井中的陽極、及一陰極;提供一形成於該矽控整流器之該井中的 p 型金屬氧化物半導體(PMOS)電晶體,其包括一閘極、一第一擴散區域及一與該第一擴散區域隔開的第二擴散區域;提供一形成於該井中並電連接至該PMOS 電晶體之該第一擴散區域的 n 型區域;提供一形成於該基體中並物理性連接至該PMOS 電晶體之該第二擴散區域的 p 型區域;在一靜電放電事件發生之前,將該 PMOS

電晶體保持於一開啟狀態;響應一靜電放電事件而觸發該井中的一第一電流,其流過該 n 型區域;響應該第一電流而觸發該基體中的一第二電流,其流過該 p 型區域;以及 將 由該靜電放電事件所引起的一靜電放電電流從該陽極釋放至該陰極。

- 23. 如申請專利範圍第 22 項所述之方法,其進一步包括在一靜電放電事件發生之前將該 PMOS 電晶體之該閘極保持於一參考電壓位準。

- 24. 如申請專利範圍第 22 項所述之方法,其進一步包括偏壓該 PMOS 電晶體之該閘極,以關閉該 PMOS 電晶體。

- 25. 如申請專利範圍第 24 項所述之方法,其進一步包括響應一靜電放電事件而藉由一具有一 RC 延遲常數的偵測電路來開啟該 PMOS 電晶體。

- 26. 一種提供靜電放電(ESD)防護之方法,其包括:提供一靜電放電鉗位元件,其包括:一矽 控整流器(SCR),其進一步包括一半導體基體以及一形成於該基體中的井;提供一形成於 該矽控整流器之該井中的 p 型金屬氧化物半導體(PMOS)電晶體,其包括一閘極、一第一 擴散區域及一與該第一擴散區域隔開的第二擴散區域;一 n 型區域,其係形成於該井中 並電連接至該 PMOS 電晶體之該第一擴散區域;以及一 p 型區域,其係形成於該基體中 並物理性連接至該 PMOS 電晶體之該第二擴散區域; 在一靜電放電事件發生之前,將該 PMOS 電晶體保持於一開啟狀態;響應一靜電放電事件而觸發該井中的一第一電流;以 及響應該第一電流而觸發該基體中的一第二電流。

- 27. 如申請專利範圍第 26 項所述之方法,其進一步包括將該靜電放電鉗位元件置放於一第一電壓位準之一第一電源線與一積體電路之一觸點區之間。

- 28. 如申請專利範圍第 27 項所述之方法,其進一步包括將該靜電放電鉗位元件置放於一第二電壓位準之一第二電源線與一積體電路之一觸點區之間,該第二電壓位準不同於該第一電壓位準。

- 29. 如申請專利範圍第 26 項所述之方法,其進一步包括將該靜電放電鉗位元件置放於一第一電壓位準之一第一電源線與一第二電壓位準之一第二電源線之間,該第二電壓位準不同於該第一電壓位準。

- 30. 如申請專利範圍第 26 項所述之方法,其進一步包括將該靜電放電鉗位元件置放於在一第一電壓位準下操作的一第一積體電路與在一第二電壓位準下操作的一第二積體電路之間的一介面處,該第二電壓位準不同於該第一電壓位準。

- 31. 如申請專利範圍第 28 項之方法,其進一步包括在一靜電放電事件發生之前將該 PMOS 電晶體之該閘極保持於一參考電壓位準。

- 32. 一種提供靜電放電(ESD)防護之方法,其包括:提供一矽控整流器(SCR),其包括一半導體基體、一形成於該基體中的井、一形成於該井中的陽極、及一陰極;提供一形成於該矽控整流器之該井中的 p 型金屬氧化物半導體(PMOS)電晶體,其包括一閘極、一第一擴散區域及一與該第一擴散區域隔開的第二擴散區域;提供一形成於該井中並電連接至該PMOS 電晶體之該第一擴散區域的 n 型區域;提供一形成於該基體中並電連接至該PMOS 電晶體之該第二擴散區域的 p 型區域;在一靜電放電事件發生之前,將該 PMOS 電晶體 保持於一開啟狀態;響應一靜電放電事件而觸發該井中的一第一電流,其流過該 n 型區域;響應該第一電流而觸發該基體中的一第二電流,其流過該 p 型區域;以及將由該靜電放電事件所引起的一靜電放電電流從該陽極釋放至該陰極。

- 33. 如申請專利範圍第 32 項之方法,其進一步包括在一靜電放電事件發生之前將該 PMOS 電晶體之該閘極保持於一參考電壓位準。

- 34. 如申請專利範圍第 32 項之方法,其進一步包括偏壓該 PMOS 電晶體之該閘極,以關閉該 PMOS 電晶體。

- 35. 如申請專利範圍第 34 項之方法,其進一步包括響應一靜電放電事件而藉由一具有一 RC 延遲常數的偵測電路來開啟該 PMOS 電晶體。

- 36. 一種提供靜電放電(ESD)防護之方法,其包括:提供一靜電放電鉗位元件,其包括:一矽 控整流器(SCR),其進一步包括一半導體基體以及一形成於該基體中的井;提供一形成於 該矽控整流器之該井中的 p 型金屬氧化物半導體(PMOS)電晶體,其包括一閘極、一第一 擴散區域及一與該第一擴散區域隔開的第二擴散區域;一 n 型區域,其係形成於該井中 並電連接至該 PMOS 電晶體之該第一擴散區域;以及一 p 型區域,其係形成於該基體中 並電連接至該 PMOS 電晶體之該第二擴散區域;在一靜電放電事件發生之前,將該 PMOS 電晶體保持於一開啟狀態:響應一靜電放電事件而觸發該井中的一第一電流;以及響應 該第一電流而觸發該基體中的一第二電流。

- 37. 如申請專利範圍第 36 項之方法,其進一步包括將該靜電放電鉗位元件置放於一第一電壓位準之一第一電源線與一積體電路之一觸點區之間。

- 38. 如申請專利範圍第 37 項之方法,其進一步包括將該靜電放電鉗位元件置放於一第二電壓 位準之一第二電源線與一積體電路之一觸點區之間,該第二電壓位準不同於該第一電壓 位準。

- 39. 如申請專利範圍第 36 項之方法,其進一步包括將該靜電放電鉗位元件置放於一第一電壓 位準之一第一電源線與一第二電壓位準之一第二電源線之間,該第二電壓位準不同於該 第一電壓位準。

- 40. 如申請專利範圍第 36 項之方法,其進一步包括將該靜電放電鉗位元件置放於在一第一電壓位準下操作的一第一積體電路與在一第二電壓位準下操作的一第二積體電路之間的一介面處,該第二電壓位準不同於該第一電壓位準。

## 圖式簡單說明

當並同各後載圖式而閱覽時,即可更佳瞭解本發明之前揭摘要以及上文詳細說明。為達本發明之說明目的,各圖式裏圖繪有現屬較佳之各具體實施例。然應瞭解本發明並不限於所繪之精確排置方式及設備裝置。

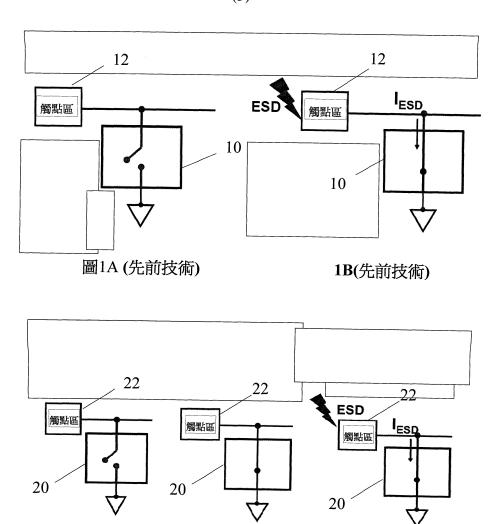

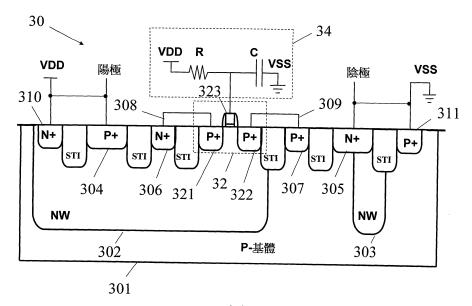

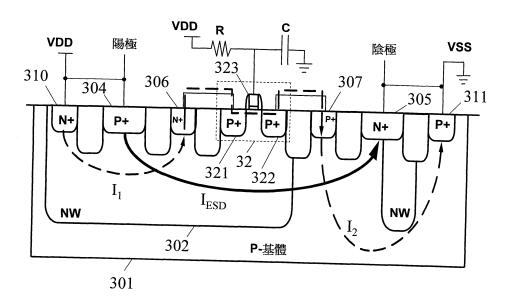

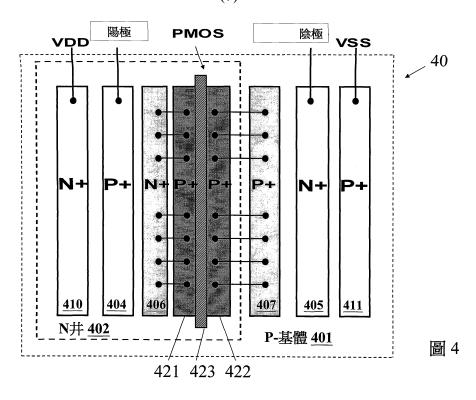

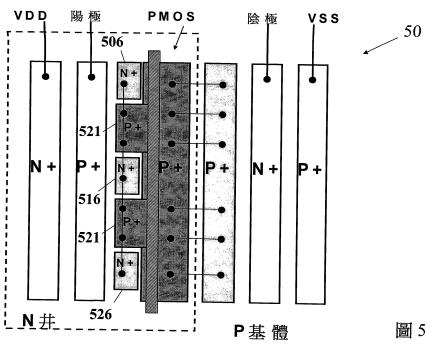

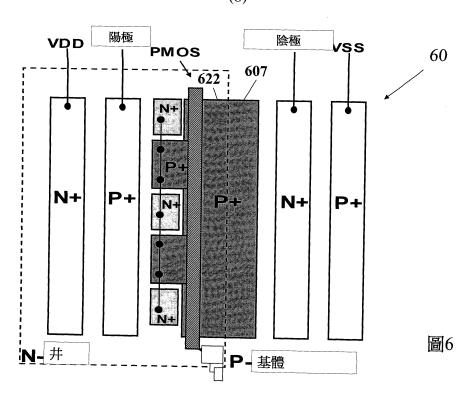

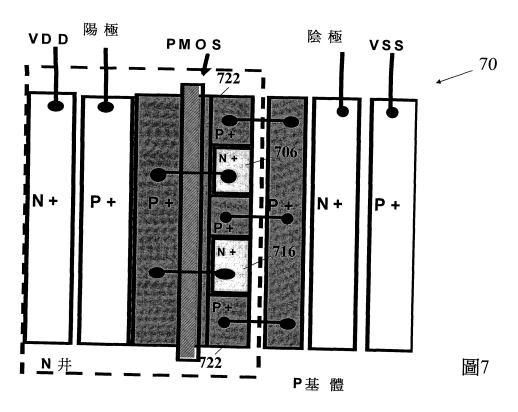

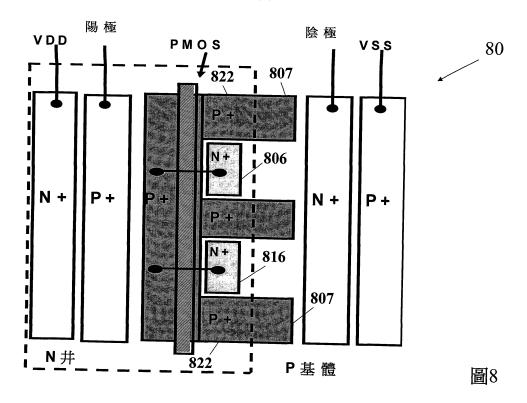

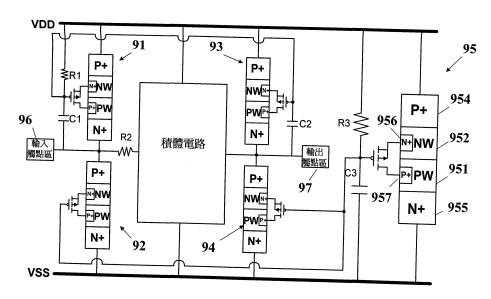

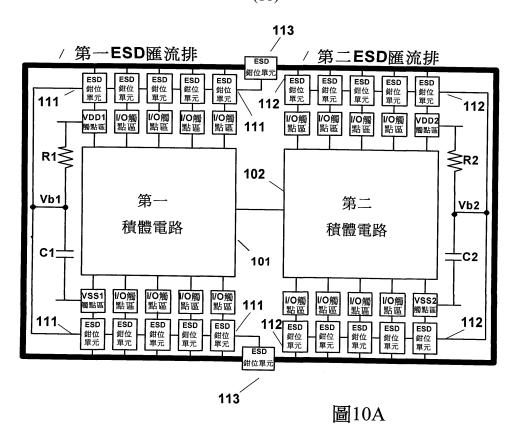

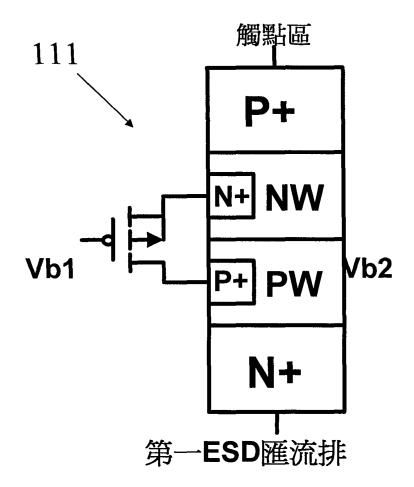

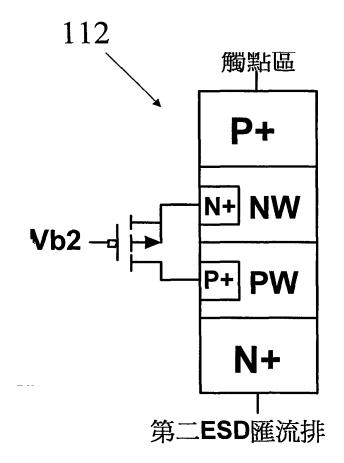

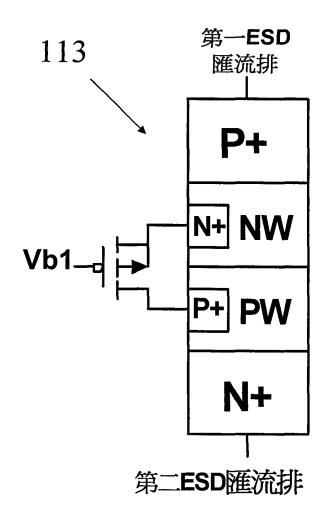

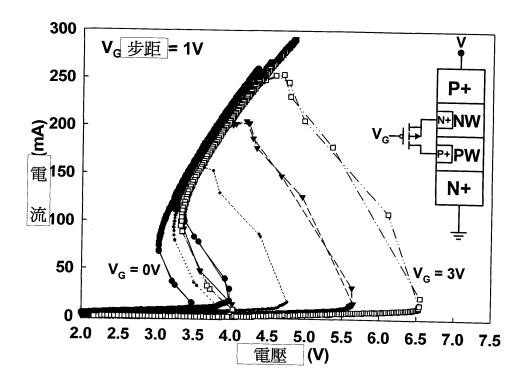

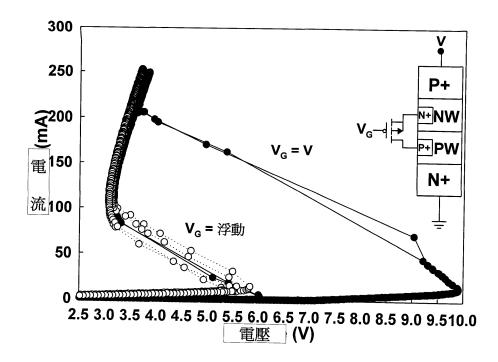

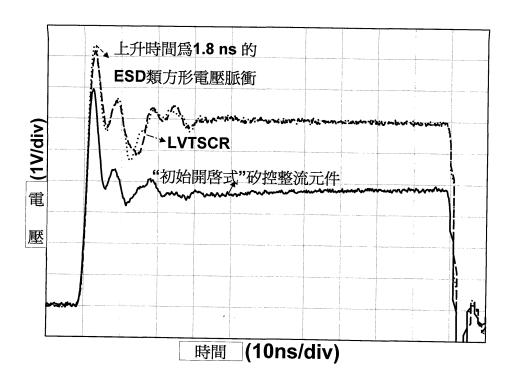

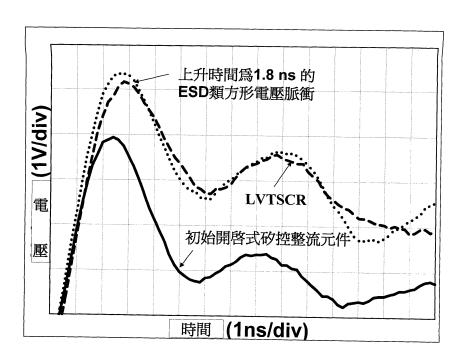

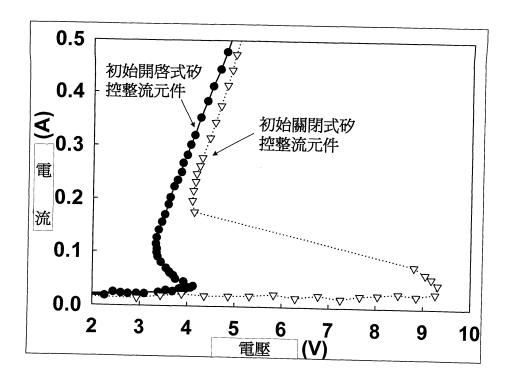

在各圖式中:圖 1A 與 1B 為說明一初始關閉式靜電放電(「ESD」)防護元件之操作的示意圖;圖 3A、2B 及 2C 為說明一初始開啟式靜電放電防護元件之操作的示意圖;圖 3A 為根據本發明之一具體實施例之矽控整流(「SCR」)元件之斷面圖;圖 3B 為說明圖 3A 所示之矽控整流元件之操作的示意圖;圖 4 為根據本發明之一具體實施例之矽控整流元件之佈局圖;圖 5 為根據本發明之另一具體實施例之矽控整流元件之佈局圖;圖 5 為根據本發明之另一具體實施例之矽控整流元件之佈局圖;圖 6 為根據本發明之另一具體實施例之矽控整流元件之佈局圖;圖 9 為根據本發明之另一具體實施例之矽控整流元件之佈局圖;圖 9 為根據本發明之一具體實施例之靜電放電防護架構之示意圖;圖 10A 為根據本發明之一具體實施例用於一混合電壓系統之靜電放電防護架構之示意圖;圖 10B、10C 與 10D 為圖 10A 所示的靜電放電鉗位單元的示意圖;圖 11A 與 11B 為根據本發明之一具體實施例之靜電放電鉗位元件之電流 - 電壓(I - V)曲線;圖 12A 與 12B 為說明根據本發明之一具體實施例之習知 LVTSCR 及靜電放電鉗位元件之測量結果的曲線;以及圖 13 為說明初始關閉式矽控整流元件與根據本發明之一具體實施例之一初始開啟式矽控整流元件之間比較的 I - V 曲線。

圖2B

(先前技術)

圖2C

(先前技術)

圖 2A

(先前技術)

圖 3A

圖 3B

圖9

圖10B

圖10C

圖10D

(14)

圖11A

圖11B

(15)

圖12A

圖12B

圖13