## 【19】中華民國

## 【12】專利公報 (B)

【11】證書號數: I333737

【45】公告日: 中華民國 99 (2010) 年 11 月 21 日 【51】Int. Cl.: *H03H9/19 (2006.01*)

發明 全5頁

【54】名 稱:採用低電壓元件之混合電壓石英振盪電路

MIXED-VOLTAGE CRYSTAL OSCILLATOR CIRCUIT WITH LOW-

**VOLTAGE DEVICES**

【21】申請案號:096120733 【22】申請日:中華民國96(2007)年06月08日

【11】公開編號:200849815 【43】公開日期: 中華民國 97 (2008) 年 12 月 16 日

【72】發 明 人: 柯明道 (TW) KER, MING DOU;廖宏泰 (TW) LIAO, HUNG TAI

【71】申 請 人: 國立交通大學 NATIONAL CHIAO TUNG

**UNIVERSITY**

新竹市大學路 1001 號

【74】代理人: 黃于真;李國光

【56】參考文獻:

CA 1258298A1 JP 1995-193428A US 2001/002876A1 US 2002/0070817A1

## [57]申請專利範圍

- 1. 一種採用低電壓元件之混合電壓石英振盪電路,包含:一輸入接點,能用以接收一外部時脈信號;一輸出接點;一第一反相器,具有一第一輸入端和一第一輸出端,該第一輸出端係電連接至該輸出接點;一 N 型電晶體,該 N 型電晶體具有一第一閘極、一第一汲極和一第一源極,該第一閘極係電連接至一參考電壓源,該第一汲極係電連接至該輸入接點,該第一源極係電連接至該第一輸入端;以及一 P 型電晶體,該 P 型電晶體具有一第二閘極、一第二汲極和一第二源極,該第二閘極係電連接至該第一輸出端,該第二級極係電連接至該第一輸入端,該第二源極係電連接至該參考電壓源;其中該外部時脈信號之一高邏輯準位可高於該參考電壓源所提供之一參考電壓,該第一反相器係由低電壓元件組成,並且該 N 型電晶體及該 P 型電晶體皆為低電壓元件。

- 2. 如申請專利範圍第 1 項所述之混合電壓石英振盪電路,其中該第一反相器係以一 NAND 邏輯閘實現。

- 3. 如申請專利範圍第1項所述之混合電壓石英振盪電路,進一步包含:一第二反相器,具有一第二輸入端和一第二輸出端,該第二輸入端係電連接至該輸入接點,該第二輸出端係電連接至該輸出接點。

- 4. 如申請專利範圍第 3 項所述之混合電壓石英振盪電路,其中該第二反相器係以一 NAND 邏輯閘實現。

- 5. 如申請專利範圍第 3 項所述之混合電壓石英振盪電路,其中該第二反相器係由低電壓元件組成。

- 6. 如申請專利範圍第3項所述之混合電壓石英振盪電路,進一步包含:一控制電路,該控制電路係分別電連接至該第一反相器及該第二反相器,當該輸入接點係用以接收該外部時脈信號,該控制電路停止該第二反相器之運作,當一石英晶體係電連接於該輸入接點及該輸出接點之間,該控制電路停止該第一反相器之運作。

7. 如申請專利範圍第6項所述之混合電壓石英振盪電路,其中該控制電路係由低電壓元件組成。

## 圖式簡單說明

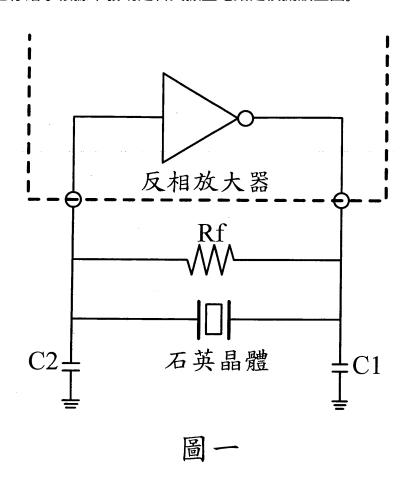

- 圖一係繪示傳統之 Pierce 型石英振盪電路之電路圖。

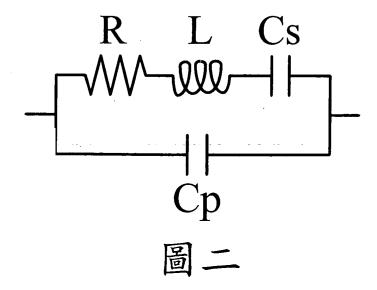

- 圖二係繪示一石英晶體之等效電路圖。

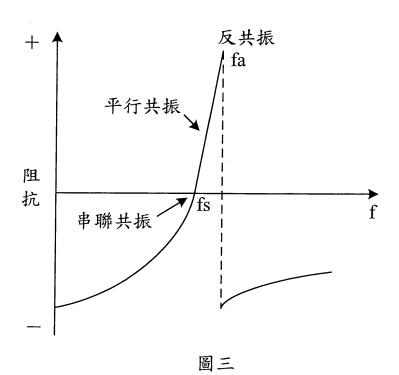

- 圖三係繪示一石英晶體之電抗 頻率圖。

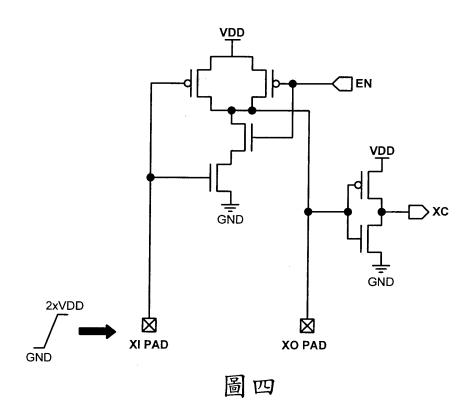

- 圖四係繪示當傳統之石英振盪電路接收外部時脈訊號時之電路圖。

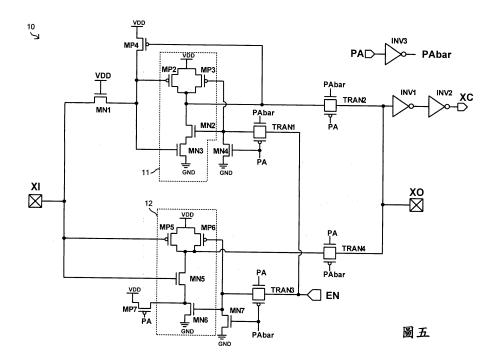

- 圖五係繪示根據本發明之一具體實施例之混合電壓石英振盪電路的電路圖。

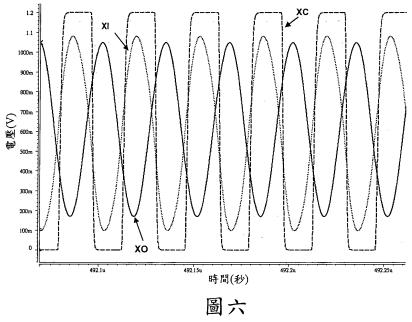

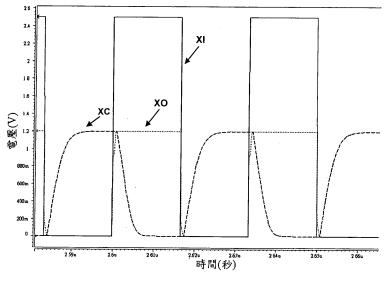

- 圖六及圖七係繪示根據本發明之石英振盪電路之模擬波型圖。

(5)

圖七