## 【19】中華民國 【12】專利公報 (B)

【11】證書號數: I369050

【45】公告日: 中華民國 101 (2012) 年 07 月 21 日

[51] Int. Cl.: H02H9/04 (2006.01) H01L27/04 (2006.01)

發明 全9頁

【54】名 稱:靜電放電防護電路

ESD PROTECTION CIRCUIT

【21】申請案號:097108451 【22】申請日:中華民國 97 (2008) 年 03 月 11 日 【11】公開編號:200924338 【43】公開日期:中華民國 98 (2009) 年 06 月 01 日

【30】優先權: 2007/11/28 美國 11/987,222

【72】發明人: 柯明道 (TW) KER, MING DOU; 陳志豪 (TW) CHEN, CHIN HAO; 姜信欽

(TW) JIANG, HSIN CHIN

【71】申 請 人: 晶焱科技股份有限公司 AMAZING MICROELECTRONIC

CORP.

新北市中和區中正路 716 號 15 樓之 2

【74】代理人: 陳瑞田;康清敬

【56】參考文獻:

CN 1691122A US 5946177 US 6167329 US 6385021B1 US 6724603B2 US 6989979B1

審查人員:彭椏富

## [57]申請專利範圍

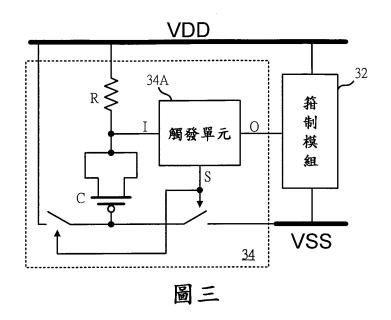

- 1. 一種靜電放電防護電路,包含:一箝制模組,耦接於一正電源線及一負電源線之間;以及一偵測模組,包含:一觸發單元,具有一輸入端、一輸出端及一切換端,該輸出端係耦接至並用以觸發該箝制模組;一電阻,耦接於該正電源線及該觸發單元之該輸入端之間;以及一金氧半電容,具有一第一接點及一第二接點,該第一接點係耦接於該觸發單元之該輸入端;其中,在一正常電源操作狀況下,該觸發單元之該切換端使該金氧半電容之該第二接點耦接至該正電源線;在一靜電放電狀況中,該觸發單元之該切換端使該金氧半電容之該第二接點耦接至該負電源線。

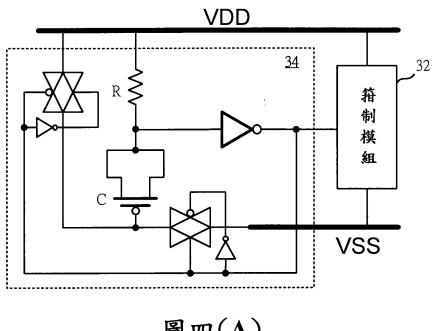

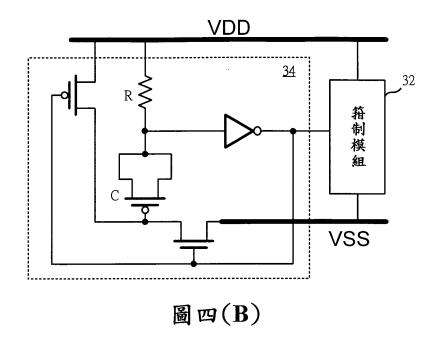

- 2. 如申請專利範圍第1項所述之靜電放電防護電路,其中該觸發單元包含:一第一反相器,具有一輸入接點及一輸出接點,該輸入接點為該觸發單元之該輸入端,且該輸出接點為該觸發單元之該輸出端及該切換端;一第一開關,由該切換端控制,並係耦接於該金氧半電容及該負電源線之間;在該靜電放電狀況中,該第一開關被切換為將該金氧半電容之該第二接點耦接至該負電源線;以及一第二開關,由該切換端控制,並係耦接於該金氧半電容及該正電源線之間;在該正常電源操作狀況下,該第二開關被切換為將該金氧半電容之該第二接點耦接至該正電源線。

- 3. 如申請專利範圍第 2 項所述之靜電放電防護電路,其中該第一開關及該第二開關分別包含一傳輸閘及一第二反相器。

- 4. 如申請專利範圍第 2 項所述之靜電放電防護電路,其中該第一開關包含一 N 型金氧半電晶體(NMOS);該第二開關包含一 P 型金氧半電晶體(PMOS)。

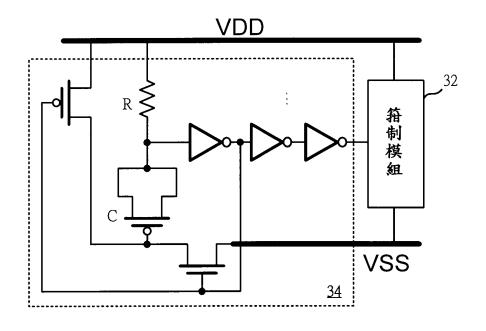

- 5. 如申請專利範圍第 2 項所述之靜電放電防護電路,其中該觸發單元進一步包含 M 個第二 反相器,該 M 個第二反相器係耦接於該第一反相器之該輸出接點與該箝制模組之間, M 為一正偶數。

- 6. 如申請專利範圍第 1 項所述之靜電放電防護電路,其中該金氧半電容為一 PMOS,該 PMOS 之一閘極端為該第二接點;該 PMOS 之一源極端與一汲極端彼此耦接,成為該第 一接點。

- 7. 如申請專利範圍第 1 項所述之靜電放電防護電路,其中該金氧半電容為一 NMOS,該 NMOS 之一閘極端為該第一接點;該 NMOS 之一源極端與一汲極端彼此耦接,成為該第 二接點。

- 8. 如申請專利範圍第 1 項所述之靜電放電防護電路,其中該觸發單元包含:一 PMOS,該 PMOS 之一閘極端係耦接至該金氧半電容之該第二接點,該 PMOS 之一源極端係耦接至 該正電源線,並且該 PMOS 之一汲極端為該觸發單元之該輸出端及該切換端;一 NMOS,該 NMOS 之一閘極端為該觸發單元之該輸入端,該 NMOS 之一源極端係耦接 至該負電源線,並且該 NMOS 之一汲極端係耦接至該 PMOS 之該汲極端;以及一反相器,具有一輸入接點及一輸出接點,且該輸入接點係耦接至該 PMOS 之該汲極端,該輸出接點係耦接至該金氧半電容之該第二接點。

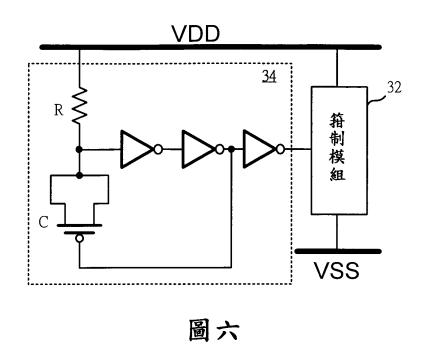

- 9. 如申請專利範圍第 1 項所述之靜電放電防護電路,其中該觸發單元包含 N 個串連的反相器,N 為一正奇數,該 N 個反相器之一輸入接點為該觸發單元之該輸入端,該 N 個反相器之一輸出接點為該觸發單元之該輸出端,該 N 個反相器之一中間節點為該觸發單元之該切換端,該輸出端之一輸出信號與該切換端之一切換信號彼此反相。

- 10. 一種靜電放電防護電路,包含:一箝制模組,耦接於一正電源線及一負電源線之間;以及一偵測模組,包含:一觸發單元,具有一輸入端、一輸出端及一切換端,該輸出端係耦接至並用以觸發該箝制模組;一電阻,耦接於該負電源線與該觸發單元之該輸入端之間;以及一金氧半電容,具有一第一接點及一第二接點,該第一接點係耦接至該觸發單元之該輸入端;其中,在一正常電源操作狀況下,該觸發單元之該切換端使該金氧半電容之該第二接點耦接至該負電源線;在一靜電放電狀況下,該觸發單元之該切換端使該金氧半電容之該第二接點耦接至該正電源線。

- 11. 如申請專利範圍第 10 項所述之靜電放電防護電路,其中該觸發單元包含:一第一反相器,具有一第一輸入接點及一第一輸出接點,該第一輸入接點為該觸發單元之該輸入端,該第一輸出接點為該觸發單元之該切換端;一第二反相器,具有一第二輸入接點及一第二輸出接點,該第二輸入接點係耦接至該第一輸出接點,該第二輸出接點為該觸發單元之該輸出端;一第一開關,由該切換端控制,並係耦接於該金氧半電容與該負電源線之間;在該正常電源操作狀況下,該第一開關被切換為將該金氧半電容之該第二接點耦接至該負電源線;以及一第二開關,由該切換端控制,並係耦接於該金氧半電容與該正電源線之間;在該靜電放電狀況下,該第二開關被切換為將該金氧半電容之該第二接點耦接至該正電源線。

- 12. 如申請專利範圍第 11 項所述之靜電放電防護電路,其中該第一開關及該第二開關分別包含一傳輸閘及一第二反相器。

- 13. 如申請專利範圍第 11 項所述之靜電放電防護電路,其中該第一開關包含一 NMOS;該第二開關包含一 PMOS。

- 14. 如申請專利範圍第 11 項所述之靜電放電防護電路,其中該觸發元件進一步包含 M 個第二反相器,該 M 個第二反相器係耦接於該第二輸出接點及該箝制模組之間,且 M 為一正偶數。

- 15. 如申請專利範圍第 10 項所述之靜電放電防護電路,其中該金氧半電容為一 PMOS,該 PMOS 之一閘極端為該第一接點;該 PMOS 之一源極端及一汲極端彼此耦接,成為該第 二接點。

- 16. 如申請專利範圍第 10 項所述之靜電防護電路,其中該金氧半電容為一 NMOS,該 NMOS 之一閘極端為該第二接點;該 NMOS 之一源極端及一汲極端彼此耦接,成為該第一接點。

- 17. 如申請專利範圍第 10 項所述之靜電放電防護電路,其中該觸發單元包含:一第一反相器,具有一第一輸入接點及一第一輸出接點,該第一輸入接點為該觸發單元之該輸入端;以及一第二反相器,具有一第二輸入接點及一第二輸出接點,該第二輸入接點係耦接至該第一輸出接點,該第二輸出接點為該觸發單元之該輸出端及該切換端。

## 圖式簡單說明

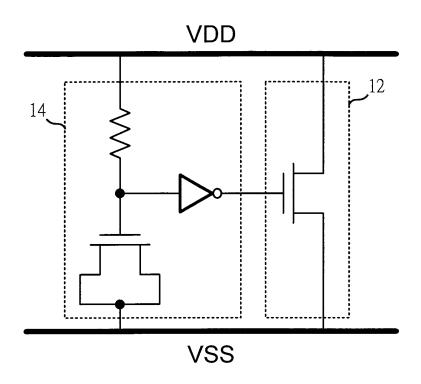

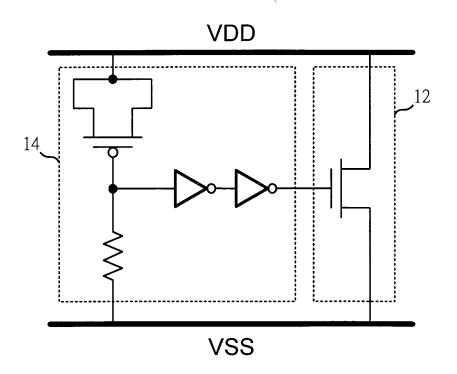

圖一及圖二係繪示先前技術中的 ESD 防護電路。

圖三係繪示根據本發明之一實施例中的 ESD 防護電路。

圖四(A)及圖四(B)係繪示根據本發明之具體實施例中的偵測模組。

圖五及圖六係繪示包含多個反相器之觸發元件的實施例。

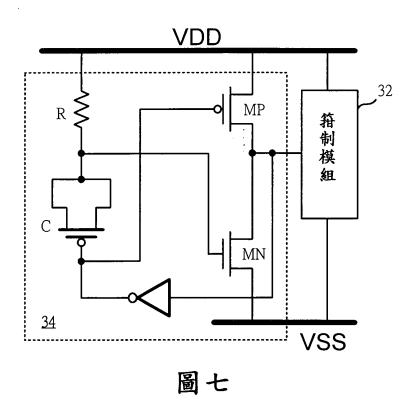

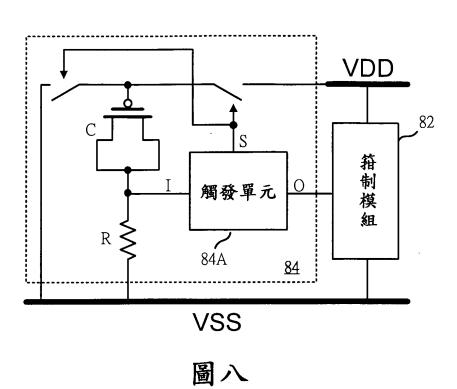

圖七及圖八係繪示根據本發明之另一實施例中的 ESD 防護電路。

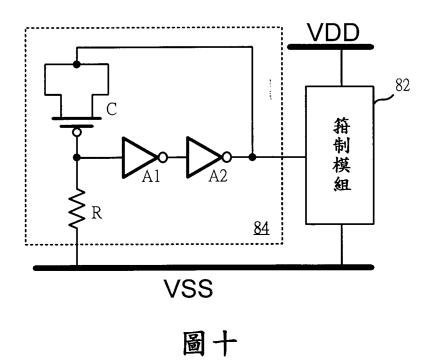

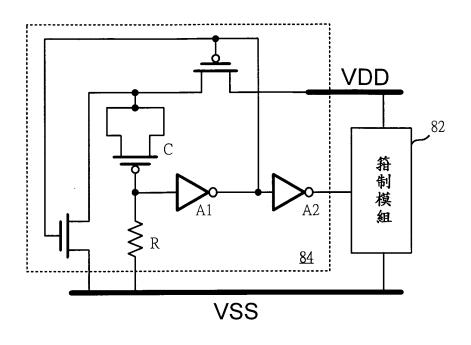

圖九(A)及圖九(B)、圖十係繪示根據本發明之具體實施例中的偵測模組。

圖一(先前技術)

圖二(先前技術)

圖四(A)

圖五

圖九(A)

圖九(B)