## 【19】中華民國 【12】專利公報 (B)

【11】證書號數:I406385

【45】公告日: 中華民國 102 (2013) 年 08 月 21 日

[51] Int. Cl.: H01L23/60 (2006.01) H05F3/02 (2006.01)

發明 全8頁

【54】名 稱:靜電放電保護裝置

ELECTROSTATIC DISCHARGE PROTECTION DEVICE

【21】申請案號:099102530 【22】申請日:中華民國 99 (2010) 年 01 月 29 日

【11】公開編號:201126689 【43】公開日期: 中華民國 100 (2011) 年 08 月 01 日

【72】發明人: 柯明道 (TW) KER, MING DOU;許哲綸 (TW) HSU, CHE LUN;周業甯 (TW)

JOU, YEH NING; 林耿立 (TW) LIN, GEENG LIH; 黃曄仁 (TW) HUANG.

YEH JEN

【71】申 請 人: 世界先進積體電路股份有限公司 VANGUARD INTERNATIONAL

SEMICONDUCTOR CORPORATION

新竹縣新竹科學工業園區園區三路 123 號

國立交通大學 NATIONAL CHIAO TUNG

**UNIVERSITY**

新竹市大學路 1001 號

【74】代理人: 洪澄文;顏錦順

【56】參考文獻:

US 2007/0285854A1

審查人員:陳建仲

## [57]申請專利範圍

- 1. 一種靜電放電保護裝置,包括:一第一放電單元;一第二放電單元,與該第一放電單元 串聯於一第一接觸墊與一第二接觸墊之間,用以釋放一靜電放電電流;一第一觸發單 元,包括一第一電晶體以及至少一第一二極體,該第一電晶體與該第一二極體串聯於該 第一接觸墊與該第一放電單元之間,當一靜電放電事件發生時,該第一觸發單元觸發該 第一放電單元;以及一第二觸發單元,包括一第二電晶體,並耦接於該第一接觸墊與該 第二放電單元之間,當該第一放電單元被觸發時,該第二電晶體觸發該第二放電單元。

- 2. 如申請專利範圍第1項所述之靜電放電保護裝置,其中該第一電晶體係為一第一P型電晶體,具有一第一閘極、一第一源極以及一第一汲極,該第一閘極耦接該第一汲極,該 第一源極耦接該第一接觸墊,該第一汲極耦接該第一二極體之陰極。

- 3. 如申請專利範圍第 2 項所述之靜電放電保護裝置,其中該第一放電單元係為一第一矽控整流器(silicon controlled rectifier; SCR),具有一第一陽極、一第一陰極以及一第一觸發端,該第一陽極耦接該第二放電單元,該第一陰極耦接該第二接觸墊,該第一觸發端耦接該第一二極體之陽極。

- 4. 如申請專利範圍第 3 項所述之靜電放電保護裝置,其中該第二電晶體係為一第二 P 型電晶體,具有一第二閘極、一第二源極以及一第二汲極,該第二閘極耦接該第一閘極,該第一源極耦接該第一接觸墊,該第一汲極耦接該第二放電單元。

- 5. 如申請專利範圍第4項所述之靜電放電保護裝置,其中該第二放電單元係為一第二矽控整流器,具有一第二陽極、一第二陰極以及一第二觸發端,該第二陽極耦接該第一接觸墊,該第二陰極耦接該第一陽極,該第二觸發端耦接該第二汲極。

- 6. 如申請專利範圍第1項所述之靜電放電保護裝置,更包括一第三放電單元以及一第三觸發單元,該第三放電單元與該第二及第一放電單元串聯於該第一及第二接觸墊之間,該第三觸發單元具有一第三電晶體,該第三電晶體耦接於該第一接觸墊與該第三放電單元之間,當該第一放電單元被觸發時,該第三電晶體觸發該第三放電單元。

- 7. 如申請專利範圍第1項所述之靜電放電保護裝置,其中該第一電晶體係為一第一N型電晶體,具有一第一閘極、一第一源極以及一第一汲極,該第一閘極耦接該第一汲極,該 第一源極耦接該第一接觸墊,該第一汲極耦接該第一二極體之陽極。

- 8. 如申請專利範圍第7項所述之靜電放電保護裝置,其中該第一觸發單元更包括一電阻, 耦接於該第一閘極與該第一源極之間。

- 9. 如申請專利範圍第 8 項所述之靜電放電保護裝置,其中該第一放電單元係為一第一矽控整流器(silicon controlled rectifier; SCR),具有一第一陽極、一第一陰極以及一第一觸發端,該第一陽極耦接該第二接觸墊,該第一陰極耦接該第二放電單元,該第一觸發端耦接該第一二極體之陰極。

- 10. 如申請專利範圍第9項所述之靜電放電保護裝置,其中該第二電晶體係為一第二N型電晶體,具有一第二閘極、一第二源極以及一第二汲極,該第二閘極耦接該第一閘極,該 第一汲極耦接該第二放電單元,該第一源極耦接該第一接觸墊。

- 11. 如申請專利範圍第 10 項所述之靜電放電保護裝置,其中該第二放電單元係為一第二矽控整流器,具有一第二陽極、一第二陰極以及一第二觸發端,該第二陽極耦接該第一陰極,該第二陰極耦接該第一接觸墊,該第二觸發端耦接該第二汲極。

- 12. 如申請專利範圍第 1 項所述之靜電放電保護裝置,更包括:一第三觸發單元,包括一第三電晶體以及至少一第二二極體,該第三電晶體與該第二二極體串聯於該第二接觸墊與該第一放電單元之間,當一靜電放電事件發生時,該第三觸發單元觸發該第一放電單元;以及一第四觸發單元,包括一第四電晶體,耦接於該第二接觸墊與該第二放電單元之間,當該第一放電單元被觸發時,該第四電晶體觸發該第二放電單元。

- 13. 如申請專利範圍第 12 項所述之靜電放電保護裝置,其中該第一電晶體係為一第一 P 型電晶體,具有一第一閘極、一第一源極以及一第一汲極,該第一閘極耦接該第一汲極,該 第一源極耦接該第一接觸墊,該第一汲極耦接該第一二極體之陰極。

- 14. 如申請專利範圍第 13 項所述之靜電放電保護裝置,其中該第一放電單元係為一第一矽控整流器(silicon controlled rectifier; SCR),具有一第一陽極、一第一陰極、一第一觸發端以及一第二觸發端,該第一陽極耦接該第二放電單元,該第一陰極耦接該第二接觸墊,該第一觸發端耦接該第一二極體之陽極,該第二觸發端耦接該第二二極體之陰極。

- 15. 如申請專利範圍第 14 項所述之靜電放電保護裝置,其中該第二電晶體係為一第二 P 型電 晶體,具有一第二閘極、一第二源極以及一第二汲極,該第一閘極耦接該第一閘極,該 第一源極耦接該第一接觸墊,該第一汲極耦接該第二放電單元。

- 16. 如申請專利範圍第 15 項所述之靜電放電保護裝置,其中該第二放電單元係為一第二矽控整流器,具有一第二陽極、一第二陰極、一第三觸發端以及一第四觸發端,該第二陽極耦接該第一接觸墊,該第三陰極耦接該第一陽極,該第三觸發端耦接該第二汲極。

- 17. 如申請專利範圍第 16 項所述之靜電放電保護裝置,其中該第三電晶體係為一第一 N 型電晶體,具有一第三閘極、一第三源極以及一第三汲極,該第三閘極耦接該第三接觸墊,該第三汲極耦接該第二二極體之陽極。

- 18. 如申請專利範圍第 17 項所述之靜電放電保護裝置,其中該第三觸發單元更包括一電阻, 耦接於該第三閘極與該第三源極之間。

- 19. 如申請專利範圍第 18 項所述之靜電放電保護裝置,其中該第四電晶體係為一第二 N 型電晶體,具有一第四閘極、一第四源極以及一第四汲極,該第四閘極耦接該第三閘極, 該第四汲極耦接該第四觸發端,該第四源極耦接該第二接觸墊。

- 20. 一種靜電放電保護裝置,包括:一第一放電單元;一第二放電單元,與該第一放電單元 串聯於一第一接觸墊與一第二接觸墊之間;一第一觸發單元,耦接於該第一接觸墊與該 第一放電單元之間;以及一第二觸發單元,耦接於該第一接觸墊與該第二放電單元之 間,當該第一觸發單元觸發該第一放電單元時,該第二觸發單元觸發該第二放電單元。

- 21. 如申請專利範圍第 20 項所述之靜電放電保護裝置,其中當一電流由該第一接觸墊開始,流經該第一觸發單元、該第一放電單元以及該第二接觸墊時,該第二觸發單元觸發該第二放電單元。

- 22. 如申請專利範圍第 20 項所述之靜電放電保護裝置,其中該第一及第二觸發單元具有一電流鏡電路。

- 23. 如申請專利範圍第 20 項所述之靜電放電保護裝置,更包括:一第三放電單元,與該第一及第二放電單元串聯於該第一及第二接觸墊之間一第三觸發單元,耦接於該第一接觸墊與該第三放電單元之間,當該第一觸發單元觸發該第一放電單元時,該第三觸發單元觸發該第三放電單元。

- 24. 如申請專利範圍第 23 項所述之靜電放電保護裝置,其中該第一、第二及第三觸發單元具有一電流鏡電路。

- 25. 如申請專利範圍第 20 項所述之靜電放電保護裝置,更包括:一第三觸發單元,耦接於該第二接觸墊與該第一放電單元之間;以及一第四觸發單元,耦接於該第二接觸墊與該第二放電單元之間,當該第三觸發單元觸發該第一放電單元時,該第四觸發單元觸發該第二放電單元。

- 26. 如申請專利範圍第 25 項所述之靜電放電保護裝置,其中該第一及第二觸發單元具有一第一電流鏡電路,該第三及第四觸發單元具有一第二電流鏡電路。

- 27. 如申請專利範圍第 25 項所述之靜電放電保護裝置,其中該第一放電單元具有一第一觸發端以及一第二觸發端,該第一觸發端接收來自該第一觸發單元的一第一觸發信號,該第二觸發端接收來自該第三觸發單元的一第二觸發信號。

- 28. 如申請專利範圍第 27 項所述之靜電放電保護裝置,其中該第一觸發端具有一 P 型摻雜物,該第二觸發端具有一 N 型摻雜物。

## 圖式簡單說明

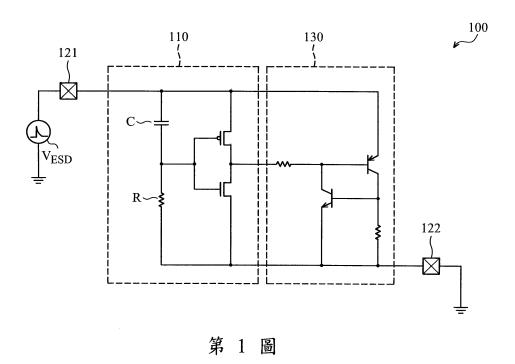

- 第1圖為習知 ESD 保護裝置。

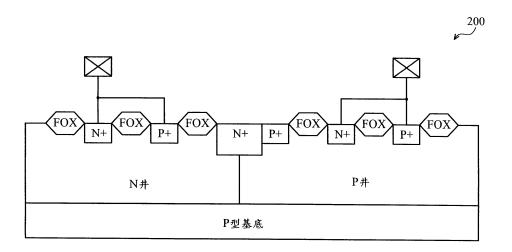

- 第 2 圖為另一習知 ESD 保護裝置的剖面圖。

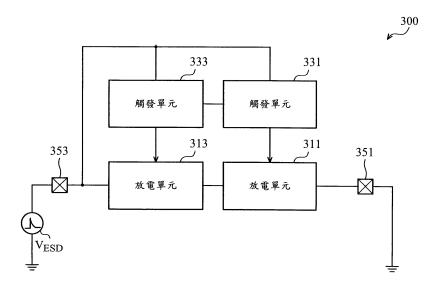

- 第3圖為本發明之 ESD 保護裝置之示意圖。

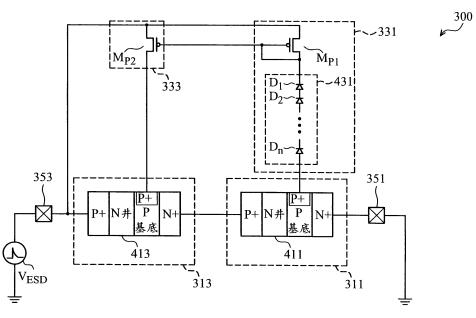

- 第 4A 圖為本發明之 ESD 保護裝置之一可能實施例。

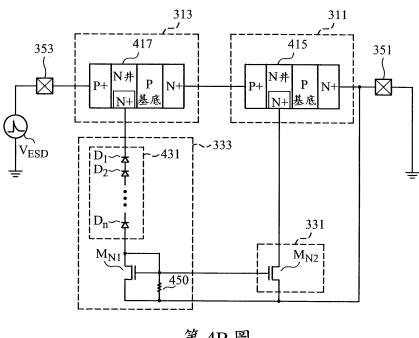

- 第 4B 圖為本發明之 ESD 保護裝置之另一可能實施例。

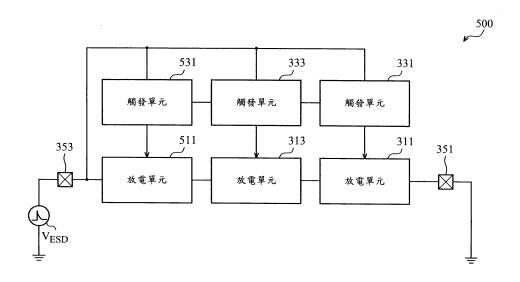

- 第 5 圖為本發明之 ESD 保護裝置之另一示意圖。

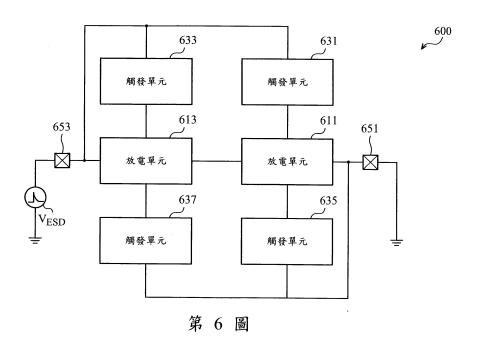

- 第6圖為本發明之 ESD 保護裝置之另一示意圖。

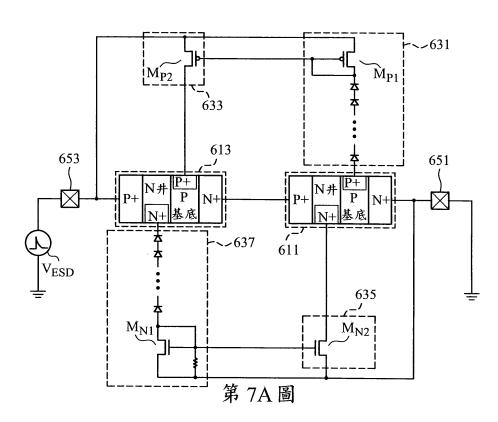

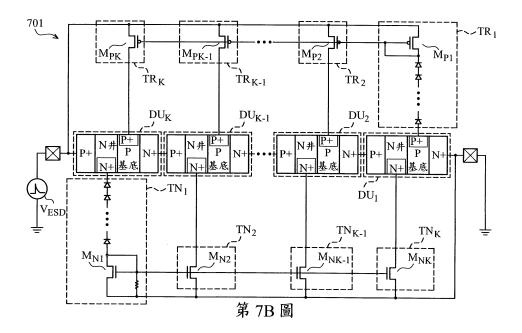

- 第7A 圖為本發明之 ESD 保護裝置之另一可能實施例。

- 第7B 圖為本發明之 ESD 保護裝置之另一可能實施例。

第 2 圖

## 第 3 圖

第 4A 圖

第 4B 圖

第 5 圖