## 【19】中華民國 【12】專利公報 (B)

【11】證書號數:I449158

【45】公告日: 中華民國 103 (2014) 年 08 月 11 日 [51] Int. Cl.: H01L27/04 (2006.01)

發明 全9頁

稱:具有多重電源區域積體電路之靜電放電防護電路 【54】名

ESD PROTECTION CIRCUIT FOR INTEGRATED CIRCUIT WITH

MULTIPLE POWER DOMAIN

【21】申請案號:098120418 【22】申請日: 中華民國 98 (2009) 年 06 月 18 日

【11】公開編號:201101460 【43】公開日期:中華民國 100 (2011) 年 01 月 01 日

【72】發 明 人: 蔡富義 (TW) TSAI, FU YI; 柯明道 (TW) KER, MING DOU

【71】申 請 人: 智原科技股份有限公司 FARADAY TECHNOLOGY CORP.

新竹市新竹科學工業園區力行三路 5 號

【74】代理人: 戴俊彥;吳豐任

【56】參考文獻:

TW 200513001A TW 200908276A

US 2005/0098830A1

審查人員:郭子鳳

## [57]申請專利範圍

- 1. 一種具有多重電源區域積體電路之靜電放電防護電路,包含:一第一 ESD 保護元件,耦 接於一第一電源供應線和一第一地線之間;一第一內部電路,具有耦接於該第一電源供 應線的一第一端;一第一開關,耦接於該第一內部電路的一第二端以及一第二地線之 間;以及一第一ESD 偵測電路,耦接於一第二電源供應線以及該第二地線之間,耦接於 該第一開關,用以偵測一靜電放電訊號,並在該靜電放電訊號產生時,使該第一開關不 導通:一第二內部電路,耦接於該第二電源供應線以及該第一地線之間:以及一第二 ESD 保護元件,耦接於該第二電源供應線以及該第二地線之間。

- 2. 如申請專利範圍第1項所述之靜電放電保護電路,更包含:一第二開關,耦接於該第一 內部電路的該第一端以及該第一電源供應線之間;以及一第二 ESD 偵測電路, 耦接於該 第一電源供應線以及該第一地線之間, 耦接於該第二開關, 用以偵測一靜電放電訊號, 並在該靜電放電訊號產生時,使該第二開關不導通。

- 3. 如申請專利範圍第1項所述之靜電放電保護電路,其中該第一開關係為一 NMOS,且該 第一開關的一基體係直接連接於該第一開關的一源極以及該第一開關。

- 4. 如申請專利範圍第 3 項所述之靜電放電保護電路,其中該第一開關具有一深層 N 型佈植 層(Deep N Well)。

- 5. 如申請專利範圍第 1 項所述之靜電放電保護電路,其中該第一開關係為一 NMOS,且該 第一開關的一基體係直接連接於該第一地線。

- 6. 如申請專利範圍第1項所述之靜電放電保護電路,更包含一第二開關,耦接於該第一內 部電路的該第一端以及該第一電源供應線之間,亦耦接於該第一 ESD 偵測電路,該第一 ESD 偵測電路在該靜電放電訊號產生時, 使該第二開關不導通。

- 7. 一種具有突發性電流防護機制的積體電路,包含:一第一欲保護電路,具有耦接於一第 一電源供應線的一第一端;一第一開關,耦接於該第一欲保護電路的一第二端以及一第 二地線之間;一第一突發性電流偵測電路,耦接於一第二電源供應線以及該第二地線之

- 間,耦接於該第一開關,用以偵測一靜電放電訊號,並在該靜電放電訊號產生時,使該 第一開關不導通,以及;一第二欲保護電路,耦接於該第二電源供應線以及該第一地線 之間。

- 8. 如申請專利範圍第7項所述之具有突發性電流防護機制的積體電路,更包含:一第二開關,耦接於該第一欲保護電路的該第一端以及該第一電源供應線之間;以及一第二突發性電流偵測電路,耦接於該第一電源供應線以及該第一地線之間,耦接於該第二開關,用以偵測一靜電放電訊號,並在該靜電放電訊號產生時,使該第二開關不導通。

- 9. 如申請專利範圍第7項所述之具有突發性電流防護機制的積體電路,其中該第一開關係為一NMOS,且該第一開關的一基體係直接連接於該第一開關的一源極以及該第一開關。

- 10. 如申請專利範圍第 9 項所述之具有突發性電流防護機制的積體電路,其中該第一開關具有一深層 N 型佈植層(Deep N Well)。

- 11. 如申請專利範圍第 7 項所述之具有突發性電流防護機制的積體電路,其中該第一開關係 為一 NMOS,且該第一開關的一基體係直接連接於該第一地線。

- 12. 如申請專利範圍第7項所述之具有突發性電流防護機制的積體電路,更包含一第二開關,耦接於該第一欲保護電路的該第一端以及該第一電源供應線之間,亦耦接於該第一突發性電流偵測電路,該第一突發性電流偵測電路在該靜電放電訊號產生時,使該第二開關不導通。

- 13. 如申請專利範圍第1項所述之靜電放電保護電路,更包含:一訊號傳輸路徑,耦接於該第一內部電路以及該第二內部電路之間。

- 14. 如申請專利範圍第7項所述之具有突發性電流防護機制的積體電路,更包含:一訊號傳輸路徑,耦接於該第一欲保護電路以及該第二欲保護電路之間。

## 圖式簡單說明

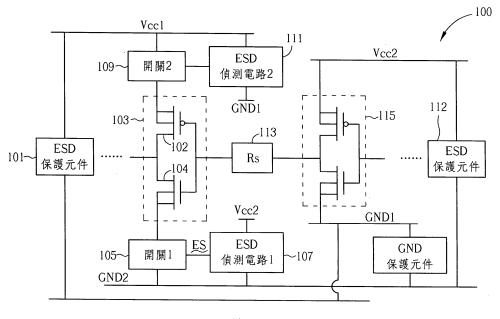

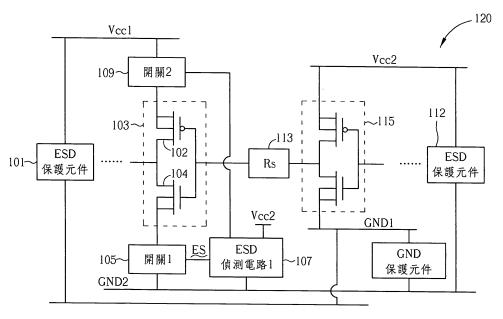

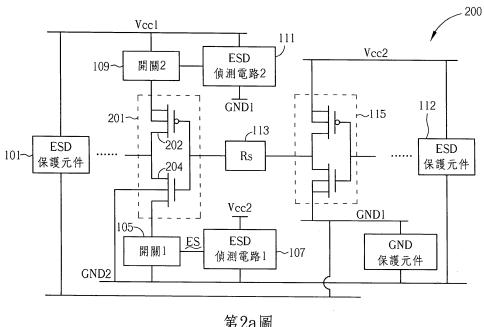

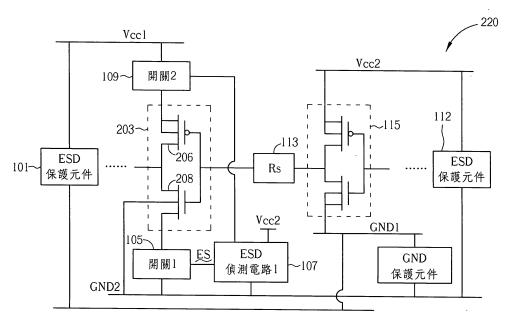

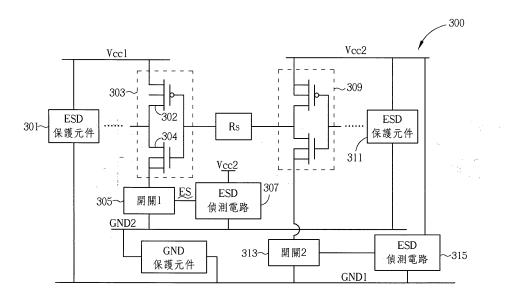

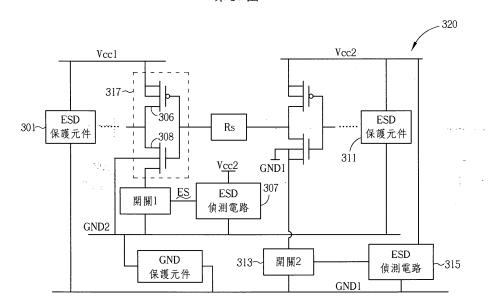

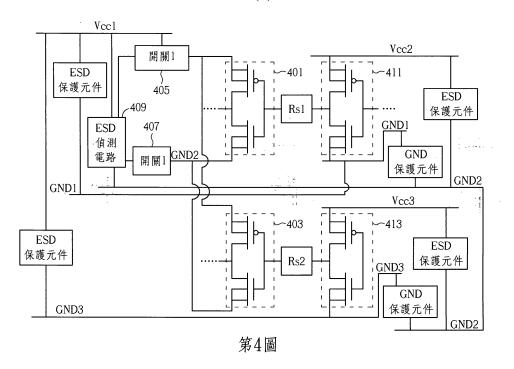

第 1a、1b、2a、2b、3a、3b 圖以及第 4 圖分別繪示了根據本發明之實施例的具有多重電源區域積體電路之靜電放電防護電路之電路圖。

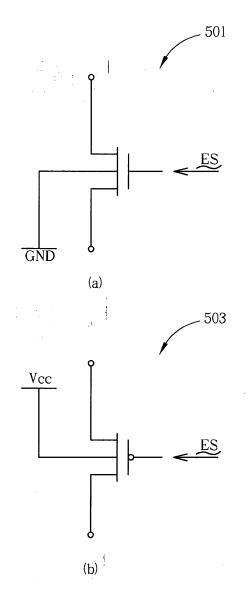

第 5 圖繪示了第 1a、1b、2a、2b、3a、3b 圖以及第 4 圖所示之電路的開關之示範性詳細結構。

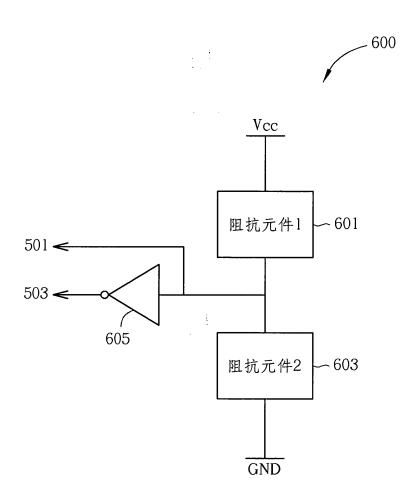

第 6 圖繪示了第 1a、1b、2a、2b、3a、3b 圖以及第 4 圖所示之電路的 ESD 偵測電路之示範性詳細結構。

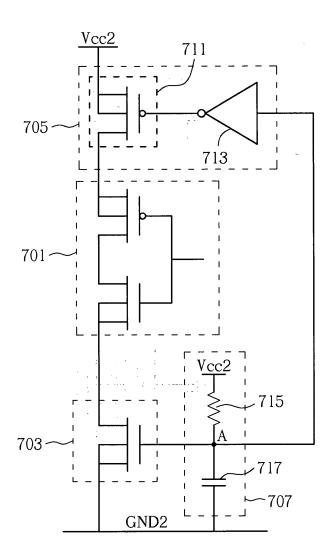

第 7 圖繪示了使用第 5-6 圖所示之結構的具有多重電源區域積體電路之靜電放電防護電路 之電路圖。

第1a圖

第1b圖

第2a圖

第2b圖

第3a圖

第3b圖

第5圖

第6圖

第7圖