## Novel Implantation Method to Improve Machine-Model Electrostatic Discharge Robustness of Stacked N-Channel Metal-Oxide Semiconductors (NMOS) in Sub-Quarter-Micron Complementary Metal-Oxide Semiconductors (CMOS) Technology

Ming-Dou KER\*, Hsin-Chyh HSU and Jeng-Jie PENG<sup>1</sup>

Nanoelectronics and Gigascale Systems Laboratory, Institute of Electronics, National Chiao-Tung University, 1001 Ta-Hsueh Road, Hsinchu, Taiwan, R.O.C. <sup>1</sup>ESD Protection Technology Department, SoC Technology Center, Industrial Technology Research Institute (ITRI),

<sup>1</sup>ESD Protection Technology Department, SoC Technology Center, Industrial Technology Research Institute (ITRI), Bldg. 14, 195, Sec. 4, Chung-Hsing Rd., Chutung, Hsinchu, Taiwan, R.O.C.

(Received September 13, 2002; accepted for publication October 15, 2002)

A novel ion implantation method for electrostatic discharge protection, often called as ESD implantation, is proposed to significantly improve machine-model (MM) ESD robustness of N-channel metal-oxide semiconductors (NMOS) device in stacked configuration (stacked NMOS). By using this ESD implantation method, the ESD current is discharged far away from the surface channel of NMOS, therefore the stacked NMOS in the mixed-voltage I/O interface can sustain a much higher ESD level, especially under the MM ESD stress. The MM ESD robustness of the stacked NMOS with a device dimension of  $W/L = 300 \,\mu\text{m}/0.5 \,\mu\text{m}$  for each NMOS has been successfully improved from the original 358 V to become 491 V in a 0.25- $\mu$ m complementary metal-oxide semiconductors (CMOS) process. [DOI: 10.1143/JJAP.41.L1288]

KEYWORDS: electrostatic discharge (ESD), ESD protection, machine model, ESD implantation, stacked NMOS

Component-level electrostatic discharge (ESD) stresses on IC products had been classified as three models:<sup>1)</sup> the humanbody model (HBM), the machine model (MM), and the charged device model (CDM). The ESD voltage ratio between the HBM and MM ESD robustness of complementary metal-oxide semiconductors (CMOS) IC products were around  $\sim 10$  in the submicron (1.0–0.5  $\mu$ m) CMOS processes. Typically, a CMOS IC product, which has a HBM ESD robustness of 2 kV, can sustain a MM ESD stress of 200 V. However, this ratio has approached to about 15-20 in the sub-quarter-micron CMOS processes. The MM ESD robustness of IC products has been found to degrade much worse than its HBM ESD robustness in the sub-quartermicron CMOS processes. How to effectively improve MM ESD robustness of IC products has become a challenge in the sub-quarter-micron CMOS processes.

In order to enhance ESD robustness, some ESD implantations had been reported for including into process flow to modify the device structures for ESD protection.<sup>2–4)</sup> The N-type ESD implantation was used to cover the lightly-doped drain (LDD) peak structure and to make a deeper junction in N-channel metal-oxide semiconductors (NMOS) device for ESD protection.<sup>2)</sup> The P-type ESD implantation with a higher concentration located under the drain junction of NMOS was used to reduce the junction breakdown voltage and to earlier turn on the parasitic lateral BJT of the NMOS.<sup>3)</sup> Moreover, both of the N-type and P-type ESD implantations were used in NMOS device to wish a higher ESD robustness.<sup>4)</sup> The experimental results to compare the effectiveness among those ESD implantation methods had been investigated in a 0.18- $\mu$ m CMOS process.<sup>5)</sup>

In the mixed-voltage circuit application, the stacked NMOS structure had been widely used in the mixed-voltage I/O buffer<sup>6)</sup> to solve the gate-oxide reliability issue without using the additional thick gate-oxide process (or called as dual gate oxide in some CMOS process), or even used in the power-rail ESD clamp circuit.<sup>7)</sup> Unfortunately, in such mixed-voltage I/O circuits the stacked NMOS often have much lower

ESD level, as compared to the buffer with single NMOS.<sup>8,9)</sup> To improve the ESD robustness of the stacked NMOS in the mixed-voltage I/O interface, ESD implantation method is the method without occupied extra silicon area to enhance ESD robustness.

In this letter, a novel ESD implantation method to especially improve machine-model (MM) ESD robustness of stacked NMOS is proposed and verified in a 0.25- $\mu$ m CMOS process.

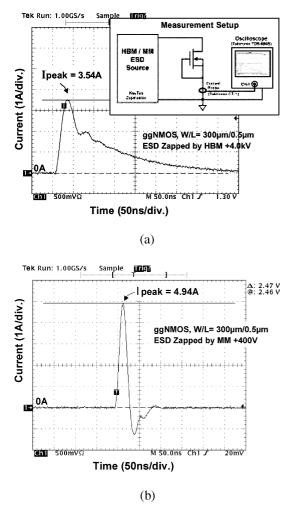

The ESD current waveforms through the gate-grounded NMOS (ggNMOS) under 4-kV HBM and 400-V MM ESD stresses are measured in Figs. 1(a) and 1(b), respectively. The measurement setup is shown in the inserted block in Fig. 1(a). Such HBM and MM ESD events are generated by the Zap-Master (from KeyTek Inc.), which is a typical ESD tester widely used to verify ESD robustness of IC products. The measured current peak of 4-kV HBM ESD stress in Fig. 1(a) is 3.54 A, whereas that of 400-V MM ESD stress in Fig. 1(b) is 4.94 A. Comparing these two ESD current waveforms, the MM ESD stress has a much higher ESD current peak and a shorter current pulse width than those of HBM ESD stress. The rise time of MM ESD current is also faster than that in HBM ESD stress. This implies that MM ESD events generate more heat in a shorter time period on the ggNMOS. So, the ggNMOS is easily burned out by such a faster MM ESD current, and cause a much lower ESD robustness. MM ESD robustness of IC products will be degraded much worse than its HBM ESD robustness in the sub-quarter-micron CMOS processes.

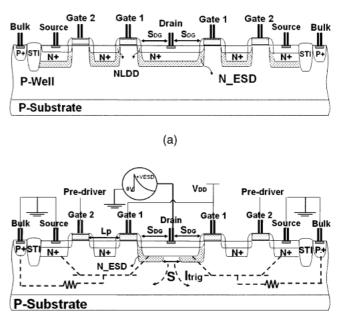

In submicron CMOS technology, the NMOS fabricated with LDD structure to overcome the hot-carrier issue often leads to a lower ESD robustness. To improve ESD robustness, the traditional ESD implantation with n-type impurity on the stacked NMOS is shown in Fig. 2(a), where the N\_ESD impurity in sub-quarter-micron CMOS process often has a lower concentration than that of N+ drain/source diffusion to overcome the hot-carrier issue. To significantly improve MM ESD robustness of the stacked NMOS, a new ESD implantation method is proposed in Fig. 2(b), where the spacing "S" is the

<sup>\*</sup>Corresponding author. E-mail address: mdker@ieee.org

Fig. 1. The measured ESD current waveforms through a ggNMOS  $(W/L = 300 \,\mu\text{m}/0.5 \,\mu\text{m})$  zapped by (a) the human-body-model ESD stress of 4 kV, and (b) the machine-model ESD stress of 400 V.

important layout parameter to be investigated in the 0.25  $\mu$ m CMOS processes. In Fig. 2(b), the ESD implantation region covers the whole drain region of the stacked NMOS, but except the region around the drain contact. This ESD implantation region in this experimental test chip has a lighter doping dosage of  $1 \times 10^{15}$  ions/cm<sup>2</sup> and a junction depth of  $\sim 0.2 \,\mu$ m. The drain/source N+ diffusion for the normal NMOS device has a doping dosage of  $5 \times 10^{15}$  ions/cm<sup>2</sup> and a junction depth of  $\sim 0.18 \,\mu$ m. The junction covered by the proposed ESD implantation method has an increased junction breakdown voltage. But, the region without covering by this ESD implantation has the original junction breakdown voltage.

When a positive ESD voltage is zapped to the pad with the VSS relatively grounded. The drain of stacked NMOS is stressed by the ESD voltage and therefore breaks down to clamp the overstress voltage on the pad. The region, which is not covered by the N\_ESD implantation, has a lower junction breakdown voltage. So, the ESD current is first discharged through this region to generate the substrate current (Itrig) to quickly trigger on the parasitic lateral n-p-n BJT in the stacked NMOS structure. ESD current is mainly discharged through this lateral n-p-n BJT in the stacked NMOS, where such ESD current path is far away from the weakest surface channel of the stacked NMOS. With the selfgenerated substrate triggering current, the lateral n-p-n BJT

(b)

Fig. 2. (a) The traditional ESD implantation with n-type impurity for improving ESD robustness of the stacked NMOS. (b) The new proposed ESD implantation method to significantly improve machine-model ESD robustness of stacked NMOS. The spacing "S" is the important layout parameter to be investigated.

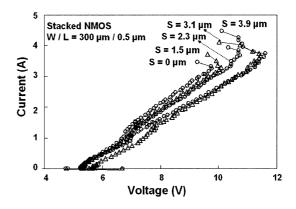

Fig. 3. The TLP-measured *I–V* curves of the stacked NMOS with the proposed ESD implantation under different layout spacing "S".

in the stacked NMOS structure can be fully turned on more quickly.<sup>10)</sup> So, the faster transient current of MM ESD events can be quickly discharged through the lateral n-p-n BJT in the stacked NMOS structure. This causes a significant improvement on ESD robustness of the stacked NMOS in the mixed-voltage I/O interface, especially during the MM ESD zapping.

To investigate the effectiveness of the new proposed ESD implantation method, the stacked NMOS with different layout spacing of "S" in Fig. 2(b) had been fabricated in a 0.25- $\mu$ m CMOS process with shallow trench isolation. The transmission-line-pulse (TLP) generator<sup>11)</sup> with a pulse width of 100 ns is used to measure the secondary breakdown current (It2) of the fabricated stacked NMOS. The TLP-measured *I*-*V* curves of stacked NMOS (*W*/*L* = 300  $\mu$ m/0.5  $\mu$ m) with the new ESD implantation method are shown in Fig. 3 under different layout spacing "S". While the spacing S is increased, the It2 of the stacked NMOS is increased.

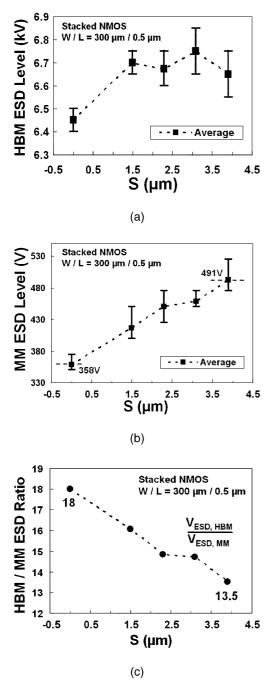

Fig. 4. The dependences of (a) the HBM ESD level, (b) the MM ESD level, and (c) the HBM/MM ratio, on the layout spacing "S" of the stacked NMOS fabricated with the proposed ESD implantation method.

The dependences of HBM and MM ESD levels and the HBM/MM ESD level ratio on the layout spacing "S" are measured by the ZapMaster ESD simulator, and the results are shown in Figs. 4(a), 4(b), and 4(c), respectively. The drain diffusion of the stacked NMOS has a fixed spacing of 5.7  $\mu$ m for all devices in the experimental test chips. The spacing ( $S_{DG}$ )

## M.-D. KER et al.

from drain contact to poly gate edge is  $2.4 \,\mu$ m, and the spacing  $(L_p)$  between poly gate 1 and poly gate 2 is 0.4  $\mu$ m. While the spacing S is increased, the HBM and MM ESD levels of stacked NMOS are also increased. The HBM/MM ESD level ratio shown in Fig. 4(c) has verified that the MM ESD robustness of the stacked NMOS can be significantly improved by this new proposed ESD implantation method under a wider layout spacing S. The MM ESD level of the stacked NMOS with W/L of 300  $\mu$ m/0.5  $\mu$ m has been successfully increase from the original 358 V (with S = 0) to become 491 V (with  $S = 3.9 \,\mu\text{m}$ ), where the MM ESD level is improved 37% by this new proposed ESD implantation method. The HBM ESD level of the stacked NMOS is also slightly improved from the original 6.45 kV (with S = 0) to become 6.65 kV (with  $S = 3.9 \,\mu\text{m}$ ) by this method. Consequently, the HBM/MM ESD level ratio can be really reduced to  $\sim 13.5$  when the spacing S is drawn with  $3.9 \,\mu$ m.

The actual ESD current discharging waveforms of HBM and MM ESD events on ggNMOS has been measured and compared to find the difference. A new ESD implantation method is proposed to improve HBM and MM ESD levels of stacked NMOS in the mixed-voltage I/O interface. Especially, this method can significantly increase ESD level of stacked NMOS under the MM ESD zapping. The experimental results shown in this work is the first report in the literature to specially increase MM ESD robustness in CMOS technology. This ESD implantation method is fully processes compatible to general sub-quarter-micron CMOS processes.

This work was supported by the National Science Council (NSC), Taiwan, and partially supported by the Taiwan Semiconductor Manufacturing Co. (tsmc), Ltd., Taiwan.

- M. D. Ker, J. J. Peng and H. C. Jiang: Proc. 8th IEEE Int. Conf. Electronics, Circuits & Systems, Malta, 2001 (IEEE, New York, 2001) p. 1011.

- 2) J. S. Lee: U.S. Patent 5672527 (1997).

- 3) C. C. Hsue and J. Ko: U.S. Patent 5374565 (1994).

- 4) J. J. Yang and C. M. Hsien: U.S. Patent 6040603 (2000).

- M. D. Ker and C. H. Chuang: Proc. Int. Symp. Physical & Failure Analysis of Integrated Circuits, Singapore, 2001 (IEEE, New York, 2001) p. 85.

- 6) G. Singh and R. Salem: IEEE J. Solid-State Circuits 34 (1999) 1512.

- T. Maloney and W. Kan: Proc. 21th Electrical Overstress/Electrostatic Discharge (EOS/ESD) Symp., Orlando, Florida, 1999 (ESD Association, New York, 1999) p. 70.

- W. Anderson and D. Krakauer: Proc. 20th Electrical Overstress/ Electrostatic Discharge (EOS/ESD) Symp., Reno, Nevada, 1998 (ESD Association, New York, 1998) p. 54.

- J. Miller, M. Khazhinsky and J. Weldon: Proc. 22th Electrical Overstress/Electrostatic Discharge (EOS/ESD) Symp., Anaheim, California, 2000 (ESD Association, New York, 2000) p. 308.

- T. Y. Chen and M. D. Ker: IEEE Trans. Device & Mater. Reliab. 1 (2001) 190.

- J. Barth, J. Richner, K. Verhaege and L. G. Henry: Proc. 22th Electrical Overstress/Electrostatic Discharge (EOS/ESD) Symp., Anaheim, California, 2000 (ESD Association, New York, 2000) p. 85.