# Characterization of SOA in Time Domain and the Improvement Techniques for Using in High-Voltage Integrated Circuits

Wen-Yi Chen and Ming-Dou Ker, Fellow, IEEE

*Abstract*—Safe operating area (SOA) in power semiconductors is one of the most important factors affecting device reliability. The SOA region of power MOSFETs must be well characterized for using in circuit design to meet the specification of applications, particularly including the time domain of circuit operations. In this paper, the characterization of SOA in the time domain is performed with the experimental measurement on silicon devices, and the useful techniques to improve SOA of power MOSFETs for using in high-voltage integrated circuits are overviewed.

*Index Terms*—Electrical safe operating area (SOA) (eSOA), power MOSFETs, SOA, snapback, thermal SOA (tSOA).

## I. INTRODUCTION

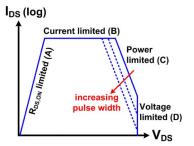

**H** IGH-VOLTAGE (HV) and high current operations are common requirements for semiconductor devices in power applications. To sustain the high operating voltage  $(V_{\rm CC})$ , sufficient device breakdown voltage  $(BV_{\rm DSS})$  is a must for power semiconductors. To minimize the power consumption over a switching transistor, device turn-on resistance per unit area, i.e., the specific on-resistance  $R_{\rm SP}$ , is another important factor for the development of power devices. Safe operating area (SOA), as the third factor to meet the HV and high current operating requirements, defines the I-V boundary in which a power transistor can safely switch. These three factors,  $BV_{\rm DSS}$ ,  $R_{\rm SP}$ , and SOA, are therefore known as the design triangle of power semiconductor devices as shown in Fig. 1[1].

Among power MOS field effect transistors (MOSFETs), lateral DMOS (LDMOS) devices have been used a lot because LDMOS have device cross-sections that are easier to be integrated into processes. Various DMOS structures featuring advantages in different aspects have also been devised. For example, a quasi-vertical trench DMOS integrated into a planar process can exhibit a better  $R_{\rm SP}$  performance than its planar counterpart [2].

Manuscript received October 29, 2011; accepted February 2, 2012. Date of publication February 10, 2012; date of current version June 6, 2012. This work was supported in part by the National Science Council (NSC), Taiwan, under Contract NSC 100-2221-E-009-048 and in part by the "Aim for the Top University Plan" of National Chiao Tung University and the Ministry of Education, Taiwan.

W.-Y. Chen is with the Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan (e-mail: wychen.ee96g@gmail.com).

M.-D. Ker is with the Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan and also with the Department of Electronic Engineering, I-Shou University, Kaohsiung 840, Taiwan (e-mail: mdker@ieee.org).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TDMR.2012.2187450

Fig. 1. Design triangle of power semiconductor devices (redrawn after [1]).

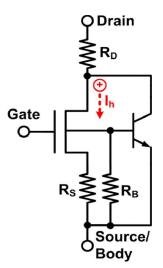

Fig. 2. Equivalent circuit model of a HV NMOS, shown with the parasitic bipolar junction transistor (BJT) in the device structure.

In this paper, the characterization of SOA in time domain and the useful techniques for SOA improvement of power MOSFETs are presented with the experimental data measured from silicon devices. This paper mainly focuses on LDMOS devices as they are popular devices in most power technologies. Results from this paper will be very useful for the designers to well adjust their designs to achieve safe operations of the power integrated circuits for field applications.

#### II. PHYSICAL LIMITATION OF SOA

The physical limitation of SOA in a power MOSFET lies in the triggering of intrinsic bipolar junction transistors (BJTs) [3]. The equivalent circuit model of a HV NMOS is shown in Fig. 2.  $R_D$ ,  $R_S$ , and  $R_B$  are, respectively drain, source, and body (parasitic) resistors of the HV NMOS; and the  $I_h$  is the hole current that can forward bias the BJT base–emitter junction

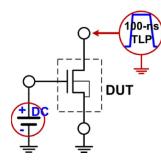

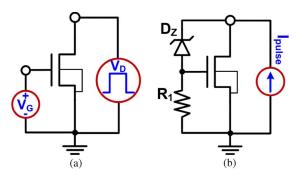

Fig. 3. Test setup for eSOA measurement by 100-ns TLP pulses.

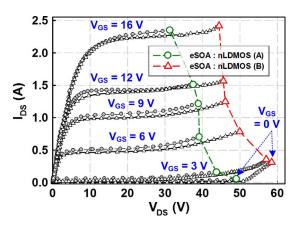

Fig. 4. Measured eSOA boundaries of two nLDMOS transistors by 100-ns TLP pulses.

through  $R_{\rm B}$  to trigger on the intrinsic NPN BJT. Major sources of the current  $I_{\rm h}$  include avalanche-generated holes  $(I_{\rm AV})$  and thermal generation  $(I_{\rm TG})$  due to device self-heating, which can be expressed as

$$I_h = I_{\rm AV} + I_{\rm TG}.$$

(1)

In (1),  $I_{\rm AV}$  is a function of the drain-source current  $I_{\rm DS}$ and avalanche multiplication factor M [3]. To minimize the effect of device self-heating and to estimate the impact of  $I_{\rm AV}$  to SOA, device under tests (DUTs) are usually stressed by the pulses with a short pulse width. Such an electrical SOA (eSOA) boundary is important when thermal effect is not strongly involved during operation. For example, small devices that benefit from good lateral thermal spreading [1]. A 50- $\Omega$  transmission line pulsing (TLP) system that delivers square pulses with an 100-ns pulse width is usually adopted for the measurement of eSOA [1], [4]. The setup of eSOA measurement is shown in Fig. 3, and the TLP-measured eSOA boundaries of two 24-V n-channel lateral DMOS (nLDMOS) devices are shown in Fig. 4. Since snapback (triggering of the intrinsic BJT) usually causes irreversible damage to a power MOSFET or circuit malfunctions, the eSOA boundary is defined by sweeping different gate biases and connecting the I-V points right before the device snapback (indicated by the symbols of circles and triangles in Fig. 3). A higher gate bias causes a reduction in  $V_{\rm DS}$  rating because a higher  $I_{\rm DS}$ accelerates the electron-hole pair generation and leads to a higher  $I_{AV}$ . The eSOA differences between the two devices A and B in Fig. 4 are discussed later in this paper (Section IV-A).

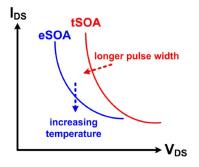

Fig. 5. Diagram showing tendencies of eSOA and tSOA with respect to temperature and pulse widths.

Fig. 6. Diagram showing SOA of a power MOSFET.

When a power MOSFET operates with strong device selfheating, the second term in (1),  $I_{\rm TG}$ , can become the dominating factor. Thermal SOA (tSOA) defines the boundary of device failure initiated by thermal instability [1], [5]. Tendencies of eSOA and tSOA boundaries with respect to temperature and pulse widths are depicted in Fig. 5 [1], [6]. When temperature increases, usually the eSOA shifts downward. A longer pulse width induces a stronger device self-heating, and the tSOA shifts inward. At a certain pulse width the tSOA boundary becomes enclosed within the eSOA. The tSOA is accordingly important for a large-area power MOSFET, or when a power MOSFET is operated with a long (~ms) pulse time, solenoid drivers for example.

Though eSOA and tSOA define boundaries from different mechanisms, the two effects are usually coupled in nature as an electrothermal effect [6], [7].  $R_{\rm D}$ ,  $R_{\rm S}$ , and  $R_{\rm B}$  resistors in the equivalent circuit model have positive temperature coefficients. The increases in  $R_{\rm D}$  and  $R_{\rm S}$  resistances under high temperature can suppress  $I_{\rm AV}$  due to a reduced  $I_{\rm DS}$ . The increase in  $R_{\rm B}$  resistance, on the contrary, help forward bias the base-emitter junction and make the parasitic BJT easier to be triggered on. Avalanche multiplication factor M and the built-in potential of a bipolar base-emitter junction are also functions of temperature [1]. Techniques to decouple the electrical and thermal effects through deactivating the parasitic BJT showed appreciable electrothermal coupling to determine the SOA of power MOSFETs [8], [9]. It is therefore hard to acquire pure electrical or thermal SOA under different gate biases, and the SOA chart of a power MOSFET usually shows boundaries under different pulse widths.

Fig. 6 is an example showing different regions of SOA for a power MSOFET. There are four regions in Fig. 6; region (A) is limited by the turn-on resistance  $R_{DS,ON}$  of the power MOSFET. Region (B) is limited by the current carrying

Fig. 7. Circuit diagram of an nLDMOS switching an external capacitor.

capability either from the power MOSFET or the package. Region (C) is determined by the operating current and voltage across the power MOSFET (power limited). When pulse width increases, region (C) moves downward due to the increasing device self-heating and the electrothermal coupling. Region (D) is defined by the maximum drain to source voltage rating, the  $BV_{DSS}$ . In Fig. 6, because boundaries are defined when turning the power transistor into on-state, it is referred to as the forwardbiased SOA (FB-SOA).

## **III. SWITCHING REACTIVE LOADS**

Power transistors are used to drive various loads in industrial and automotive applications. A switching trajectory within the SOA boundary ensures safe operation of a power transistor. Accordingly, it is equally important to understand the I–V loci when switching different loads.

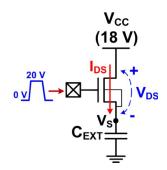

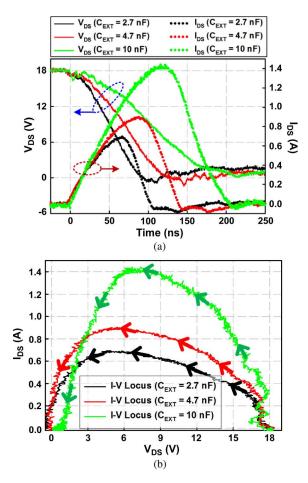

### A. Capacitive Load

When switching a resistive load, the I-V loci follow the Ohm's law and are relatively simple. However, when switching a reactive load, the switching loci become complicated. Voltage and current can have phase differences, resulting in high voltage and high current to occur at the same time. Test circuit of an nLDMOS to drive a large external discrete capacitor, output of a gate driver IC for example, is shown in Fig. 7. Capacitances used in the test circuits were 2.7, 4.7, and 10 nF. Device dimension (W/L) of the nLDMOS is 9600  $\mu$ m/0.35  $\mu$ m. When the nLDMOS is switched on,  $C_{\text{EXT}}$  is charged up through the  $I_{\rm DS}$  current of the nLDMOS. However, due to the RC time delay from resistances of nLDMOS and metal wiring, and the capacitance of  $C_{\text{EXT}}$ , source voltage (V<sub>S</sub>) of the nLDMOS is not pulled high immediately. Measured I-V waveforms in Fig. 8(a) clearly show the high  $I_{\rm DS}$  and  $V_{\rm DS}$ across the nLDMOS when switching a load capacitor. The  $I_{\rm DS}$ current in Fig. 8 is acquired from a current probe; the  $V_{\rm DS}$ voltage is calculated from  $(V_{\rm CC} - V_{\rm S})$ , where  $V_{\rm S}$  is measured by using a voltage probe. When  $C_{\text{EXT}}$  is increased, a larger RCtime delay causes a larger and a longer  $I_{\rm DS} - V_{\rm DS}$  stress across the nLDMOS. The I-V switching trajectories in Fig. 8(a) are redrawn in Fig. 8(b). Even though the peak  $I_{\rm DS}$  and  $V_{\rm DS}$  do not occur at the same time when charge/discharge a capacitor, Fig. 8 demonstrates the importance of SOA to HV transistors. Waveforms in Fig. 8(a) also suggested that when switching a

Fig. 8. Measured (a) turn-on waveforms and (b) I-V trajectories of an nLDMOS switching capacitors with different capacitance values.

Fig. 9. Test circuit for unclamped inductive switching of an nLDMOS.

capacitive load, eSOA is important due to the relatively short I-V stress time across the switching transistor [1].

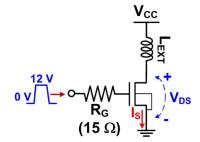

#### B. Inductive Load (Unclamped Inductive Switching)

Another typical example is the switching trajectory for inductive turn-off. Application example includes the solenoid driver or the relay actuator. The test circuit and some parameters used are shown in Fig. 9. Without additional clamping element, this test is usually referred to as the unclamped inductive switching (UIS) and is important for stringent operating environments such as automotive electronics [10]–[12].

When the nLDMOS is turned on, the current increasing rate follows the relationship of

$$\frac{di}{dt} \approx \frac{V_{\rm CC}}{L_{\rm EXT}} \tag{2}$$

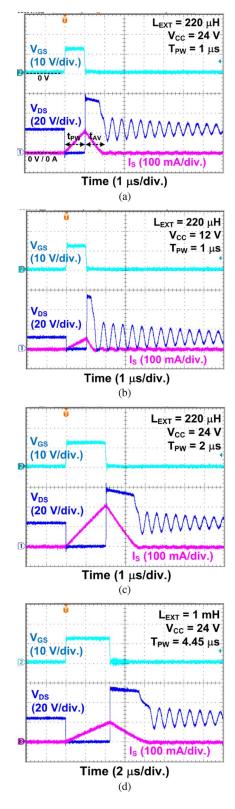

Fig. 10. Measured UIS waveforms with different  $L_{\rm EXT}$ ,  $V_{\rm CC}$ , or  $T_{\rm PW}$  parameters. (a)  $L_{\rm EXT} = 220 \ \mu$ H,  $V_{\rm CC} = 24 \ V$ , and  $T_{\rm PW} = 1 \ \mu$ S; (b)  $L_{\rm EXT} = 220 \ \mu$ H,  $V_{\rm CC} = 12 \ V$ , and  $T_{\rm PW} = 1 \ \mu$ S; (c)  $L_{\rm EXT} = 220 \ \mu$ H,  $V_{\rm CC} = 24 \ V$ , and  $T_{\rm PW} = 2 \ \mu$ S; and (d)  $L_{\rm EXT} = 1 \ m$ H,  $V_{\rm CC} = 24 \ V$ , and  $T_{\rm PW} = 4.45 \ \mu$ S.

where the total series resistance along the circuit is assumed to be small. As the measured I–V waveforms shown in Fig. 10(a), within the turn-on period  $T_{PW}$  (pulse width of the gate signal  $V_{\rm GS}$ ) the measured  $I_{\rm S}$  current linearly increases with time and the  $V_{\rm DS}$  has a voltage level close to the ground. During the turnon stage, the total energy stored in the inductor is given by

$$E = \frac{1}{2} L_{\rm EXT} I_{\rm AS}^2 \tag{3}$$

where  $I_{AS}$  is the load current right before switching off the nLDMOS.  $I_{AS}$  in Fig. 10(a) is ~110 mA, for example.

When the nLDMOS is switched off, the current flowing through the inductor cannot immediately drop to zero. The energy stored in the inductor drives up the  $V_{\rm DS}$  voltage of the nLDMOS and forces the nLDMOS to discharge the load energy through avalanche breakdown [13]–[15]. The peak current  $I_{\rm AS}$  corresponds to the avalanche current  $I_{\rm AV}$  in (1), and the energy  $E_{\rm AS}$  to be dissipated during inductive turn-off is

$$E_{\rm AS} = \frac{1}{2} L_{\rm EXT} I_{\rm AS}^2 \frac{BV}{BV - V_{\rm CC}}.$$

(4)

As the measured waveforms shown in Fig. 10(a), when the  $V_{\rm GS}$  is turned off, the  $V_{\rm DS}$  voltage shoots up to the breakdown voltage (BV) of the nLDMOS (~58 V); current begins to decrease linearly and the  $V_{\rm DS}$  voltage is kept high until  $I_{\rm S}$  drops to zero. The current decreasing rate during inductive turn-off follows:

$$\frac{di}{dt} = \frac{BV - V_{\rm CC}}{L_{\rm EXT}}.$$

(5)

Since the switching transistor is operated under avalanche breakdown, the time to discharge the energy stored in the inductor is usually referred to as  $t_{\rm AV}$ . From (5),  $t_{\rm AV}$  can be derived as [15]

$$t_{\rm AV} = \frac{L_{\rm EXT} \times I_{\rm AS}}{BV - V_{\rm CC}}.$$

(6)

With the above equations, several parameters affecting the UIS waveforms can be observed from Fig. 10. When  $V_{\rm CC}$  voltage is reduced from 24 to 12 V, (2) and (6) suggest that  $I_{\rm AS}$  should be reduced to a half and  $t_{\rm AV}$  is shortened as well [see Fig. 10(a) and (b)]. Increasing the  $T_{\rm PW}$  width from 1 to 2  $\mu$ s doubles  $I_{\rm AV}$ ;  $t_{\rm AV}$  increases as well [see Fig. 10(a) and (c)]. When the inductance is increased from 220  $\mu$ H to 1 mH,  $T_{\rm PW}$  to reach the same  $I_{\rm AV}$  current magnitude is increased from 1 to 4.45  $\mu$ s [see Fig. 10(a) and (d)]. From (4) and (6), at the same  $I_{\rm AV}$  the larger inductance results in a longer  $t_{\rm AV}$  and a larger energy to be dissipated, i.e., the transistor is stressed more severely.

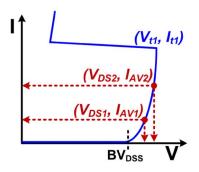

From Fig. 10(a) and (c), dependence between the peak  $V_{\rm DS}$  voltage and the  $I_{\rm AV}$  magnitude during inductive turnoff, though weak, is also observed. For a gate-grounded nLDMOS entering avalanche breakdown, the I–V characteristic is illustrated as Fig. 11. When the  $V_{\rm DS}$  voltage across an nLDMOS is higher than its  $BV_{\rm DSS}$ , avalanche current  $I_{\rm AV}$ starts to flow; snapback does not happen immediately until the current magnitude reaches  $I_{\rm t1}$ , at which the BJT base–emitter junction is forward biased through  $R_{\rm B}$  (see Fig. 2). The  $I_{\rm AS}$ current level during UIS test cannot exceed  $I_{\rm t1}$ , otherwise the nLDMOS snaps back and a latchup-like electrical overstress

Fig. 11. Diagram depicting the I-V characteristic of a gate-grounded nLDMOS.

Fig. 12. CIS test circuit using a Zener diode to clamp the nLDMOS drain voltage during inductive turn-off.

will permanently damage the nLDMOS. For an UIS test with a peak inductor current  $I_{AS1}$ , the energy stored in the inductor will correspondingly charge up the drain voltage to  $V_{DS1}$  during inductive turn-off so as to keep current continuity. From Fig. 11, it is known that a higher peak inductor current  $I_{AV2}$  causes a higher voltage  $V_{DS2}$  during inductive turn-off. Note that  $I_{TG}$  in (1) can contribute greatly to the device snapback in UIS because of the high power during avalanche breakdown and the long  $t_{AV}$ during inductive turn-off (from several  $\mu$ s up to several tens of ms) [16].

Because the stress across the transistor in an UIS test happens when turning off the transistor, it is classified as the reverse-biased SOA (RB-SOA) and usually uses different rating methods than the FB-SOA [17]. The term RB-SOA is often reserved for BJTs switching unclamped inductive load, and for MOSFETs UIS is used more often. To evaluate the transistor ruggedness against UIS, two parameters are usually adopted as the benchmark. The first parameter is the maximum allowable switching current ( $I_{AS,Max}$ ) without inducing transistor failure [10], [18]. The other rating method uses (4), the maximum energy  $E_{AS,Max}$  dissipated in the switching transistor without inducing failure, as the benchmark. The second method is also known as the energy capability of a power MOSFET [11].

## C. Inductive Load (Clamped Inductive Switching)

Due to the high junction temperature over a MOSFET during avalanche breakdown, UIS is a harsh test for power MOSFETs. In practical designs, the clamped inductive switching (CIS) is usually used to bypass the energy during inductive turn-off without avalanching the switching transistor.

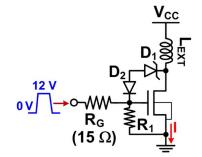

An example of the CIS circuit is shown in Fig. 12 [8], [19]. When switching off the inductive load, the Zener diode  $D_1$

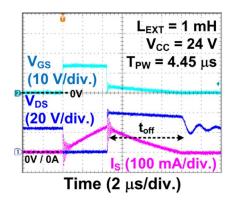

Fig. 13. Measured I–V waveforms of the CIS test circuit. The breakdown voltage of the Zener diode is 37 V.

breaks down and a current  $I_Z$  pulls high the gate potential of the nLDMOS through the diode  $D_2$  and the  $R_1$  resistor. The  $D_1$  diode is chosen to have a breakdown voltage  $BV_Z$  smaller than the  $BV_{Dss}$  of the nLDMOS so as to prevent nLDMOS from avalanche breakdown. The drain voltage of the nLDMOS during inductive turn-off is therefore limited at  $V_{\rm clamp} =$  $BV_z + V_{diode} + (R_1 \times I_z)$ . With the gate potential pulled high, the energy stored in the inductor is mainly discharged through the channel current of the nLDMOS. Measured I-V waveforms of the CIS test circuit are shown in Fig. 13;  $BV_Z$  of the Zener diode  $D_1$  in Fig. 13 is 37 V, and the nLDMOS is the same transistor used to measure Fig. 10. When switching off the inductor, the measured  $V_{\rm DS}$  voltage is clearly limited at a lower voltage level around the  $BV_Z$  of  $D_1$ . Note that in a CIS circuit, FB-SOA of the switching transistor is important as well because the transistor has to sustain  $V_{\text{clamp}}$  and the inductive turn-off current at the same time.

In the CIS circuit, because the drain voltage of the nLDMOS is limited at  $V_{\text{clamp}}$ , the time  $t_{\text{off}}$  to dissipate the energy stored in the inductor becomes

$$t_{\rm off} = \frac{L_{\rm EXT} \times I_{\rm MAX}}{V_{\rm clamp} - V_{\rm CC}} \tag{7}$$

where  $I_{\text{MAX}}$  is the current right before switching off the nLDMOS. Comparing (6) and (7), with the  $V_{\text{clamp}}$  smaller than the breakdown voltage of the nLDMOS, the CIS circuit results in a longer inductive turn-off time as shown in Fig. 13. The energy dissipated in the nLDMOS during inductive turn-off becomes

$$E_{\rm AS} = \frac{1}{2} L_{\rm EXT} I_{\rm MAX}^2 \frac{V_{\rm clamp}}{V_{\rm clamp} - V_{\rm CC}}.$$

(8)

When measuring energy capabilities, (4) and (8) show that different inductances, current magnitudes, Zener diodes . . . etc. have to be changed during tests to figure out the  $E_{AS,MAX}$  of a DUT. The test procedures are inconvenient and difficult to control. To facilitate the measurement, alternative rectangular power pulsing (RPP) test methods which use rectangular voltage or current pulses with different pulse widths have been proposed [19]. Voltage and current RPP testing circuits are shown in Fig. 14(a) and (b), respectively. The RPP tests save the usage of external inductors. Energy capabilities of DUTs can be easily figured out simply by varying pulse widths or magnitudes of delivered voltage/current pulses. Though in a

Fig. 14. Measurement setups for (a) voltage and (b) current rectangular power pulsing test circuits (redrawn after [19]).

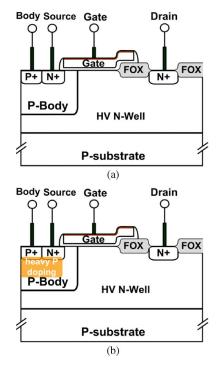

Fig. 15. Device cross-sections of (a) a regular nLDMOS and (b) an nLDMOS with additional P-type implantation at body to improve SOA.

real inductive switching condition the current waveform is in a triangular shape, RPP tests have been verified to deliver reasonably accurate results [19].

## IV. TECHNIQUES TO SOA IMPROVEMENT IN HIGH-VOLTAGE INTEGRATED CIRCUITS

A power MOSFET with wide intrinsic SOA can enhance device reliability under different load conditions. As a result, aside from the CIS method to assist transistors, various techniques to improve the intrinsic SOA of power MOSFETs have been proposed.

#### A. Additional Body Implantation

Since the criterion for a BJT to be triggered on is the forward conduction of its base-emitter junction, reducing the resistance of  $R_{\rm B}$  in Fig. 2 is effective in widening the MOSFET SOA [20]–[23]. The process integration method in reducing the  $R_{\rm B}$  resistor is illustrated in Fig. 15. Comparing to the regular nLDMOS structure shown in Fig. 15(a), an additional

Fig. 16. Device cross-sectional view of an nLDMOS with the additional drain adaptive region to improve SOA.

P-type body implantation (PBI) is added to elevate the doping concentration of P-body [see Fig. 15(b)]. An nLDMOS which does not have the PBI layer showed the measured eSOA boundary (A) in Fig. 4; another nLDMOS with the additional PBI layer has the eSOA boundary (B) in Fig. 4. Except for the additional body implantation, both devices have the same layout and device dimension, 4800  $\mu$ m/0.35  $\mu$ m. It is clear from Fig. 4 that the additional P-type body implantation substantially improves the FB-SOA of power MOSFETs. With the reduced  $R_{\rm B}$ ,  $I_{\rm AS,MAX}$  in an UIS test for the 4800- $\mu$ m nLDMOS improves from 100 to 350 mA as well, a result consistent to previous publications [20], [21].

## B. Drift Configuration

It is well known that for a power MOSFET under high current conduction, the kirk effect shifts the high electric field region toward the transistor drain contacts [24]. Since the avalanche current that induces both the triggering of parasitic BJTs and the electrothermal coupling is a result of the high electric field, engineering the drift region of a power MOSFET is another approach to the SOA adjustment. A higher doping concentration in the drift region of an nLDMOS can compensate the negative electron charges during transistor on-state and hence push the onset of kirk effect to a higher current level [25]. However, increasing the doping concentration in the drift region reduces the device  $BV_{DSS}$  as well [26]. Lengthening the drift region is another method to adjust the device SOA because the higher series resistance from the drift region limits the transistor saturation current. This, however, results in a higher transistor  $R_{\rm SP}$ . Accordingly, an adaptive method that introduces an additional n-type adaptive doping region was proposed to counteract the drawbacks and to improve the transistor SOA [23], [26]-[28]. The device cross-sectional view of an nLDMOS with the adaptive doping region is shown in Fig. 16; the adaptive region has a doping concentration higher than that of the HV N-Well. Besides the benefit on the SOA, the drain profile has also been reported as a key device parameter for implementing power MOSFETs with high electrostatic discharge (ESD) protection levels [23], [29]–[33].

## C. Dotted-Channel LDMOS

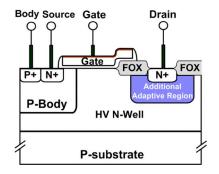

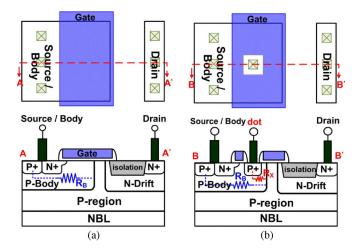

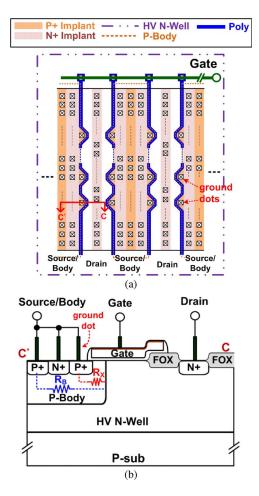

Using additional body implantation to reduce the  $R_{\rm B}$  resistance and to suppress the BJT action is useful, but often inaccessible to fabless IC design companies. A dotted-channel layout

Fig. 17. Layout and device cross-sectional views of (a) a regular LDMOS and (b) a dotted-channel LDMOS (redrawn after [34]).

technique for the SOA improvement without modifying process steps or mask layers is reported in [34]. As illustrated in Fig. 17, poly gate in a dotted-channel LDMOS is intentionally opened with squares to insert P+ diffusion regions and metal contacts (dots). When these dots are grounded through metallurgical connection, an additional parasitic resistor  $R_X$  is formed [see Fig. 17(b)];  $R_X$  is in parallel with the body resistor  $R_B$  of a regular LDMOS and hence, the effective body resistance  $R_B$ ' in a dotted-channel LDMOS becomes  $(R_B//R_X)$ , and the parasitic BJT is suppressed.

In the dotted-channel layout, in order to open dots in transistor poly gate the gate length may need to be extended, depending on the technology node being used. Moreover, to prevent transistor breakdown voltage from being affected by the dots, the distance between the dotted contact and the drift region has to be larger than the minimum allowable channel length [34]. These restrictions result in a negative impact to transistor  $R_{\rm SP}$ , and the quantity of impact is highly processdependent. Recently, a poly-bending layout structure that bends the poly gate in  $45^{\circ}$  was proposed. The poly-bending layout has ground dots as well to improve the degraded SOA of an nLDMOS due to the insertion of a silicon controlled rectifier [35]. This poly-bending layout can also be implemented on an nLDMOS. Layout top view of an nLDMOS utilizing the polybending layout is illustrated in Fig. 18(a), and the device crosssectional view along the C - C' line is shown in Fig. 18(b). The ground dots in the poly-bending nLDMOS create an additional  $R_{\rm X}$  similar to the dotted-channel LDMOS, thus making the poly-bending layout promising for the SOA improvement of nLDMOS transistors.

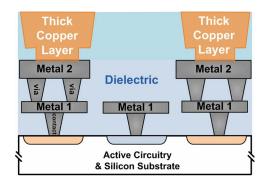

## D. Thick Copper Metallization

For a power transistor that operates with a long on-state period or has a large device area ( $\sim$ mm<sup>2</sup>), thermal effect is prominent and the transistor junction temperature can become high enough to initiate thermal runaway [36], [37]. The removal of the temperature rise within the active transistor in response to the dissipated energy accordingly helps improve the device stability. In power technologies, this can be accomplished by

Fig. 18. (a) Layout top view and (b) device cross-sectional view along C - C' line of a poly-bending nLDMOS.

Fig. 19. Illustration of the thick copper metallization in power ICs for the improvement of transistor SOA.

using a heat sink over the power transistor. Due to the good thermal properties and mature process integration techniques to handle with, copper is chosen over other metal materials. As illustrated in Fig. 19, thick copper metal layers are plated over active circuitry to serve as a waver-level heat sink [38]–[40]. This on-chip technique is equally important for sub-millisecond operations where the time is not enough for the IC packaging to give an effect to the device temperature [41], [42]. The copper metallization has been demonstrated to substantially improve the transistor energy capability, and a thicker copper metallization further enhances the improvement [38]–[42]. Moreover, it

Fig. 20. Illustration of power MOSFET arrays with (a) single-step, (b) dual step, and (c) checkerboard layout design for improving the uniformity of power distribution (redrawn after [44]).

is also used as a surface layer of metal wiring to solve the voltage de-biasing effect [43] in large power MOSFETs and to save power consumption through the reduced overall  $R_{ON}$ [38], [40].

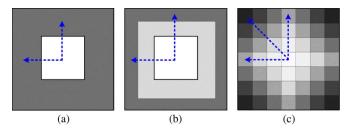

#### E. Power Distribution

With the strong device self-heating involved in switching a large power MOSFET, the temperature spread across the transistor array is found to be inhomogeneous. Device edges benefit from a better thermal removal through surrounding silicon and the weak spot (highest temperature) hence locates at the center of the array [37], [44]. A uniform temperature distribution across the power transistor array eliminates the weak spot and improves the transistor energy capability.

From the 1-dimensional heat flow theory, a simple relationship between power dissipation P, temperature increase  $\Delta T$ and time t is

$$\Delta T = \frac{2P}{\sqrt{\pi k \rho c_p} A_E} \sqrt{t} \tag{9}$$

where k is thermal conductivity,  $\rho$  is density,  $c_p$  is specific heat capacity, and  $A_E$  is active area. From (9), the temperature increase is proportional to the power dissipation and the square root of time. Having different operating time among an array is less practical; uniform power distribution across a power MOSFET array is more feasible. With the MOSFET saturation current being

$$I_{D,\text{sat}} = \frac{1}{2}\mu C_{\text{ox}} \frac{W}{L} (V_{\text{GS}} - V_t)^2$$

(10)

a multi-step layout design utilizing different current carrying capabilities is proposed to engineer the power distribution (see Fig. 20) [44]. Power MOSFET arrays are divided into regions of different channel lengths (L) or oxide thickness. Arrows in Fig. 20 indicate the direction of increasing current carrying capability (shorter channel length for example). Experimental results in [44] showed a more than 20% improvement on the energy capability and less than 10% increase on transistor turn-on resistance. Moreover, with a proper design, the simple single-step layout shown in Fig. 20(a) was able to optimize the power distribution to its fullest already [44].

#### V. CONCLUSION

A wide SOA is required to sustain the high voltage and high current at the same time that happens across a power MOSFET during the circuit operations with the switching of reactive loads. Through the circuit design technique, clamped inductive switching can help improve SOA when driving an inductive load. Process integration approaches such as a heavily doped body region, an adaptive drift implantation, or a thick plated copper layer can improve intrinsic SOA of power MOSFETs. Besides the circuit and the process integration methods, layout modifications can also enhance SOA of power MOSFETs. In summary, safe operating area is one of the most important indicators for the reliability of power MOSFETs. Improvement techniques on the SOA will keep continuing as an essential and critical factor in the development of power MOSFETs for using in high-voltage integrated circuits.

#### ACKNOWLEDGMENT

The authors would like to thank Hanwa Electronic Ind. Company, Ltd., Japan, particularly to T. Hasebe, K. Hasegawa, and M. Sawada, for their support with the equipment of the transmission line pulsing system to National Chiao Tung University, Hsinchu, Taiwan.

#### REFERENCES

- P. Hower, "Safe operating area—A new frontier in Ldmos design," in Proc. Int. Symp. Power Semicond. Devices ICs, 2002, pp. 1–8.

- [2] T. Dyer, J. McGinty, A. Strachan, and C. Bulucea, "Monolithic integration of trench vertical DMOS (VDMOS) power transistors into a BCD process," in *Proc. Int. Symp. Power Semicond. Devices ICs*, 2005, pp. 1–4.

- [3] C. Hu and M.-H. Chi, "Second breakdown of vertical power MOSFETs," *IEEE Trans. Electron Devices*, vol. ED-29, no. 8, pp. 1287– 1293, Aug. 1982.

- [4] T. Maloney and N. Khurana, "Transmission line pulsing techniques for circuit modeling of ESD phenomena," in *Proc. EOS/ESD Symp.*, 1985, pp. 49–54.

- [5] P. Moens and G. Van den bosch, "Characterization of total safe operating area of lateral DMOS transistors," *IEEE Trans. Device Mater. Rel.*, vol. 6, no. 3, pp. 349–357, Sep. 2006.

- [6] P. Hower, C. Tsai, S. Merchant, T. Efland, S. Pendharkar, R. Steinhoff, and J. Brodsky, "Avalanche-induced thermal instability in LDMOS transistors," in *Proc. Int. Symp. Power Semicond. Devices ICs*, 2001, pp. 153–156.

- [7] Y. Chung and B. Baird, "Electrical-thermal coupling mechanism on operating limit of LDMOS transistor," in *IEDM Tech. Dig.*, 2000, pp. 83–86.

- [8] D. Farenc, G. Charitat, P. Dupuy, T. Sicard, I. Pages, and P. Rossel, "Clamped inductive switching of LDMOST for smart power ICs," in *Proc. Int. Symp. Power Semicond. Devices ICs*, 1998, pp. 359–362.

- [9] B. Khemka, V. Parthasarathy, R. Zhu, and A. Bose, "A novel technique to decouple electrical and thermal effects in SOA limitation of power LDMOSFET," *IEEE Electron Device Lett.*, vol. 25, no. 10, pp. 705–707, Oct. 2004.

- [10] Single Pulse Unclamped Inductive Switching (UIS) Avalanche Test Method, JEDEC Std. JESD 24-5, Oct. 2002.

- [11] Method for Repetitive Inductive Load Avalanche Switching, JEDEC Std. JESD 24-8, Oct. 2002.

- [12] Short Circuit Reliability Characterization of Smart Power Devices for 12 V Systems, AEC-Q101-006, Sep. 2006.

- [13] J. Phipps and K. Gauen, "New insights affect power MOSFET ruggedness," in Proc. IEEE Appl. Power Electron. Conf., 1988, pp. 290–298.

- [14] K. Fischer and K. Shenai, "Dynamics of power MOSFET switching under unclamped inductive loading conditions," *IEEE Trans. Electron Devices*, vol. 43, no. 6, pp. 1007–1015, Jun. 1996.

- [15] K. Chinnaswamy, P. Khandelwal, M. Trivedi, and K. Shenai, "Unclamped inductive switching dynamics in lateral and vertical power DMOSFETs," in *Conf. Rec. IEEE IAS Annu. Meeting*, 1999, pp. 1085–1092.

- [16] J. McGloin and D. Sdrulla, "Estimating the temperature rise of power MOSFETs during the UIS test," in *Proc. Appl. Power Electron. Conf.*, 1992, pp. 448–453.

- [17] J. Steighner and J.-S. Yuan, "The effect of SOA enhancement on device ruggedness under UIS for the LDMOSFET," *IEEE Trans. Device Mater. Rel.*, vol. 11, no. 2, pp. 254–262, Jun. 2011.

- [18] R. Stoltenburg, "Boundary of power-MOSFET unclamped inductiveswitching (UIS) avalanche-current capability," in Proc. Appl. Power Electron. Conf., 1989, pp. 359-364.

- [19] G. Van den Bosch, P. Moens, P. Gassot, D. Wojciechowski, and G. Groeseneken, "Analysis and application of energy capability characterization methods in power MOSFETs," in Proc. Eur. Solid-State Device Res. Conf., 2004, pp. 453-456.

- [20] C. Kocon, J. Zeng, and R. Stokes, "Implant spacer optimization for the improvement of power MOSFETs unclamped inductive switching (UIS) and high temperature breakdown," in Proc. Int. Symp. Power Semicond. Devices ICs, 2000, pp. 157-160.

- [21] X. Zhou, J. Ng, and J. Sin, "A novel SONOS gate power MOSFET with excellent UIS capability," IEEE Electron Device Lett., vol. 32, no. 10, pp. 1415–1417, Oct. 2011.

- [22] P. Hower, J. Lin, S. Pendharkar, B. Hu, J. Arch, J. Smith, and T. Efland, "A rugged LDMOS for LBC5 technology," in Proc. Int. Symp. Power Semicond. Devices ICs, 2005, pp. 327-330.

- [23] K. Kawamoto, S. Takahashi, S. Fujino, and I. Shirakawa, "A no-snapback LDMOSFET with automotive ESD endurance," IEEE Trans. Electron Devices, vol. 49, no. 11, pp. 2047-2053, Nov. 2002.

- [24] P. Hower and S. Merchant, "Snapback and safe operating area of LDMOS transistors," in IEDM Tech. Dig., 1999, pp. 193-196.

- [25] Y. Taur and T. Ning, Fundamentals of Modern VLSI Devices, 2nd ed. Cambridge, U.K.: Cambridge Univ. Press, 2009.

- [26] K. Kinoshita, Y. Kawaguchi, and A. Nakagawa, "A new adaptive resurf concept for 20 V LDMOS without breakdown voltage degradation at high current," in Proc. Int. Symp. Power Semicond. Devices ICs, 1998, pp. 65-68.

- [27] P. Hower, J. Lin, S. Merchant, and S. Paiva, "Using adaptive resurf to improve the SOA of Ldmos transistors," in Proc. Int. Symp. Power Semicond. Devices ICs, 2000, pp. 345-348.

- [28] B. Bakeroot, P. Moens, M. Vermandel, and J. Doutreloigne, "Using adaptive RESURF technique and field plate working to improve the safe operating area of n-type drain extended MOS transistors," in Proc. Int. Conf. Model. Simul. Microsyst., 2001, pp. 498-501.

- [29] Electrostatic Discharge Sensitivity Testing-Human Body Model (HBM)-Component Level ESD Association, Std. Test Method ESD STM5.1, 2001.

- [30] V. Parthasarathy, V. Khemka, R. Zhu, J. Whitfield, R. Ida, and A. Bose, "Drain profile engineering of RESURF LDMOS devices for ESD ruggedness," in Proc. Int. Symp. Power Semicond. Devices ICs, 2002, pp. 265–268.

- [31] V. Parthasarathy, V. Khemka, R. Zhu, J. Whitfield, A. Boase, and R. Ida, "A double RESURF LDMOS with drain profile engineering for improved ESD robustness," IEEE Electron Device Lett., vol. 23, no. 4, pp. 212-214, Apr. 2002.

- [32] K. Kim and W.-J. Choi, "Effects of background doping concentration on ESD protection properties of high-voltage operation extended drain N-type MOSFET device," in Proc. IEEE Int. Rel. Phys. Symp., 2007, pp. 334-341.

- [33] T. Imoto, K. Mawatari, K. Wakiyama, T. Kobayashi, M. Yano, M. Shinohara, T. Kinoshita, and H. Aasai, "A novel ESD protection device structure for HV-MOS ICs," in Proc. IEEE Int. Rel. Phys. Symp., 2009, pp. 663–668.

- [34] T. Khan, V. Khemka, R. Zhu, and A. Bose, "Rugged dotted-channel LDMOS structure," in IEDM Tech. Dig., 2008, pp. 129-132.

- [35] W.-Y. Chen and M.-D. Ker, "Improving safe operating area of nLDMOS array with embedded silicon controlled rectifier for ESD protection in a 24-V BCD process," IEEE Trans. Electron Devices, vol. 58, no. 9, pp. 2944–2951, Sep. 2011.

- [36] G. Haberfehlner, S. Bychikhin, V. Dubec, M. Heer, A. Podgaynaya, M. Pfost, M. Stecher, E. Gornik, and D. Pogany, "Thermal imaging of smart power DMOS transistors in the thermally unstable regime using a compact transient interferometric mapping system," Microelectron. Reliab., vol. 49, no. 9-11, pp. 1346-1351, Sep.-Nov. 2009.

- [37] M. Pfost, D. Costachescu, A. Podgaynaya, M. Stecher, S. Bychikhin, D. Pogany, and E. Gornik, "Small embedded sensors for accurate temperature measurements in DMOS power transistors," in Proc. IEEE Int. Conf. Microelectron. Test Struct., 2010, pp. 3-7.

- [38] E. Kobori, N. Izumi, N. Kumamoto, and Y. Hamazawa, "Efficiency of power devices using full Cu metallization technologies," in Proc. Int. Symp. Power Semicond. Devices ICs, 1999, pp. 67-70.

- [39] G. Van den bosch, T. Webers, E. Driessens, B. Elattari, D. Wojciechowski, P. Gassot, P. Moens, and G. Groeseneken, "Design and characterization of a post-processed copper heat sink for smart power drivers," in Proc. IEEE *Int. Conf. Microelectron. Test Struct.*, 2005, pp. 27–31. [40] T. Efland, C.-Y. Tsai, and S. Pendharkar, "Lateral thinking about power

- devices (LDMOS)," in IEDM Tech. Dig., 1998, pp. 679-682.

- [41] Y. Chung, T. Willett, V. Macary, S. Merchant, and B. Baird, "Energy capability of power devices with Cu layer integration," in Proc. Int. Symp. Power Semicond. Devices ICs, 1999, pp. 63-66.

- [42] F. Alagi, L. Labate, A. Andreini, and C. Contiero, "Sub-millisecond energy handling capability improvement of IC power devices with thick copper metallization," in Proc. Int. Symp. Power Semicond. Devices ICs, 2003, pp. 249-252.

- [43] M. Darwish, J. Huang, M. Liu, M. Shekar, R. Williams, and M. Cornell, "Scaling issues in lateral power MOSFETs," in Proc. Int. Symp. Power Semicond. Devices ICs, 1998, pp. 329-332.

- [44] V. Khemka, V. Parthasarathy, R. Zhu, A. Bose, and T. Roggenbauer, "Detection and optimization of temperature distribution across large-area power MOSFETs to improve energy capability," IEEE Trans. Electron Devices, vol. 51, no. 6, pp. 1025-1032, Jun. 2004.

Wen-Yi Chen received the B.S., M.S., and Ph.D. degrees from the Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan.

He is currently with the Institute of Electronics, National Chiao Tung University. His current research interests include reliability designs in high-voltage technologies.

Dr. Chen was a recipient of the Graduate Student Study Abroad Program supported by the National Science Council, Taiwan.

Ming-Dou Ker (S'92-M'94-SM'97-F'08) received the Ph.D. degree from the Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan, in 1993.

He ever worked as the Department Manager with the VLSI Design Division, Computer and Communication Research Laboratories, Industrial Technology Research Institute, Hsinchu. Since 2004, he has been a Full Professor with the Department of Electronics Engineering, National Chiao Tung University, where he is currently a Distinguished Professor. During

2008-2011, he was a Chair Professor and the Vice President of I-Shou University, Kaohsiung, Taiwan. He ever served as the Executive Director of the National Science and Technology Program on System-on-Chip in Taiwan during 2010-2011 and has been serving as the Executive Director of the National Science and Technology Program on Nano Technology in Taiwan (2011-2014). In the technical field of reliability and quality design for microelectronic circuits and systems, he has published over 450 technical papers in international journals and conferences. He has proposed many solutions to improve the reliability and quality of integrated circuits (ICs), which have been granted with 190 U.S. patents and 165 Taiwan patents. He had been invited to teach and/or to consult the reliability and quality design for ICs by hundreds of design houses and semiconductor companies in the worldwide IC industry. His current research interests include reliability and quality design for nanoelectronics and gigascale systems, as well as the biomimetic circuits and systems for intelligent prosthesis.

Prof. Ker has served as a member of the Technical Program Committee and the Session Chair of numerous international conferences for many years. He ever served as an Associate Editor for the IEEE TRANSACTIONS ON VLSI SYSTEMS in 2006–2007. He was selected as the Distinguished Lecturer in the IEEE Circuits and Systems Society (2006-2007) and in the IEEE Electron Devices Society (2008-2012). He was the Founding President of Taiwan ESD Association.