# **On-Chip HBM and HMM ESD Protection Design** for RF Applications in 40-nm CMOS Process

Jie-Ting Chen<sup>®</sup>, Chun-Yu Lin<sup>®</sup>, *Senior Member, IEEE*, Rong-Kun Chang, and Ming-Dou Ker<sup>10</sup>, Fellow, IEEE

Abstract-On-chip electrostatic discharge (ESD) protection device with large dimension can sustain high-ESD current, but the parasitic capacitance of the ESD protection device will increase the difficulty of impedance matching and degrade the bandwidth for broadband radio frequency (RF) applications. The traditional distributed ESD protection circuit can achieve good impedance matching, but it has a worse ESD robustness because of larger resistance caused by the input inductor. In this paper, a new distributed ESD protection structure with the stacked diodes with embedded silicon-controlled rectifier is proposed to attain good ESD robustness without degrading the RF performance. The proposed ESD protection circuit has been successfully verified in a 40-nm, 2.5-V CMOS process to sustain a human-metal model of 5 kV. The proposed ESD protection circuit is suitable to protect the broadband RF circuits in advanced nanoscale CMOS technology.

Index Terms—Distributed electrostatic discharge (ESD) protection, ESD, radio frequency (RF), silicon-controlled rectifier (SCR).

## I. INTRODUCTION

**X** TITH the development of CMOS technology, improving the high-frequency characteristics and quality of reliability in radio frequency (RF) ICs has been the ultimate goal of the IC industry [1]. The electrostatic discharge (ESD) protection ability has become one of the important concerns on the reliability of IC products. Unfortunately, devices in nanoscale CMOS technology are very sensitive to ESD events due to the lower gate oxide breakdown and junction breakdown voltages [2], [3], but the commercial IC products still need to pass the required ESD specification, such as 1 kV in the human-body model (HBM) [4], [5] or more. For the RF IC applications, the major concern of ESD protection design is the parasitic effect of the ESD protection circuit. It will

Manuscript received May 31, 2018; revised September 11, 2018; accepted September 25, 2018. Date of publication October 22, 2018; date of current version November 26, 2018. This work was supported in part by Novatek Microelectronics Corporation, Taiwan, and in part by the Ministry of Science and Technology, Taiwan, under Contract MOST 107-2622-8-009-006-TE1. The review of this paper was arranged by Editor E. Rosenbaum. (Corresponding author: Ming-Dou Ker.)

J.-T. Chen, R.-K. Chang, and M.-D. Ker are with the Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan (e-mail: mdker@ieee.org).

C.-Y. Lin is with the Department of Electrical Engineering, National Taiwan Normal University, Taipei 106, Taiwan (e-mail: cy.lin@ieee.org). Color versions of one or more of the figures in this paper are available

online at http://ieeexplore.ieee.org

Digital Object Identifier 10.1109/TED.2018.2873768

Power-Rail ESD Clamp Circuit Device Device Lı RF ⊠--000 Internal 000 N-Type Circuit I/O N-Type  $L_2$ ESD Pad ESD Device Device Vss

VDD

P-Type

ESD

P-Type

ESD

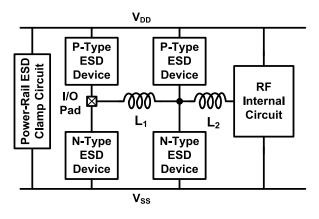

Fig. 1. Traditional distributed ESD protection circuit with ESD devices in two stages for RF applications [6]-[8].

strongly degrade the bandwidth in normal RF operation [6]. Therefore, the ESD protection circuit should be designed to achieve the desired RF performance as well as sustain good ESD robustness.

Several ESD protection designs have been reported to improve the impedance matching and to achieve the requested ESD robustness for RF circuits [7], [8]. Fig. 1 shows a traditional distributed ESD protection circuit, which is composed of two inductors  $(L_1 \text{ and } L_2)$  and two stages of ESD protection devices [9]–[11]. However, some characteristics of this structure during ESD stress condition should be further optimized for RF applications. First, the inductor  $(L_1)$  connected to I/O pad will cause a higher turn-ON resistance and clamp voltage during the ESD stress condition, even though this structure has a good broadband RF performance. Second, the metal width of the inductor  $(L_1)$  should be widened to enhance the current handling capability. It will enlarge the footprint in the layout. Third, the ESD protection device of the diode has a higher parasitic capacitance [12], [13], which will result in a weaker ESD protection ability than silicon-controlled rectifier (SCR) under the same value of parasitic capacitance. Consequently, a modified scheme of the distributed network to further optimize ESD protection ability and RF performance is needed.

Recently, new test method, human-metal model (HMM) [14], using the system-level ESD gun to directly zap the I/O ports of the stand-alone devices or circuit module is adopted by some industrial companies. Compared with the HBM, the system-level ESD gun has a higher storage capacitor and a lower discharge resistor. It creates more than  $5 \times$  ESD peak current that can cause serious damage to the I/O pins [15]-[18]. Therefore, the HMM test method will

Fig. 2. New proposed distributed ESD protection circuit with ESD devices in two stages for RF applications.

increase the difficulty of on-chip ESD protection design for RF applications.

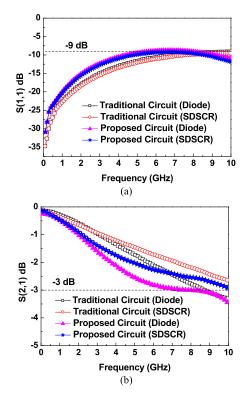

The purpose of this paper is to investigate the characteristic of the distributed structure during a high-ESD current condition. A new ESD protection circuit with the stacked diodes with embedded SCR (SDSCR) [19]-[21] for RF applications is proposed and fabricated in 40-nm 2.5-V CMOS process. The ESD protection devices of the first stage are put under the I/O pad to reduce layout area and can discharge the ESD current immediately. In detail, the specifications in this paper of input return loss  $(S_{11})$  and insertion loss  $(S_{21})$  are -9 and -3 dB, respectively, during the operating frequency from 0.1 to 10 GHz. In addition to the traditional ESD test method, this paper performed the HMM test method on the test circuits. As compared with the traditional distributed ESD protection circuit, this newly proposed protection circuit has achieved lower turn-ON resistance, good ESD robustness, and required RF performance. It is more desirable than the traditional distributed ESD protection circuit under high-ESD current stress.

# II. NEW DISTRIBUTED ESD PROTECTION DESIGN

#### A. Circuits Implementation

In the traditional distributed ESD protection circuit, the inductors have been utilized to compensate the effect of the parasitic capacitances generated by ESD protection devices. Following this concept, the new proposed distributed ESD protection circuit that consists of two inductors  $(L_1 \text{ and } L_2)$  and two stages of ESD protection devices is presented in Fig. 2. Inductors  $L_1$  and  $L_2$  are used to match the input impedance. Furthermore,  $L_2$  that has small size can limit the ESD current to avoid gate oxide damage to the internal circuit. In ESD protection devices, several studies have noted that SDSCR has good ESD robustness and low-parasitic effect [19]-[21]. Accordingly, the proposed circuit has replaced the ESD protection diode with the p-type SDSCR and the n-type SDSCR. Considering the HMM issue, the ESD protection devices are designed to be under the I/O pad. Thus, it can quickly conduct the ESD current to the protection devices by via. In addition,

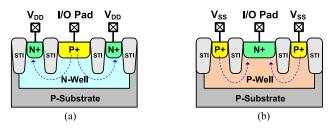

Fig. 3. Device cross-sectional view of (a) p+/n-well diode and (b) n+/p-well diode.

Fig. 4. Device cross-sectional views of (a) p-type SDSCR and (b) n-type SDSCR.

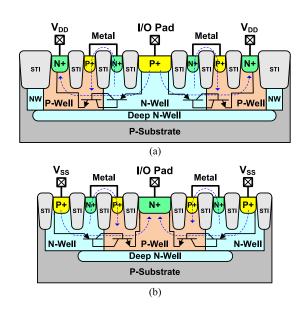

Fig. 5. Simplified model of (a) p-type SDSCR and (b) n-type SDSCR.

this design can also reduce the turn-ON resistance of the ESD protection device to get better ESD protection ability.

To investigate the influence of the ESD protection device on the traditional and the proposed distributed ESD protection circuit, the ESD protection devices in each design are realized with two types of devices, traditional diode and SDSCR. The traditional p+/n-well diode, n+/p-well diode, p-type SDSCR, and n-type SDSCR are shown in Figs. 3 and 4. The equivalent circuit of SCR is made up of a p-n-p bipolar junction transistor (BJT) and an n-p-n BJT. The layout is drawn in stripe style, and the width is selected as 30  $\mu$ m per finger. The layout area of p+/n-well is equal to that of n+/p-well in each ESD device layout. The simplified model of SDSCR that consists of the junction capacitances is shown in Fig. 5, where the junction capacitance of p-well/n-well is neglected because of the short circuit by metal. The capacitance of the diode seen on the I/O pad is about 1.4× as large as that of the SDSCR. Estimated by

TABLE I DESIGN PARAMETERS OF THE ESD PROTECTION CIRCUITS

| Design<br>parameters   | Traditional distributed<br>ESD protection circuit | Proposed distributed<br>ESD protection circuit |  |  |  |  |

|------------------------|---------------------------------------------------|------------------------------------------------|--|--|--|--|

| C <sub>Pad</sub> (fF)  | 100                                               | 100                                            |  |  |  |  |

| C <sub>ESD1</sub> (fF) | 240                                               | 240                                            |  |  |  |  |

| C <sub>ESD2</sub> (fF) | 240                                               | 360                                            |  |  |  |  |

| L <sub>1</sub> (pH)    | 360                                               | 700                                            |  |  |  |  |

| L <sub>2</sub> (pH)    | 360                                               | 170                                            |  |  |  |  |

Fig. 6. Equivalent RF circuit models of (a) traditional distributed ESD protection circuit in two stages and (b) new proposed distributed ESD protection circuit in two stages.

the foundry's data, the parasitic capacitance of the diode and the SDSCR is about 30 and 20 fF, respectively, in each finger with a width of 30  $\mu$ m. According to the previous report [22], the capacitance of the first stage ESD protection device ( $C_{\text{ESD1}}$ ) is assumed to be 240 fF, which is sufficient to achieve the HMM ESD test level of 4 kV. To meet the first stage capacitance of 240 fF, the number of fingers for the diode and SDSCR is designed as four and six, respectively. In other words, the total width of the diode and SDSCR is 120  $\mu$ m (30  $\mu$ m × 4 fingers) and 180  $\mu$ m (30  $\mu$ m × 6 fingers), respectively.

# B. Circuits Simulation

Starting with a standard 50- $\Omega$  system, which is commonly found in RF systems, the equivalent RF circuit models of these two different ESD protection circuits are shown in Fig. 6(a) and (b). A signal source with 50- $\Omega$  impedance (Z<sub>I</sub>) drives the input node of the ESD protection circuits, and a 50- $\Omega$  output load (Z<sub>L</sub>) is connected to the output node of ESD protection circuits. Each ESD protection device is modeled as capacitances (C<sub>ESDx</sub>). All the design parameters for simulation are listed in Table I. The capacitance of pad is 100 fF from the foundry's data. Moreover, the layout effect of metal routing is

Fig. 7. Matching procedures of (a) traditional distributed ESD protection circuit and (b) new proposed distributed ESD protection circuit in Smith chart.

extracted by an electromagnetic simulation tool to modify the simulated RF characteristics.

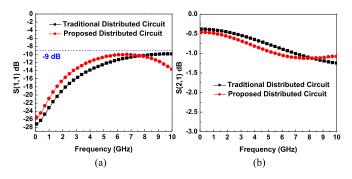

In order to meet the desired specifications of  $S_{11}$  and  $S_{21}$ , the way by using the inductor to compensate the parasitic capacitances has been adopted in this paper. Following the matching step shown in Fig. 7(a), the compensated inductors  $(L_1 \text{ and } L_2)$  in the traditional distributed ESD protection circuit are both selected as 360 pH because the capacitance of the second stage  $(C_{ESD2}+C_{Metal})$  is the same as that of the first stage ( $C_{ESD1}+C_{Metal}$ ). In the proposed circuit, the capacitance value of the first stage is contributed by  $C_{\text{Pad}}$ ,  $C_{\text{ESD1}}$ , and  $C_{\text{Metal}}$ . This capacitance value is fixed in the matching step to meet good ESD specification. By adding the inductors of  $L_1$  and  $L_2$ , the matching procedure is modified as that shown in Fig. 7(b). To meet the center point of 50- $\Omega$  output load in Smith chart, the inductors  $L_1$  and  $L_2$ , which can limit the ESD current and compensate the parasitic capacitances, are selected as 700 and 170 pH, respectively. In addition, the capacitance value of the second stage ( $C_{ESD2}$ ) is selected as 360 fF. Fig. 8 shows the S-parameter simulation results with layout effect in the frequency range of 0.1-10 GHz. The return loss and insertion loss of the traditional circuit and the proposed circuit can both achieve the desired specifications.

## **III. EXPERIMENTAL RESULTS OF ESD TEST CELLS**

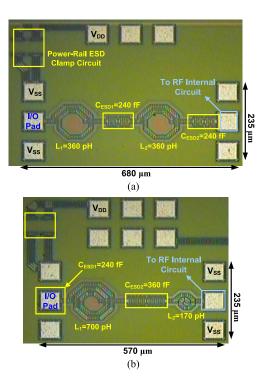

In order to reduce the parasitic capacitance, the top metal (metal7 in the given process) is used for the routing to I/O pad, and the bottom metal is used for the routing to  $V_{\text{DD}}$  and  $V_{\text{SS}}$  pads. Each inductor is composed of two metal layers (top metal and aluminum). To sustain high-ESD current, the width of inductor's metal is selected as 12  $\mu$ m, which is the maximum value of the top metal in this process. The width

Fig. 8. Simulation results with layout effect on the RF performance of (a)  $S_{11}$ -parameters and (b)  $S_{21}$ -parameters for the traditional circuit and the proposed circuit.

Fig. 9. Chip micrographs of (a) traditional circuit and (b) proposed circuit.

of other metal layers (metal1 to metal6) is also limited in advanced process. In addition, a special layout skill of stacking multiple metal layers has been proposed in this paper to follow the foundry's design rule, without degrading the ESD robustness. Each ESD protection device utilizes four layers of metal (metal2 to metal5) for the metal routing to sustain high-ESD current. Fig. 9 shows the chip micrographs of the traditional circuits and the proposed circuits.

## A. RF Performances

With the on-wafer and two-port S-parameter measurements, the RF characteristics of test circuits have been extracted. The voltage supply of  $V_{DD}$  is 2.5 V, and the input dc bias is 1.0 V. The source and load resistances to the fabricated ESD protection circuits are kept at 50  $\Omega$ . Fig. 10(a) and (b) shows the measured  $S_{11}$ - and  $S_{21}$ -parameters versus frequencies among the test circuits. During the operating frequency from 0.1 to 10 GHz, the maximum values of  $S_{11}$  in traditional circuit

Fig. 10. Measurement results of (a)  $S_{11}$ -parameters and (b)  $S_{21}$ -parameters for the traditional and proposed circuits.

with the diodes and the SDSCRs are -9.2 and -9.6 dB, respectively. The maximum values of  $S_{11}$  in the proposed circuit with the diodes and the SDSCRs are -8.8 and -9.2 dB, respectively. The circuit with the traditional diode has a larger insertion loss than the one with the SDSCR, as predicted in the simulation results. In addition, the experimental results have a little difference with the simulation results. The reason is that the front-end parasitic effect is roughly estimated by using the junction and sidewall capacitances from the foundry's data. Moreover, the ESD device under the I/O pad has a large overlap area between back-end metal and front-end device, and it may cause some unpredictable parasitic effect that was not considered in the simulation results.

#### B. ESD Robustness

The HBM test method is typically used to verify the ESD robustness of the fabricated circuits. The ESD pulses are stressed to each test circuit under positive I/O-to- $V_{DD}$  (PD mode), positive I/O-to- $V_{SS}$  (PS mode), negative I/O-to- $V_{DD}$  (ND mode), and negative I/O-to- $V_{SS}$  (NS mode) ESD stress conditions. All the test circuit can sustain more than 8-kV HBM ESD level under each test condition. Furthermore, this paper also shows the HMM test method on the test circuits to investigate the robustness under ESD gun stress. The failure criterion is defined as the I-V characteristics of the circuit shifting more than 30% from its initial curve after ESD gun zapped at each ESD test level. The HBM and HMM test results of the test circuits under four modes of ESD test condition are summarized in Tables II and III. The ESD robustness of the test circuit is judged by the lowest level among the four modes

TABLE II MEASURED RESULTS OF THE TRADITIONAL DISTRIBUTED ESD PROTECTION CIRCUITS

|                                         | Traditional distributed<br>ESD protection circuit<br>with the diodes   |     |      |                                                                        | Traditional distributed<br>ESD protection circuit<br>with the SDSCRs |     |     |     |

|-----------------------------------------|------------------------------------------------------------------------|-----|------|------------------------------------------------------------------------|----------------------------------------------------------------------|-----|-----|-----|

| First stage<br>ESD device<br>size (µm)  | P+/N-Well Diode=120<br>N+/P-Well Diode=120                             |     |      |                                                                        | P-type SDSCR=180<br>N-Type SDSCR=180                                 |     |     |     |

| Second stage<br>ESD device<br>size (µm) | P+/N-Well Diode=120<br>N+/P-Well Diode=120                             |     |      | P-type SDSCR=180<br>N-type SDSCR=180                                   |                                                                      |     |     |     |

| Area (mm <sup>2</sup> )                 | 0.1598                                                                 |     |      | 0.1598                                                                 |                                                                      |     |     |     |

| L (pH)                                  | L <sub>1</sub> =360, L <sub>2</sub> =360                               |     |      | L <sub>1</sub> =360, L <sub>2</sub> =360                               |                                                                      |     |     |     |

| Mode                                    | PD                                                                     | PS  | ND   | NS                                                                     | PD                                                                   | PS  | ND  | NS  |

| V <sub>t1</sub> (V)                     | 0.86                                                                   | 1.0 | 1.04 | 0.86                                                                   | 1.0                                                                  | 1.7 | 1.8 | 1.6 |

| I <sub>t2</sub> (A)                     | 9.3                                                                    | 8.5 | 7.4  | 10                                                                     | 9.4                                                                  | 8.3 | 6.9 | 10  |

| HBM (kV)                                | >8                                                                     | >8  | >8   | >8                                                                     | >8                                                                   | >8  | >8  | >8  |

| HMM (kV)                                | 4.5                                                                    | 4   | 3.5  | 5                                                                      | 4.5                                                                  | 4   | 3.5 | 5   |

| FOM<br>(kV/dB*<br>mm <sup>2</sup> )     | 8.5                                                                    | 7.6 | 6.6  | 9.5                                                                    | 10.8                                                                 | 9.6 | 8.4 | 12  |

| S-parameter<br>(dB)                     | S <sub>11</sub> = -9.2, S <sub>21</sub> = -3.3<br>(from 0.1 to 10 GHz) |     |      | S <sub>11</sub> = -9.6, S <sub>21</sub> = -2.6<br>(from 0.1 to 10 GHz) |                                                                      |     |     |     |

of ESD test condition. Therefore, the HMM ESD robustness of the traditional circuit with diodes, the traditional circuit with SDSCRs, the proposed circuit with diodes, and the proposed circuit with SDSCRs is 3.5, 3.5, 4.5, and 5 kV, respectively.

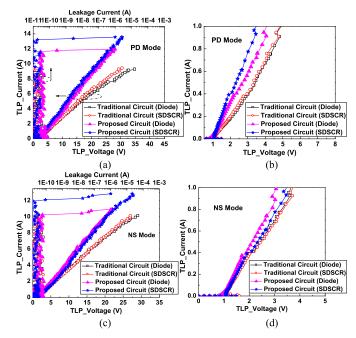

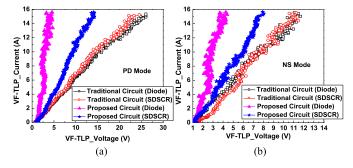

#### C. Transmission-Line-Pulsing I–V Characteristics

A 100-ns transmission-line-pulsing (TLP) system with 10-ns rise time was used to investigate the circuit behavior during an ESD transient pulse [23]. The important parameters of TLP measurement I-V curve include trigger voltage ( $V_{t1}$ ), holding voltage  $(V_h)$ , and second breakdown current  $(I_{t2})$ . In order to analyze the performance of p-type and n-type devices, the comparisons of TLP I-V curves among all test circuits under PD and NS mode ESD test conditions are shown in Fig. 11.  $I_{t2}$  of the proposed circuit with SDSCRs is on the top, and the proposed circuit with diodes is the second. It is due to the small size of the diode under the same value of the parasitic capacitance, as compared with SCR. In Fig. 11, the holding voltage of traditional circuits is higher than that of the proposed circuits. It can be attributed to the inherent resistance of the input inductor. The input inductor also degrades the ESD robustness of traditional circuits. Since the failure point of traditional circuits was located on the input inductor rather than the ESD device, the leakage current has no significant difference after the TLP test. The optical micrographs will be shown in Section III-D. All the measurement results are listed in Tables II and III.

TABLE III MEASURED RESULTS OF THE PROPOSED DISTRIBUTED ESD PROTECTION CIRCUITS

|                                         | Proposed distributed<br>ESD protection circuit<br>with the diodes      |     |      |                                                                        | Proposed distributed<br>ESD protection circuit<br>with the SDSCRs |      |      |      |

|-----------------------------------------|------------------------------------------------------------------------|-----|------|------------------------------------------------------------------------|-------------------------------------------------------------------|------|------|------|

| First stage<br>ESD device<br>size (µm)  | P+/N-Well Diode=120<br>N+/P-Well Diode=120                             |     |      |                                                                        | P-Type SDSCR=180<br>N-Type SDSCR=180                              |      |      |      |

| Second stage<br>ESD device<br>size (µm) | P+/N-Well Diode=180<br>N+/P-Well Diode=180                             |     |      | P-Type SDSCR=270<br>N-Type SDSCR=270                                   |                                                                   |      |      |      |

| Area (mm <sup>2</sup> )                 | 0.13395                                                                |     |      | 0.13395                                                                |                                                                   |      |      |      |

| L (pH)                                  | L <sub>1</sub> =700, L <sub>2</sub> =170                               |     |      | L <sub>1</sub> =700, L <sub>2</sub> =170                               |                                                                   |      |      |      |

| Mode                                    | PD                                                                     | PS  | ND   | NS                                                                     | PD                                                                | PS   | ND   | NS   |

| V <sub>t1</sub> (V)                     | 0.85                                                                   | 1.0 | 1.02 | 0.85                                                                   | 1.0                                                               | 1.8  | 1.8  | 1.6  |

| I <sub>t2</sub> (A)                     | 11.9                                                                   | 9.0 | 9.0  | 10.9                                                                   | 13.5                                                              | 9.6  | 9.7  | 12.8 |

| HBM (kV)                                | >8                                                                     | >8  | >8   | >8                                                                     | >8                                                                | >8   | >8   | >8   |

| HMM (kV)                                | 6                                                                      | 4.5 | 4.5  | 5.5                                                                    | 7                                                                 | 5    | 5    | 6.5  |

| FOM<br>(kV/dB*<br>mm <sup>2</sup> )     | 13.2                                                                   | 9.9 | 9.9  | 12.1                                                                   | 18.7                                                              | 13.3 | 13.3 | 17.3 |

| S-parameter<br>(dB)                     | S <sub>11</sub> = -8.8, S <sub>21</sub> = -3.4<br>(from 0.1 to 10 GHz) |     |      | S <sub>11</sub> = -9.2, S <sub>21</sub> = -2.8<br>(from 0.1 to 10 GHz) |                                                                   |      |      |      |

Fig. 11. TLP measured FV characteristics of (a) PD mode, (b) zoomedin view illustration of PD mode, (c) NS mode, and (d) zoomed-in view illustration of NS mode among the traditional circuits and the proposed circuits.

# D. VF-TLP and Transient Overshoot Measurement

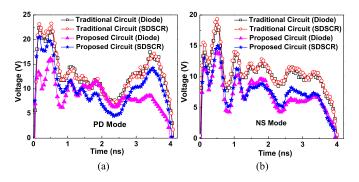

A very fast TLP (VF-TLP) system with pulsewidth of 5 ns and rising time of 200 ps is used to verify the performance of the ESD protection circuits during the charge-device

Fig. 12. VF-TLP measured HV characteristics of (a) PD and (b) NS mode among the traditional circuits and the proposed circuits.

Fig. 13. VF-TLP transient voltage waveform of (a) PD and (b) NS mode among the traditional circuits and the proposed circuits under 5-A condition.

Fig. 14. (a) OM photograph and (b) SEM photograph of traditional circuits after 4.5-kV PS mode HMM stress.

model (CDM) ESD events. Fig. 12 shows the comparison of the VF-TLP I-V curves among all the test circuits under PD and NS mode ESD test conditions. As shown in Fig. 13, the transient voltage waveforms among the traditional circuits and the proposed circuits are measured under the 5-A VF- $I_{t2}$ condition. Based on the measurement results, test circuits can overcome the zapping voltage of 900 V, which is a maximum pulse voltage supplied from the VF-TLP instrument. Moreover, the overshoot of the proposed circuits is lower than that of traditional circuits. The proposed circuit can provide more effective protection for the internal circuits against CDM events.

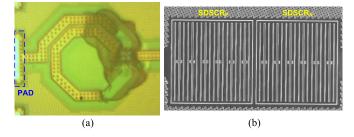

## E. Failure Analysis

Fig. 14(a) shows the optical microscope (OM) photograph of traditional circuits after PS mode HMM ESD test of 4.5 kV. Despite using the maximum width of metal, the failure of traditional circuits is still located at the input inductor. The tra-

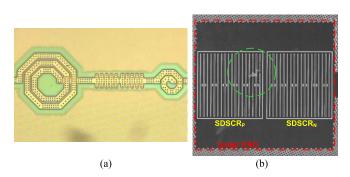

Fig. 15. (a) OM photograph and (b) SEM photograph of the proposed circuits after 5.5-kV PS mode HMM stress

ditional circuits have the same phenomenon under each mode of HMM ESD test. The scanning electron microscope (SEM) experiment was used to further observe the certain failure point. The failure point of the traditional circuits was not found in Fig. 14(b). It means that the ESD level of the traditional circuits is dominated by the metal width of the input inductor. The OM photograph of the proposed circuits after PS mode HMM ESD test of 5.5 kV is shown in Fig. 15(a). The proposed circuit is intact under the microscope. In Fig. 15(b), the failure point of the proposed circuit is located at the p-type SDSCR of the first stage. The ESD robustness of the proposed circuit is significantly dependent on the size of the ESD protection device at the first stage. To conclude, the traditional distributed ESD protection circuit has a risk of metal damage as well as losing the protection ability during the high-current ESD test.

#### F. Comparison

The important factors of ESD protection circuits for highfrequency applications include S-parameter and ESD robustness. The ESD protection circuits are wished to have required insertion loss under the normal circuit operating conditions, and high-ESD robustness during the ESD current discharging conditions. Obviously, the HBM level of each test circuit is all higher than 8 kV. It cannot use to verify the performance of test circuits. Therefore, the figure of merit (FOM) in this paper can be expressed as

$$FOM = \frac{HMM}{|S_{21}| \times A}$$

(1)

where A is the cell area of each test circuit. The FOM of the traditional circuit with diodes, the traditional circuit with SDSCRs, the proposed circuit with diodes, and the proposed circuit with SDSCRs is 6.6, 8.4, 9.9, and 13.3 kV/dB·mm<sup>2</sup>, respectively. For good ESD protection ability and RF performance, it is desirable to have a high FOM. Unfortunately, the traditional circuits suffered a low-HMM level, and the proposed circuit with diodes has a bad RF performance. Consequently, the proposed circuit with SDSCRs can effectively sustain high-HMM level without degrading RF performance. The proposed circuit was implemented with a cell area of  $570 \times 235 \ \mu m^2$  to save the chip area about 15%, as compared with the traditional circuit. Moreover, the inductor  $L_2$  can be integrated into the internal matching network by using the codesign approach.

#### **IV. CONCLUSION**

For the limitation of back-end metal width in the advanced process, the traditional distributed ESD protection circuit has been demonstrated that it has a risk of metal damage as well as degrading the protection capability. A new distributed ESD protection circuit with the SDSCR for broadband RF applications is proposed in this paper. The ESD protection devices of the proposed circuit are put under the I/O pad to reduce layout area and can discharge the ESD current immediately. As compared with the traditional distributed ESD protection circuit, the experimental results in a 40-nm, 2.5-V CMOS process have successfully verified that the proposed distributed ESD protection circuit with the SDSCRs can effectively sustain the HMM stress of 5 kV without influencing the RF performance. By using the SDSCR, the return loss and insertion loss of the proposed circuit in the frequency range of 0.1-10 GHz are -9.2 and -2.8 dB, respectively. The layout area can efficiently reduce more than 15%. Therefore, the proposed circuit with the SDSCRs provides a good solution for broadband RF applications to sustain a high-ESD robustness.

#### ACKNOWLEDGMENT

The authors would like to thank P.-C. Lin and T.-C. Tzeng of Novatek Corporation for their valuable technical suggestions and the support of chip fabrication. They would also like to thank C.-Y. Chen and G.-L. Lin of Vanguard International Semiconductor Corporation for the support of VF-TLP measurement.

#### REFERENCES

- D. Fritsche, G. Tretter, C. Carta, and F. Ellinger, "Millimeter-wave lownoise amplifier design in 28-nm low-power digital CMOS," *IEEE Trans. Microw. Theory Techn.*, vol. 63, no. 6, pp. 1910–1922, Jun. 2015, doi: 10.1109/TMTT.2015.2427794.

- [2] C. Duvvury, "ESD qualification changes for 45nm and beyond," in *IEDM Tech. Dig.*, Dec. 2008, pp. 1–4, doi: 10.1109/IEDM.2008. 4796688.

- [3] H. Gossner, "Design for ESD protection at its limits," in *Proc. Symp. VLSI Technol.*, Jun. 2013, pp. T120–T121.

- [4] Standard Test Method for Electrostatic Discharge (ESD) Sensitivity Testing: Human Body Model (HBM)-Component Level, Standard ANSI/ESDA/JEDEC JS-001-2017, 2017.

- [5] Recommended ESD Target Levels for HBM/MM Qualification, JEDEC Solid State Technol. Assoc., Standard JEDEC JEP155A.01, 2012.

- [6] M.-D. Ker, C.-Y. Lin, and Y.-W. Hsiao, "Overview on ESD protection designs of low-parasitic capacitance for RF ICs in CMOS technologies," *IEEE Trans. Device Mater. Rel.*, vol. 11, no. 2, pp. 207–218, Jun. 2011, doi: 10.1109/TDMR.2011.2106129.

- [7] C.-Y. Lin and M.-D. Ker, "Low-capacitance SCR with waffle layout structure for on-chip ESD protection in RF ICs," in *Proc. IEEE Radio Freq. Integr. Circuit Symp.*, Jun. 2007, pp. 749–752, doi: 10.1109/RFIC.2007.380991.

- [8] M.-D. Ker and Y.-W. Hsiao, "On-chip ESD protection strategies for RF circuits in CMOS technology," in *Proc. 8th Int. Conf. Solid-State Integr. Circuit Technol.*, Oct. 2006, pp. 1680–1683, doi: 10.1109/ICSICT.2006.306371.

- [9] C. Ito, K. Banerjee, and R. W. Dutton, "Analysis and design of distributed ESD protection circuits for high-speed mixed-signal and RF ICs," *IEEE Trans. Electron Devices*, vol. 49, no. 8, pp. 1444–1454, Aug. 2002, doi: 10.1109/TED.2002.801257.

- [10] M.-D. Ker and B.-J. Kuo, "Decreasing-size distributed ESD protection scheme for broad-band RF circuits," *IEEE Trans. Microw. Theory Techn.*, vol. 53, no. 2, pp. 582–589, Feb. 2005, doi: 10.1109/RFIC.2004.1320629.

- [11] C.-Y. Lin, L.-W. Chu, M.-D. Ker, T.-H. Lu, P.-F. Hung, and H.-C. Li, "Self-matched ESD cell in CMOS technology for 60-GHz broadband RF applications," in *Proc. IEEE Radio Freq. Integr. Circuit Symp.*, May 2010, pp. 573–576, doi: 10.1109/RFIC.2010.5477291.

- [12] K. Bhatia, N. Jack, and E. Rosenbaum, "Layout optimization of ESD protection diodes for high-frequency I/Os," *IEEE Trans. Device Mater. Rel.*, vol. 9, no. 3, pp. 465–475, Sep. 2009, doi: 10.1109/TDMR.2009.2025956.

- [13] C.-T. Yeh, M.-D. Ker, and Y.-C. Liang, "Optimization on layout style of ESD protection diode for radio-frequency front-end and high-speed I/O interface circuits," *IEEE Trans. Device Mater. Rel.*, vol. 10, no. 2, pp. 238–246, Jun. 2010, doi: 10.1109/TDMR.2010.2043433.

- [14] ESD Association Standard Practice for Electrostatic Discharge Sensitivity Testing-Human Metal Model (HMM)–Component Level, Standard ANSI/ESD SP5.6-2009, 2009.

- [15] IEC 61000-4-2, 2008, "EMC—Part 4-2: Testing and measurement techniques–electrostatic discharge immunity test," International Standard.

- [16] M. H. Song, T. Smedes, J. C. Tseng, T. H. Chang, R. Derikx, and R. Velghe, "A contribution to the evaluation of HMM for IO design," in *Proc. EOS/ESD Symp.*, Sep. 2011, pp. 1–7.

- [17] D. Linten et al., "A 4.5 kV HBM, 300 V CDM, 1.2 kV HMM ESD protected DC-to-16.1 GHz wideband LNA in 90 nm CMOS," in Proc. 31st EOS/ESD Symp., Aug./Sep. 2009, pp. 1–6.

- [18] K. Muhonen, N. Peachey, and A. Testin, "Human metal model (HMM) testing, challenges to using ESD guns," in *Proc. 31st EOS/ESD Symp.*, Aug./Sep. 2009, pp. 1–9.

- [19] C.-Y. Lin, M.-L. Fan, M.-D. Ker, L.-W. Chu, J.-C. Tseng, and M.-H. Song, "Improving ESD robustness of stacked diodes with embedded SCR for RF applications in 65-nm CMOS," in *Proc. Int. Rel. Phys. Symp.*, Jun. 2014, pp. EL.1.1–EL.1.4, doi: 10.1109/IRPS.2014.6861132.

- [20] J.-T. Chen, C.-Y. Lin, R.-K. Chang, M.-D. Ker, T.-C. Tzeng, and T.-C. Lin, "ESD protection design for high-speed applications in CMOS technology," in *Proc. IEEE 59th Int. Midwest Symp. Circuits Syst.*, Oct. 2016, pp. 1–4, doi: 10.1109/MWSCAS.2016.7870016.

- [21] A. Dong *et al.*, "ESD protection structure with reduced capacitance and overshoot voltage for high speed interface applications," *Microelectron. Rel.*, vol. 79, pp. 201–205, Dec. 2017, doi: 10.1016/j.microrel.2017.03.014.

- [22] J.-T. Chen, C.-Y. Lin, and M.-D. Ker, "On-chip ESD protection device for high-speed I/O applications in CMOS technology," *IEEE Trans. Electron Devices*, vol. 64, no. 10, pp. 3979–3985, Oct. 2017, doi: 10.1109/TED.2017.2734059.

- [23] J. E. Barth, K. Verhaege, L. G. Henry, and J. Richner, "TLP calibration, correlation, standards, and new techniques," *IEEE Trans. Electron. Packag. Manuf.*, vol. 24, no. 2, pp. 99–108, Apr. 2001, doi: 10.1109/6104.930960.

**Jie-Ting Chen** received the M.S. degree from National Chiao Tung University, Hsinchu, Taiwan, in 2013, where he is currently pursuing the Ph.D. degree with the Institute of Electronics.

His current research interests include high-speed electrostatic discharge (ESD) protection designs and power-rail ESD clamp circuit designs in CMOS technologies.

**Chun-Yu Lin** (SM'17) received the Ph.D. degree from the Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan, in 2009.

He is currently an Associate Professor with the Department of Electrical Engineering, National Taiwan Normal University, Taipei, Taiwan, and the Secretary-General of Taiwan Electrostatic Discharge (ESD) Association, Hsinchu, Taiwan. His current research interests include ESD protection designs.

**Rong-Kun Chang** received the M.S. degree from National Taiwan Normal University, Taipei, Taiwan, in 2015. He is currently pursuing the Ph.D. degree with the Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan.

His current research interests include electrostatic discharge (ESD) protection designs for RF circuits and power-rail ESD clamp in CMOS technologies.

**Ming-Dou Ker** (F'08) received the Ph.D. degree from the Institute of Electronics, National Chiao Tung University (NCTU), Hsinchu, Taiwan, in 1993.

He is currently a Distinguished Professor with the Institute of Electronics, NCTU, and the Director of Biomedical Electronics Translational Research Center, NCTU, Hsinchu, Taiwan.

Dr. Ker is currently serving as an Editor for the IEEE TRANSACTIONS ON DEVICE AND MATERIALS RELIABILITY, and an Associate Editor for the IEEE

TRANSACTIONS ON BIOMEDICAL CIRCUITS AND SYSTEMS.