# Optimization Design on Active Guard Ring to Improve Latch-Up Immunity of CMOS Integrated Circuits

Chun-Cheng Chen and Ming-Dou Ker<sup>10</sup>, Fellow, IEEE

Abstract—A new optimization design of an active guard ring has been proposed to improve latch-up immunity of CMOS integrated circuits and been successfully verified in a 0.18-µm 1.8-/3.3-V CMOS technology. Codesigned with the on-chip electrostatic discharge (ESD) protection devices (gate-ground nMOS and gate-VDD pMOS) equipped at the input-output (I/O) pad, the overshooting/undershooting trigger current during latch-up test can be conducted away through the turned-on channels of the ESD protection MOSFET's to the power rails ( $V_{DD}$  or  $V_{SS}$ ). Therefore, the trigger current injecting from the I/O devices (that directly connected to the I/O pad) through the substrate to initiate the latch-up occurrence at the internal circuit blocks can be significantly reduced. Thus, the latch-up immunity of the whole chip can be effectively improved under the same placement distance between the I/O cells and the internal circuit blocks. The new proposed design is a cost-efficient solution to improve latch-up immunity and also to mention good ESD robustness of the I/O cells.

*Index Terms*—Active guard ring, electrostatic discharge (ESD) protection, guard ring, latch-up, silicon-controlled rectifier (SCR).

# I. INTRODUCTION

**I** N CMOS integrated circuits, latch-up is formed by the parasitic silicon-controlled rectifier (SCR) structure which crosses between  $V_{DD}$  and  $V_{SS}$ . When the parasitic SCR path is triggered on by the external overshooting/undershooting noises at input–output (I/O) pads, a low-impedance path will be generated to conduct a huge current from  $V_{DD}$  to  $V_{SS}$  [1]–[3]. The huge current of the latch-up path often causes unrecoverable failures in the CMOS chips. Due to the inherent parasitic SCR paths existing in the CMOS technology, the latch-up issue has been one of the main reliability concerns in CMOS IC products.

Manuscript received October 18, 2018; revised February 3, 2019; accepted February 6, 2019. Date of publication February 20, 2019; date of current version March 22, 2019. This work was supported in part by the "Center for Neuromodulation Medical Electronics Systems" from The Featured Areas Research Center Program within the framework of the Higher Education Sprout Project by the Ministry of Education in Taiwan and in part by the Ministry of Science and Technology, Taiwan, under Contract MOST 108-2622-8-009-001-TE1. The review of this paper was arranged by Editor E. Rosenbaum. (Corresponding author: Ming-Dou Ker.)

The authors are with the Institute of Electronics, National Chiao Tung University, Hsinchu 30010, Taiwan (e-mail: mdker@ieee.org).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2019.2898317

TABLE I

TRIGGER CHARACTERIZATION IN LATCH-UP CURRENT TEST [4]

| Immunity<br>Level | Test                                   | Magnitude of Trigger<br>Force Current |  |

|-------------------|----------------------------------------|---------------------------------------|--|

| А                 | <b>Positive I-Test</b>                 | ≥ 100 mA                              |  |

|                   | Negative I-Test                        | ≥ 100 mA                              |  |

| В                 | If immunity level A cannot be achieved |                                       |  |

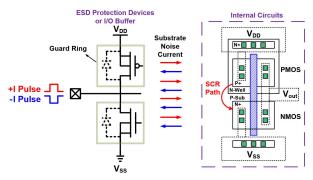

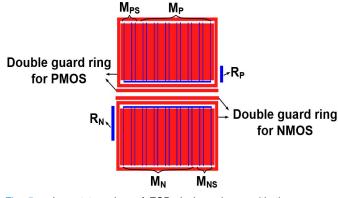

Fig. 1. Traditional latch-up prevention in CMOS IC with guard rings to surround the ESD protection devices and I/O buffer.

Joint Electron Device Engineering Council (JEDEC) has defined the method with test procedures to investigate the latch-up immunity with positive and negative trigger current tests (I-tests) for CMOS ICs. The trigger characterization for latch-up I-test in the up-to-dated standard (JESD78E) is listed in Table I [4]. To avoid damages or reliability issues from the latch-up phenomenon in real field applications, IC companies may have even much higher specification on latch-up immunity level for their CMOS IC products. Therefore, the costefficient solution to further improve the latch-up immunity is strongly requested in IC industry.

It is difficult to eliminate the external noises at I/O pads according to the complex operating environments in the extensive applications of CMOS ICs. To improve the latch-up immunity of CMOS ICs, some process methods [5]–[10] and layout skills [11]–[15] had been reported. Without additional special process modification, the guard rings in layout placement are universally applied for latch-up prevention, but those occupy extra silicon area. The illustration of traditional latch-up prevention in CMOS IC with guard rings to surround the electrostatic discharge (ESD) protection devices or I/O buffer is shown in Fig. 1. Under latch-up trigger current

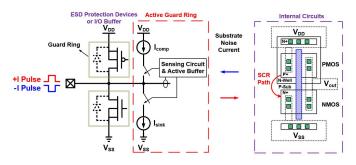

Fig. 2. Concept of active guard ring to reduce substrate noise current at the SCR path of internal circuits under latch-up I-tests.

test, the positive/negative current pulse is injected to I/O pads, which may be conducted to  $V_{DD}/V_{SS}$  through the body diode of ESD protection devices or I/O buffer in the forward-biased conditions. In reality, the applied trigger current is not totally absorbed by the body diode of ESD protection devices or I/O buffer. On the contrary, a certain part of trigger current applied at the I/O pad may flow into p-substrate to enable the parasitic SCR path existing in the logic gates of internal circuits without guard rings surrounding them. As a result, to avoid the latch-up concern in the internal circuit blocks due to the latch-up trigger current applied at the I/O pad, the spacing between I/O cells and internal circuit blocks must be extended [15].

A novel design concept named as an active guard ring to improve the latch-up immunity of ICs was reported in [16]. Using additional sensing circuit and active buffer to turn on the ESD protection devices, the large-dimensional ESD devices or I/O buffer can provide or receive extra compensation current to the negative or positive current perturbation through the inversion layer of MOSFET during the latch-up current test, as shown in Fig. 2. Therefore, the latch-up risk of internal circuits decreased significantly because the injected current almost flowed through the channels of I/O devices to the power rails instead of leaking into the substrate. However, the extra layout area of sensing circuit and active buffer can be resulted in an additional layout area. On the other hand, the leakage current caused by the diode string providing the voltage reference for the gate bias in the sensing circuit and active buffer should be further reduced.

In this paper, an optimization design of active guard ring to improve latch-up immunity of CMOS integrated circuits was proposed and verified in 0.18- $\mu$ m 1.8-/3.3-V CMOS technology. In comparison with the prior active guard ring [16], the new proposed design can successfully integrate the I/O devices and the circuit of active guard rings within a limited I/O cell layout area. In addition, the standby leakage current issue in the prior art is also completely solved. Finally, the detailed examinations to verify the latch-up immunity have been measured by a commercial latch-up test machine.

# II. OPTIMIZATION DESIGN OF ACTIVE GUARD RING

# A. Circuit Implementation

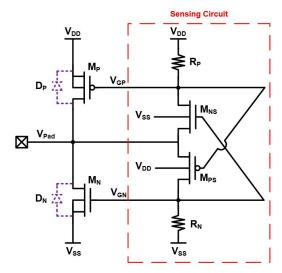

Fig. 3 shows the circuit structure of the proposed active guard ring composed of a sensing circuit block and a pair

Fig. 3. Circuit structure of the proposed active guard ring with simplification and optimization design.

of large-dimensional ESD protection transistors. The sensing circuit is composed of two sensing devices ( $M_{PS}$  and  $M_{NS}$ ) and two resistors ( $R_P$  and  $R_N$ ).

Under normal circuit operation, the gate voltage of pMOS ( $V_{\text{GP}}$ ) is pulled to  $V_{\text{DD}}$ , and the gate voltage of nMOS ( $V_{\text{GN}}$ ) is pulled to  $V_{\text{SS}}$  through  $R_{\text{N}}$ . Thus, all devices are kept in OFF-state to prevent the signal loss without excessive leakage current. Under latch-up I-test with the positive or negative trigger currents applied to the I/O pad, the detail circuit operations are shown in Fig. 4(a) and (b), respectively.

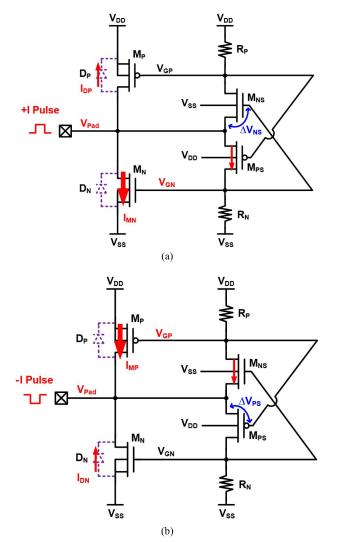

In Fig. 4(a), once a large enough positive current pulse is injected to I/O pad under positive I-test,  $V_{Pad}$  will be raised up with a certain high voltage above  $V_{DD}$ . For the traditional latch-up prevention with guard ring, the trigger current mostly flows into the body diode ( $D_P$ ) of  $M_P$ . With the drain-tobulk current ( $I_{DP}$ ) of  $M_P$  increasing, more and more substrate noise current will induce latch-up in internal circuits as well. However, in this new proposed design,  $M_{PS}$  will be turned on if  $V_{Pad}$  is larger than  $V_{GP}$  which is normally biased at  $V_{DD}$ under power-ON situation. As a result, the gate voltage ( $V_{GN}$ ) of  $M_N$  is pulled up by the channel current of  $M_{PS}$ , and the inversion layer of  $M_N$  is generated to conduct the trigger current from the pad to  $V_{SS}$ . In this way, the latch-up risk is improved with less current injecting into the substrate.

The circuit operation during negative I-test is shown in Fig. 4(b). In contrast to positive I-test, while a large enough negative current pulse is applied to I/O pad,  $V_{Pad}$  will be pulled down with a low voltage level below  $V_{SS}$ . Therefore, for the latch-up prevention with traditional guard ring, the trigger current is mostly absorbed by the body diode  $(D_N)$  of  $M_N$  to enhance the latch-up risk of internal circuits. However, in this new proposed design,  $M_{NS}$  will be turned on once  $V_{Pad}$  is lower than  $V_{GN}$  which is normally biased at  $V_{SS}$  under power-ON situation. In addition, the gate voltage  $(V_{GP})$  of  $M_P$  is pulled down to trigger  $M_P$  by the channel current of  $M_{NS}$ , and the inversion layer of  $M_P$  is generated to conduct some current from  $V_{DD}$  to the I/O pad that compensates the negative trigger current applied at the I/O pad. By this way, the drain-to-bulk current  $(I_{DN})$  of  $M_N$  is restrained to suppress the latch-up

Fig. 4. Circuit operations of the proposed active guard ring during latch-up I-test with (a) positive and (b) negative, trigger current.

event in internal circuits because the current injecting into the substrate through the drain-to-bulk diode of  $M_N$  is significantly reduced.

On the other hand, if the gate of  $M_{\rm NS}$  is connected to  $V_{\rm ss}$  directly, the voltage difference ( $\Delta V_{\rm NS}$ ) between  $V_{\rm Pad}$  and the gate voltage of  $M_{\rm NS}$  may be over 1.1-times  $V_{\rm DD}$  which may cause reliability concern under positive I-test. As a result, the gate of  $M_{\rm NS}$  has to be connected to the gate of  $M_{\rm N}$  to avoid the overvoltage stress issue. During negative I-test, the similar reliability issue will show up if the gate of  $M_{\rm PS}$  is directly connected to  $V_{\rm DD}$ , so the gate of  $M_{\rm PS}$  must be connected to the gate of the gate of  $M_{\rm PS}$  to avoid the overvoltage stress.

#### B. Simulation

All simulated results are investigated by HSPICE simulation in a 0.18- $\mu$ m 1.8-/3.3-V CMOS process with the device parameters provided by foundry, including the drain-to-bulk diodes in the ESD devices ( $M_P$  and  $M_N$ ). For latch-up I-test, the timing specification of the trigger pulse has been defined in the JEDEC standard [4]. The positive or negative trigger current pulse with a 10- $\mu$ s pulsewidth and a 200 mA of peak current is applied to I/O pad, and the  $V_{DD}$  is biased at 3.3 V.

#### TABLE II

SIMULATED RESULTS FOR THE ESD DEVICES WITH THE PROPOSED DESIGN UNDER POSITIVE I-TEST WITH A 200 mA OF CURRENT PULSE

| Device          | Temperature |         |         |

|-----------------|-------------|---------|---------|

|                 | 25°C        | 75°C    | 125°C   |

| I <sub>MP</sub> | 1.07mA      | 1.19mA  | 1.26mA  |

| I <sub>MN</sub> | 195.3mA     | 195.5mA | 187.1mA |

| I <sub>DP</sub> | 0.02mA      | 0.64mA  | 9.06mA  |

| I <sub>DN</sub> | 3.32mA      | 2.32mA  | 1.62mA  |

| $\Delta V_{NS}$ | 1.29V       | 1.14V   | 0.94V   |

#### TABLE III

Simulated Results for the ESD devices With the Proposed Design Under Negative I-Test With a -100 mA of Current Pulse

| ESD Devices with the Proposed Design<br>under Negative I-Test with a -100-mA Current Pulse |             |         |         |

|--------------------------------------------------------------------------------------------|-------------|---------|---------|

| Device                                                                                     | Temperature |         |         |

|                                                                                            | 25°C        | 75°C    | 125°C   |

| I <sub>MP</sub>                                                                            | 99.42mA     | 98.54mA | 91.14mA |

| I <sub>MN</sub>                                                                            | 0.27mA      | 0.30mA  | 0.31mA  |

| I <sub>DP</sub>                                                                            | 0.17mA      | 0.13mA  | 0.09mA  |

| I <sub>DN</sub>                                                                            | 0.05mA      | 0.91mA  | 7.89mA  |

| $\Delta V_{PS}$                                                                            | 1.93V       | 1.86V   | 1.86V   |

For the ESD devices with the optimized design of active guard ring circuit, the simulated results under positive I-test with a 200 mA of current pulse are listed in Table II. When the positive energy is performed on pad,  $M_{PS}$  will be turned on to pull up the gate of  $M_N$ . The inversion layer of  $M_N$  is generated to provide a low-impedance path and leads the current to  $V_{SS}$ . As shown in Table II, the drain-to-source current ( $I_{MN}$ ) of  $M_N$  dominated above 90% trigger current even at 125 °C, and the substrate current is predicted to be decreased effectively.

Table III illustrates the simulated results under negative I-test with a current pulse of -100 mA. The proposed optimization design of active guard ring circuit normally works under negative I-test with a lower peak current. However, the function of the proposed design was degraded under negative I-test with a -200-mA current pulse at high temperature, as illustrated in Table IV. The drain-to-source current  $(I_{MP})$ of  $M_{\rm P}$  dominates about 80% trigger current at 25 °C but only 15% trigger current at 125 °C. Because the turn-on voltage of diode decreases significantly at high temperature, more trigger current is led to the body (drain-to-bulk) diode. In addition,  $M_{\rm P}$  is unable to afford such a high current of 200 mA due to the lower mobility of pMOS with limited device size. As a result, more trigger current at the I/O pad may be injected into the substrate to induce latch-up occurrence at the neighborhood internal circuit blocks at high temperature. To further verify this phenomenon, the simulated results for the ESD devices with the proposed design with an enlarged dimension of  $M_{\rm P}$  under negative I-test of -200-mA current pulse are listed in Table V. At a high temperature of 125 °C,

#### TABLE IV

Simulated Results for the ESD Devices With the Proposed Design Under Negative I-Test With a  $-200\ \mathrm{mA}$  of Current Pulse

| Device          | Temperature |         |         |

|-----------------|-------------|---------|---------|

|                 | 25°C        | 75°C    | 125°C   |

| I <sub>MP</sub> | 159.5mA     | 91.06mA | 28.71mA |

| I <sub>MN</sub> | 4.51mA      | 2.96mA  | 1.58mA  |

| I <sub>DP</sub> | 0.02mA      | 0.06mA  | 0.07mA  |

| I <sub>DN</sub> | 32.96mA     | 98.63mA | 158.3mA |

| $\Delta V_{PS}$ | 0.45V       | 1.35V   | 2.35V   |

#### TABLE V

Simulated Results for the ESD Devices With the Proposed Design and an Enlarged  $M_{\rm P}$  Under Negative I-Test With a  $-200~{\rm mA}$  Current Pulse

| Device          | Temperature |         |         |

|-----------------|-------------|---------|---------|

|                 | 25°C        | 75⁰C    | 125°C   |

| I <sub>MP</sub> | 199.2mA     | 197.2mA | 181.6mA |

| I <sub>MN</sub> | 0.44mA      | 0.48mA  | 0.48mA  |

| I <sub>DP</sub> | 0.01mA      | 0.06mA  | 0.04mA  |

| I <sub>DN</sub> | 0.12mA      | 2.04mA  | 16.78mA |

| $\Delta V_{PS}$ | 1.14V       | 1.05V   | 1.07V   |

TABLE VI DEVICE DIMENSIONS AND RESISTANCE USED IN THE TESTKEYS

| Device          | ESD Devices<br>with<br>Traditional<br>Guard Ring | ESD Devices<br>with the<br>Proposed Design | ESD Devices<br>with the<br>Proposed Design<br>and enlarged M <sub>P</sub> |

|-----------------|--------------------------------------------------|--------------------------------------------|---------------------------------------------------------------------------|

| M <sub>P</sub>  | (35 μm*16)/<br>0.30 μm                           | (35 μm*13)/<br>0.30 μm                     | (35 μm*25)/<br>0.30 μm                                                    |

| M <sub>N</sub>  | (35 μm*16)/<br>0.35 μm                           | (35 μm*13)/<br>0.35 μm                     | (35 μm*13)/<br>0.35 μm                                                    |

| M <sub>PS</sub> | N/A                                              | (35 μm*3)/<br>0.30 μm                      | (35 μm*3)/<br>0.30 μm                                                     |

| M <sub>NS</sub> | N/A                                              | (35 μm*3)/<br>0.35 μm                      | (35 μm*3)/<br>0.35 μm                                                     |

| R <sub>P</sub>  | 3.8 kohm                                         | 3.8 kohm                                   | 25 kohm                                                                   |

| R <sub>N</sub>  | 10 kohm                                          | 10 kohm                                    | 10 kohm                                                                   |

$M_{\rm NS}$  will be turned on to pull low the gate of  $M_{\rm P}$ . The inversion layer of  $M_{\rm P}$  is generated to provide a low-impedance path and leads the current to  $V_{\rm DD}$ . As shown in Table V, the negative trigger current mainly flows into the inversion layer of MOS to prevent excessive substrate current from causing latch-up event in the internal circuits. The detailed device dimensions used in all simulations are listed in Table VI.

According to HSPICE simulation results shown in Tables II–V, the voltage difference  $(\Delta V_{\rm NS})$  between  $V_{\rm Pad}$  and the gate voltage  $(V_{\rm GN})$  of  $M_{\rm NS}$  is not above 1.1-times  $V_{\rm DD}$  (3.63 V) and so is the voltage difference  $(\Delta V_{\rm PS})$  between  $V_{\rm Pad}$  and the gate voltage  $(V_{\rm GP})$  of  $M_{\rm PS}$ . Therefore, there is no overvoltage stress issue in this optimization design of the

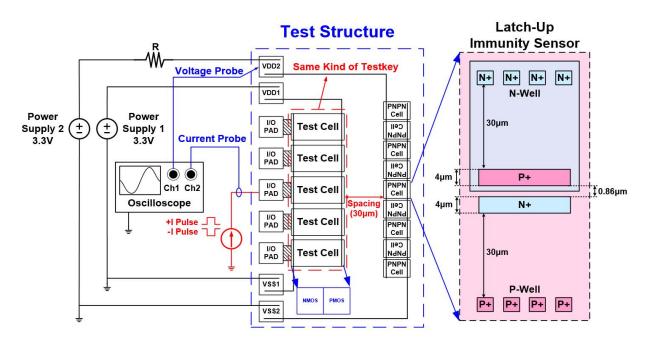

Fig. 5. Layout top view of ESD devices drawn with the proposed optimization design of active guard ring.

Fig. 6. Layout top view of ESD devices drawn with the traditional guard ring.

active guard ring to improve latch-up immunity of CMOS integrated circuits.

To test whether the normal operating I/O signals may mistrigger the proposed design, a signal pulse with a 0.1-ns rising time, a 0.1-ns falling time, a 20-ns pulsewidth, and a 1.1-times pulse voltage of overshoot/undershoot voltage is applied to I/O pad to monitor the gate voltage of each device. All devices in each testkey always are kept in OFF-state, when the overshoot/undershoot signal pulse is applied to I/O pad.

In further optimized layout area of the proposed design, both pMOS devices ( $M_P$  and  $M_{PS}$ ) are placed together and surrounded by guard ring and so are the two nMOS devices ( $M_N$  and  $M_{NS}$ ). The layout top view of the proposed design of the active guard ring is shown in Fig. 5. To compare with the proposed design, the ESD devices composed of a gate-ground nMOS (GGNMOS,  $M_N$ ) and a gate- $V_{DD}$  pMOS (GDPMOS,  $M_P$ ) with traditional guard ring is also studied in this paper, and the corresponding layout top view of the traditional design with guard ring, the total width of GGNMOS is designed to be the same as the total width of all nMOS in the proposed design. Similarly, the total width of all pMOS is designed to be the same as the total width of all pMOS in the proposed design.

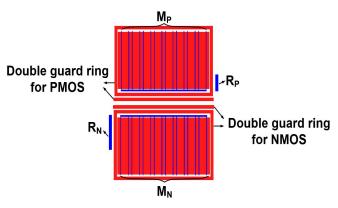

## C. Latch-Up Test Structure

Fig. 7 shows the test structure with the external setup of latch-up I-test measurement. The latch-up sensitivity of the

Fig. 7. Latch-up test structure to examine the latch-up immunity of testkey.

internal p-n-p-n cells (latch-up immunity sensor) toward the external trigger source is affected by the testkeys arranged in the test cells, as well as the distance between the test cells and the p-n-p-n cells. The latch-up immunity sensor is composed of a p-n-p-n structure which is drawn with the minimum design rule of 0.86  $\mu$ m from p+ to n+ diffusions in the given  $0.18 - \mu m \ 1.8 - /3.3 - V \ CMOS$  process, as that indicated in Fig. 7. The test cells are drawn and placed in parallel to p-n-p-n cells with a 30- $\mu$ m spacing between test cells and the p-n-p-n cells (latch-up immunity sensor). Since the holding voltage of the latch-up immunity sensor drawn with a minimum design rule of 0.86  $\mu$ m from p+ to n+ diffusions is typically lower than 1 V, a large current will be conducted if the latch-up event happens on the p-n-p-n cells (latch-up immunity sensor) under 3.3-V power supply. As a result, the occurrence of latch-up event can be detected by monitoring the current or voltage waveforms at  $V_{DD2}$ . To avoid the burn-out issue on the p-n-p-n cells (latch-up immunity sensor) when the latch-up path is activated, a small resistor (R) of 100  $\Omega$ is added between the pad of  $V_{DD2}$  and the external power supply (3.3 V), as shown in Fig. 7. To investigate the latch-up immunity, the test methods as described in [15] and [17] are used.

# **III. EXPERIMENTAL RESULTS**

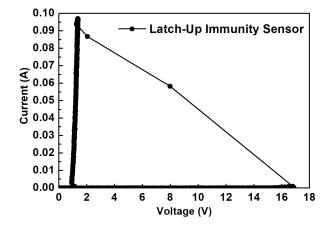

# A. Latch-Up Trigger Current Test

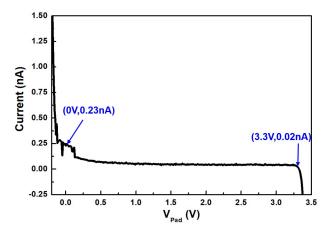

The latch-up test structures with different testkeys have been fabricated by 0.18- $\mu$ m 1.8-/3.3-V CMOS technology. The dc *I*-*V* curve of p-n-p-n cell measured by the curve tracer Tek370B is shown in Fig. 8, where the holding voltage is ~0.92 V. The latch-up I-test is specified in the JEDEC standard (JESD78E) to verify the latch-up immunity. The measurement setup applied to the test structure has been shown in Fig. 7 with two 3.3-V power supplies biased to V<sub>DD1</sub>

Fig. 8. Measured dc -V curve of the latch-up immunity sensor with a holding voltage of 0.92 V.

and  $V_{DD2}$  pads, respectively, and  $V_{SS1}$  and  $V_{SS2}$  pads being grounded. A current pulse generator applied to the I/O pin, and an oscilloscope is used to monitor the waveforms of the  $V_{DD2}$ voltage and the injected current pulse. In addition, the  $V_{DD2}$ pin is connected in series with a 100- $\Omega$  resistor to the 3.3-V voltage source to limit the huge current generated during the latch-up event. The trigger current pulse with a 10-ms pulsewidth is injected into I/O pad to investigate the latch-up occurrence in latch-up immunity sensor under latch-up I-test.

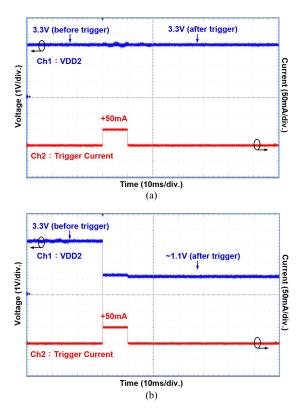

Fig. 9(a) and (b) shows the measured results of the ESD devices (the test cells in Fig. 7) with the proposed optimization design of active guard ring and the traditional guard ring, respectively, under positive I-test with a 50-mA trigger current and a 10-ms pulsewidth applied to the I/O pad. In Fig. 9(a), the trigger current did not generate enough substrate current to induce latch-up in p-n-p-n cells, and therefore, the voltage level at the  $V_{DD2}$  pad is still kept at 3.3 V after the latch-up trigger current applied to the I/O pad. However, since the

Fig. 9. Measured waveforms of the ESD devices with (a) proposed optimization design of active guard ring and (b) traditional guard ring, under positive I-test with a 50-mA trigger current and a 10-ms pulsewidth applied to the I/O pad.

I/O test cell with traditional guard ring cannot efficiently reduce the injecting substrate current under such a latch-up I-test verification, the voltage level at the  $V_{DD2}$  pad is pulled down to 1.1 V, as that shown in Fig. 9(b), where the latch-up occurrence happened in the internal p-n-p-n cells (latch-up immunity sensor).

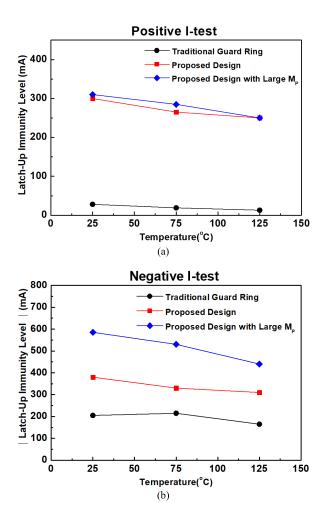

More detailed examinations to investigate the latch-up immunity are measured by the latch-up tester (Thermo Scientific MK.1) with 10-ms pulsewidth and 5-mA current step. The latch-up positive and negative I-test results for the testkeys with the traditional guard ring, the proposed design (optimization design of active guard ring), and the proposed design with a large-dimensional  $M_{\rm P}$  are shown in Fig. 10(a) and (b), respectively, under different temperatures. According to these figures, the optimized design of active guard ring shows a higher latch-up immunity level than that with the traditional guard ring, under both positive and negative I-test. Moreover, the negative latch-up immunity of the proposed design somewhat degrades at high temperature because p-n-p-n cells are far away from  $M_{\rm N}$ , where the negative current mainly injects into p-substrate. Even if more trigger current is injected into p-substrate, the guard rings placed between  $M_N$  and latch-up immunity sensors will absorb this substrate current. In addition, the proposed design with large-dimension  $M_{\rm P}$ really improves the latch-up immunity level under negative I-test.

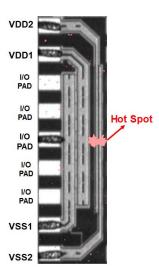

After the current pulse is applied to the I/O pad to investigate the latch-up immunity level, Emission Microscope (EMMI) analysis is taken to show the location of the

Fig. 10. Latch-up immunity levels of the testkeys at different temperatures under (a) positive and (b) negative I-test.

Fig. 11. EMMI photograph of the latch-up test result for the I/O pad of test cell with traditional guard ring under 30-mA positive current pulse.

abnormal current. Fig. 11 shows the EMMI photograph of the latch-up test result for the test cell with a traditional guard ring under 30-mA positive current pulse. The location of hot spot is at the nearest p-n-p-n cell from the I/O pad of the test cell where the trigger current is applied to.

Fig. 12. Measured waveforms of standby current on the I/O pad of test cell with the proposed optimization design of active guard ring under dc sweep of  $V_{Pad}$  from -0.5 to 3.5 V.

Fig. 13. Standby leakage current on the I/O pad of test cell (ESD devices) with the proposed optimization design of active guard ring or the traditional guard ring when  $V_{Pad}$  biased at 0 –3.3 V, respectively, under different temperatures.

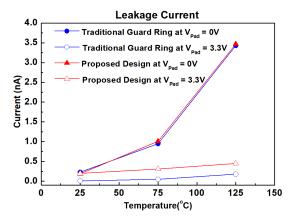

# B. Leakage Current

To observe the leakage current under different voltage levels at the I/O pad  $(V_{Pad})$  and temperatures, the measurement equipment of Keysight 4156C was used. The measured waveforms of standby current on the I/O pad of test cell with the proposed optimization design of active guard ring under dc sweep of  $V_{\text{Pad}}$  from -0.5 to 3.5 V is shown in Fig. 12. In comparison with the prior art [16], there is no diode string providing the voltage reference in the proposed design. The standby current of I/O pad of test cell (ESD devices) with the proposed design is almost the same as that of I/O pad of test cell with traditional guard ring, as shown in Fig. 13, where the leakage currents are captured with the  $V_{\text{Pad}}$  biased at 0 or 3.3 V under different temperatures. The device dimensions of ESD devices in the I/O pads of test cells with the proposed active guard ring design or the traditional guard ring have been listed in Table VI, where the total device dimensions and the drain diffusions (connected to the I/O pad) in layout are kept the same for this leakage current comparison.

#### C. ESD Robustness

The ESD robustness of the I/O cells with the optimized active guard ring design and the traditional guard ring is tested

TABLE VII ESD ROBUSTNESS OF THE I/O CELLS (ESD DEVICES) WITH ALL TESTKEYS UNDER PS-MODE AND ND-MODE HBM ESD TEST

| Testk                          | xeys           | ESD Devices<br>with<br>Traditional<br>Guard Ring | ESD Devices<br>with the<br>Proposed Design |

|--------------------------------|----------------|--------------------------------------------------|--------------------------------------------|

| Dimension<br>of<br>ESD devices | M <sub>P</sub> | 35 μm*16                                         | 35 μm*13                                   |

|                                | M <sub>N</sub> | 35 μm*16                                         | 35 μm*13                                   |

| HBM ESD-<br>Stress mode        | PS mode        | 7.8kV                                            | 6.4kV                                      |

|                                | ND mode        | -4.6kV                                           | -5.8kV                                     |

| HBM/Area<br>of<br>ESD devices  | PS mode        | 3.43V/µm <sup>2</sup>                            | 3.46V/µm <sup>2</sup>                      |

|                                | ND mode        | $-2.02V/\mu m^2$                                 | -3.14V/µm <sup>2</sup>                     |

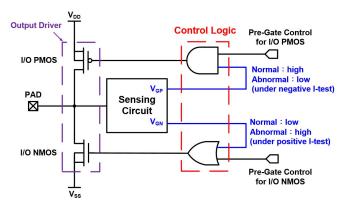

Fig. 14. Concept of the output driver codesigned with the proposed optimization active guard ring design (sensing circuit) and the control logic.

with a commercial ESD tester (HED-W5100D) for the humanbody model (HBM). The ESD levels of I/O cells (with ESD devices) of all testkeys under PS (positive-to- $V_{SS}$ ) mode and ND (negative-to- $V_{DD}$ ) mode of HBM ESD stresses are listed in Table VII. The HBM levels of I/O cells (ESD devices) with the proposed optimization active guard ring design are even better, in comparison with that with traditional guard ring, when the ESD levels are normalized to the silicon area of ESD devices. Especially in the ND mode, the ESD robustness of the I/O cells (ESD devices) with the proposed optimization active guard ring design is more improved.

#### IV. APPLICATIONS

The proposed active guard ring design can also be applied to the output drivers. The concept of the output driver codesigned with the proposed active guard ring and the control logic is shown in Fig. 14. An "AND" gate is added between  $V_{GP}$  of the sensing circuit and the pregate control for I/O pMOS of the output driver. Furthermore, an "OR" gate connects between  $V_{GN}$  of the sensing circuit and the pregate control for I/O nMOS of the output driver. The sensing circuit has been shown in Fig. 3, which is surrounded by a red dashed line. Under normal circuit operation,  $V_{GP}$  is kept at logic "1" and  $V_{GN}$  is kept at logic "0." During latch-up I-test, the logic states of  $V_{GP}$  and  $V_{GN}$  will be changed by the sensing circuit to run the function of "active guard ring." When a negative I-test is applied to the output pad,  $V_{GP}$  will be pulled low due to the operation of the sensing circuit (active guard ring), which in turn turns on the I/O pMOS. Therefore, some positive current will flow from  $V_{DD}$  to the pad through the channel of I/O pMOS, and to compensate the negative current injected to the pad. On the contrary, when a positive I-test is performed on the output pad,  $V_{\rm GN}$  will be pulled high due to the operation of sensing circuit (active guard ring), which in turn turns on the I/O nMOS. Therefore, the positive latch-up trigger current applied to the pad will be conducted to VSS through the channel of I/O nMOS and to compensate the positive current injected to the pad. Hence, the latch-up trigger current injecting into p-substrate can be reduced significantly. The overall latch-up immunity of the output driver can be effectively improved. Moreover, the spacing between I/O cells and core circuits can be closer to reduce the chip area, as well as the latch-up immunity is not degraded. The circuit implementation of the control logic in Fig. 14 with the inputs of  $V_{\text{GP}}$ ,  $V_{\text{GN}}$ , and the pregate control signals should be carefully designed with tapped buffer to drive the large-dimensional MOSFETs in the output driver.

# V. CONCLUSION

The new proposed optimized active guard ring design has been successfully verified to improve latch-up immunity of CMOS ICs in 0.18- $\mu$ m 1.8-/3.3-V CMOS technology. The new proposed design can further save 42% silicon area and not suffer standby leakage current, as compared to the prior work [16]. The layout to enable the proposed optimization active guard ring design from the I/O cell with traditional guard ring can be simply achieved by changing the metal connection to the gates of ESD devices (GGNMOS and GDPMOS) with the resistors  $R_{\rm P}-V_{\rm DD}$  and  $R_{\rm N}-V_{\rm SS}$ , respectively. In other words, if the latch-up immunity level of some I/O cells in a CMOS IC did not meet the requested specification of applications, the proposed optimization active guard ring design will be a cost-efficient solution for latch-up immunity improvement. In addition, the ESD robustness of I/O cells can become even better, when the optimization active guard ring design is applied on the I/O cells.

#### ACKNOWLEDGMENT

The chip fabrication was supported by the National Chip Implementation Center, Taiwan. The authors would like to thank Vanguard International Semiconductor Corporation for the support of commercial latch-up test equipment. They would also like to thank for the JDP Program supported by TSMC, Hsinchu, Taiwan.

### REFERENCES

- S. H. Voldman, *Latchup*. Hoboken, NJ, USA: Wiley, 2007, doi: 10.1002/.9780470516171.

- [2] M.-D. Ker and C.-Y. Wu, "Modeling the positive-feedback regenerative process of CMOS latchup by a positive transient pole method: Part I-theoretical derivation," *IEEE Trans. Electron Devices*, vol. 42, no. 6, pp. 1141–1148, Jun. 1995, doi: 10.1109/16.387249.

- [3] M.-D. Ker and S.-F. Hsu, *Transient-Induced Latchup in CMOS Integrated Circuits*. Hoboken, NJ, USA: Wiley, 2009, doi: 10.1002/.9780470824092.

- [4] JEDEC Solid State Technology Association, JEDEC Standard JESD78E, IC Latch-Up Test, 2016.

- [5] D. B. Estreich, A. Ochoa, and R. W. Dutton, "An analysis of latch-up prevention in CMOS IC's using an epitaxial-buried layer process," in *IEDM Tech. Dig.*, Dec. 1978 pp. 230–234, doi: 10.1109/IEDM.1978.189394.

- [6] A. G. Lewis, R. A. Martin, T.-Y. Huang, J. Y. Chen, and M. Koyanagi, "Latchup performance of retrograde and conventional n-well CMOS technologies," *IEEE Trans. Electron Devices*, vol. 34, no. 10, pp. 2156–2164, Oct. 1987. doi: 10.1109/T-ED.1987.23211.

- [7] R. D. Rung, H. Momose, and Y. Nagakubo, "Deep trench isolated CMOS devices," in *IEDM Tech. Dig.*, Dec. 1982, pp. 237–240, doi: 10.1109/IEDM.1982.190261.

- [8] S. Voldman *et al.*, "The influence of a silicon dioxide-filled trench isolation structure and implanted sub-collector on latchup robustness," in *Proc. IRPS*, Apr. 005, pp. 112–120, doi: 10.1109/REL PHY.2005.1493072.

- [9] S. H. Voldman, "The influence of a novel contacted polysiliconfilled deep trench (DT) biased structure and its voltage bias state on CMOS latchup," in *Proc. IRPS*, Mar. 2006, pp. 151–158, doi: 10.1109/RELPHY.2006.251208.

- [10] J. P. Colinge, Silicon-on-Insulator Technology: Materials to VLSI. Norwell, MA, USA: Kluwer, 1997, doi: 10.1007/978-1-4757-2611-4.

- [11] T.-L. Hsu, Y.-C. Chen, H.-C. Tseng, V. Liang, and J. S. Jan, "Psub guard ring design and modeling for the purpose of substrate noise isolation in the SOC era," *IEEE Electron Device Lett.*, vol. 26, no. 9, pp. 693–695, Sep. 2005. doi: 10.1109/.LED.2005.854351.

- [12] F. Farbiz and E. Rosenbaum, "Modeling and understanding of external latchup in CMOS technologies—Part I: Modeling latchup trigger current," *IEEE Trans. Device Mater. Rel.*, vol. 11, no. 3, pp. 417–425, Sep. 2011, doi: 10.1109/TDMR.2011.2159504.

- [13] F. Farbiz and E. Rosenbaum, "Modeling and understanding of external latchup in CMOS technologies—Part II: Minority carrier collection efficiency," *IEEE Trans. Device Mater. Rel.*, vol. 11, no. 3, pp. 426–432, Sep. 2011, doi: 10.1109/TDMR.2011.2159505.

- [14] M. A. Halfacre, D. S. Pan, and W. K. Huie, "N- well CMOS process on a P substrate with double field guard rings and a PMOS buried channel," U.S. Patent 4574467 A, Mar. 11, 1986.

- [15] M.-D. Ker and W.-Y. Lo, "Methodology on extracting compact layout rules for latchup prevention in deep-submicron bulk CMOS technology," *IEEE Trans. Semicond. Manuf.*, vol. 16, no. 2, pp. 319–334, May 2003. doi: 10.1109/TSM.2003.811885.

- [16] H.-W. Tsai and M.-D. Ker, "Active guard ring to improve latchup immunity," *IEEE Trans. Electron Devices*, vol. 61, no. 12, pp. 4145–4152, Dec. 2014. doi: 10.1109/TED.2014.2363171.

- [17] J. Quincke, "Novel test structures for the investigation of the efficiency of guard rings used for I/O-latch-up prevention," in *Proc. IEEE Int. Conf. Microelectron. Test Struct.*, Mar. 1990, pp. 35–39, doi: 10.1109/ICMTS.1990.67876.