# Design of Stage-Selective Negative Voltage Generator to Improve On-Chip Power Conversion Efficiency for Neuron Stimulation

Shiau-Pin Lin and Ming-Dou Ker<sup>(D)</sup>, Fellow, IEEE

Abstract-Dedicated to neuron stimulation circuits, a stageselective negative voltage generator is proposed to enhance the overall power efficiency. Since the supplied voltage of the stimulus driver is subject to applications and treatments, an extensive output requirement of supply is demanded to achieve energy-efficient stimulation. The charge pump is implemented as a negative voltage generator for on-chip design. In a limited area, excess power loss is eliminated by reconfiguring the cascaded architecture and clocks. Digitally programmable voltage levels can be outputted by varying the number of stages dynamically. The function of stage selection is achieved by the proposed stage-selective scheme. With appreciate control, the stage-selective negative voltage generator can maintain higher power efficiency under different output voltage levels and loading conditions. The technique improves 40% power conversion ratio at most but only leads to an increment of 8% in area occupation. The measured output voltage covers from -0.3 V to -9.3 V within a maximum 5.5-mA output current, which is verified in a  $0.25 - \mu m$  BCD process.

*Index Terms*—Stage-selective circuit, stage control, negative voltage generator, negative charge pump, energy-efficient.

#### I. INTRODUCTION

MONG all the DC-to-DC converters, switching capacitive converters (i.e. charge pump) are suitable for highvoltage generation in many applications, especially in neuron stimulation [1]–[8]. Microelectronics-based stimulators deliver voltage or current pulses as electrical stimulation treatment and treat neurological disorders as well [9]. For the purposes of biomedical stimulation circuits, providing a high voltage to drive a stimulator is the principal objective of a highvoltage generator. Hence, area cost and energy efficiency are the two major issues to be discussed [10]. Compared with traditional inductor-based or transformer-based converters, the charge pump favors the significantly on-chip considerations

Manuscript received March 7, 2020; revised July 20, 2020; accepted July 22, 2020. Date of publication August 4, 2020; date of current version October 30, 2020. This work was supported in part by the Ministry of Education (MOE) through the SPROUT Project, Center for Neuromodulation Medical Electronics Systems of National Chiao-Tung University, Taiwan, in part by the Ministry of Science and Technology (MOST), Taiwan under Contract MOST 108-2321-B-009-007-MY2, and in part by the fabrication of silicon chip through the Taiwan Semiconductor Research Institute (TSRI). This article was recommended by Associate Editor F. M. Neri. (*Corresponding author: Ming-Dou Ker.*)

The authors are with the Biomedical Electronics Translational Research Center, National Chiao-Tung University, Hsinchu 300, Taiwan (e-mail: mdker@ieee.org).

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCSI.2020.3012086

**Detection Circuit** Variable Supply Stage Controller Stimulation Detection V V Negative Positive Impedance Charge Charge Detection Pump Pump Stimuli Stimulus Generator Driver Tissue / Stimulator Electrodes

Fig. 1. A conceptual stimulation system for energy conservation includes the variable supply, the detecting circuit, and the stimulator. In this paper, a new proposal of the variable supply is composed of a stage controller and negative charge pump.

on area concerns. From the perspective of energy efficiency, it is strongly related to battery lifetime for a long period of usage. Without any off-chip components, the charge pump can effectively generate positive or negative high voltage from a lower voltage by different charge pump topologies. Therefore, it can support stimulators to deliver desired stimulus patterns. However, the organic impedance may be varied or the stimulus scale may be changed during therapeutic processes. It indicates that the required supply for stimulators is not always a fixed value [5]–[7]. In fact, it varies from several volts to tens of volts [8]. To make stimulators work more conservative, a charge pump with a wide output range is developed.

In a stimulation system, a variable supply system is an advanced integration to provide expected power dynamically and efficiently. A conceptual system is drawn in Fig. 1, containing a variable supply system, a detecting system, and stimulus drivers. In order to maximize the overall efficiency of implantable stimulators, adaptive power supply techniques are required to minimize the voltage drop across the stimuli generator. Some algorithms are imperative as criteria for dynamic reconfigurability. One of the detection circuits is accomplished by the electrode monitoring circuit (EMC) [6]. It can immediately measure the electrode output voltage and further tell the sufficiency of power supply by comparing the output voltage of electrodes and the high voltage generator. A stimulator buffer with a triode indicator [7] is used to

1549-8328 © 2020 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

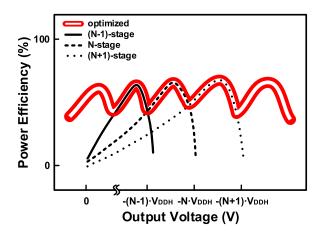

Fig. 2. An illustrated characteristic of the voltage generator (i.e. charge pump) with a fixed configuration. Black lines indicate the charge pump is implemented with an invariable architecture while the red line is an optimal performance against different output voltage.

monitor the operating region of the cascode current mirror. As long as the cascode current mirror is oppressed into the triode region, the indicator implies the inadequate power supply. Although several detection approaches are presented, an energy-efficient stimulation system may still be imperfect without the variable supply. Therefore, the charge pump with a variable output level is a decisive part to complete the entire conservative system.

One of the challenges of a variable supply system is to achieve the equilibrium of area and efficiency. More still, once the negative voltage is involved, reliability issues are critical and integrated considerations are problematic [11], [12]. Junction leakages and latch-up problems necessitate a careful solution. Besides, as if the configuration of a negative charge pump is established, the characteristic is determined as any black lines in Fig. 2. In a closed-loop system, only adjusting the reference voltage (V<sub>REF</sub>) to vary the output voltage (V<sub>OUT</sub>) and regulating V<sub>OUT</sub> by feedback control may suffer efficiency-drop issues. In other words, the peak power efficiency occurs only at a certain voltage gain in each configuration. The excessive current loss gives rise to inferior efficacy [13]. Standing on this statement, several individual charge pump loops with different stages are integrated into a single chip. All the hills are collected as the red line shown in Fig. 2. Unfortunately, it would cost a large silicon area instead. Heretofore, efficiency maintenance and area conservation are conflicted in typical negative voltage generation.

In the sight of these reasons, a stage-selective negative voltage generator is proposed to balance the trade-offs of size and efficiency. The voltage generator is implemented with a switched-capacitor regulator in a 0.25- $\mu$ m BCD process. Compare to the conventional charge pump, the key features in this work are stage selection, negative voltage operation, and efficiency maintenance. The experimental results show that the proposed stage-selective circuit for charge pump can extend the output range and improve power efficiency, though it cost few increments on the area. In this paper, the definitions of voltage generator and charge pump are equivalent. Clearly, a voltage generator is specific for its voltage conversion and the

charge pump is particular about the switched capacitor operation. The paper is organized as follows: Section II reviews variable output techniques; Section III introduces the proposed circuit; Section IV presents simulated and measured results; Section V draws the conclusion.

## II. REVIEW OF VARIABLE OUTPUT TECHNIQUES

In the past, the charge pump is applied to vast integrated circuits with different requirements. For more progressive development, the charge pump is no longer being restricted by a constant voltage level. Some variable output techniques are presented to carry out more output requirements and conserve unnecessary current consumption. Previous variable output techniques are briefly introduced below for an energy-efficient system.

In the microelectromechanical system (MEMS), the variable actuation voltage is generated by the charge pump for electrostatic resonators biasing. Through external parameterized codes, the charge pump is implemented with the reconfigurable switched capacitor array [14] and even the tunable clock amplitude [15] to drive capacitive loads. In RF filters, the cascaded stages of the charge pump are gated by separated clock signals, so the output voltage can be tuned [16]. In typical flash memories, the charge pump contributes to high voltage generation whose output level depends on read, erase, and program operations. The variable output technique is achieved by adding several bypass switches [17]. It adopts a serial-parallel topology to draw a variable-conversion-ratio converter [18]. By adding several bypass switches, any reduction of the number of stages is taken place by a short circuit between the input and output terminals [19]. In [20], the charge pump combines different cell circuits so as to generate plural output voltages with superior efficacy. But for low-power RRAM realization, a main charge pump with a monitor charge pump [21] is able to adjust the number of stages and minimize current consumption. The presented stage control circuit determines the main pump configuration based on the clock comparison results. A variable charge pump is a tendency to export a larger output voltage range so far. There is no exception for neuron stimulation. With an invariable structure, the charge pump can increase or decrease output voltage with a tunable V<sub>REF</sub> and in a closed-loop [7], [22]. The reconfigurable switched-capacitor network for neuron stimulation is addressed to convert an input voltage into half, double, or even triple [23], [24]. Another conventional charge pump with several paralleled bypass switches makes the structure and the output variable [25]. However, none of the state-of-theart is applied to negative voltage operation. Most of them are hard to perform logic control in the negative voltage domain. Since the loading current varies from hundreds of nanoamps to several milliamps, a complicated topology may cause a severe parasitic effect on charge paths. Nevertheless, an additional charge pump that assists to track loading conditions would occupy redundant area cost. It does not benefit implantable biomedical applications and larger output current. Lastly, a novel charge pump intends to improve these problems and joins in negative voltage generation in this work.

## III. PROPOSED STAGE-SELECTIVE NEGATIVE VOLTAGE GENERATOR

A stage-selective negative voltage generator is proposed to enhance the overall power efficiency within a limited area. Typically, power losses can be classified as conduction loss, switching loss, redistribution loss and reversion loss [26]. A switched-capacitor converter performs better efficiency through proper optimization among a variety of power losses. For a wide output range, efficiency decay appears at low voltage gain cases. Power dissipates through charge conduction loss and switching loss is worsening due to more charge pump stages cascaded. Redistribution loss takes place at charge sharing between any two capacitors. The last reversion loss is about an undesirable short circuit path in the power stage of the negative charge pump. In this work, the main concept is to generate the desired output voltage with appropriate activated stages and eliminate excess power loss.

## A. Proposed Stage-Selective Circuit

In a conventional configuration of the negative charge pump, charge pump cells are cascaded stage by stage and fixed. A proposed stage-selective circuit is added to make the configuration more flexible. In this work, there are two operational modes: pump mode and bypass mode. The "pump mode" is defined to increase the activated stage number of negative charge pump whereas the "bypass mode" is to decrease the activated stage number. In other words, the charge transfer path would be reconfigured from N to more than N stages in the pump mode, but it would be reconfigured from N to less than N stages in the bypass mode, where N represents the number of the activated charge pump cells.

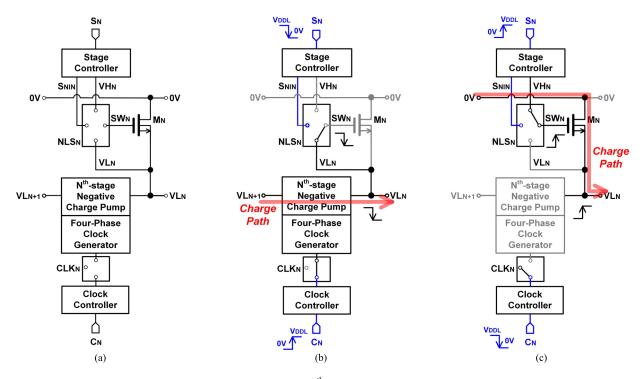

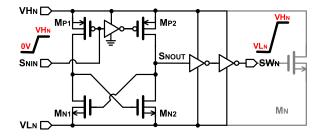

As shown in Fig. 3(a), the operational mode is specified by the digital signals S<sub>N</sub> and C<sub>N</sub> through the corresponding controllers. In each stage, the stage-selective circuit consists of a stage controller, a negative level shifter (NLS<sub>N</sub>), and a bypass switch (M<sub>N</sub>). The external digital signal S<sub>N</sub> is refined by the stage controller for time delay and then delivered as an internal control signal S<sub>NIN</sub>. Besides, the bias VH<sub>N</sub> is given by the stage controller as the power node of the NLS. Once the NLS received S<sub>NIN</sub>, it would convert and extend the voltage domain from positive to negative at S<sub>NOUT</sub> and SW<sub>N</sub>. In an NLS, M<sub>P1</sub> and M<sub>P2</sub> are used to sense input voltage levels. The associated connection is annotated in Fig. 4. By comparing the pull-up current of PMOS ( $M_{P1}$  and  $M_{P2}$ ) and the pull-down current of NMOS (M<sub>N1</sub> and M<sub>N2</sub>), the output signals SW<sub>N</sub> of negative level shifters are requested to either fully conducted or completely cut off the bypass switches (M<sub>N</sub>). When SW<sub>N</sub> is connected to VH<sub>N</sub> which is a positive potential (equal to V<sub>DDH</sub>), M<sub>N</sub> would be fully turned on. Charges transfer through the bypass switch  $(M_N)$ . When  $SW_N$  is tied to  $VL_N$  which is a negative potential, M<sub>N</sub> would be turned off. Moreover, a clock controller is commanded by the digital signal C<sub>N</sub>. C<sub>N</sub> controls whether the clock signal of the whole system is able to deliver into the charge pump cell or not. When the charge pump stage is bypassed by the S<sub>N</sub> signal, the clock controller disconnects the clock to save some energy by  $C_N$  signal. To be brief,  $S_N$

determines the operating mode of the selected  $N^{th}$  stage along with  $C_N$  whether to pump up or bypass away  $VL_N$ .

## B. Operative Mechanism

Because of the similar composition in each stage, the operation is introduced in Fig. 3(b) and Fig. 3(c). In order to pump up the voltage in Fig. 3(b), the stage control signal (S<sub>N</sub>) would go low to turn off the bypass path. Then, the clock control signal (C<sub>N</sub>) would go high to pass the clock signal into the core circuit. Thus, the output voltage at VL<sub>N</sub> can be pumped to a more negative value with the system frequency. The charge path is diverted from the N<sup>th</sup> bypass switch into the negative charge pump cell. In short, a low S<sub>N</sub> and a high C<sub>N</sub> declare that the selected N<sup>th</sup> stage is operating in the pump mode. On the contrary, S<sub>N</sub> would be pulled high when entering the bypass mode as shown in Fig. 3(c). A high S<sub>N</sub> conducts the selected bypass switch and makes the excessive voltage at VL<sub>N</sub> bypassed away. Meanwhile, C<sub>N</sub> would be pulled low to shut off the corresponding clock controller, and further stop the clock toggling in the N<sup>th</sup> four-phase clock generator. Hence, the core charge pump circuit is ceased and no longer deliver charges. The charge transfer path is substituted by the bypass switch. A higher value (i.e. less negative) at  $VL_N$  may be achieved with less energy loss due to the short circuit of  $M_N$ .

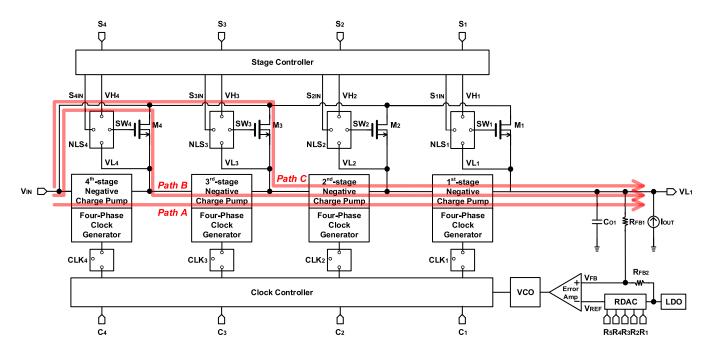

The closed-loop negative voltage generator with the stageselective is presented in Fig. 5. Since the bypass switch is connected between the first input terminal ( $V_{IN}$ , 0 V) and the N<sup>th</sup> output terminal (VL<sub>N</sub>), there is an order to pump or bypass the charge pump stages from which direction. For pumping, the power stage which is nearer the output terminal has the priority to be activated (i.e. pump 1<sup>st</sup>-, 2<sup>nd</sup>-, 3<sup>rd</sup>-, and 4<sup>th</sup>-stage in order). But for bypassing, it begins from the one nearer the input terminal to disable the power stage (i.e. bypass 4<sup>th</sup>-, 3<sup>rd</sup>-, 2<sup>nd</sup>-, and 1<sup>st</sup>- stage in order). The arrangement makes the proposed scheme not only flexible but also reconfigurable.

A four-stage composition is adopted in Fig. 5. The negative charge pump cells are successively jointed. The proposed circuit is replicated and connected to the cells accordingly. Charges are sent from the input terminal (VIN) and stored in the output capacitor  $(C_{O1})$  at the output terminal  $(VL_1)$ . In general, the input voltage at  $V_{IN}$  is 0 V as well as the ground. For example, the negative voltage generator is set to a four-stage configuration initially. Yet, the composition is expected to cut down by half for energy conservation. To prevent unknown conditions and residual charges, the fourth and the third power stages are bypassed in sequence. By conducting M<sub>4</sub> and turning off CLK<sub>4</sub>, VL<sub>4</sub> would be released to the input voltage level (VIN, 0 V). And then the similar progress is repeated in the third stage. A fully conducted M<sub>3</sub> gives the input 0 V to VL<sub>3</sub>. Clock signals are no longer coupled into the charge pump cell thanks to an open CLK<sub>3</sub>. VL<sub>3</sub> is discharged gradually as well as VL<sub>1</sub>. Lastly, only the second and the first stages are available so that charges are delivered to VL1 with a two-stage configuration of the negative voltage generator. The charge transfer path is changed from path A to path B and finally path C, as annotated in Fig. 5. Somehow a lower output voltage (more negative) is needed

Fig. 3. (a) The unit structure of the proposed stage-selective circuit in the N<sup>th</sup> stage. The operation of each selected stage with corresponding control signals. (b) In the pump mode,  $S_N$  is low but  $C_N$  is high; thus, the N<sup>th</sup>-stage negative charge pump becomes the primary charge transfer path. (c) In the bypass mode,  $S_N$  turns high and  $C_N$  turns low so that charges directly pass through the N<sup>th</sup>-stage bypass switch (M<sub>N</sub>).

Fig. 4. The detailed circuit schematic of the negative level shifter (NLS).

at VL<sub>1</sub>. Therefore, the negative voltage generator returns to the four-stage configuration by means of enabling the third and the fourth stages. To boost a more negative voltage, it is necessary to cut off the bypass path, which is created by  $M_3$  and  $M_4$ . The entire closed-loop system would attempt to regulate VL<sub>1</sub> by toggling clock signals. In this event, CLK<sub>3</sub> and CLK<sub>4</sub> are short to transfer clocks into four-phase clock generators. A more negative output voltage is produced at VL<sub>1</sub> in the end. The charge transfer path is changed from path C to path B and finally path A, as annotated in Fig. 5.

When the loop is locked at a certain output level, more than one configuration might be able to achieve this scenario. If excessive power stages and clock generators are activated to meet the specification, too many charges would be redistributed. And further, more energy is dissipated. In contrast, the lack of activated stages and clock generators may induce overclocking, thereby the more switching loss getting worse. Thus, a competent configuration can perform better efficiency and stability with exact power stages and clocks. Depending on the conversion ratio, the power loss of the pumping stage can be optimized by the proposed circuit. The output voltage at  $VL_1$  can provide the desired value with less power loss.

## C. Circuit Implementation

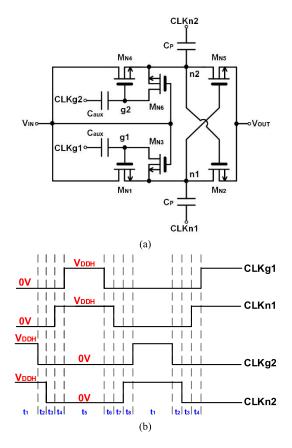

In Fig. 5, the affiliated circuits comprise the voltage divider, the reference bias circuit, the error amplifier, the voltage control oscillator (VCO), positive level shifters, the four-phase clock generator, and the four-stage charge pump. For more details, a resistive digital-to-analog converter (RDAC) is a reference bias circuit in binary-weighted R-2R networks. The generated voltage (V<sub>REF</sub>) of RDAC is controlled by five-bit signals  $R_{[1:5]}$ . According to the reference voltage ( $V_{REF}$ ) and the resistive divider, the output of the charge pump loop would be locked at a target voltage level (V<sub>TG</sub>). Whether the cascaded configuration or the output current is, the proposed stage selective negative charge pump is seen as a self-regulated closed-loop unit with pulse frequency modulation (PFM) feedback control. It is notable that the error amplifier is designed with a wide bandwidth to trace the desired output target. Considered to a quick start-up and numerous output loading conditions, the oscillation frequency of the VCO should cover from several MHz to tens of MHz. In addition, a four-phase cross-couple structure is adopted as the core circuit of the negative charge pump cell [27]. The specific connection and the four-phase sequence of the charge pump cell are presented in Fig. 6. This topology is free from overstress issues because only 1×V<sub>DDH</sub> is delivered in each cascaded stage. For the reason that the power domain of the four-phase clock generator is V<sub>DDH</sub>, the clock edges would only couple the toggling signals

Fig. 5. The block diagram of the proposed stage-selective negative voltage generator.

Fig. 6. (a) The circuit schematic and (b) the corresponding four-phase clocking waveforms of the negative charge pump cell.

with  $1 \times V_{DDH}$ . Overstress concerns in charge pump cells are eliminated. The four-phase operation releases the return-back leakage and reversion loss. By virtue of the biomedical SoC integration, the global P-substrate is tied to 0 V as a ground.

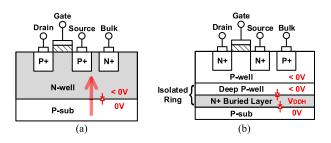

Fig. 7. The cross-section view of (a) PMOS forbidden to implement in the negative voltage domain and (b) NMOS with an isolated ring used in the negative charge pump cell.

For the sake of operation in the negative voltage, PMOS is forbidden to implement in all negative voltage domains, unless high voltage devices. Otherwise, PMOS could result in the forward parasitic diode in Fig.7 (a). All the switches are implemented in NMOS with isolation. The isolated ring is provided in the process with a deep P-well and a N+ buried layer (NBL) ring. The source and bulk terminals are jointed to avoid body effect. All NMOS are immersed in negative voltage, and the bias potential of P-well bulk ring and deep P-well ring is also negative. But the NBL is biased at V<sub>DDH</sub> which is the highest voltage in the entire system. All the parasitic PN-junctions are reverse biased to prevent junction leakage. In Fig. 7(b), it annotates the practical bias conditions and the cross-section view of a switch in one charge pump cell.

## IV. VERIFICATIONS AND DISCUSSIONS

The proposed negative voltage generator with stage- selective circuits verifies the design on area and efficiency maintenance. Furthermore, configuration diversity is improved by additional bypass switches. This work has been fabricated in a

Fig. 8. The simulated results of the negative voltage generator to demonstrate its start-up and regulation.

TSMC 0.25- $\mu$ m 2.5-V/5-V/12-V BCD process. In this process, the thick oxide in 12-V devices can tolerate the high voltage stress, yet the threshold voltage is high. Therefore, they are only adopted to NLS<sub>N</sub> and M<sub>N</sub> in the proposed stage-selective circuit. The maximum voltage difference in NLS<sub>N</sub> and M<sub>N</sub> is about 13 V in this work.

#### A. Simulation and Comparisons

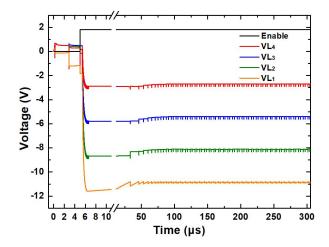

For implantable biomedical applications, the impedance of electrodes and tissue varies with the size and position of the electrode. In neuron stimulation, the impedance value of the human brain is about 1 k $\Omega$  to 3 k $\Omega$ . The requisition of the power supply of stimulus drivers is widespread for either constant voltage or constant current stimulation. Thus, the stage- selective negative voltage generator is designed to output a wide voltage range within 5.5-mA output current. The output voltage (VL<sub>1</sub>) is expected to regulate from -0.3 V to -9.3 V with the supplied voltages of 1.8 V (V<sub>DDL</sub>) and 3 V (V<sub>DDH</sub>). In this work, V<sub>DDL</sub> is for analog circuits to minimize power. Yet V<sub>DDH</sub> is for clock generators to couple the pumping capacitors. Aforementioned above, the analog type VCO gives around 100 MHz clocks to boost VL<sub>1</sub>, so the quick start-up takes only 1  $\mu$ s to reach the target voltage in Fig. 8. As long as the voltage is achieved, the clock frequency would slow down but still keep toggling to regulate by the PFM control.

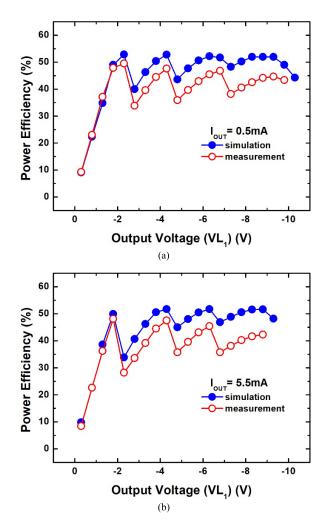

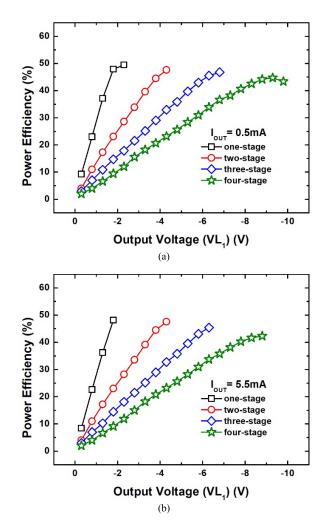

Since the negative charge pump is implemented with four stages, the charge path can be reconfigured as zero-stage, one-stage, two-stage, three-stage, and four-stage in total. The zero-stage is for discharging and reset. Each configuration is born with its characteristic curves on power efficiency and output voltage. The simulated results under different loading conditions were explained in Fig. 9 (solid), including the minimum 0.5-mA and maximum 5.5-mA output current. The maximum voltage conversion is to couple  $1 \times V_{DDH}$  in each stage. When the voltage conversion ratio is between 60% and 80%, power losses are optimized to make the overall efficacy better. In other words, if the activated stages are appropriate for the output voltage levels, the power efficiency would be kept at a higher performance.

Fig. 9. The simulated and measured characteristics of the stage-selective negative voltage generator. (a) Under 0.5-mA output current (light load). (b) Under 5.5-mA output current (heavy load).

When the target level is loose, the major power loss is attributed to redistribution loss. Some of the delivered energy is dropped out so that the power efficiency is lower. However, when the target level is tight, the entire negative voltage generator is operated under a higher frequency. The power efficiency would drop dramatically as a result of the massive switching loss. Therefore, only a particular zone is preserved to achieve the expected efficiency without reconfigurable pumping schemes. Collecting the peak power efficiency of each configuration, the characteristic curves of this work are featured with the four successive hills. With stage selection, the simulated power efficiency is around 35% to 40% at valleys and roughly 50% at hilltops. As a result, the proposed negative voltage generator holds a better configuration and keeps a higher efficiency.

## B. Silicon Verifications

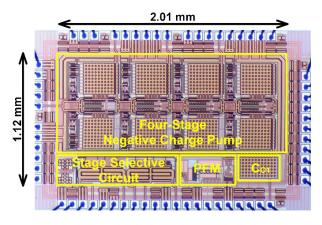

The die microphotograph of the stage-selective negative voltage generator chip is shown in Fig. 10. Excluding I/O pads, the test chip occupies a silicon area of 2.25 mm<sup>2</sup>. To further break down, 8% is occupied by the proposed stage-selection

Fig. 10. Die microphotograph of the fabricated stage-selective negative voltage generator.

circuits, 87% is the power stages and all on-chip capacitors, and the rest 5% is the peripheral PFM circuits. For on-chip realization, all the capacitors are implemented with the metalinsulator-metal (MIM) capacitors. According to different purposes, capacitors are sorted into pumping capacitors (C<sub>P</sub>), auxiliary capacitors (C<sub>aux</sub>), and output capacitors (C<sub>OUT</sub>). C<sub>P</sub> is a fly capacitor of 100 pF so as to couple  $1 \times V_{DDH}$ . C<sub>aux</sub> which is sized to 2.5 pF only helps the main transistors for conduction. In addition, C<sub>OUT</sub> at the output node (VL<sub>1</sub>) is drawn with 125 pF to store charges and reduce output ripples.

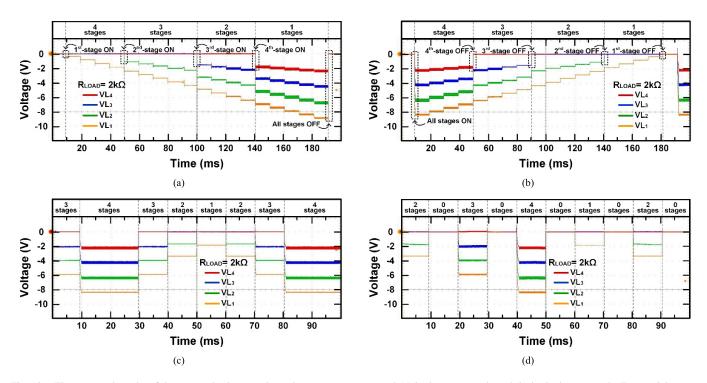

As mentioned above, each configuration possesses its own characteristic curves on power efficiency and output voltage. The silicon measured results are presented in Fig. 11. When the configuration is fixed to certain stages, it can only vary output levels by adjusting VREF and suffer low efficiency at less negative voltage cases. The major object is to combine those high efficiency parts in each configuration, and the four successive hills are gathered in Fig. 9 (hollow). The proposed circuit is verified to enhance the power conversion ratio around 40% to 55% with the assistant of the stage-selective circuit in measurements. Owing to the complex control sequence, digital codes are programmed into an external testing board and delivered to the internal test chip. Several control signals make the proposed negative voltage generator more flexible. The architecture is not fixed and the output is not constant, either. In this work, stage control signals  $(S_{[1:4]})$  and clock control signals ( $C_{[1:4]}$ ) are given to reconfigure the cascaded structure and clocks. In each configuration, reference control signals  $(R_{[1:5]})$  further alter the regulated target voltage. Except the Enable signal is still manually controlled, other control signals come from digital control. As shown in Fig. 12(a), the fabricated chip is requested to alter VL1 from -0.3 V to -9.3 V. The output impedance is 2 k $\Omega$ . In contrast, VL<sub>1</sub> in Fig. 12(b) is initially pumped to a negative high level and then stepped down. In a closed-loop system, the PFM feedback control technique is applied to regulate VL1 at numerous levels. Under the optimized and activated stages,  $VL_1$  is set with a resolution of -0.5 V. Whether it is operated in pump mode (Fig. 12(a)) or in bypass mode (Fig. 12(b)), the proposed circuit succeeds to expand the output voltage range and improves the low-efficiency issue. The variable

Fig. 11. The measured characteristics of the negative voltage generator with different cascaded configuration. (a) Under 0.5-mA output current (light load). (b) Under 5.5-mA output current (heavy load).

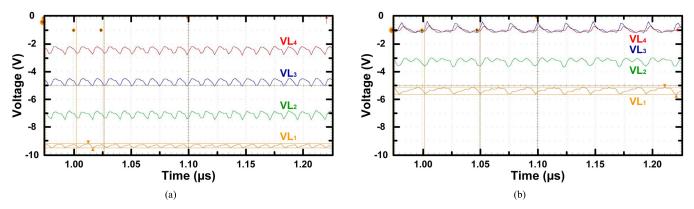

technique is mainly for energy-efficient motivation, and the slight voltage shift avoids spikes from damages. Since VL1 usually supports stimulators in biomedical SoC, increasing the supply of stimulators step by step performs a soft start-up. Decreasing the supply is to discharge and reset for thorough power-off. In Fig. 12 (c), the proposed stage-selective circuit is operated in order so that the configuration is transformed stage by stage. Under corresponding activated stages, VL<sub>1</sub> is locked at different objects. For instance, VL<sub>1</sub> is stabilized at -1.8 V with one stage validated, -3.3 V with two stages, -5.8 V with three stages, and -8.3 V with four stages. The measured results are recorded on waveforms. Moreover, it can also change the entire cascaded architecture arbitrarily. Despite the irregular transformation, the whole system is still able to settle on the target voltage. As depicted in Fig. 12(d), the configuration is varied out of order. Focusing on the transient state,  $VL_1$  is able to regulate at a certain target voltage with the feedback control. The negative voltage generator is composed of a four-stage configuration, as a result, a stable -9.3-V output voltage is delivered under a 5.5-mA current loading, as demonstrated in Fig. 13(a). The internal nodes, including  $VL_2$ ,  $VL_3$ , and  $VL_4$ , are also presented to explain the voltage

Fig. 12. The measured results of the stage-selective negative voltage generator operated (a) in the pump mode and (b) in the bypass mode. For special cases, the reference values and the activated stages of the stage-selective negative voltage generator are varied (c) in order and (d) out of order. All the measured events are verified with the output impedance of  $2-k\Omega$  (heavy load).

Fig. 13. (a) The measured results of the stage-selective negative voltage generator at -9.3-V output voltage and 5.5-mA loading current by a four-stage configuration. (b) The measured results of the stage-selective negative voltage generator at -4.3-V output voltage and 3.5-mA loading current by a two-stage configuration.

conversion ratio in each stage. In addition, it can also provide a -4.3-V output voltage and a 3.5-mA current loading with a two-stage configuration in Fig. 13(b). Since the third and the fourth stages are bypassed, VL<sub>4</sub> and VL<sub>3</sub> are short to the input terminal as well as 0 V. Under different loading conditions, the functions and performances are verified in silicon chips.

Based on these measured results, specifications of the fabricated stage-selective negative voltage generator are summarized in Table I and compared to other previous works. On the basis of negative voltage, this work takes advantage of a wide output voltage range and a large output current loading. With stage selection, an extensive voltage range and efficient power conversion have been accomplished and verified. The entire performance is flexible rather than fixed output or fixed charge transfer scheme. The new proposal of the variable output scheme can be realized in the negative voltage. From the perspective of a reconfigurable negative voltage generator, the overall power efficiency is optimized and enhanced. The proposed stage-selection circuit profits from making a proper voltage conversion for each power stage.

## C. Discussion

Since input current is consumed consistent with activated pumping stages and clocks, it is important to dispose of redundant pumping blocks. In other words, it may easily suffer low-efficiency issues without stage selection when the activated stages and clocks are not fit for the output voltage levels. On the contrary, stage selection is able to maintain higher power efficiency under different output voltage levels. The greatest originality in this work is to realize the stage-selective circuit in the negative voltage domain. Since P-substrate is connected to 0 V for integration, the usage

| TABLE I                                         |  |

|-------------------------------------------------|--|

| PERFORMANCE COMPARISON WITH RELATED PRIOR WORKS |  |

|                                 | YC. Huang<br>[12]<br>(BioCAS '12) | I. Williams<br>[23]<br>(TBioCAS '13) | J. Gak<br>[24]<br>(LASCAS '13) | JH. Tsai<br>[28]<br>(JSSC '15) | A. Rashidi<br>[29]<br>(LSC '18)            | Z. Luo<br>[25]<br>(TCAS I '19)   | A. Ptal<br>[22]<br>(VLSID '20) | This work                      |

|---------------------------------|-----------------------------------|--------------------------------------|--------------------------------|--------------------------------|--------------------------------------------|----------------------------------|--------------------------------|--------------------------------|

| Technology                      | 0.18-μm<br>CMOS                   | 0.18-μm<br>HV CMOS                   | 0.6-μm<br>HV CMOS              | 0.18-μm<br>CMOS                | 0.18-µm<br>CMOS                            | 0.18-μm<br>CMOS                  | 0.18-μm<br>BCD                 | 0.25-μm<br>BCD                 |

| Supplied<br>Voltage             | 1.8 V                             | 6 V                                  | 1.6~5.5 V                      | 1 V                            | 1.8 V                                      | 3.3 V                            | 1.8 V                          | 3 V                            |

| Output<br>Voltage               | -8.04 V                           | 3~12 V<br>(3 V/step)                 | 0.5~16 V<br>(0.5 V/step)       | 3~6 V                          | 3.48 V<br>-1.69 V*<br>-3.38 V*<br>-5.05 V* | 3.3~12.6 V                       | 7.5~24 V<br>(1.2 V/step)       | -0.3~-9.3 V<br>(-0.5 V/step)   |

| Output<br>Current               | -0.32 mA                          | N/A                                  | N/A                            | 0.24 mA                        | ±0.1 mA                                    | 0.5~3.5 mA                       | 0.1 mA                         | -0.5~-5.5 mA                   |

| Per Flying<br>Capacitance       | 25 pF<br>(on-chip)                | 150 pF<br>(on-chip)                  | 220 nF<br>(off-chip)           | N/A<br>(on-chip)               | 23 pF<br>(on-chip)                         | 50 pF<br>(on-chip)               | N/A<br>(on-chip)               | 100 pF<br>(on-chip)            |

| Area<br>(I/O pads)              | 1.27 mm <sup>2</sup><br>(w/)      | 2.8 mm <sup>2</sup><br>(w/o)         | 1.7 mm <sup>2</sup><br>(w/o)   | 0.5 mm <sup>2</sup><br>(w/o)   | 0.5 mm <sup>2</sup><br>(w/ )               | 2.87 mm <sup>2</sup><br>(w/)     | 0.32 mm <sup>2</sup><br>(w/o)  | 2.25 mm <sup>2</sup><br>(w/o)  |

| Peak<br>Efficiency              | 42.26%                            | $\sim 80\%$                          | 73~79%                         | 52%                            | POS:92.8%<br>NEG:86.8%<br>(simulated)      | ~ 70%                            | ~ 49%                          | 52%                            |

| Activated<br>Stages             | 6×<br>(fixed)                     | 1×<br>(variable)                     | 1× and 2×<br>(variable)        | 4× and 6×<br>(variable)        | 3×<br>(fixed)                              | 3×<br>(variable)                 | 15×<br>(fixed)                 | 0× to 4×<br>(variable)         |

| Variable<br>Output<br>Technique | NO                                | SC network                           | SC network<br>+ Battery        | Hybrid<br>Topology             | NO                                         | Paralleled<br>Bypass<br>Switches | Adjusted $V_{\text{REF}}$      | Grounded<br>Bypass<br>Switches |

\* The three negative voltages come from the internal and output nodes in a 3-stage negative charge pump.

of PMOS is limited. Not only the charge pump cell circuit is carefully designed with the isolated NMOS. But also the bypass switches are implemented by the high voltage NMOS. However, due to the high threshold, the less utility of high voltage devices on charge transfer path is better. Therefore, the grounded bypass switches are adopted to in this work. The most obvious efficiency difference occurs at -2.3-V output voltage. According to Fig. 11, the one-stage configuration is worthwhile to support output loading with 35% efficiency improvement against the four-stage configuration. Moreover, the proposed stage-selection circuit only takes only 8% augmentation on the area. It is obvious that the negative voltage generator with less activated amounts of stages has a higher efficacy during operation. A better performance is achieved by maintaining the voltage conversion ratio in each stage between 60% and 80%. However, it decays as the activated numbers of stages increase. An amendment on power loss is verified and noteworthy. In summary, VL1 can regulate at -9.3 V under the 5.5-mA heaviest loading. The PFM feedback mechanism in coordination with stage selection push the effective output range to a widespread use.

#### V. CONCLUSION

For biomedical treatments, the output and the supplied voltages of stimulators vary from several volts to tens of volts. To provide a larger output range, size and efficiency are the limiting factors for the charge pump with a stationary architecture. A stage-selective negative voltage generator system has been proposed and realized by using the optimized serial stages to reduce excessive power consumption. The fabricated chip has been verified in a 0.25- $\mu$ m BCD process. It generates a plurality of output voltage levels from -0.3 V to -9.3 V while the output loading current covers from 0.5 mA to 5.5 mA. It is an energy-efficient power source so that the power conversion efficiency is held at 50% roughly. With the addition of the stage-selective circuit, a compact area is achieved due to the distinct reconfiguration. Since the cascaded configuration is flexible and programmable, the entire architecture can be arbitrarily controlled by the parameterized digital codes.

#### REFERENCES

- S. Ethier and M. Sawan, "Exponential current pulse generation for efficient very high-impedance multisite stimulation," *IEEE Trans. Biomed. Circuits Syst.*, vol. 5, no. 1, pp. 30–38, Feb. 2011, doi: 10.1109/TBCAS.2010.2073707.

- [2] X.-H. Qian *et al.*, "A bone-guided cochlear implant CMOS microsystem preserving acoustic hearing," in *Symp. VLSI Circuits. Dig. Tech. Papers*, 2017, pp. C46–C47, doi: 10.23919/VLSIC.2017.8008542.

- [3] J. Zhao, L. Yao, R.-F. Xue, P. Li, M. Je, and Y. P. Xu, "An integrated wireless power management and data telemetry IC for highcompliance-voltage electrical stimulation applications," *IEEE Trans. Biomed. Circuits Syst.*, vol. 10, no. 1, pp. 113–124, Feb. 2016, doi: 10.1109/TBCAS.2015.2404038.

- [4] S.-Y. Lee, C.-H. Hsieh, and C.-M. Yang, "Wireless front-end with power management for an implantable cardiac microstimulator," *IEEE Trans. Biomed. Circuits Syst.*, vol. 6, no. 1, pp. 28–38, Feb. 2012, doi: 10.1109/TBCAS.2011.2162409.

- [5] C.-Y. Lin, Y.-J. Li, and M.-D. Ker, "High-voltage-tolerant stimulator with adaptive loading consideration for electronic epilepsy prosthetic SoC in a 0.18-μm CMOS process," in *Proc. IEEE 10th Int. New Circuits Syst. Conf.*, Jun. 2012, pp. 125–128, doi: 10.1109/NEW-CAS.2012.6328972.

- [6] E. K. F. Lee, "A 45 V 10-b electrode monitoring analog-to-digital converter," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2015, pp. 1238–1241, doi: 10.1109/ISCAS.2015.7168864.

- [7] Z. Luo, M.-D. Ker, T.-Y. Yang, and W.-H. Cheng, "A digitally dynamic power supply technique for 16-channel 12 V-tolerant stimulator realized in a 0.18-μm 1.8-V/3.3-V low-voltage CMOS process," *IEEE Trans. Biomed. Circuits Syst.*, vol. 11, no. 5, pp. 1087–1096, Oct. 2017, doi: 10.1109/TBCAS.2017.2713122.

- [8] M.-D. Ker, C.-Y. Lin, and W.-L. Chen, "Stimulus driver for epilepsy seizure suppression with adaptive loading impedance," *J. Neural Eng.*, vol. 8, no. 6, Oct. 2011, Art. no. 066008, doi: 10.1088/1741-2560/8/6/066008.

- [9] P. H. Peckham and J. S. Knutson, "Functional electrical stimulation for neuromuscular applications," *Annu. Rev. Biomed. Eng.*, vol. 7, no. 1, pp. 327–360, Aug. 2005, doi: 10.1146/annurev.bioeng.6.040803.140103.

- [10] G. Palumbo and D. Pappalardo, "Charge pump circuits: An overview on design strategies and topologies," *IEEE Circuits Syst. Mag.*, vol. 10, no. 1, pp. 31–45, Mar. 2010, doi: 10.1109/MCAS.2009.935695.

- [11] S. Ethier, M. Sawan, E. Aboulhamid, and M. El-Gamal, "A ±9 V fully integrated CMOS electrode driver for high-impedance microstimulation," in *Proc. IEEE 52nd Int. Midwest Symp. Circuits Syst.*, Aug. 2009, pp. 192–195, doi: 10.1109/MWSCAS.2009.5236121.

- [12] Y.-C. Huang, M.-D. Ker, and C.-Y. Lin, "Design of negative high voltage generator for biphasic stimulator with SoC integration consideration," in *Proc. IEEE Biomed. Circuits Syst. Conf.*, Nov. 2012, pp. 29–32, doi: 10.1109/BioCAS.2012.6418477.

- [13] G. Palumbo, D. Pappalardo, and M. Gaibotti, "Charge-pump circuits: Power-consumption optimization," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 49, no. 11, pp. 1535–1542, Nov. 2002, doi: 10.1109/TCSI.2002.804544.

- [14] K.-J. Choi and D.-W. Jee, "High-efficiency, 6.6–29 V pulse driver using charge redistribution," *Electron. Lett.*, vol. 54, no. 12, pp. 746–748, Jun. 2018, doi: 10.1049/el.2018.0800.

- [15] A.-H. Alameh and F. Nabki, "A 0.13-μm CMOS dynamically reconfigurable charge pump for electrostatic MEMS actuation," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 25, no. 4, pp. 1261–1270, Apr. 2017, doi: 10.1109/TVLSI.2016.2629439.

- [16] M. A. Khater and D. Peroulis, "Variable-output charge-pump for piezoelectric and electrostatic tunable RF filters," in *Proc. IEEE Int. Symp. Circuits Syst.*, May 2015, pp. 1362–1365, doi: 10.1109/ ISCAS.2015.7168895.

- [17] S.-K. Won *et al.*, "High-voltage wordline generator for low-power program operation in NAND flash memories," in *Proc. IEEE Asian Solid-State Circuits Conf.*, Nov. 2011, pp. 169–172, doi: 10.1109/ASSCC. 2011.6123629.

- [18] Y.-H. Chang, "Variable-conversion-ratio switched-capacitor-voltagemultiplier/divider DC–DC converter," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 8, pp. 1944–1957, Aug. 2011, doi: 10.1109/TCSI.2010.2103171.

- [19] G. Palumbo, D. Pappalardo, and M. Gaibotti, "Charge pump with adaptive stages for non-volatile memories," *IEE Proc.-Circuits, Devices Syst.*, vol. 153, no. 2, pp. 136–142, Apr. 2006, doi: 10.1049/ip-cds:20041235.

- [20] T. Tanzawa, T. Tanaka, K. Takeuchi, and H. Nakamura, "Circuit techniques for a 1.8-V-only NAND flash memory," *IEEE J. Solid-State Circuits*, vol. 37, no. 1, pp. 84–89, Jan. 2002, doi: 10.1109/4.974549.

- [21] T.-Y. Liu *et al.*, "A 130.7-mm<sup>2</sup> 2-layer 32-Gb ReRAM memory device in 24-nm technology," *IEEE J. Solid-State Circuits*, vol. 49, no. 1, pp. 140–153, Jan. 2014, doi: 10.1109/JSSC.2013.2280296.

- [22] A. Patil, S. Bhat, and A. Santra, "An accurate, power and area efficient 13.33x charge pump with wide-range programmability for biomedical sensors," in *Proc. 33rd Int. Conf. VLSI Design 19th Int. Conf. Embedded Syst.* (VLSID), Jan. 2020, pp. 219–224, doi: 10.1109/VLSID49098.2020.00055.

- [23] I. Williams and T. G. Constandinou, "An energy-efficient, dynamic voltage scaling neural stimulator for a proprioceptive prosthesis," *IEEE Trans. Biomed. Circuits Syst.*, vol. 7, no. 2, pp. 129–139, Apr. 2013, doi: 10.1109/TBCAS.2013.2256906.

- [24] J. Gak, M. Miguez, and A. Arnaud, "A programmable charge pump voltage converter for implantable medical devices in a HV technology," in *Proc. IEEE 4th Latin Amer. Symp. Circuits Syst. (LASCAS)*, Feb. 2013, pp. 1–4, doi: 10.1109/LASCAS.2013.6519060.

- [25] Z. Luo, L.-C. Yu, and M.-D. Ker, "An efficient, wide-output, high-voltage charge pump with a stage selection circuit realized in a low-voltage CMOS process," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 9, pp. 3437–3444, Sep. 2019, doi: 10.1109/TCSI.2019.2924581.

- [26] D. Ma and R. Bondade, *Reconfigurable Switched-Capacitor Power Converters*. New York, NY, USA: Springer, 2012, doi: 10.1007/978-1-4614-4187-8.

- [27] S.-P. Lin and M.-D. Ker, "Design of multiple-charge-pump system for implantable biomedical applications," in *Proc. IEEE Biomed. Circuits Syst. Conf.*, Oct. 2018, pp. 1–4, doi: 10.1109/BIOCAS.2018.8584758.

- [28] J.-H. Tsai *et al.*, "A 1 V input, 3 V-to-6 V output, 58%-efficient integrated charge pump with a hybrid topology for area reduction and an improved efficiency by using parasitics," *IEEE J. Solid-State Circuits*, vol. 50, no. 11, pp. 2533–2548, Nov. 2015, doi: 10.1109/JSSC.2015.2465853.

- [29] A. Rashidi, N. Yazdani, and A. M. Sodagar, "Fully-integrated, highefficiency, multi-output charge pump for high-density microstimulators," in *Proc. IEEE Life Sci. Conf. (LSC)*, Oct. 2018, pp. 291–294, doi: 10.1109/LSC.2018.8572121.

Shiau-Pin Lin received the B.S. degree from the Department of Engineering and System Science, National Tsing-Hua University, Hsinchu, Taiwan, in 2016, and the M.S. degree in electrical engineering from the Institute of Electronics, National Chiao-Tung University (NCTU), Hsinchu, in 2018. Her research interest in NCTU is analog circuit design for biomedical applications. Since 2018, she has been with the eMemory Technology Inc., Hsinchu. She has worked on the design of analog and mixed-signal integrated circuits for non-volatile memory applications.

**Ming-Dou Ker** (Fellow, IEEE) received the Ph.D. degree from the Institute of Electronics, National Chiao-Tung University (NCTU), Hsinchu, Taiwan, in 1993.

He is currently the Distinguished Professor with the Institute of Electronics, NCTU, where he is also the Director of Biomedical Electronics Translational Research Center, working on biomedical electronics translational projects. In the technical field, he has authored or coauthored more than 580 technical papers in international journals and conferences.

He has proposed many useful solutions to improve the reliability and quality of integrated circuits, which have been granted with hundreds of U.S. patents. He has served as a member of the Technical Program Committee and the Session Chair of numerous international conferences for many years, including the IEEE Symposium on VLSI Circuits, the IEEE International Symposium on Circuits and Systems (ISCAS), and the IEEE International Solid-State Circuits Conference (ISSCC). He has ever served as an Associate Editor for the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS and the IEEE TRANSACTIONS ON BIOMEDICAL CIRCUITS AND SYSTEMS (TBioCAS), and the Guest Editor of ISCAS2019 Special Issue in TBioCAS. He is currently serving as an Editor of the IEEE TRANSACTIONS ON DEVICE AND MATERIALS RELIABILITY.