US007554159B2

## (12) United States Patent Ker et al.

### (10) Patent No.:

US 7,554,159 B2

(45) **Date of Patent:**

Jun. 30, 2009

#### (54) ELECTROSTATIC DISCHARGE PROTECTION DEVICE AND METHOD OF MANUFACTURING THE SAME

# (76) Inventors: Ming-Dou Ker, Bldg. 51, 195, Chung Hsing Rd., Sec. 4, Chutung, Hsinchu (TW); Tang-Kui Tseng, Bldg. 51, 195, Chung Hsing Rd., Sec. 4, Chutung, Hsinchu (TW); Hsin-Chin Jiang, Bldg. 51, 195, Chung Hsing Rd., Sec. 4, Chutung, Hsinchu (TW); Chyh-Yih Chang, Bldg. 51, 195, Chung Hsing Rd., Sec. 4, Chutung, Hsinchu (TW); Jeng-Jie Peng, Bldg. 51, 195, Chung Hsing Rd., Sec. 4, Chutung, Hsinchu (TW); Jeng-Jie Peng, Bldg. 51, 195, Chung Hsing Rd., Sec. 4, Chutung, Hsinchu

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 11/045,300

(22) Filed: Jan. 31, 2005

#### (65) Prior Publication Data

(TW)

US 2005/0127445 A1 Jun. 16, 2005

#### Related U.S. Application Data

- (62) Division of application No. 10/230,055, filed on Aug. 29, 2002, now Pat. No. 6,882,009.

- (51) Int. Cl. *H01L 23/62* (2006.01)

- (52) **U.S. Cl.** ...... **257/360**; 257/E21.633; 438/133; 361/220

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 4,692,781 | $\mathbf{A}$ |   | 9/1987  | Rountree et al.   |

|-----------|--------------|---|---------|-------------------|

| 5,400,202 | $\mathbf{A}$ |   | 3/1995  | Metz et al.       |

| 5,452,171 | $\mathbf{A}$ |   | 9/1995  | Metz et al.       |

| 5,510,279 | Α            |   | 4/1996  | Chien et al.      |

| 5,517,051 | $\mathbf{A}$ |   | 5/1996  | Chatterjee        |

| 5,572,394 | Α            |   | 11/1996 | Ker et al.        |

| 5,576,574 | Α            | * | 11/1996 | Hong 438/291      |

| 5,631,793 | $\mathbf{A}$ |   | 5/1997  | Ker et al.        |

| 5,646,054 | Α            | * | 7/1997  | Rhee 438/507      |

| 5,646,808 | Α            |   | 7/1997  | Nakayama          |

| 5,698,884 | Α            |   | 12/1997 | Dennen            |

| 5,734,541 | Α            |   | 3/1998  | Iniewski et al.   |

| 5,740,000 | Α            |   | 4/1998  | Stackhouse et al. |

| 5,744,842 | Α            |   | 4/1998  | Ker               |

| 5,747,834 | Α            |   | 5/1998  | Chen et al.       |

| 5,763,919 | Α            |   | 6/1998  | Lin               |

| 5,838,146 | Α            |   | 11/1998 | Singer            |

| 5,982,600 | A            | * | 11/1999 | Cheng 361/111     |

| 6,147,383 | $\mathbf{A}$ |   | 11/2000 | Kuroda            |

|           |              |   |         |                   |

#### (Continued)

Primary Examiner—David Vu

#### (57) ABSTRACT

An electrostatic discharge protection device that includes a semiconductor substrate of a first dopant type, at least one source/drain pair of a second dopant type formed in the substrate, wherein the source/drain pair is separated to define a channel region therebetween, a lightly-doped region of the first dopant type defined between the source/drain pair and including at least a portion of the channel region, a gate dielectric layer formed over the substrate, and a gate formed over the gate dielectric layer and above the channel region.

#### 24 Claims, 14 Drawing Sheets

## US 7,554,159 B2 Page 2

| U.S. PATENT          | DOCUMENTS            |                     | 31 7/2002 Hu et al.<br>32 10/2002 Shenoy |                          |

|----------------------|----------------------|---------------------|------------------------------------------|--------------------------|

| 6,147,538 A 11/2000  | Andresen et al.      | 6,528,850 B1        |                                          |                          |

| 6,211,023 B1* 4/2001 | Yeh et al 438/299    | 6,546,522 B1*       | 4/2003                                   | Chen 716/2               |

| 6,239,472 B1 5/2001  | Shenoy               | 6,671,153 B1        |                                          |                          |

| 6,256,184 B1 7/2001  | Gauthier, Jr. et al. | 6,822,297 B2 *      | 11/2004                                  | Nandakumar et al 257/356 |

| 6,362,062 B1* 3/2002 | Nandakumar 438/303   | * cited by examiner |                                          |                          |

FIG. 3

FIG. 5

FIG. 6

FLG. 8

98 96 94 92 94 96 98

p+ s71 N+ p+ rsub

P- Jell

P- Substrate

Rsub

FIG. 10

FIG.11

FIG. 12

FIG. 13

FIG. 14

FIG. 15

FIG. 16

FIG. 17E

F19.21

FIG. 22

#### ELECTROSTATIC DISCHARGE PROTECTION DEVICE AND METHOD OF MANUFACTURING THE SAME

#### RELATED APPLICATION

This application is a division of application Ser. No. 10/230,055, filed Aug. 29, 2002, now U.S. Pat. No. 6,882,009 which is related to U.S. patent application No. 10/230,287, CIRCUIT WITH ACTIVE DEVICE," filed on Aug. 29, 2002. The entire contents of these related applications are incorporated herein by reference.

#### FIELD OF THE INVENTION

This invention pertains in general to a semiconductor device, and, more particularly, to an electrostatic discharge protection device and method for manufacturing the same.

#### BACKGROUND

A semiconductor integrated circuit ("IC") is generally susceptible to an electrostatic discharge ("ESD") event, which may damage or destroy the IC. An ESD event refers to a 25 phenomenon of electrical discharge of a current (positive or negative) for a short duration during which a large amount of current is provided to the IC. The high current may be built-up from a variety of sources, such as the human body.

Advanced MOSFET transistors, such as those manufac- 30 tured using sub-quarter-micron processes, have traditionally required certain processes such as silicide processes, lightlydoped drain (LDD) structures, and thin gate dielectric layers. As a result, the advanced MOSFET transistors are particularly susceptible to an ESD event.

Conventional ESD protection devices are implemented using bipolar junction transistors ("BJTs"), gate grounded NMOS ("GGNMOS") transistors, silicon controlled rectifiers ("SCR"), and silicon junction diodes, to name a few examples. Conventional NMOS devices have a threshold 40 voltage of about 0.6V adjustable by changing the concentration of the p-type implant in the channel regions. These devices disadvantageously have slow turn-on speed and therefore poor ESD robustness.

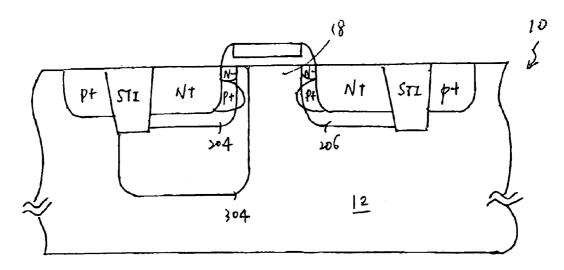

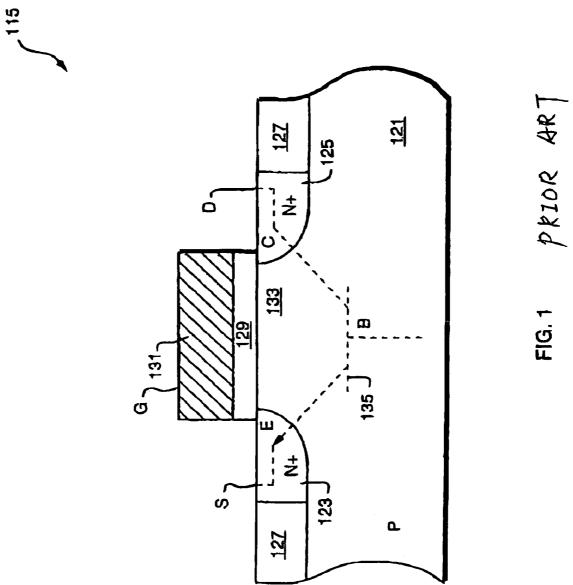

An example of a conventional ESD protection device in 45 input/output (I/O) pad design is shown in FIGS. 1 and 2, reproduction of FIGS. 1B and 2, respectively, of U.S. Pat. No. 6,256,184 to Gauthier, entitled "Method and Apparatus for Providing Electrostatic Discharge Protection." Gauthier describes an ESD protection structure that includes low 50 threshold and zero threshold FETs to conduct transient ESD currents during an ESD event. Referring to FIG. 1, an NMOS 115 for ESD protection device has a low threshold voltage, and, during normal operation, is required to connect to a negative voltage source 201 at the gate to turn off channel 55 current. Referring to FIG. 2, an ESD protection circuit 101 comprises a source diode 203 to minimize leakage current during normal IC operation.

A conventional NMOS device is generally formed in a p-well, and is manufactured by first providing a substrate and 60 forming shallow trench isolations ("STIs") or local oxidation silicon ("LOCOS"). The steps of p-well implantation, antipunchthrough implantation, and channel implantation then follow. In general, the p-well has the largest implant depth and the lowest doped concentration, and the channel region has 65 the smallest implant depth and the highest doped concentration. The steps of n-well implantation, anti-punchthrough

implantation, and channel implantation follow then. A gate oxide layer is then formed over the substrate, and a gate is formed over the gate oxide layer. Sidewall spacers are formed contiguous with the gate. Finally, source and drain regions are formed to finish the fabrication of the NMOS in a p-well.

#### SUMMARY OF THE INVENTION

In accordance with the invention, there is provided an entitled "ELECTROSTATIC DISCHARGE PROTECTION 10 electrostatic discharge protection device that includes a semiconductor substrate of a first dopant type, at least one source/ drain pair of a second dopant type formed in the substrate, wherein the source/drain pair is separated to define a channel region therebetween, a lightly-doped region of the first 15 dopant type defined between the source/drain pair and including at least a portion of the channel region, a gate dielectric layer formed over the substrate, and a gate formed over the gate dielectric layer and above the channel region.

> In one aspect, the device includes a pocket region of the 20 first dopant type formed adjacent one of the source/drain pair and under the gate.

In another aspect, the device includes an anti-punchthrough region of the first dopant type formed under the channel region and extending between the source/drain pair.

Also in accordance with the present invention, there is provided an electrostatic discharge protection device that includes a semiconductor substrate of a first dopant type, a well region of the first dopant type formed in the substrate, a source region of a second dopant type formed in the well region, a drain region pair of a second dopant type formed in the well region and spaced apart from the source region, a channel region formed between the source and drain regions, a lightly doped region of the first dopant type defined between the source and drain regions, and a gate formed on the sub-35 strate and over the channel region.

Further in accordance with the present invention, there is provided an electrostatic discharge protection device that includes a semiconductor substrate of a first dopant type, at least one source/drain pair of a second dopant type formed in the substrate, wherein the source/drain pair is separated to define a channel region therebetween, a lightly doped region of the second dopant type defined between the source/drain pair and including at least a portion of the channel region, a gate dielectric layer formed over the substrate, and a gate formed over the gate dielectric layer and above the channel region.

In accordance with the present invention, there is provided a method of manufacturing an electrostatic discharge protection device that includes providing a semiconductor substrate of a first dopant type having a surface, masking an area of the surface of the semiconductor substrate, implanting the semiconductor substrate with a dopant of a second dopant type, implanting the semiconductor substrate with a dopant of the first dopant type, unmasking the area of the surface of the semiconductor substrate, forming at least one source/drain pair of a second dopant type in the area, wherein the source/ drain pair is separated to define a channel region therebetween, and forming a gate on the substrate and over the channel region.

In one aspect, in masking an area of the surface, the method includes applying a dummy layer over the area of the surface.

In another aspect, prior to masking an area of the surface, the method includes forming a deep well region of the second dopant type in the substrate.

Also in accordance with the present invention, there is provided a method of manufacturing an electrostatic discharge protection device that includes providing a semicon-

ductor substrate of a first dopant type having a surface, forming a well region of the first dopant type in the semiconductor substrate, masking an area of the surface disposed on the well region of the first dopant type, implanting the semiconductor substrate with a dopant of a second dopant type, implanting the semiconductor substrate with a dopant of the first dopant type, unmasking the area of the surface disposed on the well region of the first dopant type, forming at least one source/drain pair of a second dopant type in the area, wherein the source/drain pair is separated to define a channel region therebetween; and forming a gate on the substrate and over the channel region.

Further in accordance with the present invention, there is provided a method of manufacturing an electrostatic discharge protection device that includes providing a semiconductor substrate of a first dopant type having a surface, masking a first area of the surface of the semiconductor substrate, implanting the semiconductor substrate with a dopant of a second dopant type, implanting the semiconductor substrate with a dopant of the first dopant type, unmasking the first area of the surface of the semiconductor substrate, implanting a second area in the first area with a dopant of the second dopant type, forming at least one source/drain pair of the second dopant type in the first area, wherein the source/drain pair is separated by the second area, and forming a gate on the 25 substrate and over the second area.

Additional objects and advantages of the invention will be set forth in part in the description which follows, and in part will be obvious from the description, or may be learned by practice of the invention. The objects and advantages of the invention will be realized and attained by means of the elements and combinations particularly pointed out in the appended claims.

It is to be understood that both the foregoing general description and the following detailed description are exemplary and explanatory only and are not restrictive of the invention, as claimed.

The accompanying drawings, which are incorporated in and constitute a part of this specification, illustrate several embodiments of the invention and together with the description, serve to explain the principles of the invention.

#### BRIEF DESCRIPTION OF THE DRAWINGS

- FIG. 1 is a cross-sectional view of a conventional low <sup>45</sup> threshold voltage ESD protection device;

- FIG. 2 is a schematic diagram of a conventional low threshold voltage ESD protection circuit;

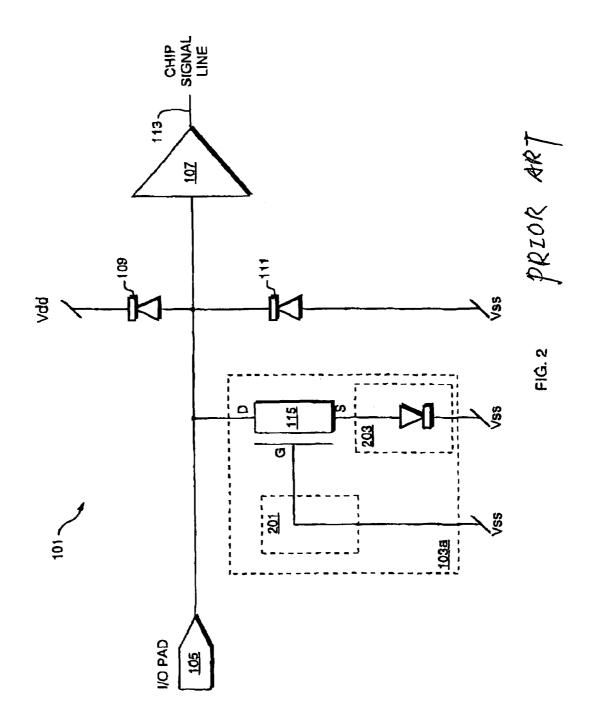

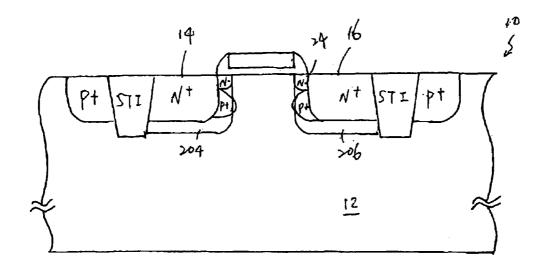

- FIG. 3 is a cross-sectional view of an ESD protection device in accordance with one embodiment of the present invention;

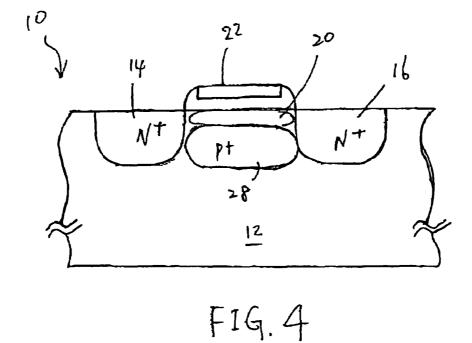

- FIG. 4 is a cross-sectional view of an ESD protection device in accordance with one embodiment of the present invention;

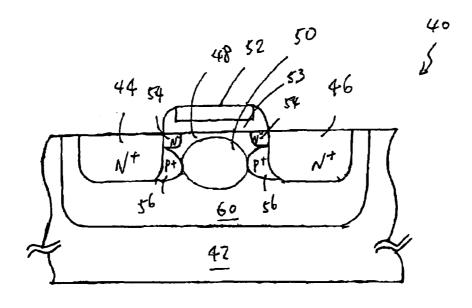

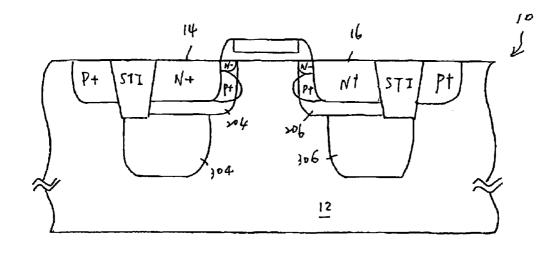

- FIG. **5** is a cross-sectional view of an ESD protection device in accordance with another embodiment of the present invention:

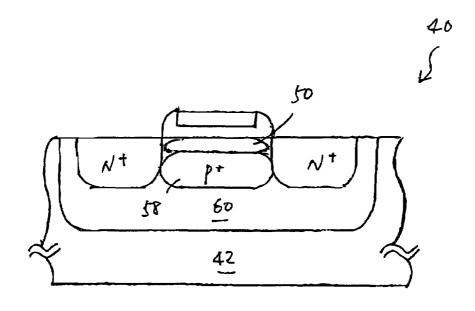

- FIG.  $\bf 6$  is a cross-sectional view of an ESD protection device in accordance with one embodiment of the present  $_{60}$  invention;

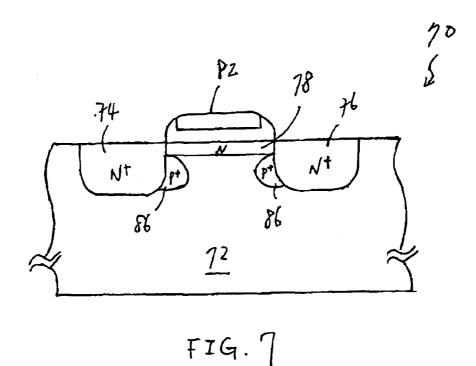

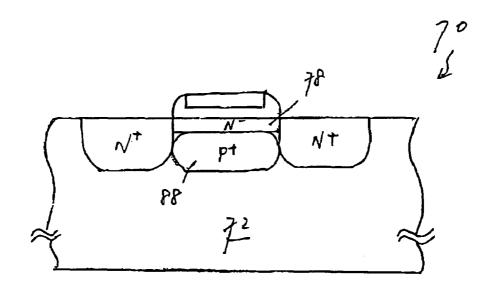

- FIG. 7 is a cross-sectional view of an ESD protection device in accordance with still another embodiment of the present invention;

- FIG. **8** is a cross-sectional view of an ESD protection 65 device in accordance with one embodiment of the present invention;

4

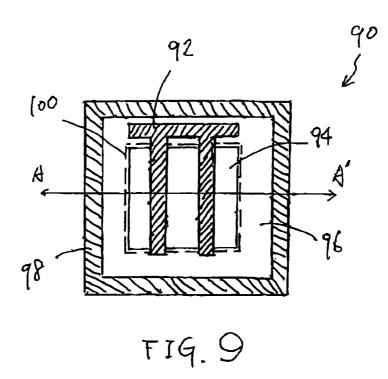

- FIG. 9 is a layout of an ESD protection device in accordance with one embodiment of the present invention;

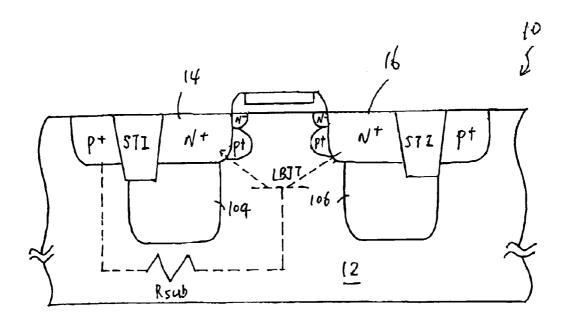

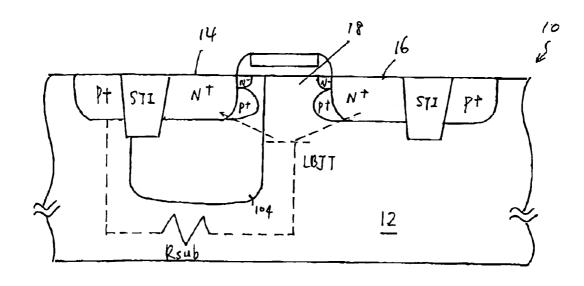

- FIG. 10 is a cross-sectional view of the ESD protection device shown in FIG. 9;

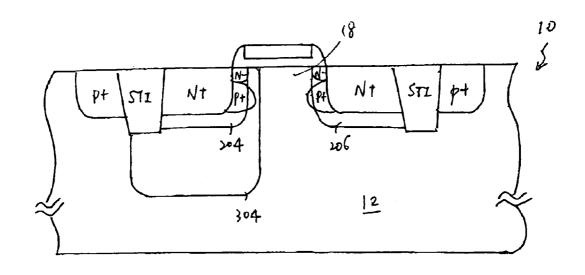

- FIG. 11 is a cross-sectional view of an ESD protection device in accordance with one embodiment of the present invention;

- FIG. 12 is a cross-sectional view of an ESD protection device in accordance with one embodiment of the present invention:

- FIG. 13 is a cross-sectional view of an ESD protection device in accordance with one embodiment of the present invention:

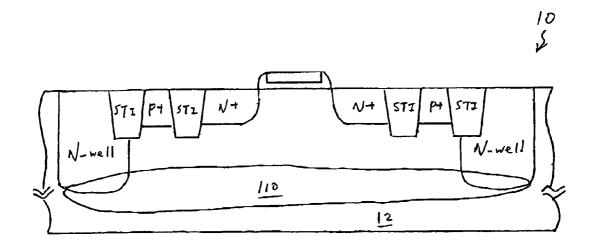

- FIG. 14 is a cross-sectional view of an ESD protection device in accordance with one embodiment of the present invention:

- FIG. 15 is a cross-sectional view of an ESD protection device in accordance with one embodiment of the present invention;

- FIG. **16** is a cross-sectional view of an ESD protection device in accordance with one embodiment of the present invention;

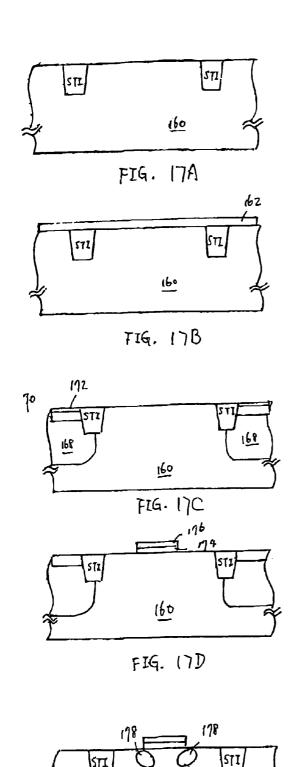

- FIGS. 17A-17H show a method of manufacturing an ESD protection device in accordance with one embodiment of the present invention;

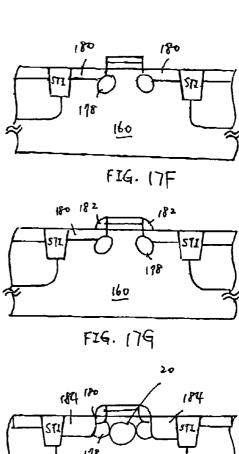

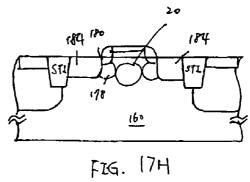

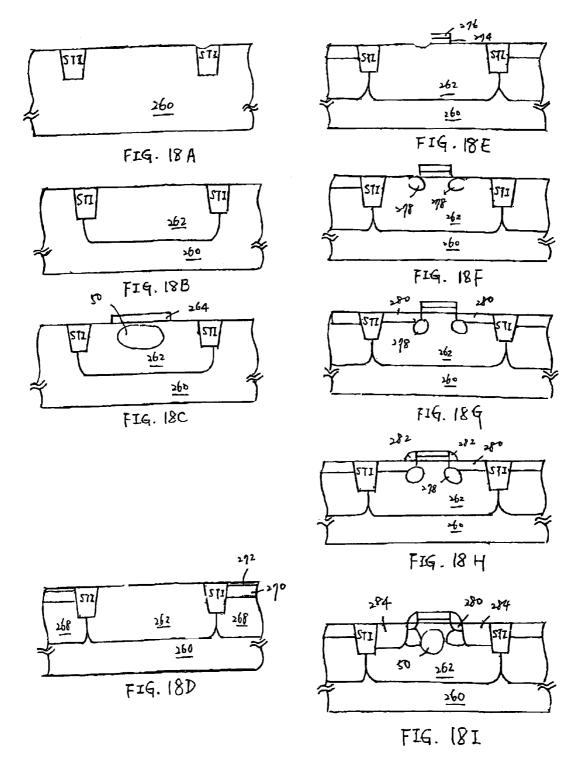

- FIGS. **18**A-**18**I show a method of manufacturing an ESD protection device in accordance with another embodiment of the present invention;

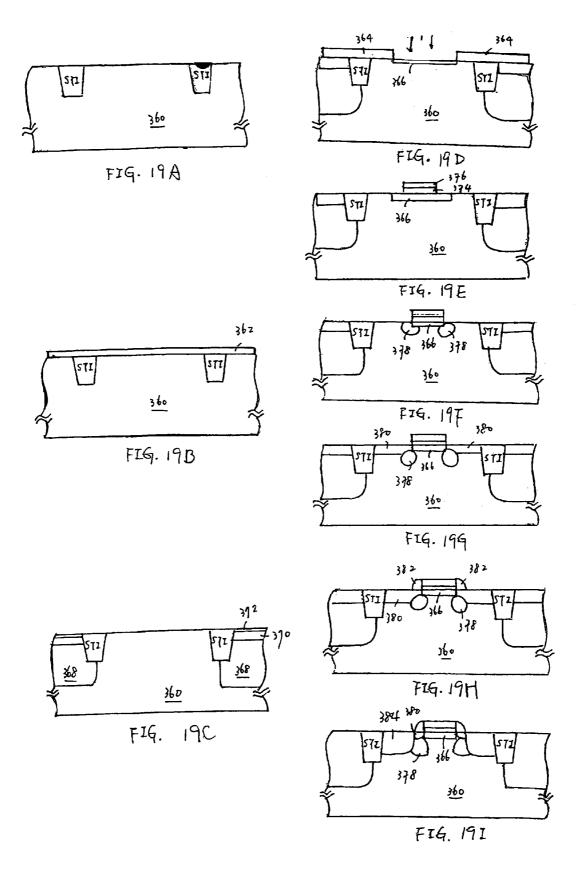

- FIGS. 19A-19I show a method of manufacturing an ESD protection device in accordance with still another embodiment of the present invention;

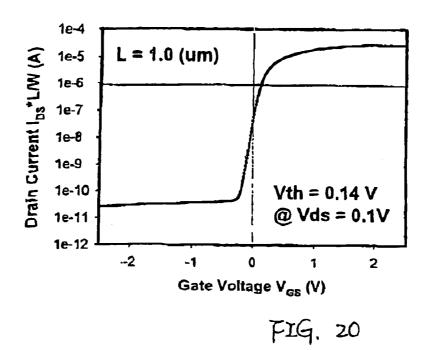

- FIG. 20 is a plot showing the relationship between a drain current and a gate voltage of the ESD protection device shown in FIG. 3;

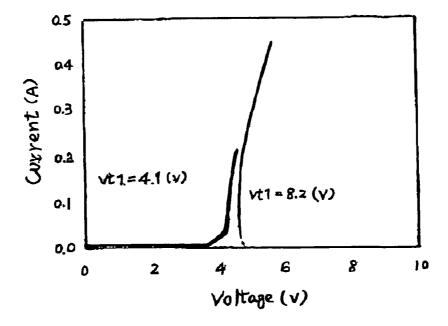

- FIG. 21 is a current-voltage curve of the ESD protection device shown in FIG. 3; and

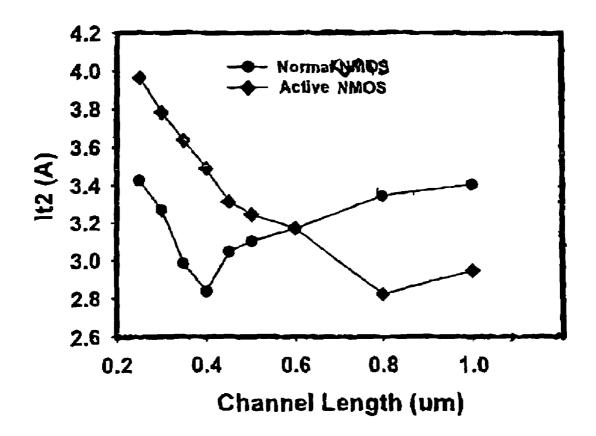

- FIG. 22 is a plot showing a comparison in characteristics between the ESD protection device shown in FIG. 3 and a conventional ESD protection device.

- FIG. 23 is a cross-sectional view of an ESD protection device of FIG. 5 modified in accordance with another embodiment.

#### DESCRIPTION OF THE EMBODIMENTS

Reference will now be made in detail to the present embodiments of the invention, examples of which are illustrated in the accompanying drawings. Wherever possible, the same reference numbers will be used throughout the drawings to refer to the same or like parts.

FIG. 3 shows a cross-sectional view of an ESD protection device 10 in accordance with one embodiment of the present invention. Referring to FIG. 3, ESD protection device 10 includes a semiconductor substrate 12 of a first dopant type, at least one source/drain pair of a second dopant type formed in the substrate 12, in which the source/drain regions 14 and 16 of each source/drain pair are spaced apart to define a channel region 18 therebetween, and a lightly doped region 20 of the first dopant type formed between the source/drain pair and including at least a portion of the channel region 18. In one embodiment, the lightly doped region 20 may include a full channel region 18. The lightly doped region 20 has a dopant concentration lower than the substrate 12. Besides, one skilled in the art would understand that which of the regions 14 and 16 is labeled the source or drain is unimportant for purposes of the present invention.

The ESD protection device 10 also includes a gate dielectric layer 21 disposed over the substrate 12, and a gate 22 formed over the gate dielectric layer 21. The gate 22 of the ESD protection device 10 includes spacers 30 of silicon oxide, polyimide or the like. In one embodiment, the ESD protection device 10 includes lightly-doped drain (LDD) regions 24 to reduce hot electron effects. In one embodiment, the ESD protection device 10 includes pocket regions 26 to reduce the influence of short transistor gate length over transistor properties such as the threshold voltage.

The ESD protection device 10 shown in FIG. 3 is an NMOS device fabricated on a substrate 12 that is lightly doped with a first type of impurities, i.e., p-type impurities. However, one skilled in the art would understand that PMOS devices are fabricated in a similar manner by substituting the p-type 15 impurities with n-type impurities. In addition, unlike conventional NMOS devices, the ESD protection device 10 is not formed in a p-well. In fabricating the device 10, a dummy layer (not shown) is used to mask the ESD protection device 10 from ion implants that would otherwise be necessary for 20 conventional NMOS devices. Since the doped concentration of the channel region 18 is lower than that of the channel region of conventional NMOS devices, the threshold voltage of the ESD protection device 10 is reduced.

FIG. 4 shows a cross-sectional view of the ESD protection 25 device 10 consistent with another embodiment of the invention. Referring to FIG. 4, the ESD protection device 10 includes an anti-punchthrough region 28 of a p-type dopant to reduce leakage current. The anti-punchthrough region 28 is formed below the lightly doped region 20. In one embodiment, the anti-punchthrough region 28 is formed contiguous with one or all of the source and drain regions 14 and 16, and the lightly doped region 20.

FIG. 5 shows a cross-sectional view of an ESD protection device 40 consistent with another embodiment of the present 35 invention. Referring to FIG. 5, the ESD protection device 40 includes a semiconductor substrate 42 of a first dopant type, a well region 60 of the first dopant type formed in the substrate 42, at least one source/drain pair of a second dopant type formed in the well region 60, wherein a source region 44 and 40 a drain region 46 of a source/drain pair are spaced apart to define a channel region 48 therebetween, and a lightly doped region 50 of the first dopant type formed between the source and drain regions 44 and 46. In one embodiment, the lightly doped region 50 includes at least a portion of the channel 45 region 48.

The ESD protection device 40 also includes a gate dielectric layer 53 formed over the substrate 42 and the channel region 48, and a gate 52 formed over the gate dielectric layer **53**. The ESD protection device **40** is formed in a p-well **60**, but 50 has not undergone any channel or anti-punchthrough implants. In fabricating the ESD protection device 40, a dummy layer is used to mask the ESD protection device 40 from the channel and anti-punchthrough implants that would otherwise be necessary for conventional NMOS devices. As a 55 result, the lightly doped region 50, which may include the channel region 48, is formed between the source and drain regions 44 and 46. Since the doped concentration of the channel region 48 is lower than that of the conventional NMOS devices, the threshold voltage of the ESD protection 60 device 40 is reduced. Since the p-well region 60 has a higher doped concentration than the substrate 42, the ESD protection device 40 has a higher threshold voltage than the ESD protection device 10 shown in FIG. 3, but still has a lower threshold voltage than conventional devices.

Referring again to FIG. 5, in one embodiment, the ESD protection device 40 includes LDD regions 54 to reduce hot

6

electron effects. In another embodiment, the ESD protection device 40 includes pocket regions 56 to reduce the influence of short transistor gate length on transistor properties such as the threshold voltage. In one embodiment, the source and drain regions 44 and 46 are doped with an n-type impurity, the LDD regions 54 are doped with an n-type impurity, and the pocket regions 56 are doped with a p-type impurity.

FIG. 6 is a cross-sectional view of the ESD protection device 40 consistent with another embodiment of the invention. Referring to FIG. 6, the ESD protection device 40 includes an anti-punchthrough region 58 to reduce leakage current. In one embodiment, the anti-punchthrough region 58 is-doped with a p-type impurity.

FIG. 7 is a cross-sectional view of an ESD protection device 70 consistent with still another embodiment of the present invention. Referring to FIG. 7, the ESD protection device 70 includes a semiconductor substrate 72 of a first dopant type, at least one source/drain pair of a second dopant type formed in the substrate 72, a lightly doped channel region 78 of the second dopant type extending between a source region 74 and a drain region 76 of a source/drain pair, and a gate 82 formed on the substrate 72 and over the channel region 78.

In fabricating the ESD protection device **70**, a dummy layer is used to mask the ESD protection device **70** from a p-well, anti-punchthrough, and channel implants that would be otherwise necessary for general NMOS devices. In contrast to the heavily doped p-type channels of conventional NMOS devices, the channel region **78** of the ESD protection device **70** is lightly doped with an n-type impurity. The lightly doped n-type channel region **78** turns the threshold voltage of the NMOS protection device **70** into a negative value so that the ESD protection device **70** is kept conductive during normal operation.

In one embodiment, the ESD protection device 70 includes pocket regions 86 to reduce the influence of short transistor gate length over transistor properties such as the threshold voltage. In one embodiment, the source and drain regions 74 and 76 are doped with an n-type impurity and the pocket regions 86 are doped with a p-type impurity.

FIG. 8 is a cross-sectional view of the ESD protection device 70 consistent with another embodiment of the invention. Referring to FIG. 8, the ESD protection device 70 includes an anti-punchthrough region 88 to reduce leakage current.

FIG. 9 shows a layout of a finger-type NMOS ESD protection device 90 in accordance with yet another embodiment of the present invention. The ESD protection device 90 includes a common gate region 92, a common source or drain region 94 of an n-type dopant, a dielectric region 96 such as a LOCOS or trench isolation, and a p-type dopant region 98. The finger-type device 90, similar to the ESD protection devices 10, 40 and 70 in FIG. 3, FIG. 5 and FIG. 7, respectively, has a lightly doped region formed under a dummy layer 100 (shown by dotted line) to reduce a threshold voltage.

FIG. 10 is a cross-sectional view of the ESD protection device 90 shown in FIG. 9 along the AA' direction. Referring to FIG. 10, the ESD protection device 90 includes at least one source/drain pair 94 and parasitic lateral bipolar junction transistor ("LBJTs") (not numbered). In operation, during an ESD event, the ESD protection device 90 achieves a drain-induced barrier lowering ("DIBL") effect, resulting in a larger substrate current  $I_{sub}$  such that the LBJTs can quickly conduct an ESD current to ground.

FIG. 11 is a cross-sectional view of the ESD protection device 10 consistent with another embodiment of the invention. Referring to FIG. 11, the ESD protection device 10

includes a first diffused region 104 and a second diffused region 106, both of n-type dopant, formed under the source region 14 and the drain region 16, respectively. The first diffused region 104 has a larger implant depth than the source region 14, which increases the base, or substrate, resistance  $R_{sub}$  of the ESD protection device 10. The second diffused region 106 has a larger implant depth than the drain region 16 and functions to direct an ESD current deep into the substrate 12 to increase heat dissipation of the ESD protection device 10. Therefore, the first diffused region 104 and the second diffused region 106 both contribute to the ESD robustness of the ESD protection device 10. One skilled in the art would understand that the first and second diffused regions 104 and 106 may be likewise incorporated into the ESD protection device 40 of FIG. 5, device 70 of FIG. 7, and device 90 of FIG. 15

FIG. 12 shows a cross-sectional view of the ESD protection device 10 consistent with still another embodiment of the invention. Referring to FIG. 12, the first diffused region 104 formed under the source region 14 extends into a portion of 20 the channel region 18. The first diffused region 104 extending into the channel region 18 prevents the parasitic LBJT (shown by dotted line) from current crowding and increase the beta value, or the gain, of the parasitic LBJT. In one embodiment, the second diffused region 106 shown in FIG. 11 formed 25 under the drain region 16 extends into a portion of the channel region 18. One skilled in the art would understand that the first diffused region 104 or the second diffused region 106 extending into the channel region 18 may be likewise incorporated into the ESD protection device 40 of FIG. 5, device 70 of FIG. 30 7, and device 90 of FIG. 9.

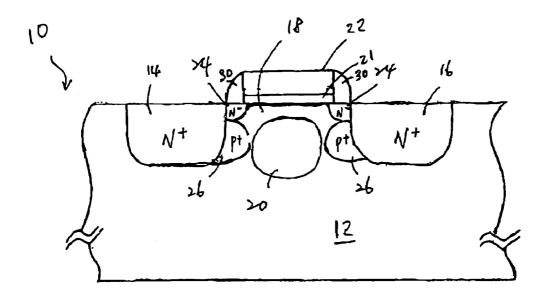

FIG. 13 shows a cross-sectional view of the ESD device 10 consistent with yet another embodiment of the invention. Referring to FIG. 13, the ESD protection device 10 includes a third diffused region 204 and a fourth diffused region 206, 35 both of which are doped with an n-type dopant, formed under the source region 14 and the drain region 16, respectively, and extending into a portion of the LDD regions 24. The third diffused region 204 or the fourth diffused region 206 has a smaller implant depth than the first diffused region 104 or the 40 second diffused region 106. Both the third and fourth diffused regions 204 and 206 function to improve the ESD robustness of the ESD protection device 10. The third diffused region 204 or the fourth diffused region 206 may be likewise incorporated into the ESD protection device 40 of FIG. 5, device 70 45 of FIG. 7, and device 90 of FIG. 9. For example, adding third diffused region 204 and fourth diffused region 206 to the embodiment depicted in FIG. 5, produces an ESD protection device as depicted in FIG. 23.

FIG. 14 shows a cross-sectional view of the ESD protection 50 device 10 consistent with yet another embodiment of the invention. Referring to FIG. 14, the ESD protection device 10 includes a fifth diffused region 304 and a sixth diffused region 306, both doped with an n-type dopant, formed under the third and fourth diffused regions 204 and 206, respectively. The 55 fifth and sixth diffused regions 304 and 306 have the same functions as the first and second diffused regions 104 and 106 shown in FIG. 11, and are applicable to the ESD protection device 40 of FIG. 5, device 70 of FIG. 7, and device 90 of FIG. 9

FIG. 15 shows a cross-sectional view of the ESD protection device 10 consistent with yet another embodiment of the invention. Referring to FIG. 15, the fifth diffused region 304 formed under the third diffused region 204 extends into a portion of the channel region 18. The fifth diffused region 304 has the same functions as the first diffused region 104 shown in FIG. 12. In one embodiment, the sixth diffused region 306

8

shown in FIG. 14 extends into a portion of the channel region 18. The fifth diffused region 304 or the sixth diffused region 306 extending into the channel region 18 is applicable to the ESD protection device 40 of FIG. 5, device 70 of FIG. 7, and device 90 of FIG. 9.

FIG. 16 shows a cross-sectional view of the ESD protection device 10 consistent yet another embodiment of the invention. Referring to FIG. 16, the ESD protection device 10 includes a deep N-well region 110 to reduce leakage current. In one embodiment, the deep N-well region 110 has an implant depth of 2 to 5  $\mu m$  (micron). The deep N-well 110 is formed after the semiconductor substrate 12 is prepared. One skilled in the art would understand that the deep N-well 110 is also applicable to the ESD protection device 40 of FIG. 5, device 70 of FIG. 7, and device 90 of FIG. 9.

In addition, the present invention also provides methods for manufacturing ESD protection devices. In particular, FIGS. 17A-17H show the steps of a method in accordance with one embodiment of the present invention for manufacturing the ESD protection device 10. Referring to FIG. 17A, the manufacturing method of the present invention begins with the formation of STIs or LOCOS in a p-type substrate 160. In one embodiment, a deep N-well (not shown) is formed prior to the formation of the STIs and LOCOS. Referring to FIG. 17B, a photoresist layer 162 is provided over the substrate 160, and then patterned and defined. The patterned and defined photoresist layer 162 serves as a dummy, or sacrificial, layer to mask the portion of the substrate 160 covered by the photoresist 162 from subsequent implantation steps.

The steps of well implantation, anti-punchthrough implantation, and channel implantation are then performed. Referring to FIG. 17C, in areas not masked by the dummy layer, an n-well 168, an anti-punchthrough region 170, and a channel 172 are formed. The lightly doped p-type region 20 shown in FIG. 3 will be later defined to achieve the desired property of low threshold voltage. The photoresist 162 is then removed.

Conventional NMOS manufacturing steps may now follow. Referring to FIG. 17D, a gate oxide layer 174 is formed over the substrate 160 and a gate conductive layer 176, such as polysilicon, is deposited over the gate oxide layer 174. The gate oxide layer 174 and gate conductive layer 176 are patterned and etched.

Referring to FIG. 17E, p-type pocket regions 178 may be optionally formed using an angled implant process. Referring to FIG. 17F, n-type LDD regions 180 are optionally formed. Referring to FIG. 17G, sidewall spacers 182 are formed contiguous with the patterned and etched gate oxide layer 174 and gate conductive layer 176. Referring to FIG. 17H, source and drain regions 184 are formed and the lightly doped p-type region 20 is defined between the source/drain pair 184. The manufacturing method of the present invention is therefore fully compatible with conventional CMOS processes.

Although not particularly described, the method of the present invention may optionally include forming the antipunchrough region 28 shown in FIG. 4, the first or second diffused region 104 or 106 shown in FIG. 11, the third or fourth diffused region 204 or 206 shown in FIG. 13, or the fifth or sixth diffused region 304 or 306 shown in FIG. 14 by conventional CMOS processes.

FIGS. **18**A-**18**I show the steps of a method for manufacturing the ESD protection device **40**. Referring to FIG. **18**A, the manufacturing method of the invention begins by providing a p-type substrate **260** and forming STIs or LOCOS in the substrate **260**. In one embodiment, after providing the substrate **260**, a deep N-well (not shown) is formed in the substrate **260**. Referring to FIG. **18**B, a p-well region **262** is formed in the substrate **260** using conventional process.

Referring to FIG. 18C, a photoresist layer 264 which serves as a dummy layer is deposited over the substrate 260. The photoresist layer 264 is then patterned and defined, and functions to mask the portion of the substrate 260 covered by the photoresist **264** from the subsequent implantation steps. Following the steps of anti-punchthrough implantation, and the channel implantation, the remaining steps shown in FIGS. 18D to 18I are similar to those of FIGS. 17C to 17H. The lightly doped p-type region 50 will be later defined to achieve the desired property of low threshold voltage.

As shown in FIG. 18D, an n-well 268, anti-punchthrough region 270, and a channel 272 are formed in the substrate 260 through n-well implantation, anti-punchthrough implantation, and channel implantation steps. The patterned and defined photoresist layer 264 is removed. Referring to 18E, a 15 gate oxide layer 274 is formed over the substrate 260 and a gate conductive layer 276 is formed over the gate oxide layer 274. The layers 274 and 276 are later patterned and etched.

As shown in FIG. 18F, p-type pocket regions 278 may be optionally formed using angled implantation steps. Referring 20 to FIG. 18G, n-type LDD regions 280 may also be optionally formed. In FIG. 18H, sidewall spacers 282 are formed contiguous with the etched gate oxide layer 274 and gate conductive layer 276. The source and drain regions 284 are then formed and the lightly-doped p-type region 50 is defined 25 between the source/drain pair 284 as shown in FIG. 18I.

FIGS. 19A-19I show the steps of a method in accordance with one embodiment of the present invention for manufacturing the ESD protection device 70. Referring to FIG. 19A, the method of the invention begins with providing a p-type 30 substrate 360 and forming STIs or a LOCOS in the substrate **360**. In one embodiment, a deep N-well (not shown) is formed prior to the formation of the STIs or LOCOS. Referring to FIG. 19B, a first photoresist layer 362 is provided over the substrate 360, and then patterned and defined. The patterned 35 and defined first photoresist layer 362 serves as a dummy layer to mask the portion of the substrate 360 covered by the photoresist 362 from subsequent implantation steps.

The steps of n-well implantation, anti-punchthrough implantation, and channel implantation are then performed. 40 the well region of the first dopant type. Referring to FIG. 19C, an n-well 368, an anti-punchthrough region 370, and a channel 372 are formed. The first photoresist layer 362 is then removed.

Referring to FIG. 19D, a second photoresist 364 is provided over the substrate 360, and is then patterned and 45 defined. With the second photoresist 364 acting as a mask, an n-type impurity is implanted into the substrate 360 to form a lightly-doped n-type region 366. The lightly-doped n-type region 366, like the lightly-doped p-type region 20 of FIG. 3 or region 50 of FIG. 5, contributes to the desired property of 50 low threshold voltage. Subsequent to the step of FIG. 19D, the remaining steps shown in FIGS. 19E to 19I are the same as the steps shown and described in FIGS. 17D to 17H.

FIG. 20 is a plot showing the relationship between the drain current  $I_{ds}$  and the gate voltage  $V_{gs}$  of the ESD protection 55 is formed to be contiguous with the source region and the device 10 shown in FIG. 3. Referring to FIG. 20, when the gate voltage is at 0.14V, the drain current is at 1 uA. Accordingly, the threshold voltage of the device 10 of the present invention, 0.14V, is much lower than 0.6V, the threshold voltage of conventional MOSFETs.

FIG. 21 is current-voltage curve of the ESD protection device 10 shown in FIG. 3. As shown in FIG. 21, the breakdown voltage (Vt1) of the conventional MOSFETs is about 8.2V, while the breakdown voltage of the device 10 of the present invention is 4.2V. As a result, the ESD protection 65 device 10 of the present invention turns on faster than conventional MOSFETs. The lower Vt1 value of the ESD pro10

tection device 10 is due to the DIBL effect, which results from a large substrate current to enable quicker conduction by the parasitic BJTs. In normal operations, a negative voltage source of about -0.4V may be applied to the gate of the ESD protection device 10 so as to prevent leakage current.

FIG. 22 is a plot comparing the threshold current values of the ESD protection device 10 show in FIG. 3 and a conventional device. As shown in FIG. 22, when the channel length is less than  $0.6\Phi m$ , the ESD protection device 10 is more robust for ESD protection than conventional MOSFETs by an average of approximately 20%.

Other embodiments of the invention will be apparent to those skilled in the art from consideration of the specification and practice of the invention disclosed herein. It is intended that the specification and examples be considered as exemplary only, with a true scope and spirit of the invention being indicated by the following claims.

What is claimed is:

1. A method, comprising:

providing a semiconductor substrate of a first dopant type: forming a well region of the first dopant type in the substrate;

forming a lightly doped region of the first dopant type in the well region;

forming at least one source/drain pair of a second dopant type in the substrate, wherein a source region of the source/drain pair is separated from a drain region of the source/drain pair by a channel region;

forming a gate on the substrate and over both the channel region and the lightly doped region so that the lightly doped region is directly below a central portion of the

forming lightly doped drain (LDD) regions of the second dopant type adjacent to the gate;

forming a first diffused region of the second dopant type under the drain region of the source/drain pair; and

forming a second diffused region of the second dopant type under the source region of the source/drain pair.

- 2. The method of claim 1, wherein the gate is formed over

- 3. The method of claim 1, further comprising forming a sidewall spacer adjacent to the gate and over the LDD regions.

- 4. The method of claim 1, wherein the first dopant type comprises a p-type dopant, and wherein the second dopant type comprises an n-type dopant.

- 5. The method of claim 1, wherein the lightly doped region is formed to be contiguous with both the source region and the drain region.

- 6. The method of claim 1, wherein the first and second diffused regions extend into a portion of the LDD regions.

- 7. The method of claim 6, further comprising forming pocket regions of the first dopant type adjacent to the source and drain regions and below the LDD regions.

- 8. The method of claim 7, wherein the lightly doped region drain region through the pocket regions.

9. A method, comprising:

providing a semiconductor substrate of a first dopant type; forming at least one source/drain pair of a second dopant type in the substrate, wherein a source region of the source/drain pair is separated from a drain region of the source/drain pair by a channel region;

forming a gate on the substrate and over the channel region; forming lightly doped drain (LDD) regions of the second dopant type adjacent to the gate;

forming a first diffused region of the second dopant type under the drain region of the source/drain pair;

- forming a second diffused region of the second dopant type under the source region of the source/drain pair; and forming a third diffused region of the second dopant type under the first diffused region.

- **10**. The method of claim **9**, further comprising forming a 5 sidewall spacer adjacent to the gate and over the LDD regions.

- 11. The method of claim 9, wherein the first dopant type comprises a p-type dopant, and wherein the second dopant type comprises an n-type dopant.

- **12**. The method of claim **9**, wherein the first and second 10 diffused regions extend into a portion of the LDD regions.

- 13. The method of claim 9, further comprising forming pocket regions of the first dopant type adjacent to the source and drain regions and below the LDD regions.

- **14**. The method of claim **13**, wherein the first and second 15 diffused regions extend into a portion of the LDD regions and the pocket regions.

- 15. The method of claim 9, further comprising:

- forming isolation regions adjacent to the source and drain regions; and

- forming doped regions of the first dopant type adjacent to the source and drain regions.

- 16. The method of claim 9, further comprising:

- forming a third diffused region of the second dopant type under the first diffused regions; and

- forming a fourth diffused region of the second dopant type under the second diffused region.

- 17. A method, comprising:

providing a semiconductor substrate of a first dopant type; forming at least one source/drain pair of a second dopant 30 type in the substrate, wherein a source region of the source/drain pair is separated from a drain region of the source/drain pair by a channel region;

12

forming a gate on the substrate and over the channel region; forming pocket regions of the first dopant type adjacent to the source and drain regions in the channel region;

forming a first diffused region of the second dopant type under the drain region of the source/drain pair;

forming a second diffused region of the second dopant type under the source region of the source/drain pair; and forming a third diffused region of the second dopant type under the first diffused region;

wherein a region under the second diffused region is a portion of the substrate having the first dopant type.

- **18**. The method of claim **17**, further comprising forming lightly doped drain (LDD) regions of the second dopant type adjacent to the gate.

- 19. The method of claim 18, further comprising forming a sidewall spacer adjacent to the gate and over the LDD regions.

- 20. The method of claim 18, wherein the first and second diffused regions extend into a portion of the LDD regions.

- 21. The method of claim 18, wherein the pocket regions are below the LDD regions.

- 22. The method of claim 21, wherein the first and second diffused regions extend into a portion of the LDD regions and the pocket regions.

- 23. The method of claim 17, wherein the first dopant type comprises a p-type dopant, and wherein the second dopant type comprises an n-type dopant.

- 24. The method of claim 17, further comprising: forming isolation regions adjacent to the source and drain regions; and

forming doped regions of the first dopant type adjacent to the source and drain regions.

\* \* \* \* \*