US007968906B2

## (12) United States Patent Ker et al.

### XCI Ct ai.

#### (54) SUBSTRATE-TRIGGERED BIPOLAR JUNCTION TRANSISTOR AND ESD PROTECTION CIRCUIT

(76) Inventors: Ming-Dou Ker, Hsinchu (TW);

Chyh-Yih Chang, Taipei (TW)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 308 days.

(21) Appl. No.: 10/309,225

(22) Filed: Dec. 4, 2002

(65) **Prior Publication Data**

US 2003/0147190 A1 Aug. 7, 2003

(30) Foreign Application Priority Data

Feb. 6, 2002 (TW) ...... 91102073 A

(51) Int. Cl. *H01L 29/74* (2006.01) *H01L 23/62* (2006.01)

(52) **U.S. Cl.** ...... **257/173**; 257/355

(58) **Field of Classification Search** ....................... 257/173–174, 257/355–363

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,465,189 A * | 11/1995 | Polgreen et al 361/58 |

|---------------|---------|-----------------------|

| 5,825,600 A   | 10/1998 | Watt                  |

| 5,856,214 A * | 1/1999  | Yu 438/133            |

| 5,882,967 A * | 3/1999  | Brown et al 438/237   |

| 6,051,458 A   | 4/2000  | Liang et al.          |

| 6,072,219 A   | 6/2000  | Ker et al.            |

| 6,087,227 A * |         | Hsu 438/275           |

| 6,358,781 B1* | 3/2002  | Lee et al 438/133     |

| 6,399,990 B1* | 6/2002  | Brennan et al 257/355 |

| 6,465,848 B2* | 10/2002 | Ker et al 257/355     |

| 6,507,090 B1* | 1/2003  | Hu et al 257/586      |

|               |         |                       |

## (10) Patent No.: US 7,968,906 B2 (45) Date of Patent: Jun. 28, 2011

| 6,566,715    | D1*  | 5/2002  | Ker et al. | 257/255 |

|--------------|------|---------|------------|---------|

| 0,300,713    | DI.  | 3/2003  | Kei et al  | 231/333 |

| 6,764,892    | B2 * | 7/2004  | Kunz et al | 438/217 |

| 6,872,987    | B2 * | 3/2005  | Yu         | 257/133 |

| 2001/0043449 | A1   | 11/2001 | Okushima   |         |

| 2005/0248891 | A1   | 11/2005 | Ker et al. |         |

#### OTHER PUBLICATIONS

Final Office Action dated Oct. 31, 2007, in related U.S. Appl. No. 11/180,714.

Response to Office in related U.S. Appl. No. 11/180,714, submitted to the USPTO on Mar. 31, 2008.

Office Action dated May 15, 2007, in related U.S. Appl. No. 11/180.714.

Response to Office Action in related U.S. Appl. No. 11/180,714, submitted to the USPTO on Aug. 17, 2007.

Response to Final Office Action in related U.S. Appl. No. 11/180,714, submitted to the USPTO Dec. 21, 2007.

Restriction Requirement issued in U.S. Appl. No. 11/180,714, on Jun. 26, 2006; 6 pages.

Response to Restriction Requirement in U.S. Appl. No. 11/180,714; 5 pages filed Aug. 26, 2008.

#### (Continued)

Primary Examiner — Ori Nadav

#### (57) ABSTRACT

An ESD protection circuit using a novel substrate-triggered lateral bipolar junction transistor (STLBJT) for providing a discharging path between power rails. The ESD protection circuit comprises an ESD detection circuit and a STLBJT device. The STLBJT device formed in a P-type substrate includes N-type collector and emitter regions coupled to the power rails, respectively. The substrate region between the collector and emitter regions, on which there is no field oxide device, serves as a base of the STLBJT device. The STLBJT device further includes a first P-type region coupled to the ESD detection circuit and a second P-type region coupled to one of the power rails, which are spatially separated from the collector/emitter regions, respectively. The STLBJT device is turned on by substrate-triggering responsive to the signal coming from the ESD detection circuit and establishes the discharging path between the power rails.

#### 8 Claims, 14 Drawing Sheets

### US 7,968,906 B2

Page 2

#### OTHER PUBLICATIONS

Official Action issued in U.S. Appl. No. 11/180,714, on Nov. 24, 2008; 11 pages.

Response to Official Action in U.S. Appl. No. 11/180,714; 8 pages filed Feb. 24, 2009.

Office Action of Sep. 18, 2009, in U.S. Appl. No.  $11/180,714,\ 14$  pages.

Response to Office Action of Sep. 18, 2009, in U.S. Appl. No. 11/180,714,9 pages.

Office Action of Apr. 1, 2010, in U.S. Appl. No. 11/180,714, 9 pages. Response to Office Action of Apr. 1, 2010, in U.S. Appl. No. 11/180,714, 11 pages.

\* cited by examiner

FIG. 1 (PRIOR ART)

FIG. 4

FIG. 5

FIG. 6

FIG. 8a

FIG. 8b

FIG. 8c

FIG. 8d

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 14

FIG. 15

FIG. 16

FIG. 17

#### SUBSTRATE-TRIGGERED BIPOLAR JUNCTION TRANSISTOR AND ESD PROTECTION CIRCUIT

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to an electrostatic discharge (ESD) protection technology, more specifically, to a substrate-triggered lateral bipolar junction transistor (STLBJT) for use in ESD protection and the related ESD protection circuit.

#### 2. Description of the Prior Art

ESD phenomena have become a reliability issue in complementary metal oxide semiconductor (CMOS) inte- 15 grated circuits (ICs) because of technology scaling and high frequency requirements. For radio frequency (RF) ICs, the on-chip ESD protection design suffers from several limitations, such as low parasitic capacitance, constant input capacitance, insensitivity to substrate coupling noises, and 20 high ESD robustness. A typical requirement of the maximal loading capacitance for an RF input pad is only 200 fF at an operating frequency of 2 GHz. As described herein, this 200 fF target not only includes ESD protection devices but also the bond pad itself. In order to fulfill these requirements, 25 diodes are commonly used for ESD protection in I/O circuits. To deal with these challenges, low-capacitance bond pad and low-capacitance ESD protection circuitry had been proposed with some specific techniques.

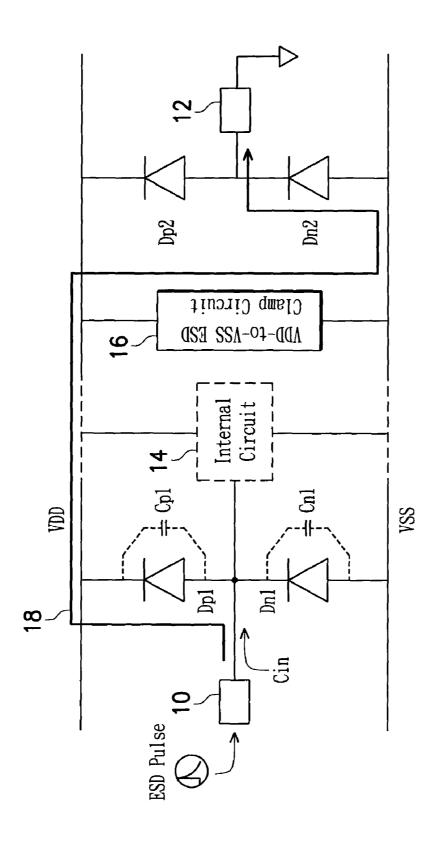

Moreover, by adding a turn-on efficient ESD clamp circuit 30 across the power rails of the input ESD protection circuit formed by the diodes, the overall ESD level of the input pin can be significantly improved. FIG. 1 is a circuit diagram of a conventional input ESD protection circuit with a power-rail (VDD-to-VSS) ESD clamp circuit. In FIG. 1, ESD diodes 35 Dp1 and Dn1 are connected to pad 10 and ESD diodes Dp2 and Dn2 are connected to pad 12. Numeral 14 represents an internal circuit and numeral 16 represents the ESD clamp circuit connected between the VDD and VSS power rails. When the ESD pulse is applied to pad 10 and pad 12 is 40 relatively grounded, the ESD current is conducted to the power rail VDD through the forward-biased ESD diode Dp1. The ESD current on the VDD power rail is discharged to the VSS power rail by the efficient VDD-to-VSS ESD clamp circuit 16. Finally, the ESD current is conducted to grounded 45 pad 2 through the forward-biased ESD diode Dn2. The overall discharging path of the ESD current is indicated by a bold line 18 in FIG. 1. By using such ESD protection design, the ESD diodes are all operating in the forward-biased condition to discharge the ESD current. The diode operated in the 50 forward-biased condition can sustain a much higher ESD level with a small device dimension. Thus, the ESD clamp device in the input ESD protection circuit can be realized with smaller device dimensions to significantly reduce the input capacitance of the input ESD protection circuit for high- 55 frequency applications.

Therefore, the turn-on efficient power-rail ESD clamp circuit can significantly improve the ESD robustness of IC products if the power-rail ESD clamp circuit can be turned on efficiently while an ESD event is happening.

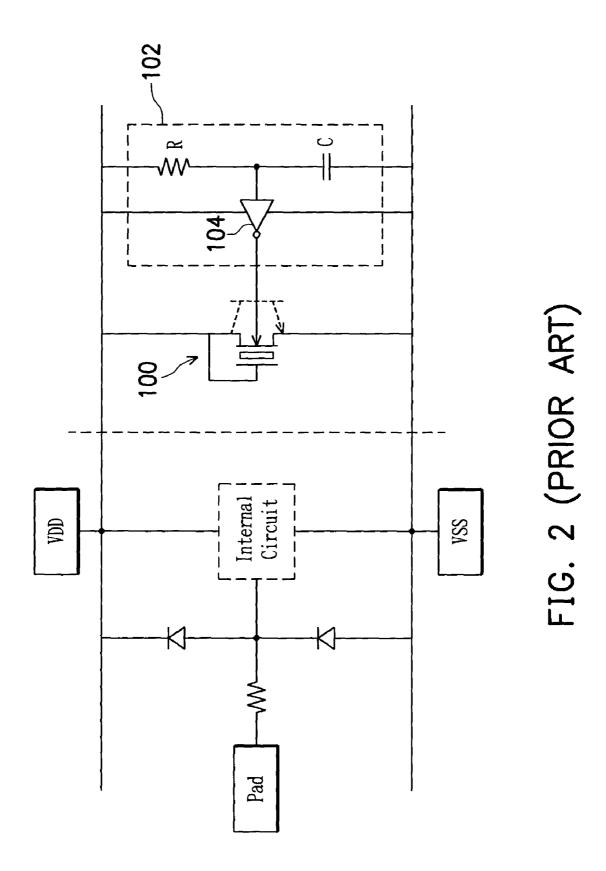

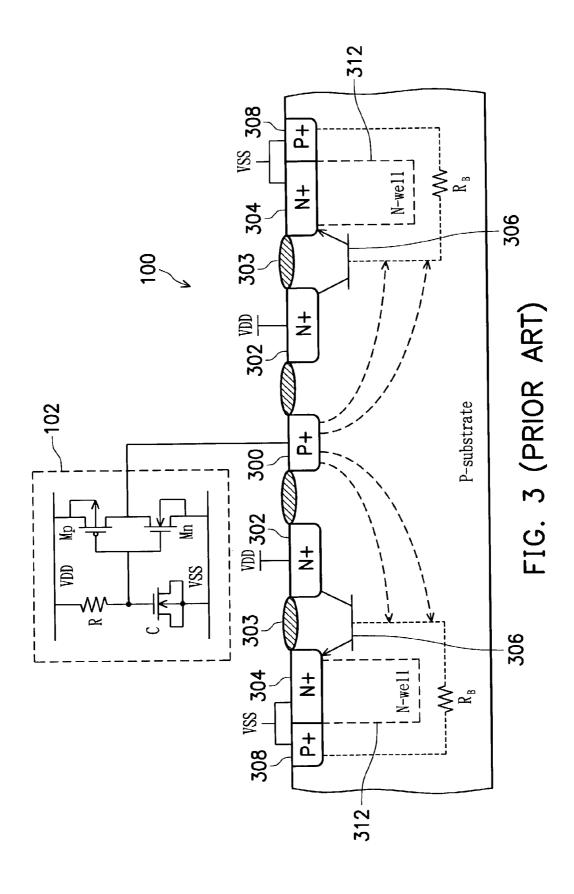

In addition, U.S. Pat. No. 5,744,842 disclosed an areaefficient VDD-to-VSS ESD protection circuit. FIG. 2 is a circuit diagram of this ESD protection circuit and FIG. 3 is a cross-section of the ESD protection circuit.

As shown in FIG. 2 and FIG. 3, the ESD protection circuit 65 is composed of an ESD transient detection circuit 102 and an N-type field oxide device 100. The ESD transient detection

2

circuit 102 comprises a resistance-capacitance network, which includes a resistor R and a capacitor C and is connected between the VDD and VSS power rails, and an inverter 104 including a PMOS transistor Mp and an NMOS transistor Mn. The field oxide device 100 is a parasitic bipolar junction device including an N+ collector 302, N+ emitter 304 and a P+ base 300. The RC network has a delay constant longer than the duration of the electrostatic pulse and shorter than the duration of the rising time of VDD power-on. The contact of the resistor R and the capacitor C is electrically coupled to the input of inverter 104. The gate of PMOS transistor Mp is coupled to the gate of NMOS transistor Mn. The sources of PMOS transistor Mp and NMOS transistor Mn are coupled to the VDD and VSS power lines, respectively. The drains of PMOS transistor Mp and NMOS transistor Mn are coupled to base 300 of the field oxide device 100. When the ESD pulse occurs on the VDD power line and the VSS power line is relatively grounded, the gates of PMOS transistor Mp and NMOS transistor Mn maintain a low voltage level since the RC network has a longer delay time constant. Thus, PMOS transistor Mp turns on and NMOS transistor Mn turns off. The initial ESD current flows into the base 300 of the field oxide device 100 through PMOS transistor Mp and then flows to the VSS power line through the substrate pickup 308. At the same time, the initial ESD current raises the base voltage of the parasitic BJT and triggers on the parasitic BJT. Then, the ESD current on the VDD power line flows to the VSS power line through the parasitic BJT.

In '842, the base of the parasitic BJT is defined by a field oxide. However, field oxide can be replaced by shallow trench isolation (STI) in sub-quarter-micron CMOS process because of bird's beak effect of the field oxide. The STI is deeper than the field oxide in silicon substrate. Therefore, the field oxide device in STI technology is hard to turn on.

U.S. Pat. No. 5,581,104 disclosed a grounded-base BJT device serving as an ESD protection device. This grounded-base BJT structure includes a parasitic diode used to aid the triggering of the BJT.

In the above, the power-rail ESD clamp circuit is important to improve the ESD robustness of IC products. As well, the power-rail ESD clamp circuit needs to be triggered efficiently while an ESD event is happening. However, the field oxide device in sub-quarter-micron CMOS process using the STI technology is hard to turn on.

Therefore, the object of the present invention is to provide an ESD protection device and an ESD protection circuit using the same, which has a lower triggering voltage and can be triggered more efficiently as the ESD event occurs, especially in the sub-quarter-micron CMOS process.

#### SUMMARY OF THE INVENTION

The present invention achieves the above-indicated object by providing an ESD protection circuit for providing a low-resistance path for discharging the ESD current between a first line and a second line, such as between the VDD and VSS power rails and between other signal lines. The ESD protection circuit comprises an ESD detection circuit and a lateral bipolar junction transistor (BJT). The function of the ESD detection circuit is to trigger the lateral BJT as an ESD event occurs, and to send a grounding signal or other signals to turn off the lateral BJT as the circuit is operated normally. The lateral BJT is coupled to an output terminal of the ESD detection circuit and used to provide a discharging path between the first line and the second line. In the preferred embodiments, the lateral BJT is formed in a P-type substrate and includes N+ collector and emitter regions coupled to the

first line and the second line, respectively. The substrate region between the collector and emitter regions, on which there is no field oxide or STI, serves as a base of the lateral BJT. In addition, in the P-type substrate, there are first/second P-type doped regions spatially separated from the collector/ emitter regions, respectively. The first P-type doped region is connected to the output terminal of the ESD detection circuit and the second P-type doped region is connected to the second line. In addition, STI structures are preferably formed between the collector region and the first doped region and 10 between the emitter region and the second doped region, where the STI structure between the emitter region and the second doped region can be omitted. In the above-mentioned ESD protection circuit, the lateral BJT can be easily triggered by substrate-triggering through the first doped region responsive to the trigger signal coming from the ESD detection circuit, forming the discharging path between the first line and the second line.

Moreover, the substrate-triggered lateral BJT can further mance. For example, an N-well can be added between the base and the substrate pickup to increase the base resistance. For another example, an N-type region can be added to increase the area of the collector of the lateral BJT.

Further scope of the applicability of the present invention 25 will become apparent from the detailed description given hereinafter. However, it should be understood that the detailed description and specific examples, while indicating preferred embodiments of the invention, are given by way of illustration only, since various changes and modifications 30 within the spirit and scope of the invention will become apparent to those skilled in the art from this detailed description.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The present invention will become more fully understood from the detailed description given hereinbelow and the accompanying drawings, which are given by way of illustration only, and thus are not limitative of the present invention, 40 and in which:

FIG. 1 is a circuit diagram of a conventional input ESD protection circuit with a VDD-to-VSS ESD clamp circuit;

FIG. 2 is a circuit diagram of a conventional ESD protection circuit:

FIG. 3 is a cross-section of the ESD protection circuit shown in FIG. 2:

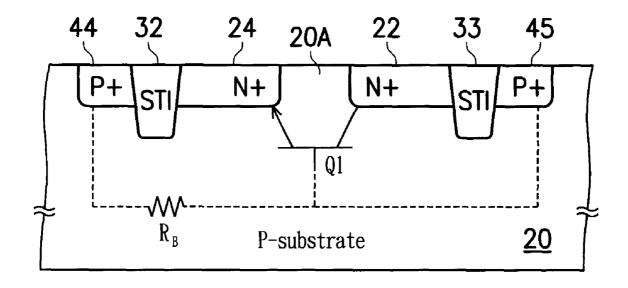

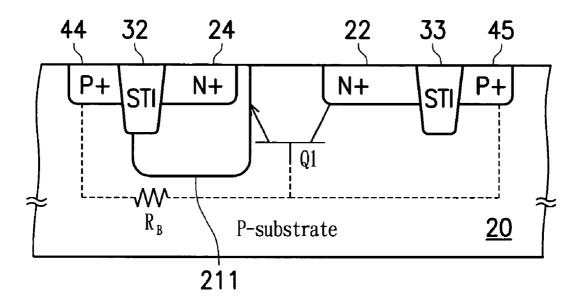

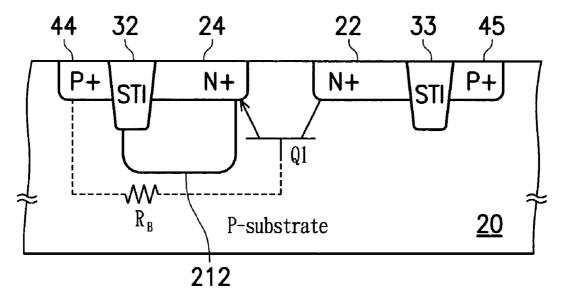

FIG. 4 is a cross-section of the STLBJT device in accordance with the first embodiment of the present invention;

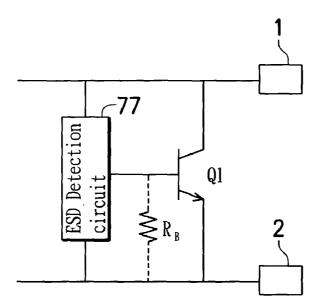

FIG. 5 is a block diagram of the ESD protection circuit 50 using the STLBJT device as an ESD protection device in accordance with the first embodiment of the present inven-

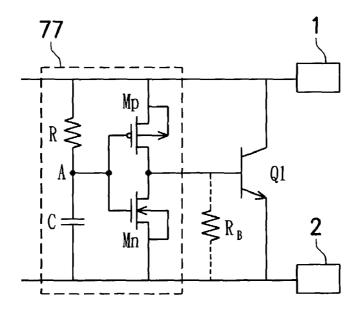

FIG. 6 is a circuit diagram of the ESD protection circuit shown in FIG. 5:

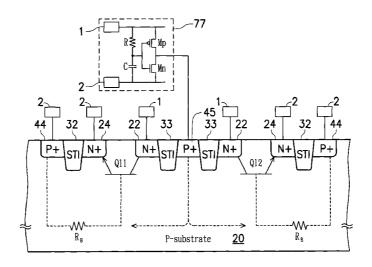

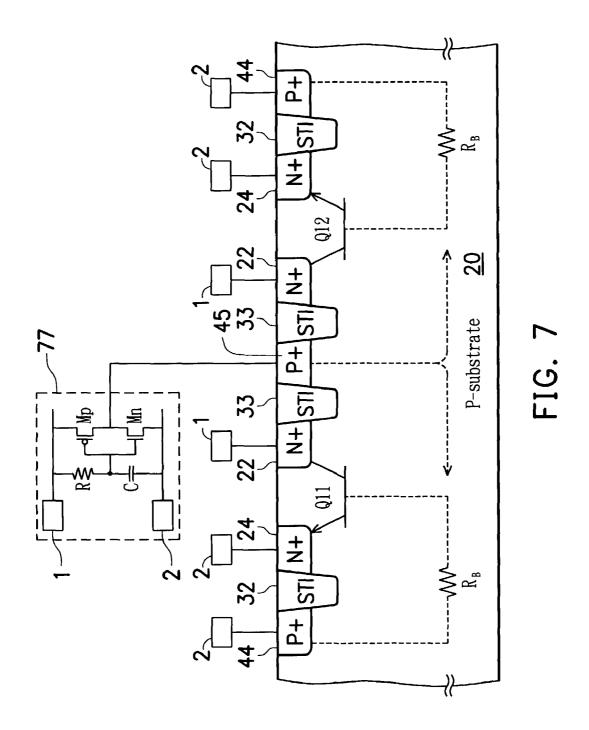

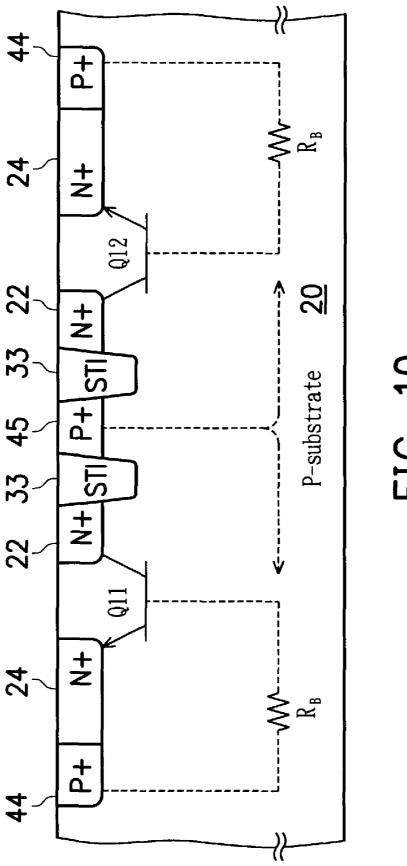

FIG. 7 is a partial cross-section of the ESD protection circuit in accordance with the first embodiment of the present invention;

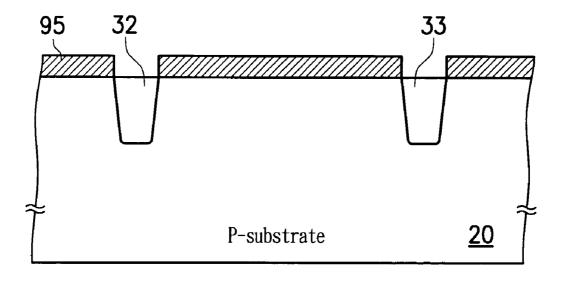

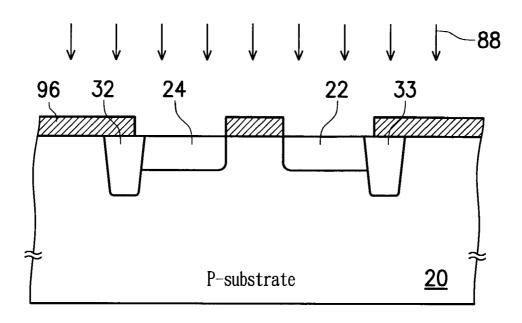

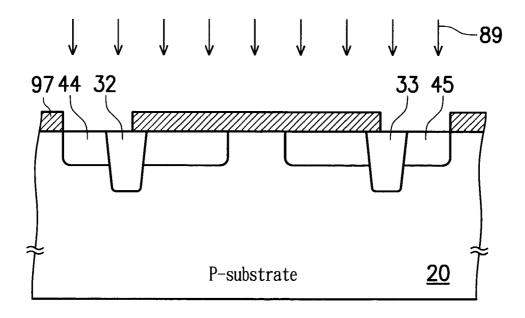

FIGS. 8a-8d are cross-sections illustrating the manufacturing process of the STLBJT device in the present embodiment. 60

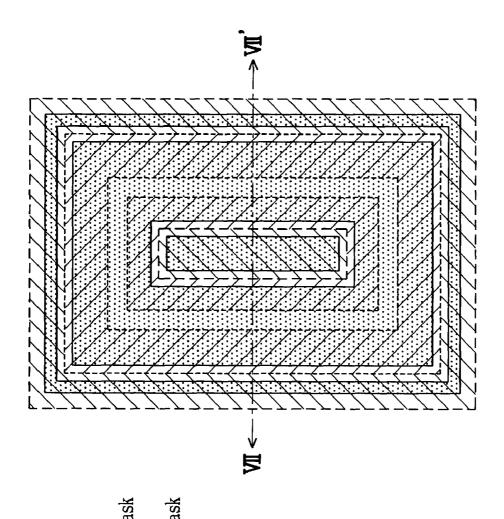

FIG. 9 is a layout view of the STLBJT device in accordance with the first embodiment of the present invention;

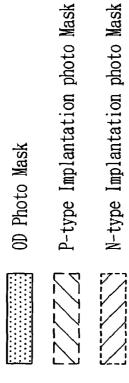

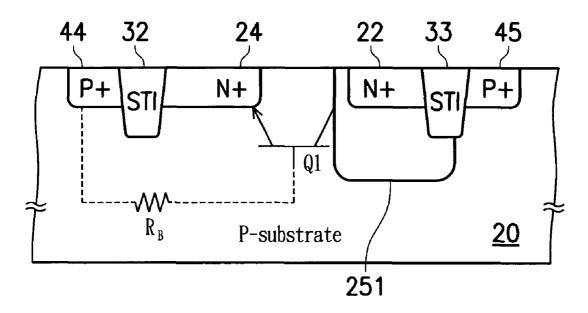

FIG. 10 is a cross-section of the STLBJT device in accordance with the second embodiment of the present invention;

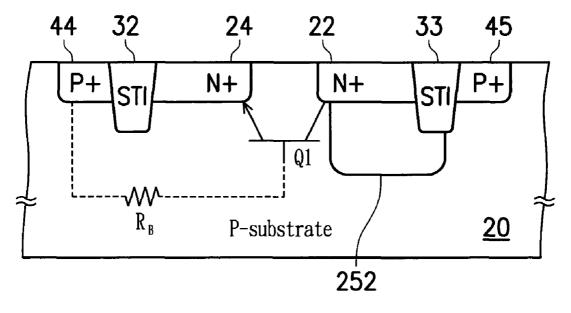

FIG. 11 is a cross-section of a first example of the STLBJT 65 device in accordance with the third embodiment of the present invention;

FIG. 12 is a cross-section of a second example of the STLBJT device in accordance with the third embodiment of the present invention:

FIG. 13 is a cross-section of a third example of the STLBJT device in accordance with the third embodiment of the present invention:

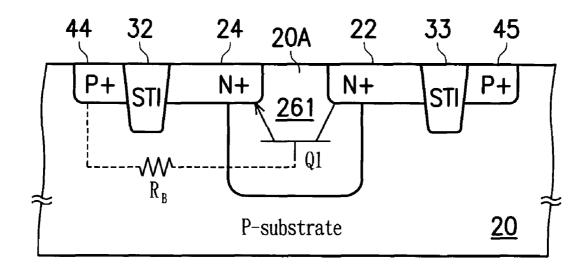

FIG. 14 is a cross-section of a fourth example of the STL-BJT device in accordance with the third embodiment of the present invention;

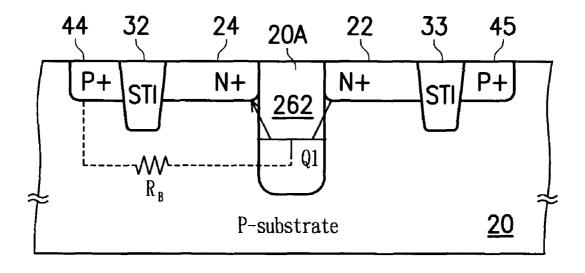

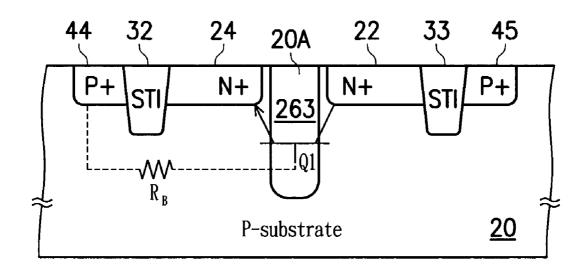

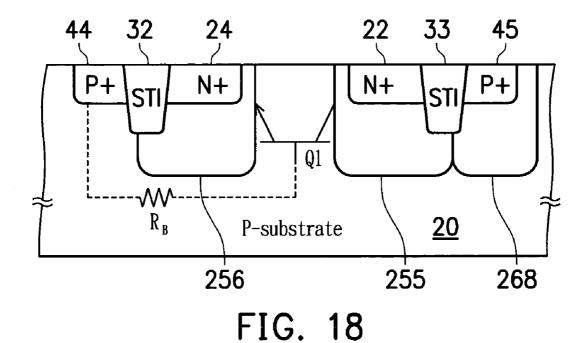

FIGS. 15-17 are cross-sections of the STLBJT devices containing P-type doped regions with different profiles; and FIG. 18 is a cross-section of the STLBJT device in accordance with the fifth embodiment of the present invention.

#### DETAILED DESCRIPTION OF THE INVENTION

#### First Embodiment

The main concept of the present invention is to utilize a comprise some doping regions to enhance the BJT perfor- 20 novel substrate-triggered lateral bipolar junction transistor (STLBJT) device as an ESD protection device. FIG. 4 is a cross-section of the STLBJT device in accordance with the first embodiment of the present invention. As shown in FIG. 4, the STLBJT device comprises two N-type regions 22 and 24 and two P-type regions 44 and 45 inside a P-type substrate 20. Both the N-type regions 22 and 24 are located between the P-type regions 44 and 45. The N-type regions 22 and 24 are close but not connected, and isolated by a substrate region 20A of P-type substrate 20. The N-type region 22, the P-type substrate region 20A and the N-type region 24 constitute the collector, base and emitter of the STLBJT device Q1. There is no STI or field oxide formed on the base of the STLBJT device Q1 (region 20A) between the N-type regions 22 and 24. Therefore, the STLBJT device can be triggered more 35 efficiently than the conventional field oxide device. In addition, there are STI structures 33 and 32 between the N-type region 22 and the P-type region 45 and between the N-type region 24 and the P-type region 44, respectively, where the symbol RE denotes the substrate resistance. In operation, the P-type region 45 receives a signal to bias the base of the STLBJT device Q1 and triggers on the STLBJT device Q1 to bypass the ESD current.

FIG. 5 is a block diagram of the ESD protection circuit including the STLBJT device Q1 in accordance with the first 45 embodiment of the present invention. The ESD protection circuit provides a discharge path between pad 1 and pad 2, such as the pads of the VDD and VSS power rails, and includes a STLBJT device Q1 and ESD detection circuit 77. The collector and emitter of the STLBJT device Q1 are respectively coupled to pad 1 and pad 2 and its base is coupled to the output of the ESD detection circuit 77. The ESD detection circuit 77 is designed to detect the ESD event across the pad 1 and the pad 2. When an ESD event occurs, the STLBJT device Q1 is substrate-triggered to provide a path for dis-55 charging the ESD current. As described above, the advantage of the present embodiment is that the STLBJT device Q1 can be triggered more efficiently than the conventional field oxide device, thus the ESD protection performance is strengthened.

FIG. 6 is a circuit diagram of an example of the ESD protection circuit shown in FIG. 5. As shown in FIG. 6, the ESD detection circuit 77 is composed of a resistor R, a capacitor C, a PMOS transistor Mp and an NMOS transistor Mn. The RC network including resistor R and capacitor C has a delay constant longer than the duration of ESD pulses and shorter than the initial rising time of the signal on pad 1. As ESD pulses are applied to pad 1 and pad 2 is relatively grounded, node A maintains the low voltage level due to the

longer delay constant of the RC network. Thus, the PMOS transistor Mp is turned on and the NMOS transistor Mn is turned off. Subsequently, the ESD current flows into the base of the STLBJT device Q1 through the PMOS transistor Mp, triggering on the STLBJT device Q1. Thus, the ESD current flows from pad 1 to pad 2 through the turned-on STLBJT device Q1.

FIG. 7 is a partial cross-section of the ESD protection circuit in accordance with the first embodiment of the present invention, where the STLBJT device is illustrated with a cross-section and the ESD detection circuit 77 with a circuit diagram. As shown in FIG. 7, the output of the ESD detection circuit 77 is coupled to P-type region 45. In addition, the N-type regions 22 (i.e. the collectors) of the STLBJT devices Q11 and Q12 are coupled to pad 1, the N-type regions 24 (i.e. the emitters) are coupled to pad 2 and the P-type regions 44 are also coupled to pad 2. The signal coming from the ESD detection circuit 77 can trigger the STLBJT devices Q11 and Q12, respectively, to provide paths for discharging the ESD current.

FIGS. 8a-8d are cross-sections illustrating the manufacturing process of the STLBJT device in the present embodiment. At first, in FIG. 8a, a P-type substrate 20 is prepared. In FIG. 8b, an active region mask 95 is defined by a photolithographic process and formed on the substrate 20. Then, the P-type 25 substrate 20 is etched and filled with insulators like silicon dioxide or silicon nitride to form STI structures 32 and 33. In FIG. 8c, an N-type implantation mask 96 is defined by a photolithographic process. The N-type regions 22 and 24 are formed with an implantation of N-type impurities 88 using 30 the N-type implantation mask 96. Finally, in FIG. 8d, a P-type implantation mask 97 is defined by a photolithographic process. Then the P-type regions 44 and 45 are formed with an implantation of P-type impurities 89 using the P-type implantation mask 97. The photolithographic process defining the 35 P-type implantation mask 97 shown in FIG. 8d can be performed earlier than that defining the N-type implantation mask **96** shown in FIG. **8**c. Using the process shown in FIGS. 8a-8d, the STLBJT device like that shown in FIG. 4 is formed on the P-type substrate 20.

FIG. 9 is a layout view of the STLBJT device in accordance with the first embodiment of the present invention. As shown in FIG. 9, there are three key photo masks used to form the STLBJT device, including an oxide definition (usually called OD) photo mask for defining implantation regions, a P-type implantation photo mask for defining the base of the STLBJT device and an N-type implantation photo mask for defining the N-type collector and emitter of the STLBJT device. The cross-section in respect of the line VII-VII' is illustrated in FIG. 7. It is noticed that the above-mentioned photolithographic processes are available in and process-compatible with the current sub-quarter-micron CMOS process. Thus, there is no need to change or add new process steps to the existing process, which is favorable to the industrial application.

#### Second Embodiment

The structure of the STLBJT device disclosed in the first embodiment of the present invention is not intended to limit 60 the scope of the invention. In respect of different requirements, this device structure can be modified to achieve the same or better ESD protection performance. FIG. 10 is a cross-section of the STLBJT device in accordance with the second embodiment of the present invention. The difference 65 in the STLBJT structures shown in FIG. 10 and FIG. 7 (the first embodiment) is that the STI structure 32 between N-type

6

region 24 and the P-type region 44 is omitted, which can still achieve the object of the present invention.

#### Third Embodiment

In the present invention, an extra N-type doped region can be added in the STLBJT device structure shown in the first embodiment to increase substrate resistance RB or change emitter concentration, expediting the triggering operation. FIG. 11 is a cross-section of a first example of the STLBJT device in the present embodiment. As shown in FIG. 11, an N-type doped region 211 is formed under the N-type region 24 (i.e. the emitter) and on the side of the N-type region 24, that is, surrounding the N-type region 24, to increase the substrate resistance RB. FIG. 12 is a cross-section of a second example of the STLBJT device in the present embodiment. As shown in FIG. 12, an N-type doped region 212 is formed just under the N-type region 24 to increase the emitter concentration. The formation of the N-type doped regions 211 and 212 is preferably made by the n-well formation step or the ESD implantation step.

In addition, the above-mentioned manipulation can also be applied to the collector of the STLBJT device. FIG. 13 is a cross-section of a third example of the STLBJT device in the present embodiment. As shown in FIG. 13, an N-type doped region 251 is formed under the N-type region 22 (i.e. the collector) and on the side of the N-type region 22, that is, surrounding the N-type region 22. FIG. 14 is a cross-section of a fourth example of the STLBJT device in the present embodiment. As shown in FIG. 14, an N-type doped region 252 is formed just under the N-type region 22 to adjust the substrate resistance and the collector concentration.

#### Fourth Embodiment

In the present invention, an extra P-type doped region can be added in the structure of the STLBJT device shown in the first embodiment to increase base resistance or base impurities. FIG. 15, FIG. 16 and FIG. 17 are cross-sections of the STLBJT devices containing P-type doped regions with different profiles. In FIG. 15, a P-type doped region 261 is formed under the substrate region 20A and the N-type regions 22 and 24. In FIG. 16, a P-type doped region 262 is formed under the substrate region 20A and laterally adjacent to the N-type regions 22 and 24. In FIG. 17, a P-type doped region 263 is formed under the substrate region 20A and its width is narrower than that of the substrate region 20A. The extra P-type doped regions shown in FIG. 15, FIG. 16 and FIG. 17 are used to increase the base resistance or the base impurity concentration.

#### Fifth Embodiment

In the above-mentioned third and fourth embodiments, extra N-type or P-type doped regions are formed in the substrate to improve the triggering performance of the STLBJT device in the present invention. In the present embodiment, several doped regions are formed in different regions to optimize the performance of the STLBJT device. FIG. 18 is a cross-section of the STLBJT device in the present embodiment. As shown in FIG. 18, an N-type doped region 256 formed by ESD implantation is added under the N-type region 24 (i.e. the emitter), an N-type doped region 255 formed by the N-well process is added under the N-type region 22 (i.e. the collector), and a P-type doped region 268 formed by the P-well process is added under the P-type region 45. In this case, the impurity concentration of N-type ESD

implantation region **256** is higher than that of N-well region **255**, which is further higher than that of P-well region **268**. Thus, the triggering performance of the STLBJT device can be optimized.

According to the above description, the advantages of the 5 STLBJT device serving as an ESD protection device and the ESD protection circuit using the same are as follows:

- 1. In the sub-quarter-micron process, the STLBJT device of the present invention can be triggered more efficiently than the field oxide device adopted in the conventional scheme. 10 Therefore, the ESD protection circuit using the STLBJT device of the present invention as an ESD protection device can provide higher resistance to the ESD current.

- 2. The manufacturing process of the STLBJT device of the present invention is fully process-compatible with current 15 sub-quarter-micron CMOS processes and does not require adding extra photo mask processes, and is thus easily incorporated to the current production line.

While the invention has been described by way of example and in terms of the preferred embodiment, it is to be understood that the invention is not limited to the disclosed embodiments. On the contrary, it is intended to cover various modifications and similar arrangements as would be apparent to those skilled in the art. Therefore, the scope of the appended claims should be accorded the broadest interpretation so as to 25 encompass all such modifications and similar arrangements.

What is claimed is:

- 1. An electrostatic discharge (ESD) protection circuit, comprising:

- an ESD detection circuit coupled to a first power rail and a 30 second power rail and having an output terminal, wherein the ESD detection circuit is configured, upon detecting an ESD condition, to output an indication of the ESD condition on the output terminal;

- a first lateral bipolar junction transistor (BJT) including: 35 ing:

- a first collector region of a first implantation type coupled to the first power rail, wherein the first collector region is in contact with a substrate of a second implantation type that is different from the first implantation type;

- a first emitter region of the first implantation type coupled to the second power rail, wherein the first emitter region is in contact with the substrate; and

- a first base region in contact with the first collector region and the first emitter region, wherein the first 45 base region is constituted entirely of the substrate, wherein neither a field oxide structure nor an STI structure is formed between the first collector region and the first emitter region and wherein no gate structure is formed directly above the first base region; and 50

a second lateral BJT including:

a second collector region of the first implantation type coupled to the first power rail, wherein the second collector region is in contact with the substrate; 8

- a second emitter region of the first implantation type coupled to the second power rail, wherein the second emitter region is in contact with the substrate; and

- a second base region in contact with the second collector region and the second emitter region, wherein the second base region is constituted entirely of the substrate, wherein neither a field oxide structure nor an STI structure is formed between the second collector region and the second emitter region and wherein no gate structure is formed directly above the second base region;

wherein the ESD detection circuit further includes:

- a common region of the second implantation type in contact with the substrate, wherein the common region is electrically coupled to the output terminal of the ESD detection circuit; and

- a first shallow trench isolation (STI) structure located between the first collector region and the second collector region and surrounding the common region;

- wherein the first lateral BJT and the second lateral BJT are configured, upon receiving the indication of the ESD condition, to trigger.

- **2**. The ESD protection circuit of claim **1**, wherein the lateral BJT is a substrate-triggered lateral BJT.

- 3. The ESD protection circuit of claim 1, wherein the first power rail is a VDD power rail and the second power rail is a VSS power rail.

- **4.** The ESD protection circuit of claim **1**, wherein the first implantation type is P type and the second implantation type is N type.

- **5**. The ESD protection circuit of claim **1**, wherein the first implantation type is N type and the second implantation type is P type.

- 6. The ESD protection circuit of claim 1, further comprising:

- a second STI structure surrounding the first emitter region and the second emitter region; and

- a doped region of the second implantation type surrounding the second STI structure.

- 7. The ESD protection circuit of claim 1, further comprising:

- a doped region of the second implantation type in contact with the substrate, the first emitter region, and the second emitter region.

- 8. The ESD protection circuit of claim 1, wherein the first collector region and the second collector region are different portions of a first region of the first implantation type, wherein the first region surrounds the first STI structure and the common region, and wherein the first emitter region and the second emitter region are different portions of a second region of the first implantation type, wherein the second region surrounds the first and second lateral BJTs.

\* \* \* \* \*

# UNITED STATES PATENT AND TRADEMARK OFFICE CERTIFICATE OF CORRECTION

PATENT NO. : 7,968,906 B2 Page 1 of 1

APPLICATION NO. : 10/309225 DATED : June 28, 2011 INVENTOR(S) : Ker et al.

It is certified that error appears in the above-identified patent and that said Letters Patent is hereby corrected as shown below:

Title page, item (56), under "Other Publications", in Column 2, Line 3, delete "Office" and insert -- Office Action --.

Title page, item (56), under "Other Publications", in Column 2, Line 10, delete "USPTO" and insert -- USPTO on --.

Title page, item (56), under "Other Publications", in Column 2, Line 12, delete "2006;" and insert -- 2008; --.

Page 2, item (56), under "Other Publications", in Column 1, Line 1, delete "on" and insert -- filed on --.

Page 2, item (56), under "Other Publications", in Column 1, Line 4, delete "filed" and insert -- filed on --.

Column 8, line 29, in Claim 4, delete "P type" and insert -- P-type --.

Column 8, line 30, in Claim 4, delete "N type." and insert -- N-type. --.

Column 8, line 32, in Claim 5, delete "N type" and insert -- N-type --.

Column 8, line 33, in Claim 5, delete "P type." and insert -- P-type. --.

Signed and Sealed this Eighth Day of November, 2011

David J. Kappos

Director of the United States Patent and Trademark Office