#

基體網發技術與積體電路晶十上之靜電故電防護電路設計

# SUBSTRATE-TRIGGERED TECHNIQUE FOR ON-CHIP ESD PROTECTION DESIGN IN DEEP-SUBMICRON CMOS INTEGRATED CIRCUITS

平完生: 陳東陽 Tung-Yang Chen

指導教授 : 枦 單 道 Ming-Dou Ker

中華气國七一一年三月

# 基體網發技術與積體電路晶十上之靜電故電 防護電路設計

## SUBSTRATE-TRIGGERED TECHNIQUE FOR ON-CHIP ESD PROTECTION DESIGN IN DEEP-SUBMICRON CMOS INTEGRATED CIRCUITS

平 完 生: 陳東陽 Student: Tung-Yang Chen

指導教授:柯印道 Advisor: Ming-Dou Ker

國立交通七學 電子工程學為電子四名 所 博 土 論 文

A Dissertation

Submitted to

Institute of Electronics

College of Electrical Engineering

and Computer Science

National Chiao Tung University

in Partial Fulfillment of Requirements

for the Degree of

Doctor of Philosophy

in

Electronic Engineering

March 2002 Hsinchu, Taiwan, Republic of China

中華民國九十一年三月

# 基體開發技術與積體電路晶片上之靜電故電防護電路設計

**石**完生: 陳東陽 捐導教授: 伊即道 副教授

國立交通七學電子工程學系電子研究所

# 捕母

本論〉提出基體觸發技術在靜電放電下啟動的物理機制,並將其應用在深次微米互補式金筆半積體電路(deep-submicron CMOS IC)的靜電放電防護設計上,因應積體電路中不斷的需求,而設計出各種靜電放電防護電路,以避免積體電路受到靜電放電的破壞。日於在先進的製程中,半導體元件的接面崩潰(Junction Breakdown)電壓越來越接近開極筆化層(Gate Oxide)的崩潰電壓,在靜電放電(ElectroStatic Discharge, ESD)防護的設計上,傳統的設計方法已越來越加困難。開極驅動(Gate Driven)技術以及基體觸發(Substrate Triggered)技術都是為了提昇靜電放電防護元件在靜電放電衝擊時的反應效率及防護能力,所發展出的最新技術。但是在進入深次微米的製程時,開極驅動技術也越來越難以設計及控制,從本論文的研究中證實基體觸發技術對於靜電放電防護的設計是一個最佳最有效的方法。

首先,從靜電放電防護基本元件在遭到靜電放電衝擊下啟動的基本原理為起點,實際在 0.35 微米製程中,以變化不斷的佈局參數,來改變指狀結構(Finger type)靜電放電防護基本元件的佈局結構,以靜電放電實驗及二次崩潰點(Secondary Breakdown)的量測來說明元件結構對靜電放電耐受力的影響,並且靜電放電防的測試結果中,求得最佳佈局方式,再從靜電放電防護元件之能帶圖(Energy Band Diagram)變化與觀察其在發射顯微鏡(EMission MIcroscope, EMMI)下的啟動變化分析,更進而說明元件在受到靜電放電衝擊下的啟動原理,並做一詳盡的物理定性分析,進而了解佈局參數對靜電放電防護能力影響的物理因素。從了解基本元件在遭到靜電放電衝擊下啟動的基本原理後,進一步分析開極驅動技術及基體觸發技術的動作原理以及其對靜電放電防護的特性。日利用實驗設計的技巧,觀察其在發射顯微鏡下受到開極驅動及基體觸發的啟動變化,並借日靜電放電防護

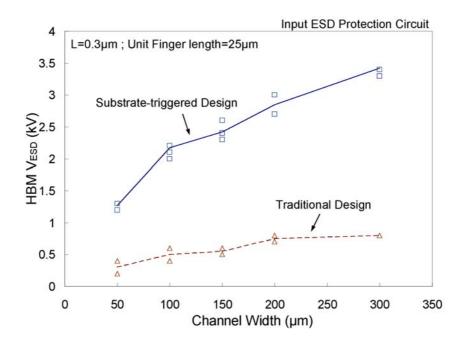

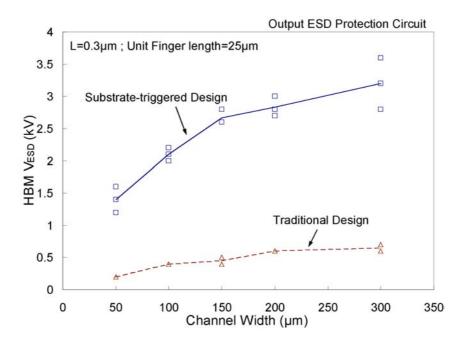

在積體電路中需要有全面性靜電放電防護設計(Full ESD Protection Design)的觀點是越來越重要,對於先進的積體電路,無論在輸入、輸出極 甚至電源間皆必需有完整的靜電放電防護設計,在本論文中,將基體觸發 技術實際應用在 0.18 微米互補式金氧半製程中,發展出一套基體觸發靜電 放電防護電路,分別應用在輸入、輸出極以及電源 VDD 與 VSS 間, 后時 才 在相后的製程中,製作傳統的靜電放電防護電路以做為比較。從人體模 式(Human Body Model, HBM) 的靜電放電測試中發現,在本製程中對靜電放 電防護能力原本相當不理想的輸出極(W/L = 300μm/0.3μm), 在加入基體觸 發技術的輸出保護電路後,可從原來 0.65 kV 的靜電放電耐受力增加到 3.2 kV,證實了基體觸發技術的實用性。此外,在先進的深次微米製程中,目 於元件的結構等比例地縮小,因此使用的電源電壓也必需從傳統的5 伏特 降下到 3.3 伏特甚至是 1.8 伏特, 因此電子系統 必需混合 5 伏特及 3.3 伏 特的電源電壓,例如一個3.3 伏特電壓源的積體電路之輸入端,就可能必需 接到一個 5 伏特的輸入訊號, 因此在此種輸入端的靜電放電防護設計,就 心需有特殊的专量。在本論文中,提供了一種新式且不需額外加遮蔽金屬 砂化物的光罩 (Salicide Blocking Mask) 及專為靜電放電防護佈植(ESD implantation) 的輸入極靜電放電防護電路,應用在這種混合電壓之電路的輸 入極當靜電放電保護電路。在運當的佈局下,整個電路可以整合在一個單 一 的砂元件結構中,以加強其基體觸發的能力。在本論立中,此種設計也 實際在 0.25 微米 互 補 式 金 氧 半 的 製 程 中 製 作 出 來 , 其 中 150 微 米 總 寬 度 的 此種新式元件,在人體模式的靜電放電測試下,可以有效改善沒有基體觸 發之基本元件的靜電放電耐受能力,在單位面積的比較下,實驗結果顯示 其靜電放電耐受能才可以從原來的1.2 V/μm²增加到1.73 V/μm²。

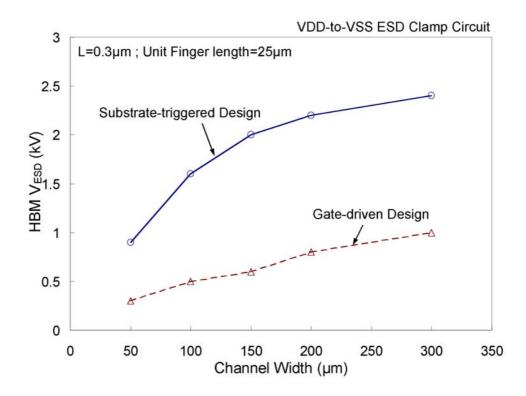

而在電源間的靜電放電箝制電路方面,本論心除了在 0.18 微米製程中所設計的基體觸發電路外,本論心還在 0.6 微米互補式金氧半製程中提出四種新式的基體觸發靜電放電箝制元件,而為了使靜電放電電流能夠更均勻,這些靜電放電箝制元件被設計成多單元的四方形結構,並將其設計應用在靜電放電箝制電路中。這些靜電放電箝制元件是直接利用到互補式金氧半元件中具有寄生雙載子電晶體的特性,而將基體觸發的原理應用這些元件上,使其在靜電放電時能夠迅速而均勻地開啟。這些元件包含了:基

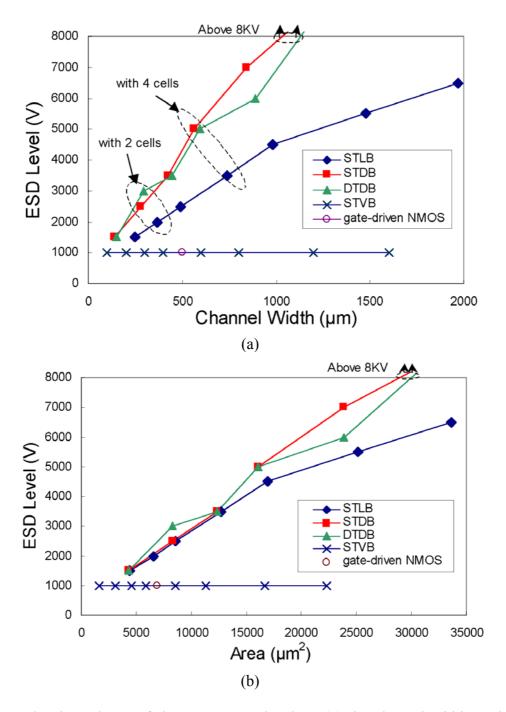

體觸發水平雙載子電晶體(STLB),基體觸發垂直雙載子電晶體(STVB),基體觸發雙雙載子電晶體(STDB),以及雙極觸發雙雙載子電晶體(DTDB)。在電路的設計方面,一種以電阻-電容為基礎的靜電放電偵測電路被用來做為主要的電路,以產生觸發電流來快速而有效地驅動這些靜電放電箝制元件。目靜電放電測試實驗結果顯示,具有基體觸發雙雙載子電晶體(STDB)的基體觸發之源極間的靜電放電箝制電路,可以比傳統開極驅動之靜電放電箝制電路在戶樣的箝制元件面積下改善200%。

目於在類比電路中,積體電路的輸入電容不可太大,而且必需對輸入訊號的變化能有一穩定值,但為承受理想的靜電放電耐受能力,靜電放電防護元件通常具有較大的接面電容值,而且對電壓的變化及相當敏感。因此,在對元件啟動的特性了解後,本論\亦提出在類比電路中設計靜電放電防護電路的解決方案。且此設計理念,在 0.35 微米金筝半製程中,可以設計出 50 微米/0.5 微米大小的輸入/輸出極,使得整個輸入電容降到只有  $\sim 0.4 pF$ ,而在人體模式及機械模式(Machine Model)的靜電放電防護測試下分別可以得到 6 kV 及 400 V 的靜電放電耐受力。在本論\口中,更對此設計方式做一深入的探討,而提出一整套完整的設計方法來遽用在所有類比電路的輸入/輸出設計中,使得輸入電容在隨 1 V 工作電壓變化範圍下能控制在 1%的誤差承。

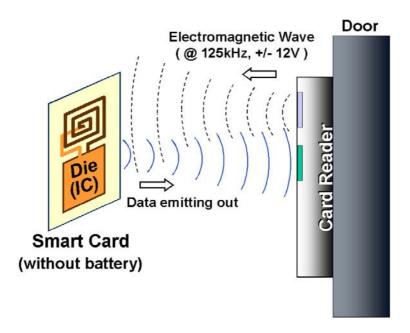

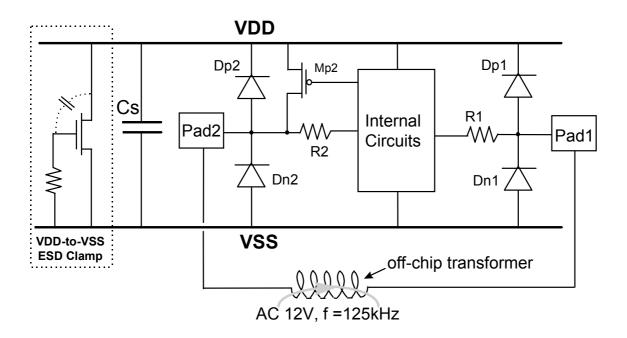

此外,目於二極體可以在積體電路的靜電放電防護之設計上廣泛應用,但目於傳統二極體在積體電路中會形成寄生的雙載子電晶體,因此在實際應用時會有難以控制的漏電電流的產生,在本論立中才首先提出利用複晶砂二極體(Polysilicon Diode)應用到積體電路的靜電放電防護設計上,自此可以設計出全面性的靜電放電防護電路,而利用堆疊的複晶砂二極體當靜電放電控制電路的方法,才設計出一個在設計電路時可以有放控制漏電電流的電源間靜電放電箝制電路。在本論立中,對複晶砂二極體的雜質慘稅了詳細的分析。此外,利用堆疊的複晶砂二極體亦可設計出一種新式具有低漏電電流的電源間靜電放電箝制電路,此種電路在整個積體電路設計之初,即可辜先模擬及安排,有效控制其在電源間的漏電電流。本論立將這些元件及電路實際應用到智慧卡(Smart Card)中,日整體的靜電放電防護設計下,可以成功地將原來只有300 V之人體模式靜電放電耐受力的產品,改善到大於3 kV。

# SUBSTRATE-TRIGGERED TECHNIQUE FOR ON-CHIP ESD PROTECTION DESIGN IN DEEP-SUBMICRON CMOS INTEGRATED CIRCUITS

Student: Tung-Yang Chen Advisor: Ming-Dou Ker

Department of Electronics Engineering and Institute of Electronics National Chiao Tung University

## **ABSTRACT**

This thesis includes physical analysis for the turn-on mechanisms of ESD protection devices during ESD stress and the applications of on-chip substrate-triggered ESD protection design. Gate-driven and substrate-triggered technologies are used to improve the turn-on efficiency of ESD (ElectroStatic Discharge) protection devices. From the analysis of the turn-on mechanisms of ESD protection device with gate-driven and substrate-triggered design in this thesis, it is proved that the substrate-triggered ESD protection design can continually improve the ESD robustness of protection devices in deep-submicron CMOS process. But, the gate-driven design has been confirmed to cause a sudden degradation on ESD robustness of the ESD protection devices. By using the substrate-triggered technique, the input, output, and power-rail ESD protection circuits are developed to enhance the ESD robustness of integrated circuits in deep-submicron CMOS process.

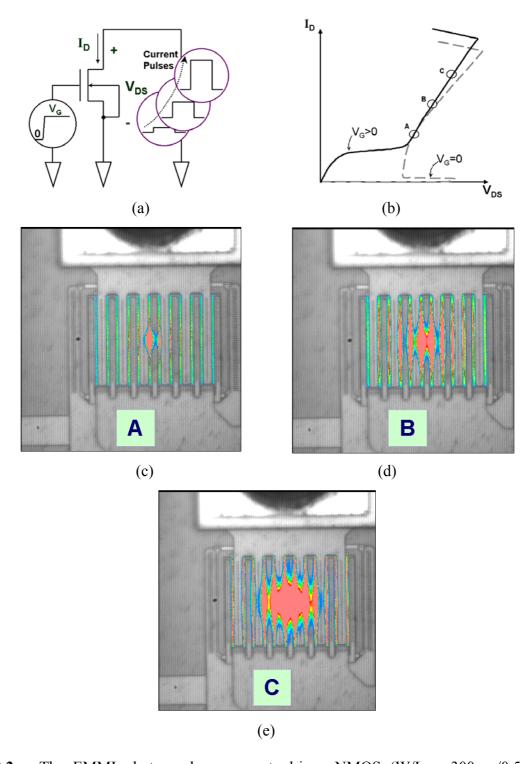

To understand the turn-on mechanisms of ESD protection device during ESD stress, the turn-on characteristics of those devices must be measured and analyzed. The energy band diagrams, EMMI (EMission MIcroscope) photographs, and TLP (Transmission Line Pulsing) measurement have been used to analyze and explain the physical turn-on mechanisms of ESD protection device. From the investigation of layout dependence on ESD robustness of NMOS and PMOS with finger-type layout, the turn-on mechanisms of ESD protection devices can be

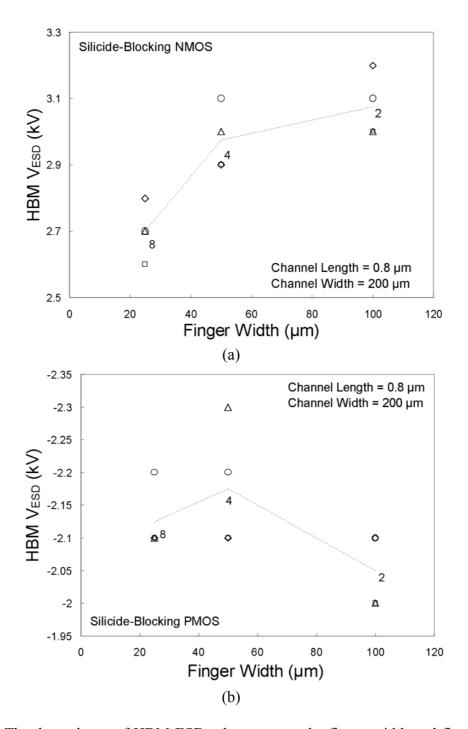

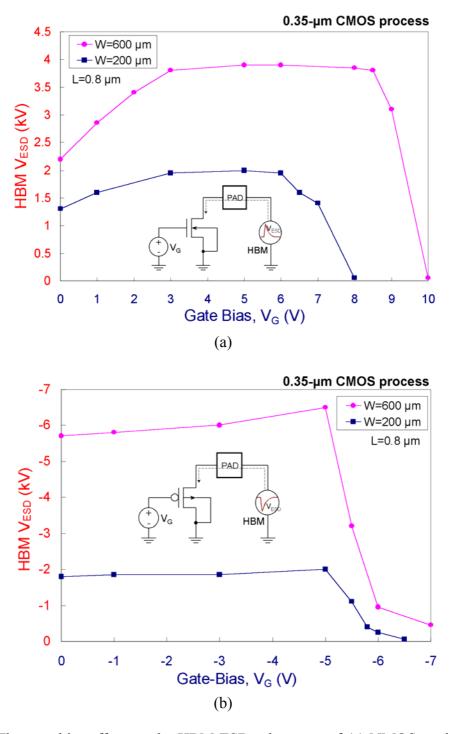

clearly understood to optimize the layout rules for the device dimensions, layout spacings, and clearances of those devices. To design high performance ESD protection device, some layout parameters must be optimized. The optimized layout parameters for a 0.35-µm CMOS process have been clearly investigated and analyzed in this thesis. To improve the ESD robustness of protection devices, gate-driven and substrate-triggered techniques have been developed. The gate-driven effect and substrate-triggered effect on ESD robustness of CMOS devices are also measured and compared in this thesis. The operation principles of gate-driven design and substrate-triggered design for ESD protection can be explained clearly by energy band diagrams and EMMI photographs. The experimental results have confirmed that the substrate-triggered design can effectively and continually improve ESD robustness of CMOS devices than the gate-driven design. But, the gate-driven design cannot continually improve ESD level of the device in the same deep-submicron CMOS process.

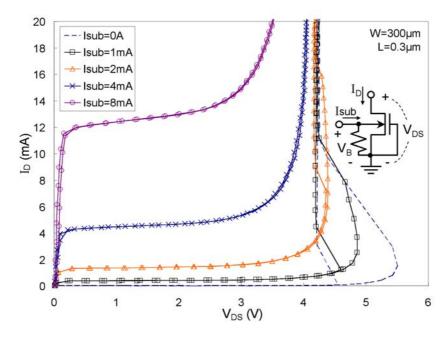

Full ESD protection design has became an important issue for integrated circuits in advanced deep-submicron CMOS process. To effectively improve ESD (electrostatic discharge) robustness of IC products, a novel substrate-triggered design for input, output, and power-rail ESD protection, as comparing to the traditional gate-driven technique, has been proposed in this thesis. With the substrate-triggered technique, the novel on-chip ESD protection circuits for the input, output, and power pins have been designed and verified in a 0.18-µm CMOS process. The HBM ESD robustness of output ESD protection circuits with ESD protection NMOS of W/L =  $300\mu m/0.3\mu m$  can be improved from the original 0.65 kV with the traditional gate-driven design to become 3.2 kV by the proposed substrate-triggered design. With aggressive device scaling, the circuit operating voltage had been decreased correspondingly. Some early 5-V systems changed from 5 V to 3.3 V, or even 1.8 V. Thus, system voltages were no longer 5 V but mixed with 5 V and 3.3 V. For mixed-voltage input design, the IC with 3.3-V power supply needs to accept 5-V input signals. A substrate-triggered technique is proposed to improve ESD protection efficiency of the ESD protection circuit without extra salicide-blocking and ESD-implantation process modifications in a salicided shallow-trench isolation (STI) CMOS process. By using layout technique, the proposed input ESD protection circuit can be merged into a compact device structure to enhance the substrate-triggered efficiency. This substrate-triggered design can increase the ESD robustness and reduce the trigger voltage of the ESD protection device. This substrate-triggered input ESD protection circuit with a field oxide device of channel width of 150 µm can sustain a HBM (Human-Body-Model) ESD level of 3250V without any extra

process modification. Comparing to the traditional ESD protection design of gate-grounded NMOS (gg-NMOS) with salicide-blocking process modification in a 0.25- $\mu$ m salicided CMOS process, the proposed substrate-triggered design without extra process modification can improve the ESD robustness per unit silicon area from the original 1.2 V/ $\mu$ m<sup>2</sup> of gg-NMOS to 1.73 V/ $\mu$ m<sup>2</sup>.

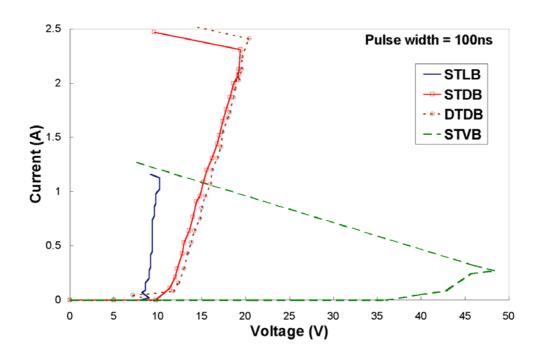

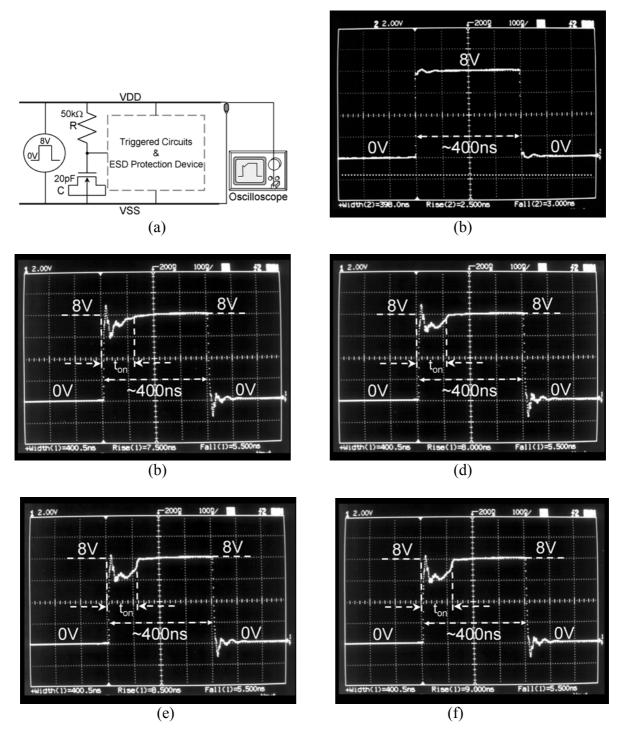

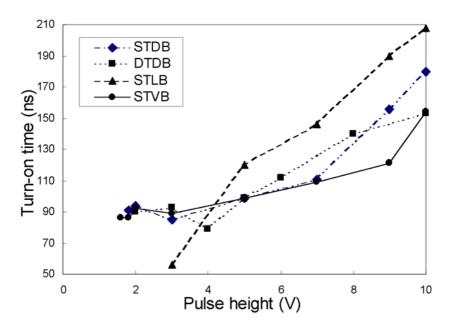

Four novel ESD clamp devices for using in power-rail ESD clamp circuits with the substrate-triggered technique are proposed to improve ESD level in this thesis. The parasitic n-p-n and p-n-p bipolar junction transistors (BJT) in the CMOS devices are used to form the substrate-triggered devices for ESD protection. Four substrate-triggered devices are proposed and investigated in this work, which are named as the substrate-triggered lateral BJT (STLB), the substrate-triggered vertical BJT (STVB), the substrate-triggered double BJT (STDB), and the double-triggered double BJT (DTDB). An *RC*-based ESD-detection circuit is used to generate the triggering current to turn on the proposed substrate-triggered devices. In order to trigger on the parasitic bipolar transistors more effectively, the symmetric multiple-cell square-type layout method is used to realize these substrate-triggered devices. The power-rail ESD clamp circuits with such substrate-triggered devices have been fabricated in a 0.6-μm CMOS process. Experimental results have shown that the substrate-triggered device with double-BJT structure can provide 200% higher ESD robustness in per silicon area, as compared to the NMOS with the traditional gate-driven design.

To keep the total input capacitance almost constant for analog IC design, a design model to find the optimized device dimensions and layout spacings on the input ESD clamp devices is developed in this work, even if the analog signal has a varying input voltage. An analog ESD protection circuit has been designed to solve ESD protection challenge on the analog pins for high-frequency applications. The device dimension (W/L) of ESD protection device connected to the I/O pad can be reduced to only 50μm/0.5μm in a 0.35-μm silicided CMOS process, but it can sustain HBM (MM) ESD level up to 6kV (400V). With such a smaller device dimension, the input capacitance of this analog ESD protection circuit can be significantly reduced to only ~0.4pF for high-frequency applications. This input capacitance can be further reduced if the ESD protection devices are designed with smaller device dimensions. Moreover, by using the optimized layout design to draw the layout of ESD protection NMOS and PMOS devices, the voltage-dependent variation on input capacitance of this analog ESD protection circuit can be kept below 1% under an input voltage swing of 1V. With such almost constant input capacitance, the nonlinear distortion causing by on-chip

ESD protection circuit can be minimized for high-precision applications.

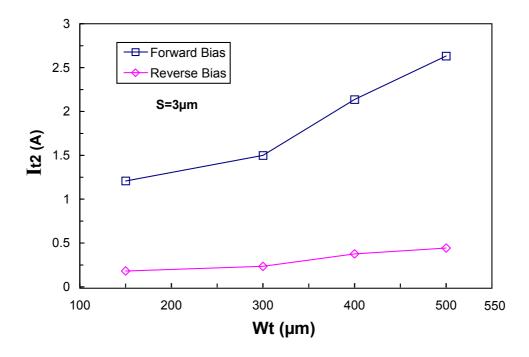

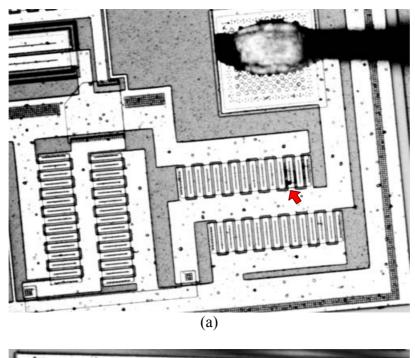

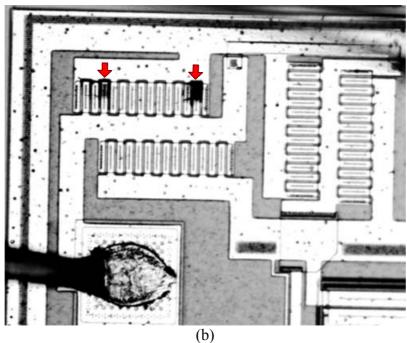

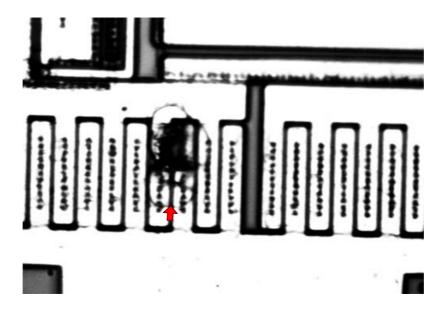

A novel on-chip ESD protection design by using polysilicon diodes as the ESD clamp devices in CMOS process is first proposed in this work. Different process splits have been experimentally evaluated to find the suitable doping concentration for optimizing the polysilicon diodes for both on-chip ESD protection design and the application requirements of the smart card IC's. The secondary breakdown current (It2) of the polysilicon diodes under the forward- and reverse-bias conditions has been measured by the transmission-line-pulsing (TLP) generator to investigate its ESD robustness. Moreover, by adding a new power-rail ESD clamp circuit with the stacked polysilicon diodes as the turn-on control circuit into the IC, the human-body-model (HBM) ESD robustness of the IC with polysilicon diodes as the ESD clamp devices has been successfully improved from the original ~300V to become ≥ 3kV. This design has been practically applied in a mass-production smart card IC.

# 誌 謝

首先要感謝我的指導教授柯明道博士及之前共后指導的吳重雨教授六年半來的耐心指導與鼓勵,使我能順利完成二年的碩士及四年半的博士學業。特別是在柯教授循序漸進的教誨下,讓我得以在積體電路靜電放電防護設計的領域中,日入門到能夠獨立解決問題,特別在論立的寫作技巧方面,柯教授夏是耐心地教導及糾正我許許多多錯誤的壞習慣,雖經柯教授多次的修正,然而弟子不才,在立中如果還有疏漏,實為弟子個人的因素,故請包函;而在吳教授的指導下,夏讓我獲得許多積體電路設計上的實責期前正確態度與方法。雖然在過程中倍感艱辛,然而卻獲益良多,夏促使我成長。另外也要感謝和藹可親的吳師母曾昭玲女士及柯師母連淑娟女士,特別是感謝吳師母對我及承人生活上的幫忙。此外還要感謝實驗室中另外所位教授,吳介琮及吳錦川教授也給了我許多指導。

在這段水學的過程中,積體電路與系統實驗室是孕育我成長的溫床, 日學長、戶學及學弟們在長期的努力下,使得我們無論在軟體及硬體的需 水上能夠一應俱全。而 在如此的環境下,無論與學長、戶學及學弟間在學 業上 的互相切磋,或共后海實驗室的運作而付出心力,都使得我在學業及 **處辜上,能有夏深一層的受惠,√因此我的論♡才得以順利完成。在此感** 謝陳志成、藍正豐、許恆壽、謝志成、姜信欽、張恆祥、曾玉光、蕭碩源、 陳巍仁、余邦政、洪浩評、顏·丁正、陳宏偉、林子超、黃建章、楊亞倫諸 位實驗室學長曾經給我的各種指導,以及育宏鑫、鄭秋宏、廖以義、施育 **全、黃冠勳、林俐如、唐忠昀、羅文裕、徐國鈞、洪根剛、莊健暉、莊哲** 豪、簡銘成、徐新智、本健銘、徐研訓、鈴明鏟、唐儒明諸位后學及學弟 妹們在我研究所的這一個階段,於各方面給了我不少點點瀋瀋的幫忙,而 使得我能順利地完成我的論文以及在知識及處事上有所成長。而特別感謝 歷任實驗室助理:邱怡玲小姐、李婷媛小姐以及小助理:蘇意文小姐、彭 筱均小姐在實驗室行政事務上的許協助;另外才感謝交大電子所的系所助 理陳美富小姐,幫我在學校事務上做各方面的聯絡通知;並感謝其化關心 我的師長及親朋好支們。

目於自碩士班開始六年半多的研究生活中,參與了許多的建教合作計畫,業界的協助著實對我的研究幫忙不少,從實驗晶片的下線機會,到實驗量測設備的支援協助,都是使得我的實驗研究能如此順利地完成之主要原因。在此要特別感謝工業技術研究院系統晶片技術中心的姜信欽、彭政傑、張智毅在實驗下線及量測上的幫忙;也感謝曾任於台灣積體電路公司的張恆祥、吳茂霖以及現任於台灣積體電路公司的王立泰、李國財在實驗下線及量測上的幫忙;並感謝聯華電子公司的唐天浩經理、陳正則副部長、

簡山傑部長、孫世偉副總在建教合作上的支持,夏感謝在聯電與交大建教 合作中歷年來實際參與計畫的黃恆盛、唐志 \ 、許世穎、唐天浩、陳孝賢 在實驗下線上的幫忙,以及曾任於聯電的蕭振高、管麗慧在實驗量測上的 支援;另外也感謝凌陽科技公司的王泰和在實驗資料上的提供以及實驗量 測的協助。夏感謝以上各公司機關所提供的優越環境,使得我部份的研究 論 \ 能在台灣及國際得獎,而獲得國際肯定。

最後,我要致上我最深最深的感謝給予我的父親陳靜修先生、母親陳莊麗華女士、岳父廖述宏先生、岳母廖詹青梅女士、姐姐陳意卿小姐、妹妹陳汀津小姐、弟弟陳太元先生,愛妻廖妙英小姐,與廖家的姊妹廖妙芳、廖妙貞、廖珠玄、廖雅莉小姐及小弟廖育震,以及連襟陳雄章、賴永章先生,沒有您們無怨悔、永無止境的付出、鼓勵、支持與照顧,就沒有我今日的成就。也感激父母親及姐姐代我照顧幼犬俊鴻的辛勞,使得我夏能專心於研究上,夏感激愛妻長年來的等待與陪伴,以及岳母在世時對我的心照顧,在此衷心地感謝您們。牙外,要祝福所有在這幾年與我相處過的師長、朋友、學弟妹們,有緣與您們旨在這一個階段成長,是我一生的榮幸,願大家都能順心如意,心想辜成!

陳 東 暘 諡誌於竹塹交大 九十一年 三月

# **CONTENTS**

| ABSTE | RACT (CHINESE)                                                             | i           |  |  |

|-------|----------------------------------------------------------------------------|-------------|--|--|

| ABSTE | RACT (ENGLISH)                                                             | iv          |  |  |

| ACKN  | ACKNOWLEDGEMENTS                                                           |             |  |  |

| CONT  | ENTS                                                                       | X           |  |  |

| TABLE | E CAPTIONS                                                                 | xiv         |  |  |

| FIGUR | RE CAPTIONS                                                                | xv          |  |  |

| CHAP  | TER 1 INTRODUCTION                                                         | 1           |  |  |

| 1.1   | BACKGROUND                                                                 | 1           |  |  |

| 1.2   | ESD TESTING COMBINATION ON IC                                              | 4           |  |  |

| 1.3   | THESIS ORGANIZATION                                                        | 6           |  |  |

| TA    | BLES                                                                       | 9           |  |  |

| FIC   | GURES                                                                      | 10          |  |  |

| CHAP  | TER 2 DEPENDENCE OF LAYOUT PARAMETERS ON ESD<br>ROBUSTNESS OF CMOS DEVICES | 14          |  |  |

| 2.1   | TURN-ON MECHANISM OF MOSFET UNDER ESD STRESS                               | 14          |  |  |

| 2.2   | LAYOUT DEPENDENCE                                                          | 17          |  |  |

|       | 2.2.1 Channel Width and Silicide Effect                                    | 17          |  |  |

|       | 2.2.2 Channel Length                                                       | 20          |  |  |

|       | 2.2.3 Clearance from Drain/Source Contact to Poly-Gate Edge                | 24          |  |  |

|       | 2.2.4 Spacing from Drain Diffusion to Guardring Diffusion                  | 27          |  |  |

|       | 2.2.5 Unit-Finger Width                                                    | 27          |  |  |

| 2.3   | SUMMARY                                                                    | 29          |  |  |

| TA    | BLES                                                                       | 30          |  |  |

| FIC   | GURES                                                                      | 31          |  |  |

| CHAP  | FER 3 GATE-DRIVEN EFFECT VERSUS SUBSTRATE-TRIGGEREI EFFECT                 | <b>)</b> 48 |  |  |

| 3.1   | GATE-DRIVEN EFFECT                                                         | 48          |  |  |

|       | 3.1.1 Turn-on Mechanism of Gate-Driven Design                              | 48          |  |  |

|       | 3.1.2 Experimental Results                                                 | 50          |  |  |

| 3.2   | SUBSTRATE-TRIGGERED EFFECT                                                 | 51          |  |  |

|       | 3.2.1 Turn-on Mechanism of Substrate-Triggered Design                      | 51          |  |  |

|       | 3.2.2 Experimental Results                                                 | 52          |  |  |

|    | 3.3  | SUN        | MMARY                                                                         | 53  |

|----|------|------------|-------------------------------------------------------------------------------|-----|

|    | FIG  | URES       |                                                                               | 54  |

| СН | [AP] | TER 4      | ON-CHIP ESD PROTECTION CIRCUITS DESIGN BY USING SUBSTRATE-TRIGGERED TECHNIQUE | 62  |

|    | 4.1  | SUB        | STRATE-TRIGGERED ESD PROTECTION DEVICE                                        | 62  |

|    |      | 4.1.1      | Device Structure                                                              | 62  |

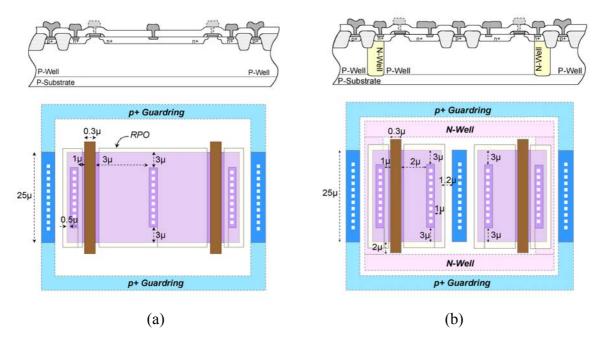

|    |      | 4.1.2      | Device Characteristics                                                        | 63  |

|    | 4.2  | ESD<br>DES | PROTECTION CIRCUITS WITH SUBSTRATE-TRIGGERED IGN                              | 64  |

|    |      | 4.2.1      | Input ESD Protection Circuits                                                 | 64  |

|    |      | 4.2.2      | Output ESD Protection Circuit                                                 | 67  |

|    |      | 4.2.3      | Power-Rail ESD Clamp Circuit                                                  | 68  |

|    | 4.3  | EXP        | PERIMENTAL RESULTS                                                            | 69  |

|    |      | 4.3.1      | HBM ESD test Results                                                          | 70  |

|    |      | 4.3.2      | Turn-on Verification                                                          | 71  |

|    | 4.4  | SUN        | MARY                                                                          | 72  |

|    | FIG  | URES       |                                                                               | 74  |

| СН | [AP] | TER 5      | SUBSTRATE-TRIGGERED ESD PROTECTION CIRCUIT WITHOUT EXTRA PROCESS MODIFICATION | 88  |

|    | 5.1  | SUB        | STRATE-TRIGGERED ESD PROTECTION CIRCUIT                                       | 89  |

|    |      | 5.1.1      | The Substrate-triggered Input ESD Protection Circuit                          | 89  |

|    |      | 5.1.2      | Alternative Substrate-triggered Input ESD Protection Circuit                  | 91  |

|    |      | 5.1.3      | Realization of Substrate-Triggered ESD Protection Circuits                    | 91  |

|    | 5.2  | EXP        | PERIMENTAL RESULTS                                                            | 93  |

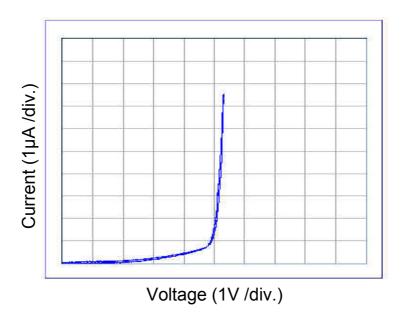

|    |      | 5.2.1      | Device Characteristics                                                        | 93  |

|    |      | 5.2.2      | TLP Measurement                                                               | 94  |

|    |      | 5.2.3      | ESD Test                                                                      | 95  |

|    | 5.3  | MO         | DIFIED DESIGN WITH ENHANCED TURN-ON SPEED                                     | 95  |

|    | 5.4  | SUN        | MARY                                                                          | 96  |

|    | FIG  | URES       |                                                                               | 98  |

| СН | [AP] | TER 6      | POWER-RAIL ESD CLAMP CIRCUITS WITH SUBSTRATE-<br>TRIGGERED TECHNIQUE          | 106 |

|    | 6.1  | SUB        | STRATE-TRIGGERED ESD CLAMP DEVICES                                            | 107 |

|    |      | 6.1.1      | Substrate-Triggered Lateral BJT (STLB) Device                                 | 108 |

|    |      | 6.1.2      | Substrate-Triggered Vertical BJT (STVB) Device                                | 109 |

|    |      | 613        | Substrate-Triggered Double BIT (STDB) Device                                  | 109 |

|       | 6.1.4 <u>D</u> ouble- <u>Triggered D</u> ouble <u>B</u> JT (DTDB) Device                       | 110 |

|-------|------------------------------------------------------------------------------------------------|-----|

| 6.2   | CIRCUIT SIMULATION                                                                             | 111 |

|       | 6.2.1 ESD Stress Condition                                                                     | 111 |

|       | 6.2.2 VDD Power-on Condition                                                                   | 112 |

| 6.3   | EXPERIMENTAL RESULTS                                                                           | 113 |

|       | 6.3.1 Device Characteristics                                                                   | 113 |

|       | 6.3.2 ESD Performance and TLPG I-V Curves                                                      | 114 |

|       | 6.3.3 Turn-On Verification                                                                     | 116 |

|       | 6.3.4 Power-Rail Noise Clamping                                                                | 117 |

| 6.4   | SUMMARY                                                                                        | 118 |

| FIG   | GURES                                                                                          | 120 |

| СНАРТ | TER 7 ANALOG ESD PROTECTION CIRCUIT WITH LOW INPUT CAPACITANCE FOR HIGH-FREQUENCY APPLICATIONS | 134 |

| 7.1   | ANALOG ESD PROTECTION CIRCUIT                                                                  | 135 |

| 7.2   | LAYOUT DESIGN ON THE INPUT CAPACITANCE                                                         | 137 |

|       | 7.2.1 Calculation on the Input Capacitance                                                     | 138 |

|       | 7.2.2 Layout Design to Minimize Capacitance Variation                                          | 140 |

|       | 7.2.3 Calculation Results                                                                      | 142 |

| 7.3   | SUMMARY                                                                                        | 145 |

| TAI   | BLES                                                                                           | 147 |

| FIG   | GURES                                                                                          | 148 |

| СНАРТ | TER 8 ON-CHIP ESD PROTECTION DESIGN BY USING POLYSILICON DIODES IN CMOS PROCESS                | 159 |

| 8.1   | ORIGINAL DESIGN IN A SMART CARD IC                                                             | 161 |

| 8.2   | NEW ON-CHIP ESD PROTECTION DESIGN                                                              | 162 |

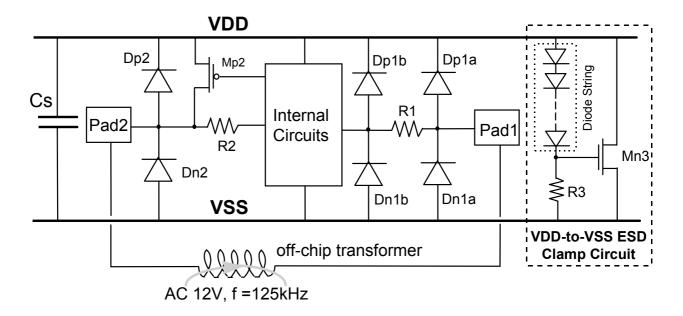

|       | 8.2.1 ESD Protection Circuit                                                                   | 163 |

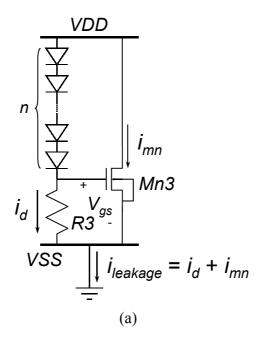

|       | 8.2.2 Leakage Current in the VDD-to-VSS ESD Clamp Circuit                                      | 164 |

|       | 8.2.3 Process Splits                                                                           | 165 |

| 8.3   | DEPENDENCE OF LAYOUT PARAMETERS ON It2 OF POLYSILICON DIODES                                   | 165 |

| 8.4   | EXPERIMENTAL RESULTS AND DISCUSSION                                                            | 167 |

|       | 8.4.1 ESD Test and Failure Analysis                                                            | 167 |

|       | 8.4.2 Turn-on Verification                                                                     | 168 |

| 8.5   | SUMMARY                                                                                        | 169 |

| 8.6   | APPENDIX                                                                                       | 169 |

| PUBLICATION LIST                       | 208 |

|----------------------------------------|-----|

| VITA                                   | 207 |

| REFERENCES                             | 197 |

| TABLES                                 | 190 |

| TABLES                                 | 196 |

| 9.2 FUTURE WORKS                       | 194 |

| 9.1 MAIN RESULTS OF THIS THESIS        | 192 |

| CHAPTER 9 CONCLUSIONS AND FUTURE WORKS | 192 |

| FIGURES                                | 174 |

| TABLES                                 | 172 |

## TABLE CAPTIONS

## **CHAPTER 1**

**Table 1.1** The summary of ESD protection design methods in CMOS IC's.

## **CHAPTER 2**

**Table 2.1** The device parameters and calculated effective total turn-on area of NMOS and PMOS with the same total channel width (W=200μm) in equation (2.14).

## **CHAPTER 7**

- **Table 7.1** ESD level of the analog ESD protection circuit in human-body-model (HBM) and machine-model (MM) ESD stresses under different pin combinations.

- **Table 7.2** *SPICE* parameters on the drain capacitance of NMOS and PMOS devices in a 0.35-µm silicided CMOS process.

## **CHAPTER 8**

- **Table 8.1** HBM ESD level of a smart-card IC with the original ESD protection design under different n-doping concentrations.

- **Table 8.2** Process splits on the n-doping concentration to investigate the breakdown voltage and the forward-biased current of the polysilicon diodes.

- **Table 8.3** Process splits on the p-doping concentration to investigate the breakdown voltage and the forward-biased current of the polysilicon diodes.

- **Table 8.4** HBM ESD level of the smart-card IC with the new proposed ESD protection design.

## **CHAPTER 9**

**Table 9.1** The discrimination between the ESD protection design methods in this thesis and prior arts.

## FIGURE CAPTIONS

## CHAPTER 1

- Fig. 1.1 Typical on-chip ESD protection circuits in a CMOS IC.

- **Fig. 1.2** Illustration of the traditional finger-type ESD protection device layout for input or output pads.

- **Fig. 1.3** (a) Positive and negative ESD stress on an input (or output) pin with respect to the grounded VSS. (b) Positive and negative ESD stress on an input (or output) pin with respect to the grounded VDD. (c) The pin-to-pin ESD stress: the ESD voltage is applied to an input (or output) pin while all other input or output pins are grounded but the VDD and VSS pins are floating. (d) The VDD-to-VSS ESD stress: the ESD voltage is directly applied to the VDD pin with the VSS pin grounded but all input and output pins are floating.

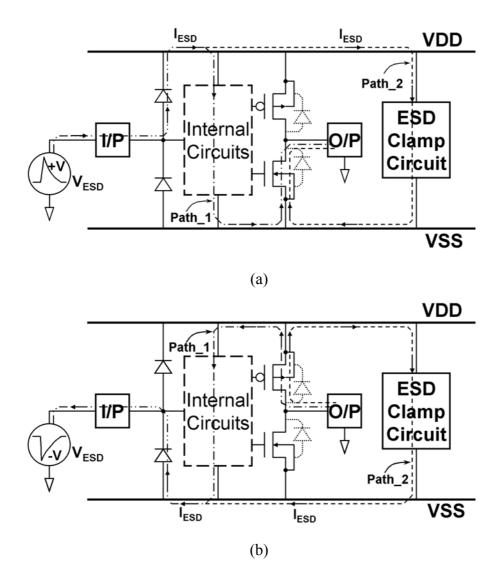

- Fig. 1.4 The ESD current discharging paths in an IC during the (a) positive, and (b) negative, pin-to-pin ESD stress conditions. If the IC has no effective ESD clamp circuit between the VDD and VSS power rails, the ESD current is discharged through the Path\_1, which often causes ESD damage located at the internal circuits. If the IC has an effective ESD clamp circuit between the VDD and VSS power rails, the ESD current is discharged through the Path\_2.

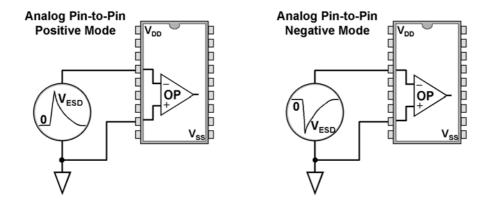

- **Fig. 1.5** Pin combination of the additional analog pin-to-pin ESD stress to verify the ESD level of analog circuits with the operational amplifier or differential input stage.

- **Fig. 1.6** ESD current path during the analog pin-to-pin ESD stress.

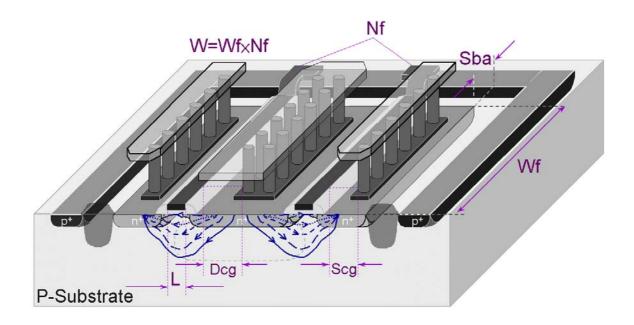

- **Fig. 2.1** 3-D structure of finger-type NMOS device with layout parameters.

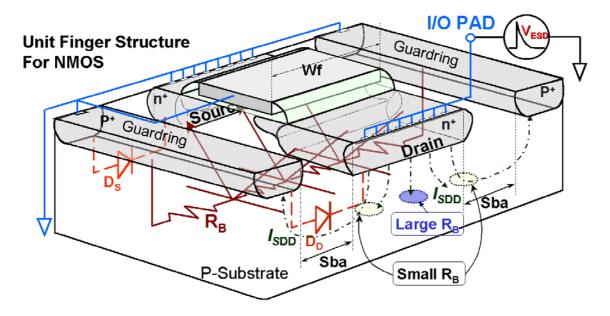

- **Fig. 2.2** Illustration of the parasitic devices and layout parameters in a unit-finger structure of a multiple-finger NMOS.

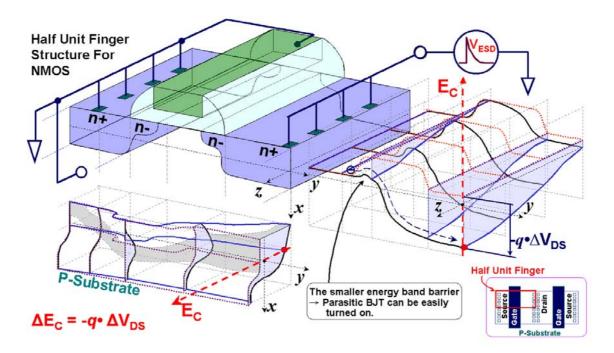

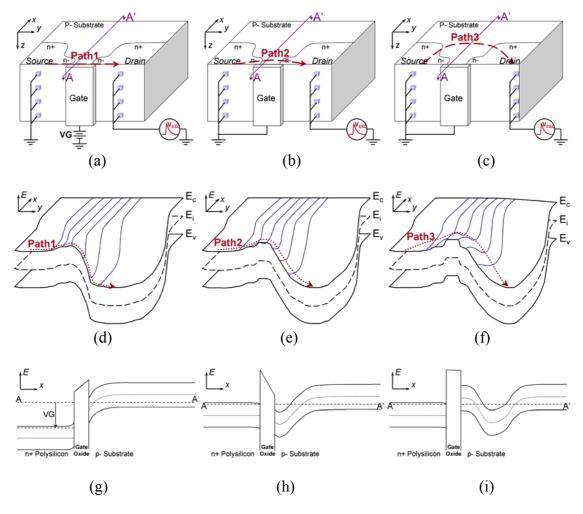

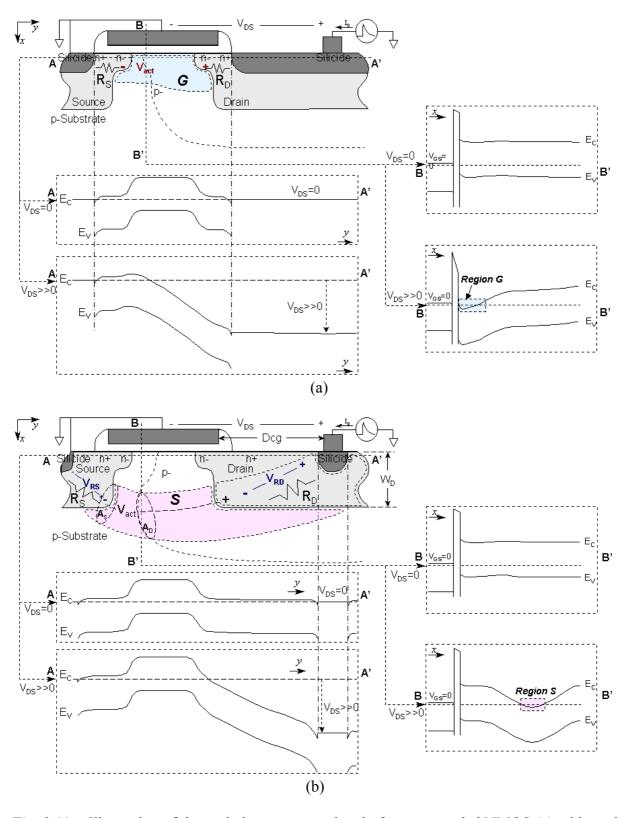

- **Fig. 2.3** Analysis of conduction energy band diagrams for a half unit-finger NMOS during positive ESD stress.

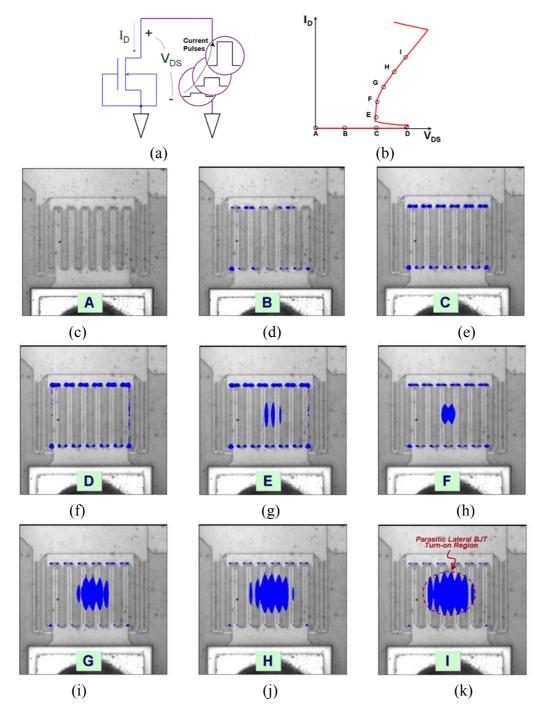

- Fig. 2.4 The EMMI photographs on a gate-ground NMOS (W/L = 300μm/0.5μm) to observe its turn-on behavior under the stress of different pulsed currents. (a) The measurement setup, (b) the corresponding I-V curve of a gate-grounded NMOS,

- (c)-(f) the hot spots in the gate-grounded NMOS before it enters into snapback region, and (g)-(k) the hot spots in the gate-grounded NMOS after it enters into snapback region.

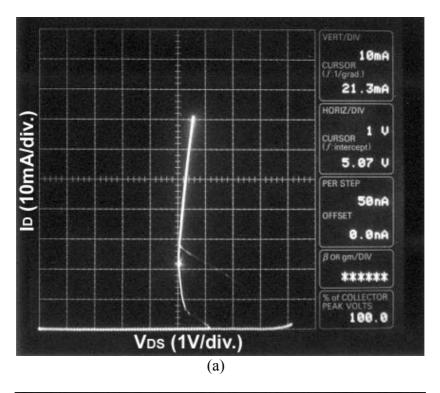

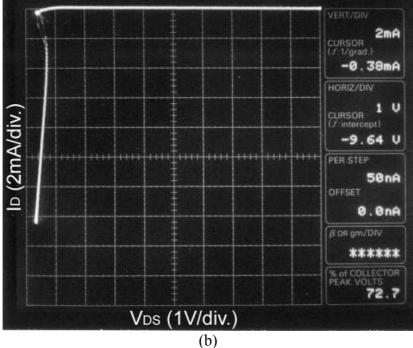

- **Fig. 2.5** The measured snapback I-V curves of (a) NMOS, and (b) PMOS, with a channel length of 0.35μm.

- Fig. 2.6 Illustrations of energy band diagram for a non-silicided NMOS with different stress conditions. (a), (b), and (c) show devices under different biases. (d), (e), and (f) show two-dimension band diagrams of NMOS in the corresponding conditions of (a), (b), and (c), respectively. (g), (h), and (i) show the x-axis band diagrams along the line A-A' of NMOS in (a), (b), and (c), respectively. A gate voltage of VG is applied on the gate of NMOS in (a).

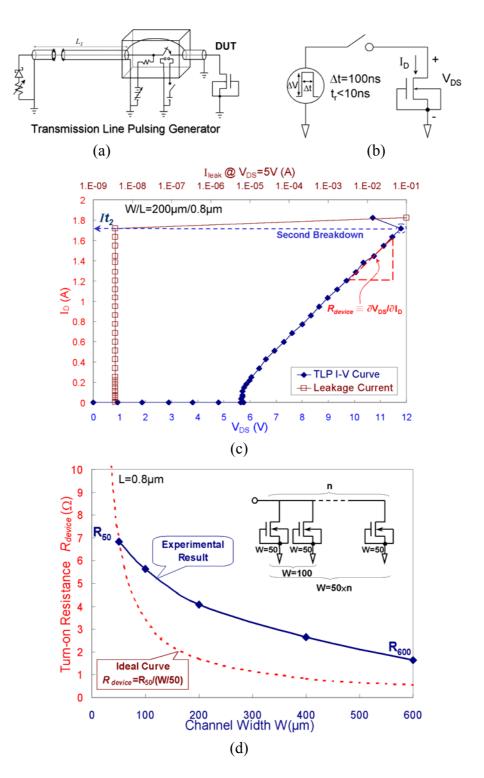

- **Fig. 2.7** (a) Illustration of transmission line pulsing generator (TLPG). (b) The corresponding circuit for TLPG measurement on a gate-grounded NMOS. (c) The measured I-V characteristics and leakage currents of NMOS by TLP with a pulse width of 100 ns. (d) The turn-on resistances of finger-type NMOS devices with different channel widths, but with the same unit-finger width and channel length.

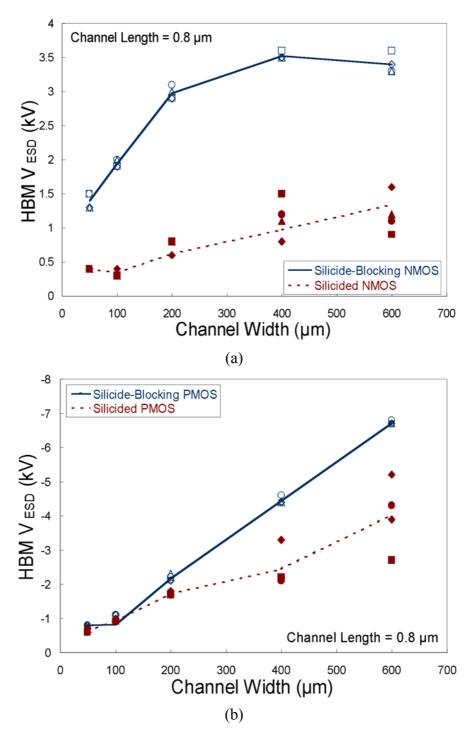

- **Fig. 2.8** The dependence of HBM ESD level on the channel width of (a) NMOS, and (b) PMOS, with or without silicided diffusion.

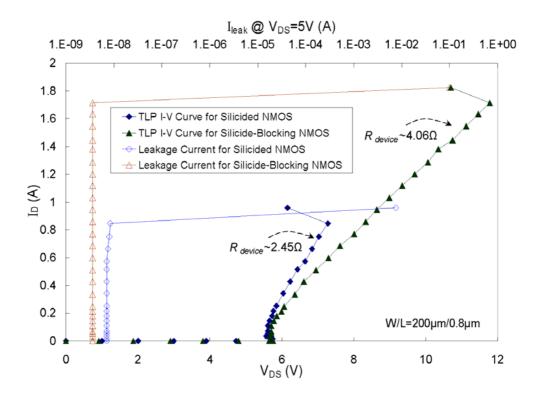

- Fig. 2.9 TLP measured I-V curves of NMOS devices with or without silicided diffusion, but with the same device dimension of  $W/L=200\mu m/0.8\mu m$ .

- **Fig. 2.10** Illustration of the variation on energy band of gate-grounded NMOS (a) with, and (b) without, silicided diffusion.

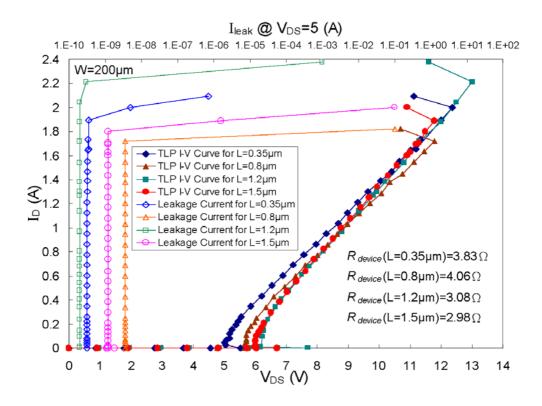

- **Fig. 2.11** TLP measured results for gate-grounded NMOS devices with different channel lengths (L=0.35μm, 0.8μm, 1.2μm, and 1.5μm).

- **Fig. 2.12** The dependence of HBM ESD level on the channel length of (a) NMOS, and (b) PMOS, with a fixed channel width of 200μm.

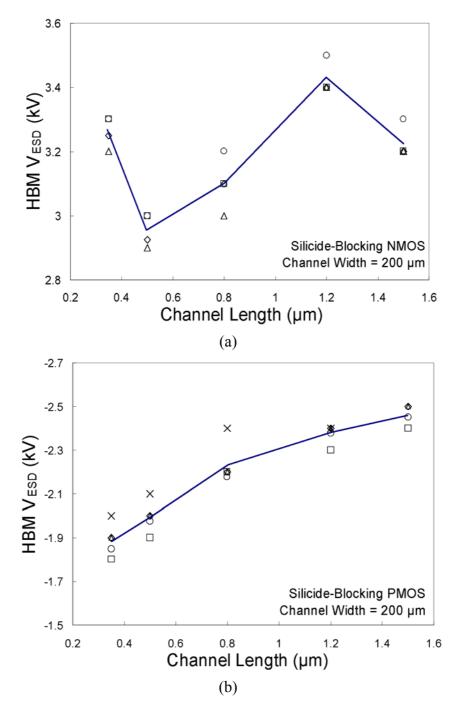

- **Fig. 2.13** Illustration of the variation on energy band of gate-grounded NMOS with (a) long, (b) normal, and (c) short, channel lengths.

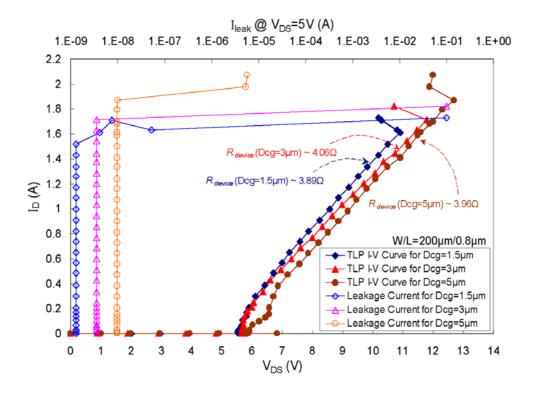

- Fig. 2.14 TLP measured I-V curves for NMOS devices with different Dcg parameters (Dcg =  $1.5\mu m$ ,  $3\mu m$ , and  $5\mu m$ ).

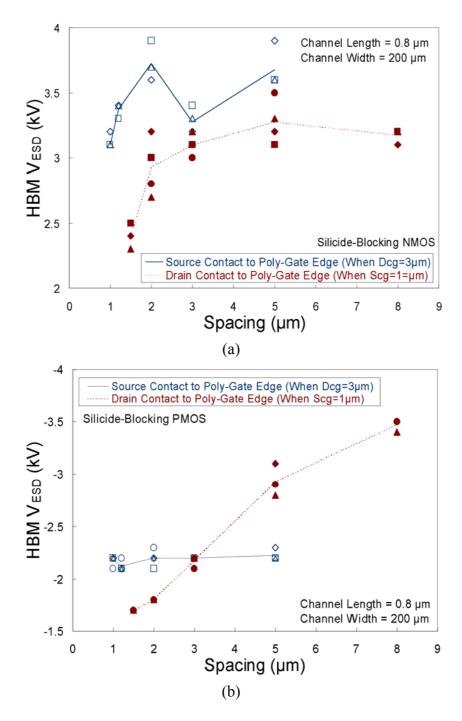

- **Fig. 2.15** The dependences of HBM ESD level on the clearance from the drain/source contact to poly-gate edge of silicide-blocking (a) NMOS, and (b) PMOS.

- Fig. 2.16 Illustration of the variation on energy band of gate-grounded NMOS with (a) small

- and (b) long, clearance of contact to poly-gate edge (Dcg).

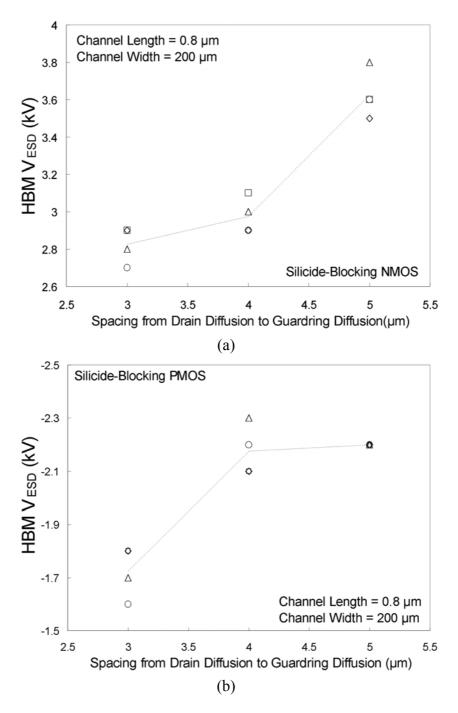

- **Fig. 2.17** The dependence of HBM ESD robustness on the Sba spacings of (a) NMOS, and (b) PMOS.

- **Fig. 2.18** The dependence of HBM ESD robustness on the finger width and finger number of (a) NMOS, and (b) PMOS, with W/L=200μm/0.8μm in the finger-type layout.

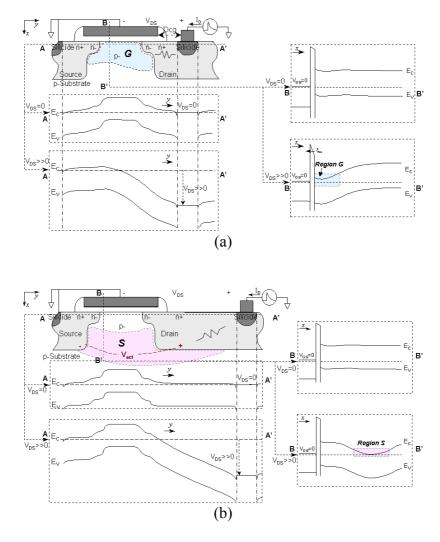

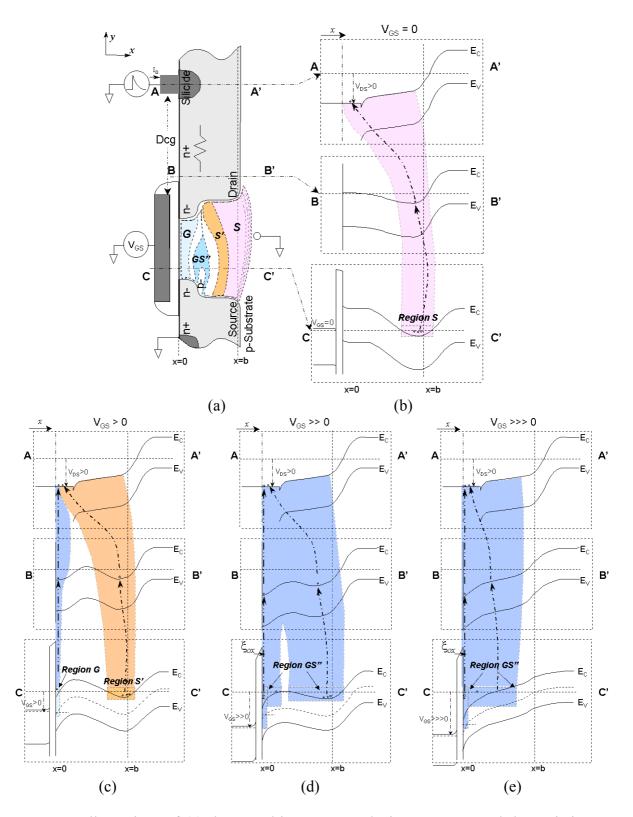

- Fig. 3.1 Illustrations of (a) the gate-driven NMOS device structure, and the variation on energy band of the gate-driven NMOS with different gate biases of (b)  $V_{GS}=0$ , (c)  $V_{GS}>0$ , (d)  $V_{GS}>>0$ , and (e)  $V_{GS}>>0$ .

- Fig. 3.2 The EMMI photographs on a gate-driven NMOS (W/L = 300μm/0.5μm) to observe its turn-on behavior under the stress of different pulsed currents. (a) The measurement setup, (b) the corresponding I-V curve of a gate-driven NMOS, (c)-(e) the hot spots in the gate-driven NMOS under different current stresses.

- **Fig. 3.3** The gate bias effect on the HBM ESD robustness of (a) NMOS, and (b) PMOS, without silicided diffusion in a 0.35-μm silicided CMOS process.

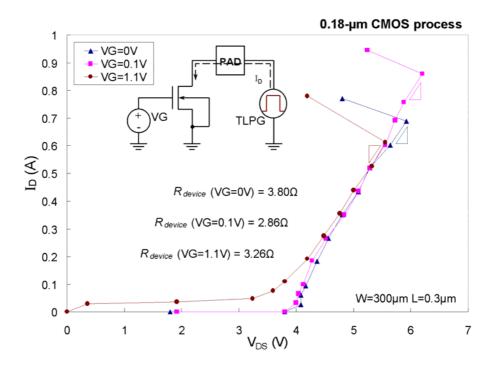

- **Fig. 3.4** TLP measured I-V curves and turn-on resistances of the gate-driven NMOS devices with silicide-blocking mask in a 0.18-μm salicided CMOS process.

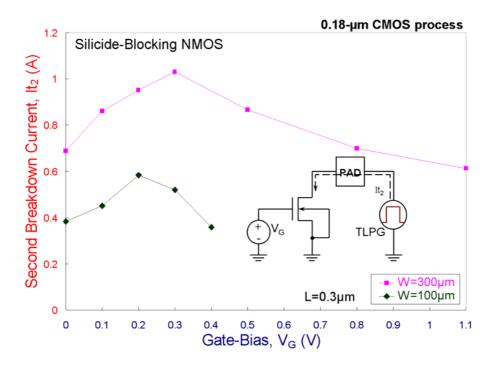

- Fig. 3.5 The gate-driven effect on the second breakdown current of silicide-blocking NMOS in a 0.18-μm salicided CMOS process.

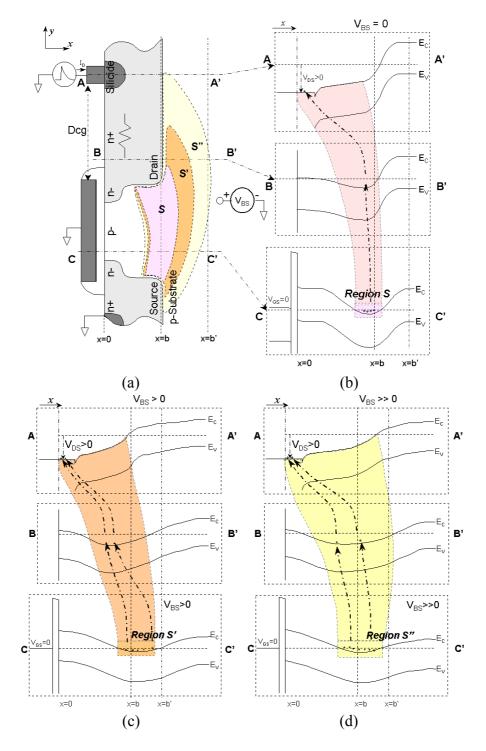

- Fig. 3.6 Illustrations of (a) the substrate-triggered NMOS device structure, and the variation on energy band of the substrate-triggered NMOS with different substrate biases of (b)  $V_{BS}$ =0, (c)  $V_{BS}$ >0, and (d)  $V_{BS}$ >>0.

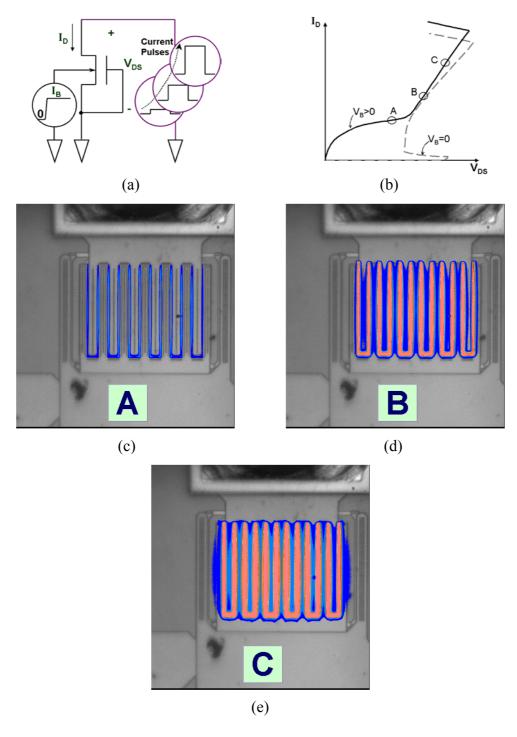

- Fig. 3.7 The EMMI photographs on a substrate-triggered NMOS (W/L =  $300\mu m/0.5\mu m$ ) to observe its turn-on behavior under the stress of different pulsed currents. (a) The measurement setup, (b) the corresponding I-V curve of a substrate-triggered NMOS, (c)-(e) the hot spots in the substrate-triggered NMOS under different current stresses.

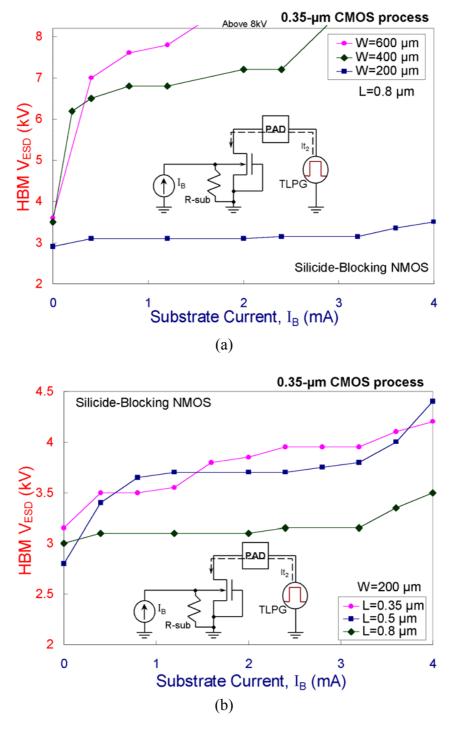

- **Fig. 3.8** The effect of substrate current on the ESD robustness of NMOS devices with (a) different channel widths, and (b) different channel lengths, in a 0.35-μm silicided CMOS process.

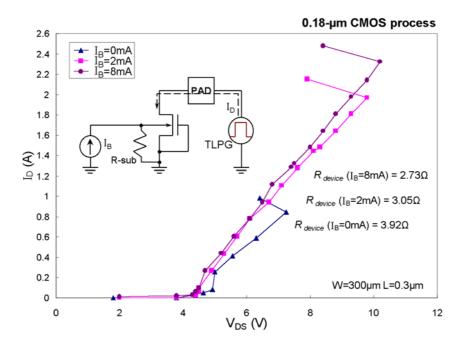

- **Fig. 3.9** TLP measured I-V curves and turn-on resistances of the substrate-triggered NMOS devices with silicide-blocking mask in a 0.18-µm salicided CMOS process.

**Fig. 3.10** The effect of substrate current on the ESD robustness of silicide-blocking NMOS devices with different channel widths in a 0.18-μm salicided CMOS process.

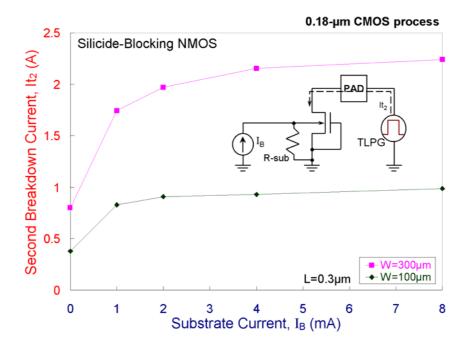

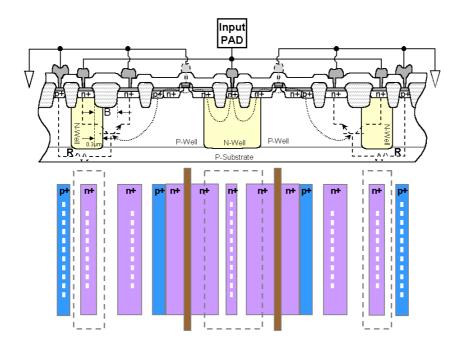

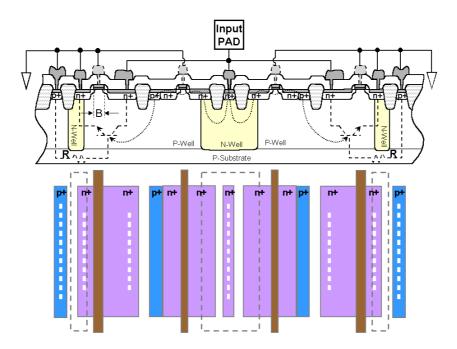

- **Fig. 4.1** Device structures and corresponding layout patterns of (a) the traditional finger-type NMOS, and (b) the proposed substrate-triggered NMOS, for ESD protection.

- **Fig. 4.2** The dc I-V curves of the substrate-triggered NMOS under different substrate current biases.

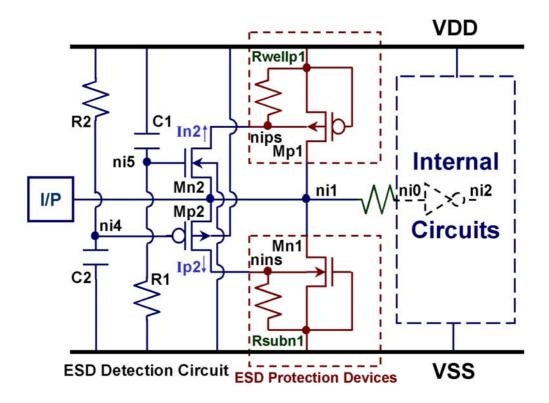

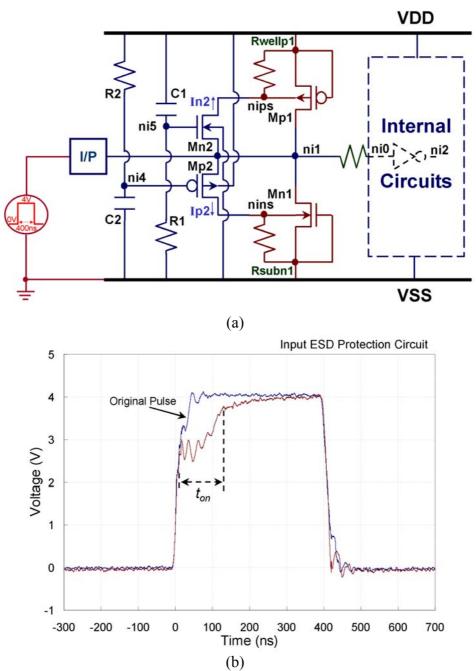

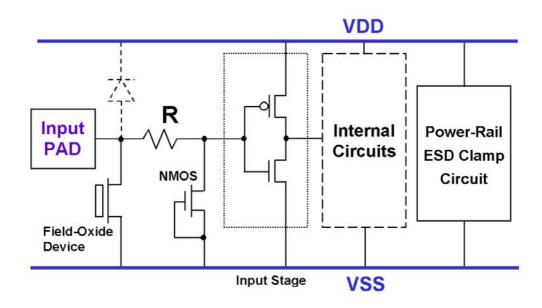

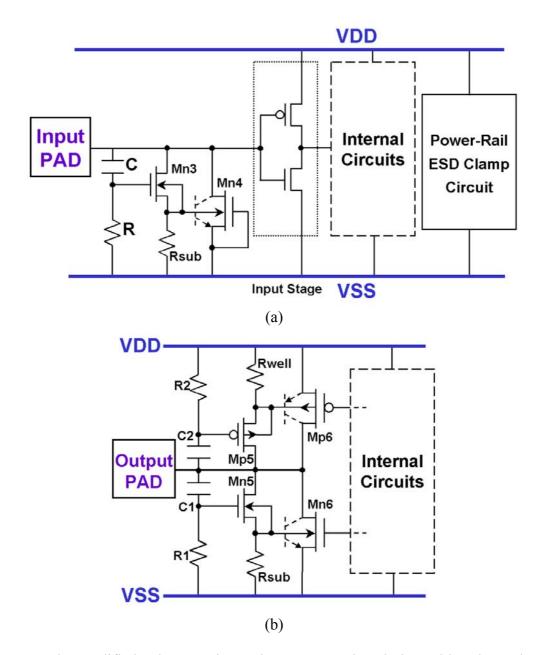

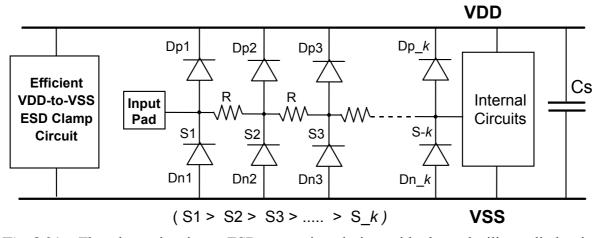

- **Fig. 4.3** The proposed input ESD protection circuit with substrate-triggered design.

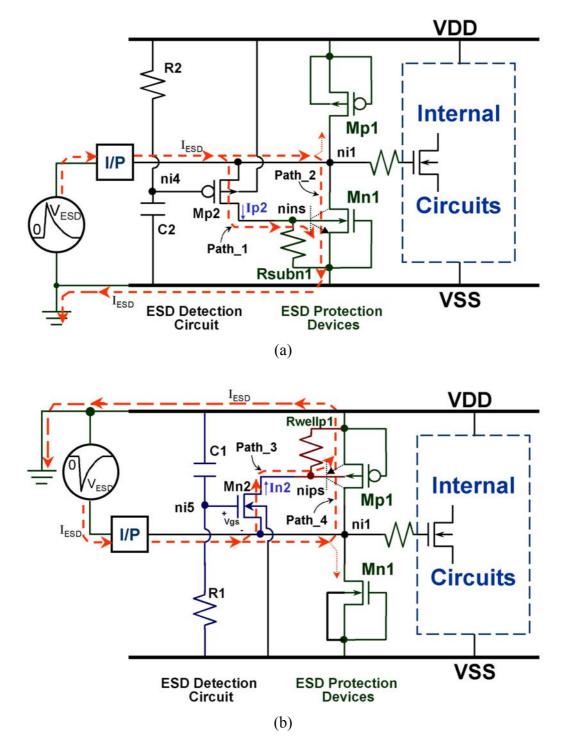

- **Fig. 4.4** Illustration of the ESD current paths in the half input ESD protection circuit with substrate-triggered design during (a) the positive-to-VSS ESD stress, and (b) the negative-to-VDD ESD stress.

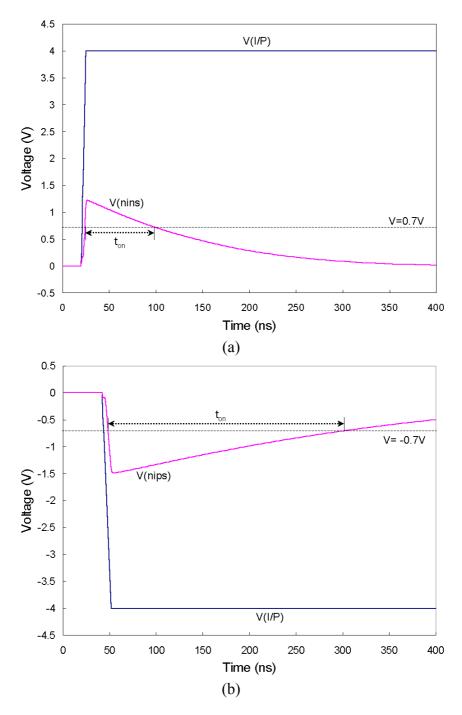

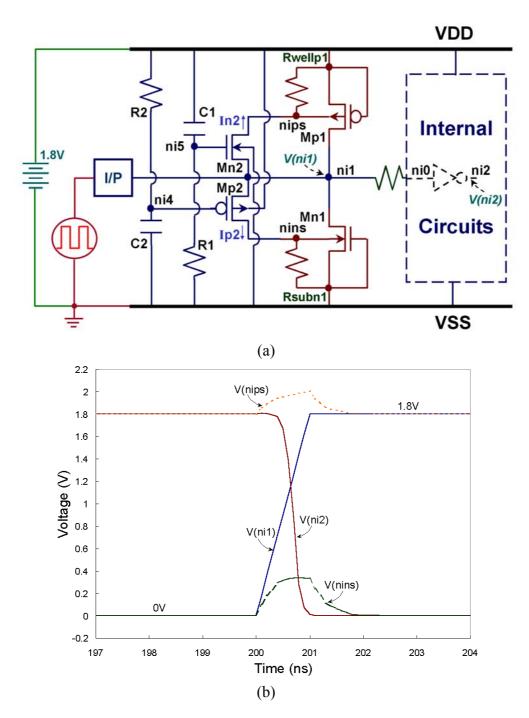

- **Fig. 4.5** *HSPICE* simulated voltage waveforms to find the turn-on time of the proposed input ESD protection circuit under (a) the positive-to-VSS ESD-stress condition, and (b) the negative-to-VDD ESD-stress condition.

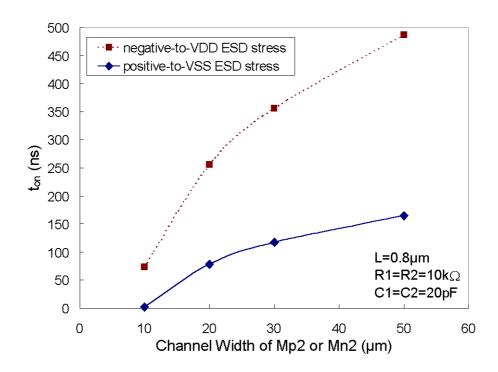

- **Fig. 4.6** The dependence between the turn-on time (t<sub>on</sub>) and the device dimension of Mp2 or Mn2 in the proposed input ESD protection circuit during positive-to-VSS or negative-to-VDD ESD-stress conditions.

- **Fig. 4.7** (a) The circuit setup to simulate the voltage transition in the proposed input ESD protection circuit under the normal circuit operating condition with a 0-to-1.8V input signal. (b) The simulated voltage waveforms on the nodes ni1, ni2, nins, and nips of the proposed input ESD protection circuit when the input signal is applied on the input pad (the node ni1).

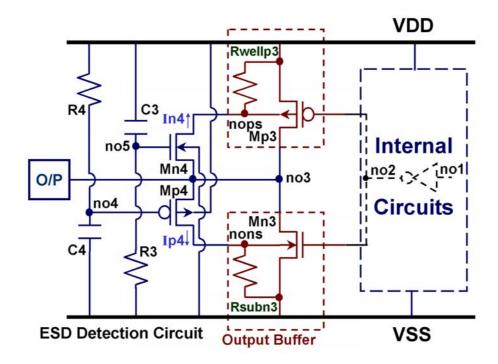

- **Fig. 4.8** Output ESD protection circuit with the proposed substrate-triggered design.

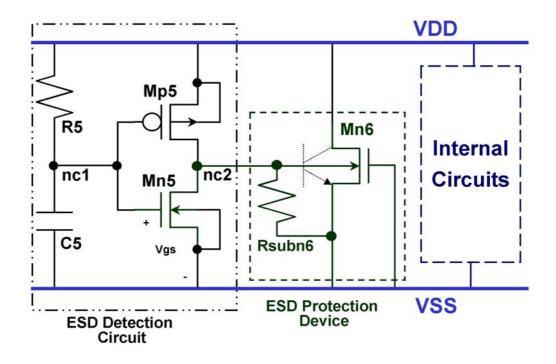

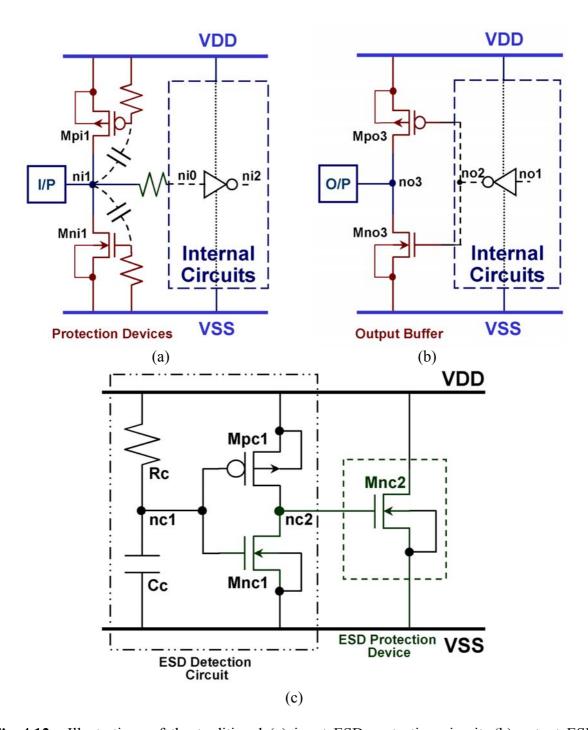

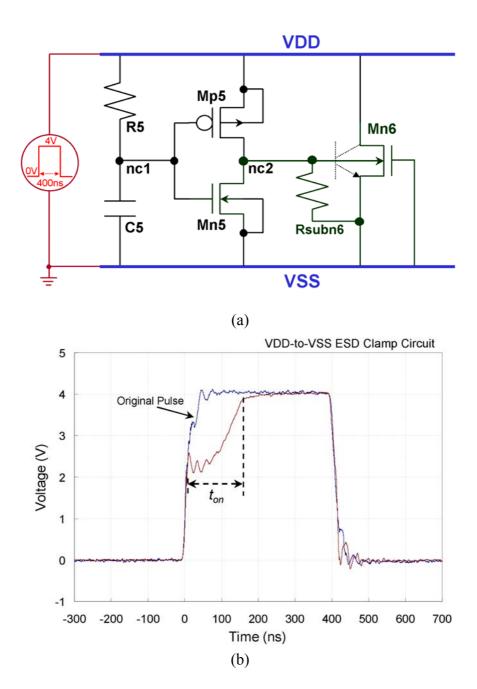

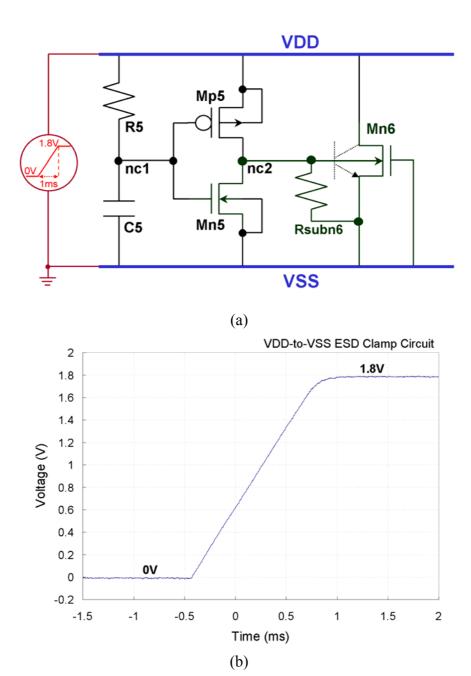

- **Fig. 4.9** Power-rail ESD clamp circuit with the proposed substrate-triggered design.

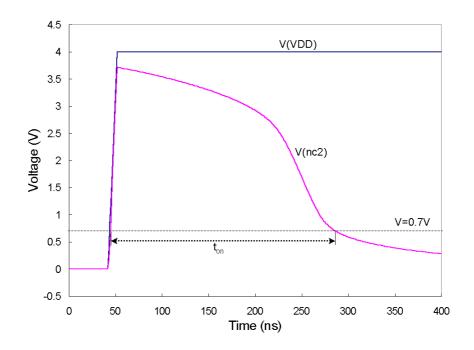

- **Fig. 4.10** The *HSPICE* simulated voltage waveforms on the VDD and the node nc2 of the proposed power-rail ESD clamp circuit under the positive ESD-stress condition, where a 4-V ramp voltage with a rise time of 10 ns is used to simulate the rising edge of an HBM ESD pulse.

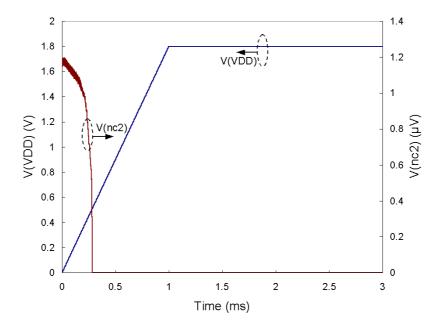

- **Fig. 4.11** The *HSPICE* simulated voltage waveforms on the VDD and the node nc2 of the proposed power-rail ESD clamp circuit under the normal power-on condition, where a 1.8-V ramp voltage with a rise time of 1 ms is applied to the VDD.

- **Fig. 4.12** Illustrations of the traditional (a) input ESD protection circuit, (b) output ESD protection circuit, and (c) power-rail ESD clamp circuit.

- **Fig. 4.13** Comparison on ESD robustness between the proposed substrate-triggered input ESD protection circuit and the traditional input ESD protection circuit.

- **Fig. 4.14** Comparison on ESD robustness between the proposed substrate-triggered output ESD protection circuit and the traditional output ESD protection circuit.

- **Fig. 4.15** Comparison on ESD robustness between the proposed substrate-triggered power-rail ESD clamp circuit and the gate-driven power-rail ESD clamp circuit.

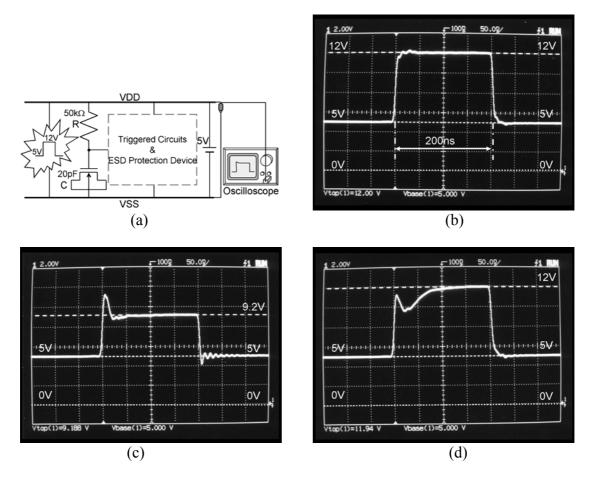

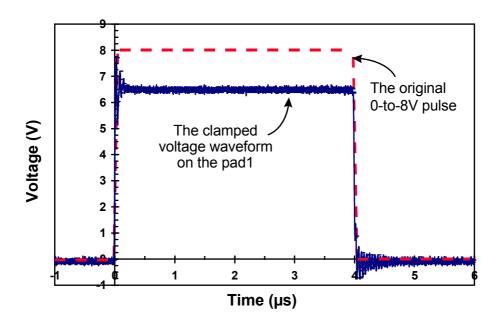

- Fig. 4.16 (a) The experimental setup to verify the turn-on efficiency of the proposed input ESD protection circuit with substrate-triggered design, where a 4-V voltage pulse with a rise time of ~10 ns is used to simulate the rising edge of a positive-to-VSS HBM ESD event. (b) Comparison between the original 0-to-4V voltage waveform generated from a pulse generator and the degraded voltage waveform on the input pad of the proposed input ESD protection circuit.

- **Fig. 4.17** (a) The experimental setup to verify the turn-on efficiency of the proposed power-rail ESD clamp circuit with substrate-triggered design, where a 4-V voltage pulse with a rise time of ∼10 ns is used to simulate the rising edge of a positive VDD-to-VSS ESD event. (b) Comparison between the original 0-to-4V voltage waveform generated from a pulse generator and the degraded voltage waveform on the VDD of the proposed power-rail ESD clamp circuit.

- **Fig. 4.18** (a) The experimental setup to verify the power-on transition of the proposed power-rail ESD clamp circuit with substrate-triggered design, where a 0-to-1.8V ramp voltage with a rise time of 1 ms is used to simulate the normal power-on event. (b) The measured voltage waveform on the VDD of the proposed power-rail ESD clamp circuit, which is not degraded by the power-rail ESD clamp circuit.

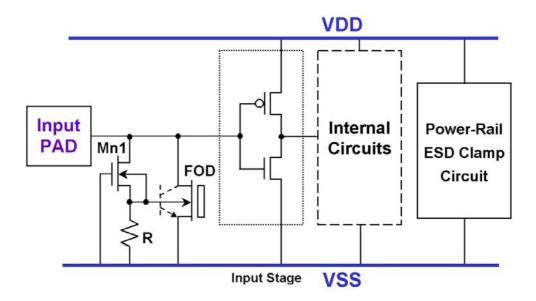

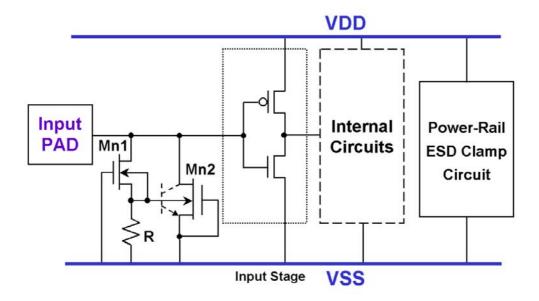

- Fig. 5.1 The traditional input ESD protection circuit for digital input pin in CMOS IC's.

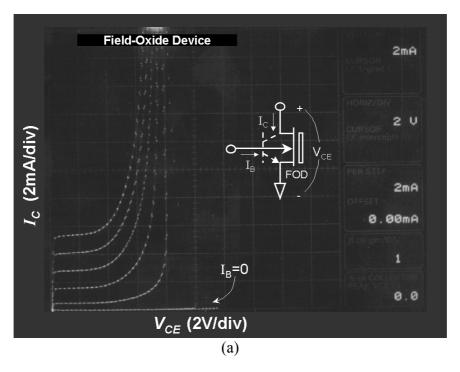

- **Fig. 5.2** The proposed substrate-triggered ESD protection circuit with field oxide device (FOD) to protect the thinner gate oxide of input stage.

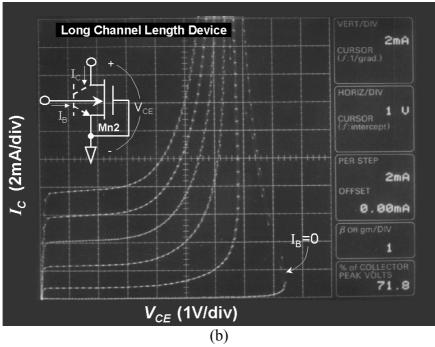

- **Fig. 5.3** An alternative design of the proposed substrate-triggered ESD protection circuit with long channel length NMOS to protect the thinner gate oxide of input stage.

- **Fig. 5.4** The merged device structure of the proposed input ESD protection circuit with substrate-triggered FOD in Fig. 5.2.

- **Fig. 5.5** The merged device structure of the alternative input ESD protection circuit with substrate-triggered NMOS Mn2 in Fig. 5.3.

- **Fig. 5.6** The measured DC I-V curve of a stand-alone (a) NMOS device, and (b) FOD, with a channel length of 2 μm under different substrate current biases.

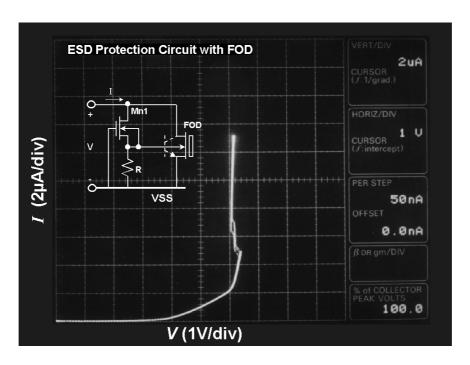

- **Fig. 5.7** The measured overall DC I-V curve of the proposed input ESD protection circuit with substrate-triggered FOD.

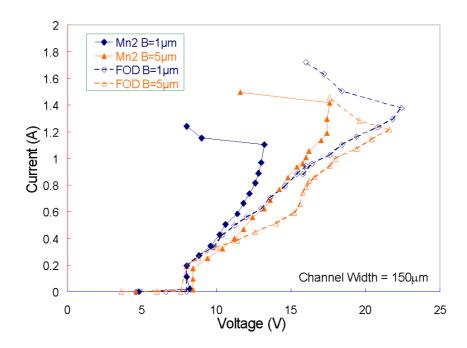

- **Fig. 5.8** The TLP measured I-V curves of the proposed input ESD protection circuits with NMOS Mn2 and FOD for different "B" spacings.

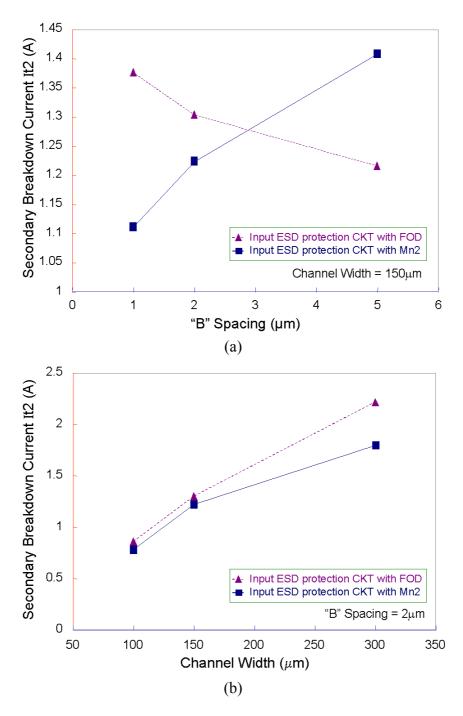

- **Fig. 5.9** The dependence of the It2 of the proposed input ESD protection circuits on (a) the "B" spacing, and (b) on the channel width, of the device structures in Fig. 5.4 (FOD) and Fig. 5.5 (Mn2).

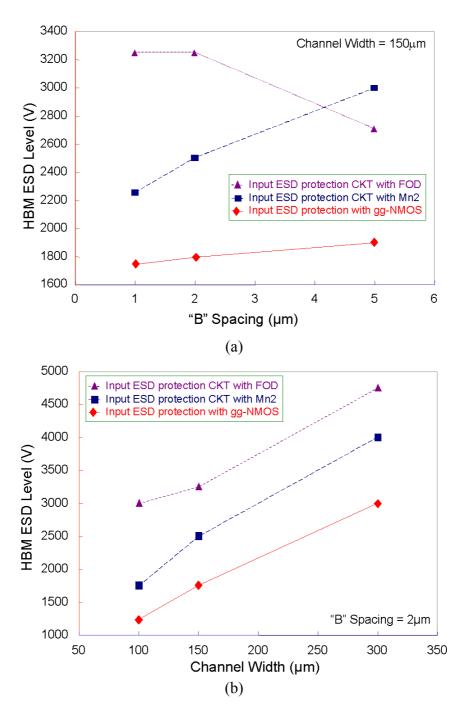

- **Fig. 5.10** The dependence of HBM ESD levels of the input ESD protection circuits (a) on the "B" spacing (channel length), and (b) on the channel width, of the ESD protection devices with the gg-NMOS, substrate-triggered FOD, or substrate-triggered NMOS Mn2.

- **Fig. 5.11** The modified substrate-triggered ESD protection design with enhanced turn-on speed for the (a) input, and (b) output, ESD protection circuits.

- Fig. 6.1 The schematic diagram of the *RC*-based ESD clamp circuit with a gate-driven NMOS as the ESD clamp device between the VDD and VSS power rails.

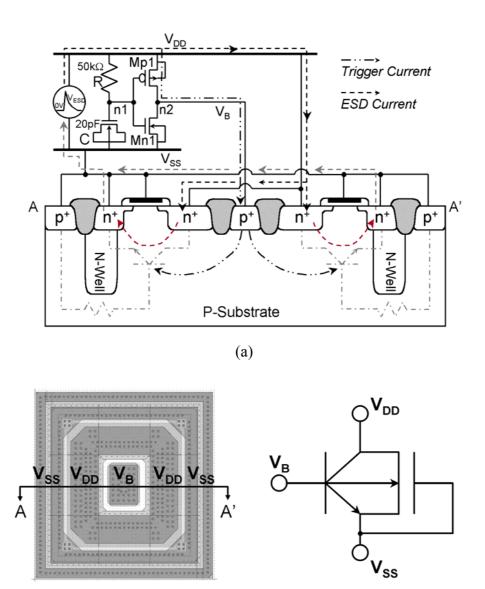

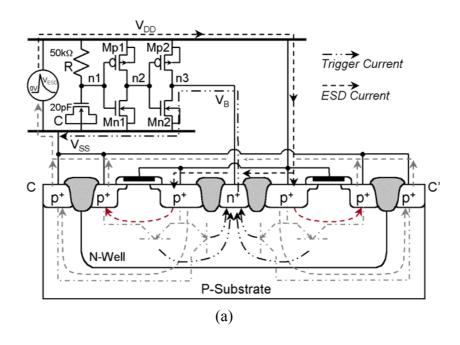

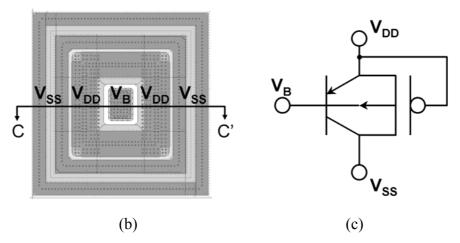

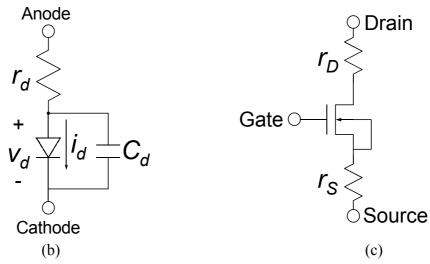

- **Fig. 6.2** (a) The schematic diagram of the ESD clamp circuit with the substrate-triggered lateral BJT (STLB) device. (b) The layout of a unit cell of the STLB device. (c) The symbol of STLB device.

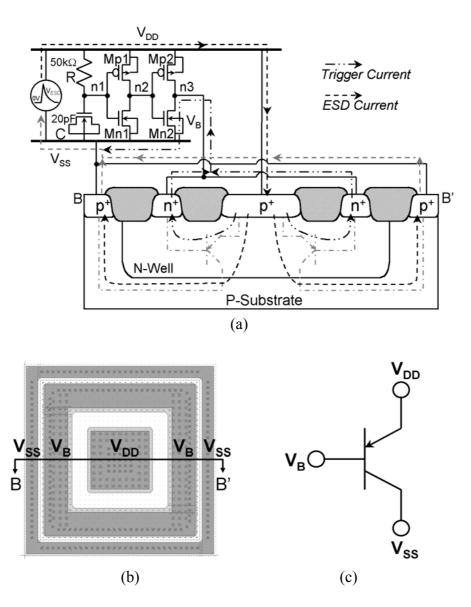

- **Fig. 6.3** (a) The schematic diagram of the ESD clamp circuit with the substrate-triggered vertical BJT (STVB) device. (b) The layout of a unit cell of the STVB device. (c) The symbol of STVB device.

- **Fig. 6.4** (a) The schematic diagram of the ESD clamp circuit with the substrate-triggered double BJT (STDB) device. (b) The layout of a unit cell of the STDB device. (c) The symbol of STDB device.

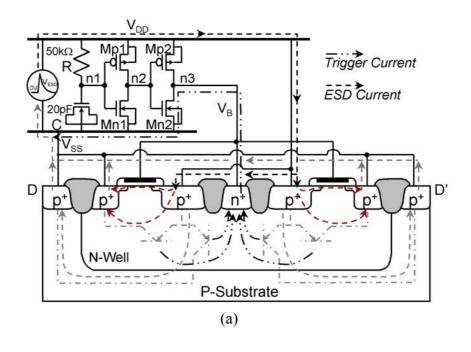

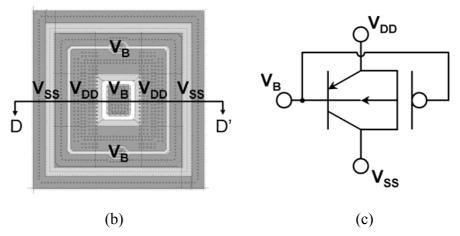

- Fig. 6.5 (a) The schematic diagram of the ESD clamp circuit with the double-triggered

- double BJT (DTDB) device. (b) The layout of a unit cell of the DTDB device. (c) The symbol of DTDB device.

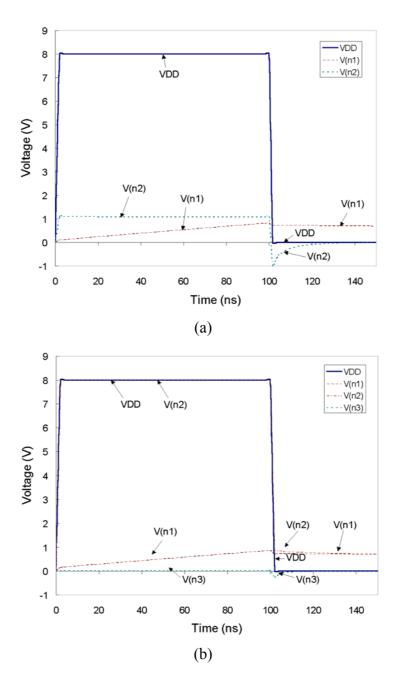

- **Fig. 6.6** The *HSPICE* simulated voltage waveforms for (a) the ESD clamp circuit with the STLB device, and (b) the ESD clamp circuit with the DTDB device, under the triggering of an 8-V voltage pulse with 100-ns pulse width and 2-ns rise time to simulate the ESD stress condition.

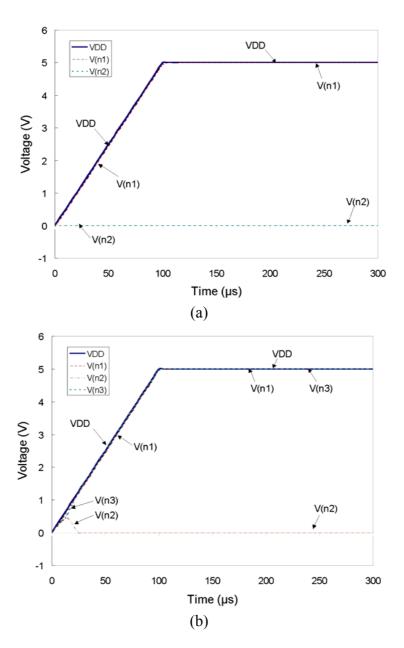

- **Fig. 6.7** The *HSPICE* simulated voltage waveforms for (a) the ESD clamp circuit with the STLB device, and (b) the ESD clamp circuit with the DTDB device, under the triggering of a 5-V ramp voltage with 0.1-ms rise time to simulate the VDD power-on condition.

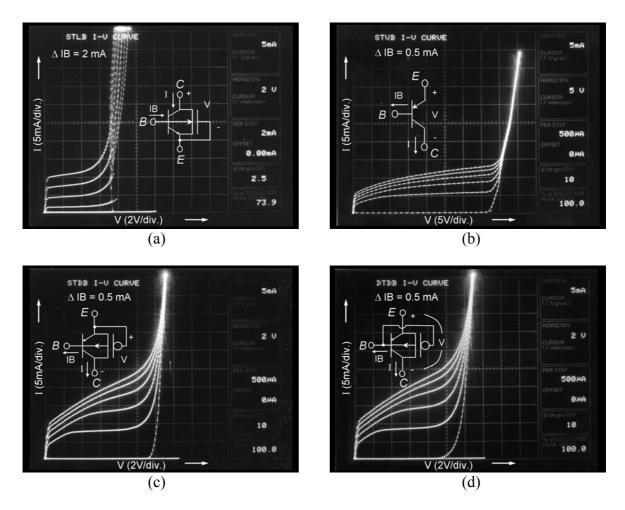

- **Fig. 6.8** The measured I-V curves of (a) the STLB, (b) the STVB, (c) the STDB, and (d) the DTDB devices. (X scale in (a), (c) and (d) is 2V/div.; X scale in (b) is 5V/div.; Y scale is 5mA/div.)

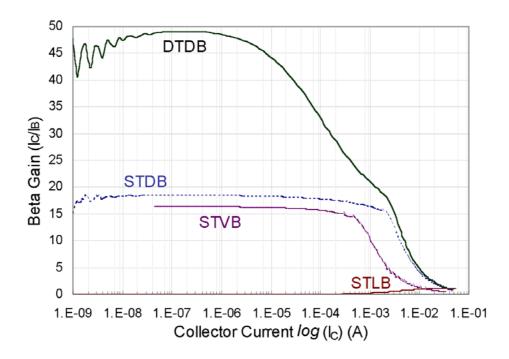

- **Fig. 6.9** The dependence of the beta gains on the collector currents among the STLB, STVB, STDB, and DTDB devices.

- **Fig. 6.10** The dependence of the HBM ESD level on (a) the channel width, and (b) the silicon area, of the power-rail ESD clamp circuits with different protection devices.

- **Fig. 6.11** The TLPG measured I-V curves of the substrate-triggered devices under 0-V substrate bias.

- **Fig. 6.12** (a) The experimental setup to verify the turn-on behavior of the power-rail ESD clamp circuits under ESD-stress condition. (b) The original 8-V voltage pulse generated from a pulse generator. The degraded voltage waveforms clamped by the power-rail ESD clamp circuits with the (c) STLB, (d) STVB, (e) STDB, and (f) DTDB devices. (X scale: 100ns/div.; Y scale: 2V/div.)

- **Fig. 6.13** The relations between the turn-on time and the pulse height of the applied voltage pulses on the power-rail ESD clamp circuits with different protection devices.

- **Fig. 6.14** (a) The experimental setup to verify the noise-clamping efficiency of the power-rail ESD clamp circuits when the IC is in the normal operating condition with 5-V VDD power supply and an overshooting noise pulse. (b) The original voltage waveform of a 5-to-12 V overshooting noise pulse. The degraded voltage waveforms of the 5-to-12 V overshooting noise pulse clamped by the power-rail ESD clamp circuits with the (c) STLB and (d) DTDB devices. (X scale: 50ns/div.;

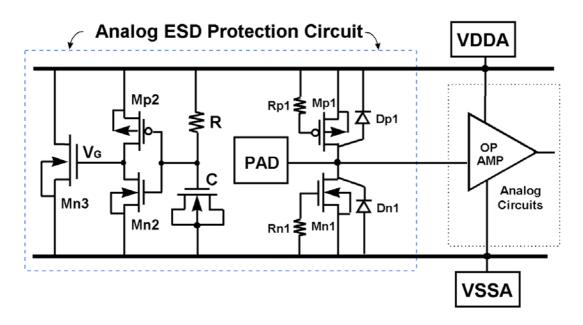

- **Fig. 7.1** The ESD protection circuit for high-frequency analog pin.

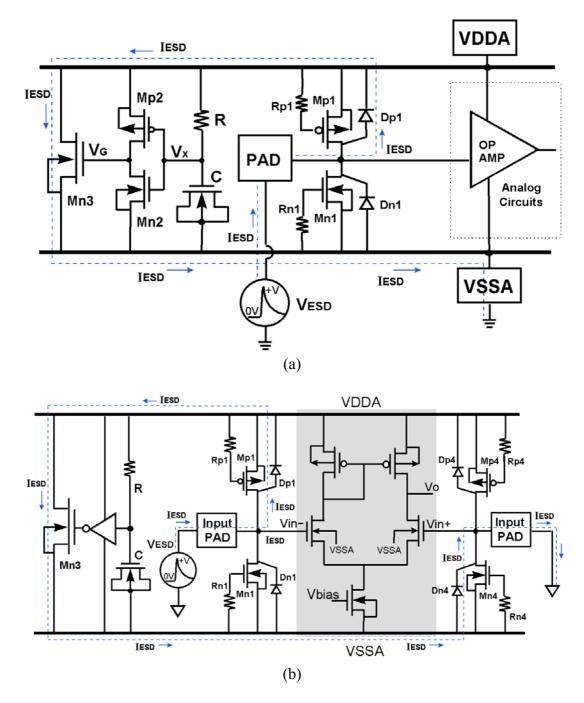

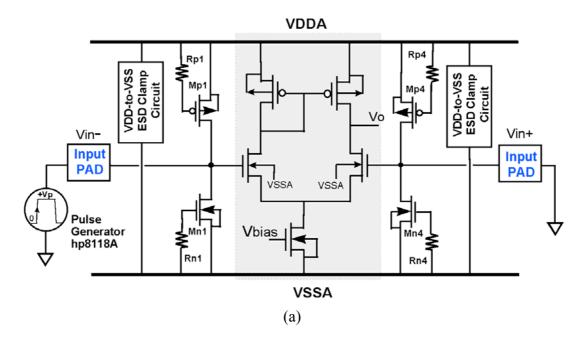

- **Fig. 7.2** The ESD current path along the analog ESD protection circuit when the analog pin is zapped in (a) the PS-mode, and (b) the pin-to-pin, ESD stresses.

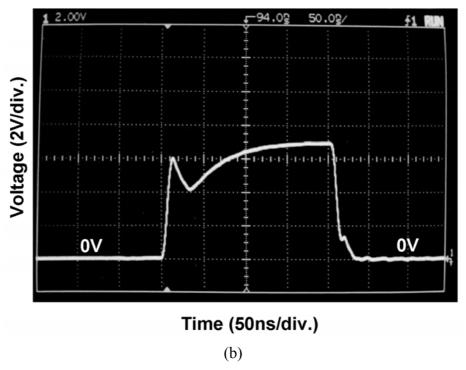

- **Fig. 7.3** (a) The experimental setup to verify turn-on efficiency of the analog ESD protection circuit during the positive pin-to-pin ESD stress condition. (b) The degraded voltage waveform when an 8V voltage pulse is applied to the inverting input pin under the pin-to-pin ESD stress condition.

- **Fig. 7.4** (a) The experimental setup to verify turn-on efficiency of the analog ESD protection circuit during the ND-mode ESD stress. (b) The degraded voltage waveform when the negative (-8V) voltage pulse is applied to the inverting input pin under the ND-mode ESD stress condition.

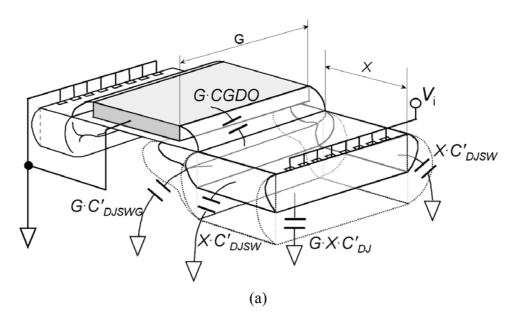

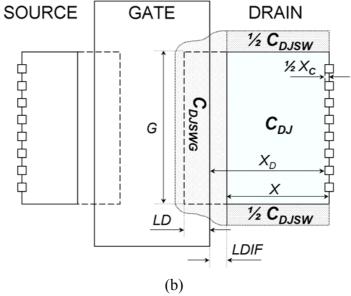

- **Fig. 7.5** (a) The three-dimension structure of a single-finger MOS device. (b) The corresponding layout top view of a single-finger MOS device with specified layout spacings.

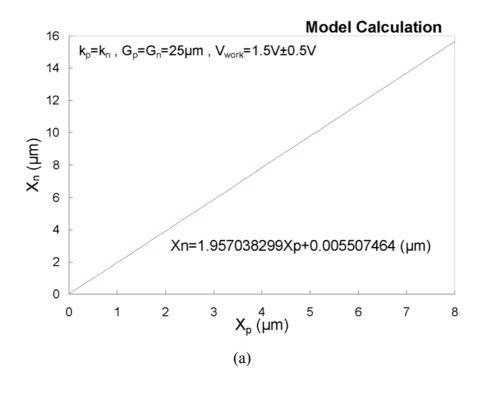

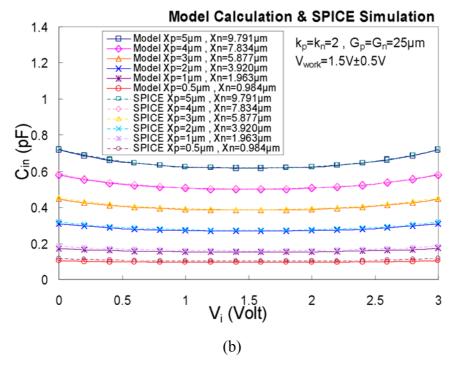

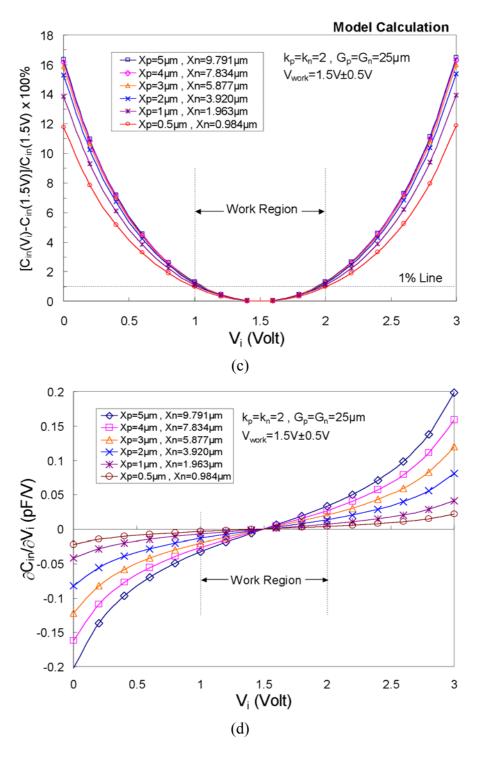

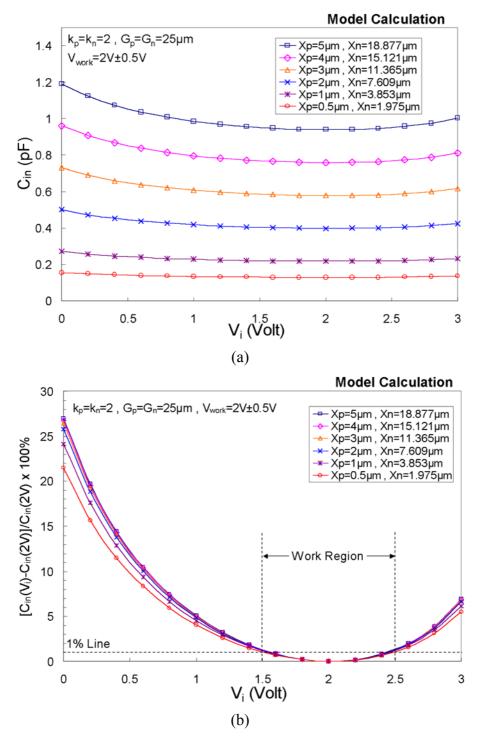

- Fig. 7.6 (a) The relation between layout parameters  $X_n$  and  $X_p$  to meet the condition in equation (7.21) with the analog common reference voltage biased at 1.5V. (b) The relation between the total input capacitance and the input voltage level under different layout parameters  $X_n$  and  $X_p$ . (c) The relation between the variation percentage on the input capacitance and the input voltage level under different layout parameters  $X_n$  and  $X_p$ . (d) The relation between the calculated  $\partial C_{in}/\partial V_i$  value and the input voltage level under different layout parameters  $X_n$  and  $X_p$ .

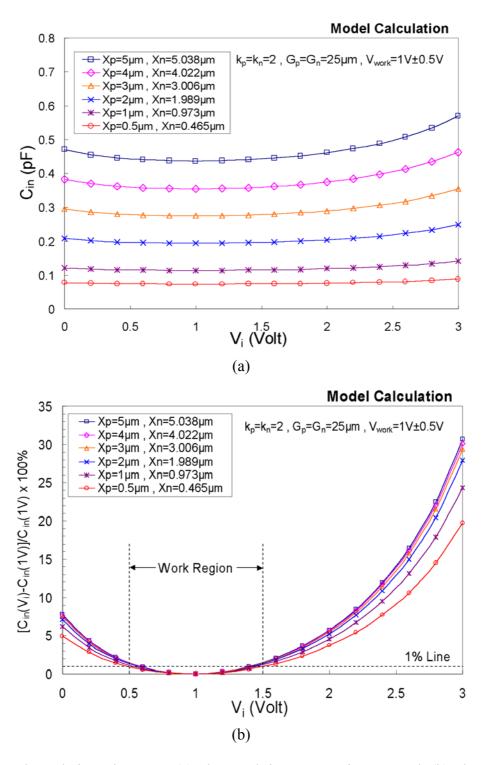

- Fig. 7.7 The relations between (a) the total input capacitance, and (b) the variation percentage on the input capacitance, of the analog ESD protection circuit and the input voltage level under different layout parameters  $X_n$  and  $X_p$ , which meet the condition in equation (7.14) with an analog common reference voltage biased at 1.0V.

- **Fig. 7.8** The relations between (a) the total input capacitance, and (b) the variation percentage on the input capacitance, of the analog ESD protection circuit and the input voltage level under different layout parameters  $X_n$  and  $X_p$ , which meet the condition in equation (7.14) with an analog common reference voltage biased at

2.0V.

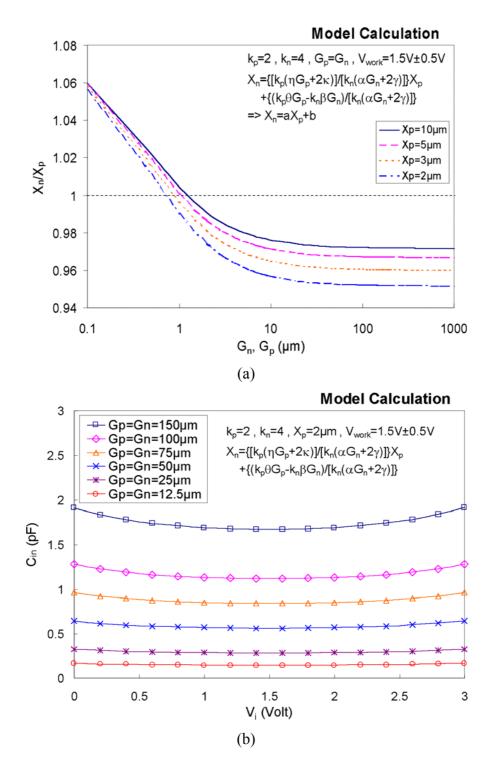

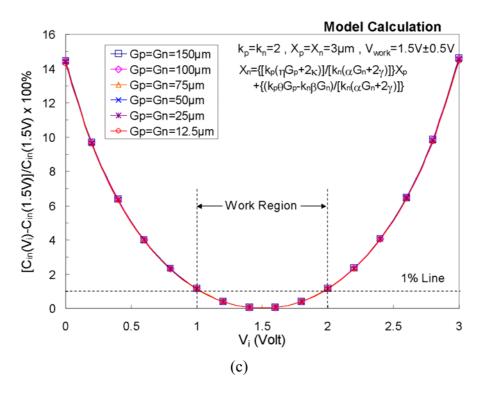

**Fig. 7.9** (a) The relation between the ratio of  $X_n/X_p$  and the finger lengths  $G_n$  and  $G_p$  to meet the condition in equation (7.21) with  $k_p$ =2,  $k_n$ =4, and  $V_{work}$ =1.5V±0.5V. (b) The relation between the total input capacitance of the analog ESD protection circuit and the input voltage level under different layout parameters  $G_n$  and  $G_p$ . (c) The relation between the variation percentage on the input capacitance and the input voltage level under different layout parameters  $G_n$  and  $G_p$ .

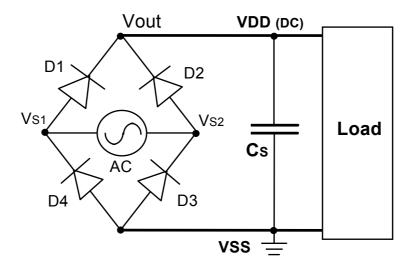

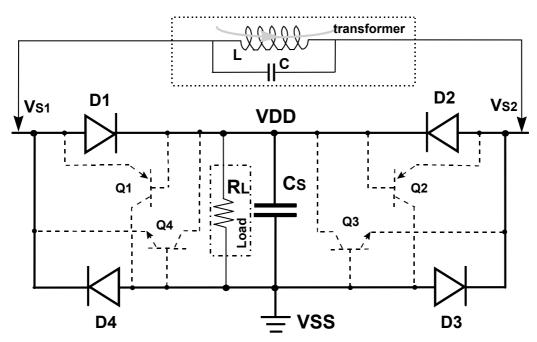

- **Fig. 8.1** The traditional full-wave bridge rectifying circuit formed by four diodes to convert the AC power into DC power.

- **Fig. 8.2** The typical application of a smart card IC for personal identification to enter a controlled door.

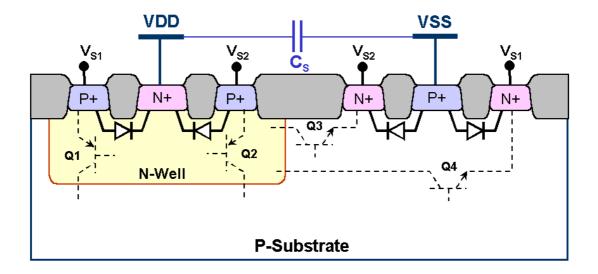

- **Fig. 8.3** Device cross-sectional view of the four p-n junction diodes of the full-wave bridge rectifying circuit realized in a CMOS IC with a common p-type substrate.

- **Fig. 8.4** The leakage current paths along the parasitic BJT's in the traditional full-wave bridge rectifying circuit realized in CMOS IC with a common p-type substrate.

- **Fig. 8.5** The on-chip bridge rectifying circuit in a smart card IC realized by four polysilicon diodes with the original design of on-chip ESD protection circuits.

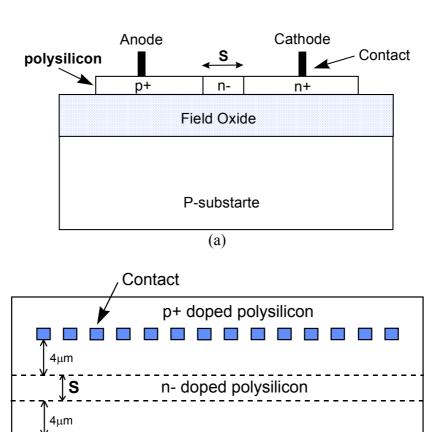

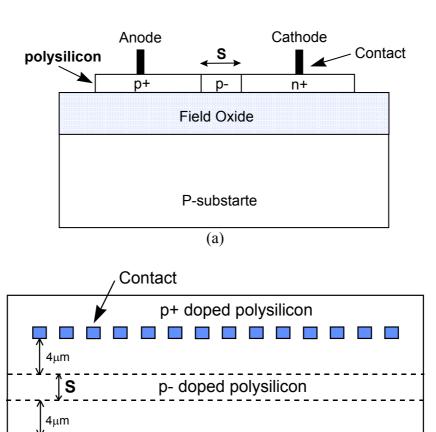

- **Fig. 8.6** (a) The device structure, and (b) the layout top view, of the p+/n-/n+ polysilicon diode realized in a 0.8-μm CMOS process.

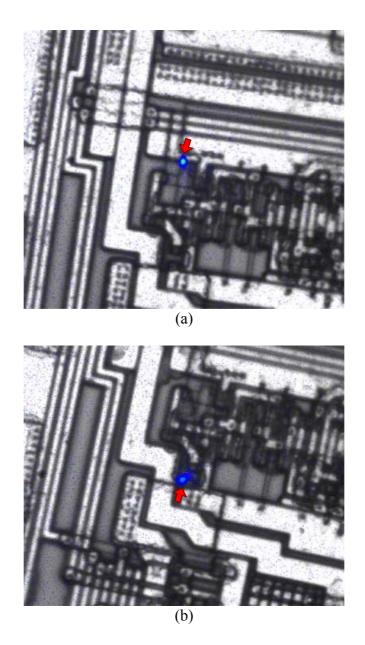

- **Fig. 8.7** The EMMI pictures to show the ESD failure location (indicated by the arrows) on the input circuits after the (a) VSS(+) test mode, and (b) VDD(-) test mode, HBM ESD stresses.

- **Fig. 8.8** The new design of on-chip ESD protection circuit with a novel VDD-to-VSS ESD clamp circuit in the smart card IC.

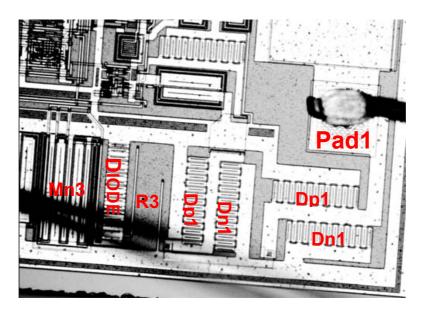

- **Fig. 8.9** The partial picture of a smart card IC with the realization of ESD protection circuit on the pad1 pin and the VDD-to-VSS ESD clamp circuit.

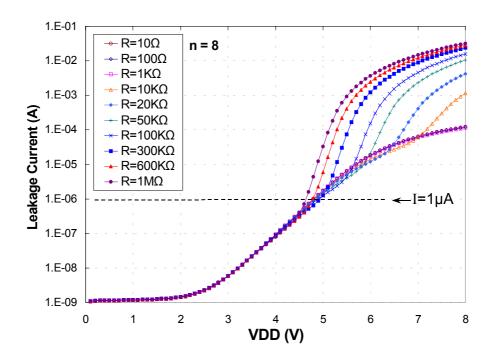

- **Fig. 8.10** *HSPICE* simulated leakage current of the proposed VDD-to-VSS ESD clamp circuit with 8 diodes in the stacked diode string under different resistance of R3. (Y axis is drawn in logarithmic scale.)

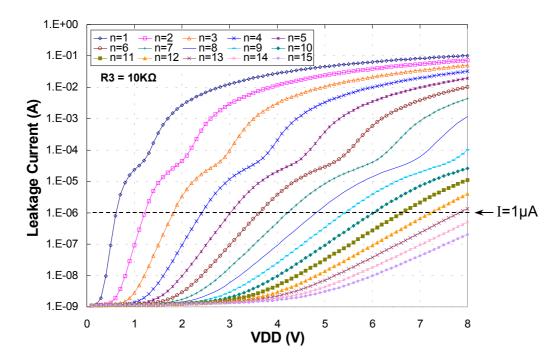

- Fig. 8.11 HSPICE simulated leakage current of the proposed VDD-to-VSS ESD clamp circuit with a fixed R3 of  $10k\Omega$  but different diode number (n) in the stacked

- diode string. (Y axis is drawn in the logarithmic scale.)

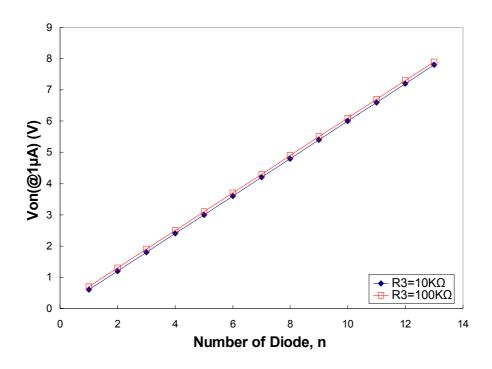

- **Fig. 8.12** The relation between *Von* defined at  $I=1\mu A$  and the diode number (*n*) of the VDD-to-VSS ESD clamp circuit under R3 of  $10k\Omega$  or  $100k\Omega$ .

- **Fig. 8.13** (a) The device structure, and (b) the layout top view, of the p+ / p- / n+ polysilicon diode realized in a CMOS process.

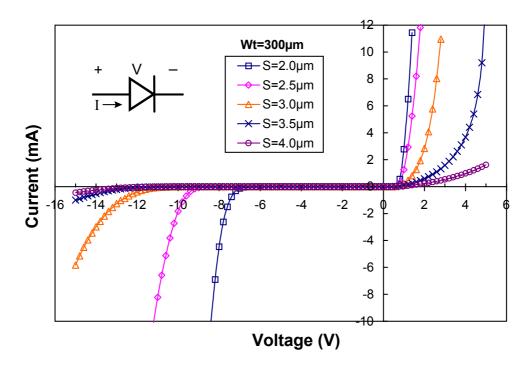

- Fig. 8.14 The measured I-V curves of the p+ / n- / n+ polysilicon diodes with a fixed Wt of 300 μm but different S spacings in a CMOS process.

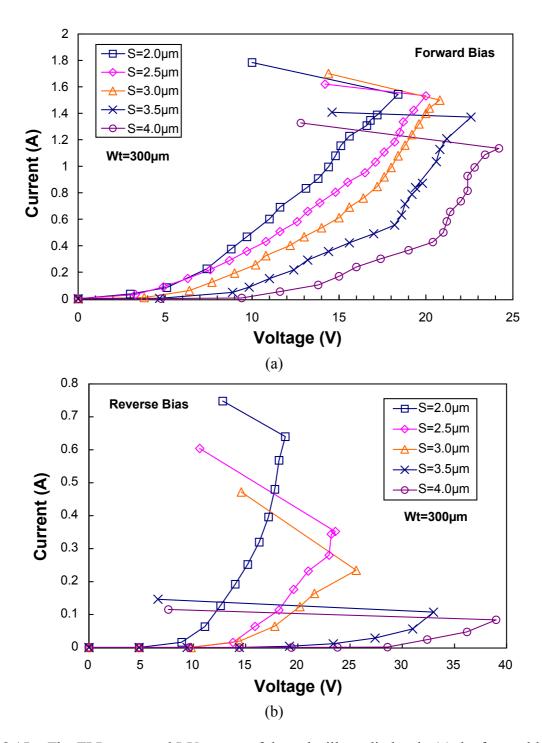

- **Fig. 8.15** The TLP-measured I-V curves of the polysilicon diodes, in (a) the forward-biased condition; and (b) the reverse-biased condition, with a fixed Wt of 300 μm but different S spacings.

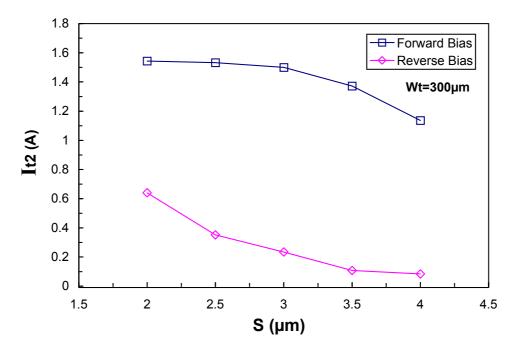

- **Fig. 8.16** Dependence of the TLP-measured It2 on the layout parameter S of the polysilicon diodes in both the forward- and reverse-biased conditions.

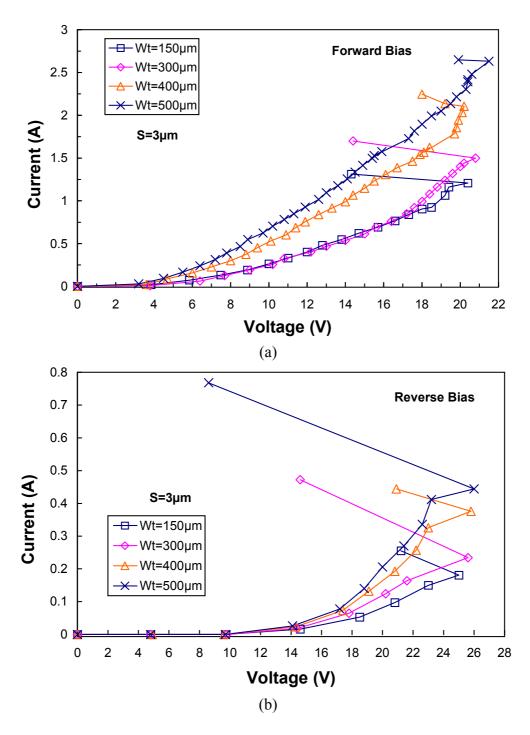

- **Fig. 8.17** The TLP-measured I-V curves of the polysilicon diodes, in (a) the forward-biased condition; and (b) the reverse-biased condition, with a fixed spacing S of 3 μm but different total perimeters Wt.

- **Fig. 8.18** Dependence of the TLP-measured It2 on the layout parameter Wt (total perimeter) of the polysilicon diodes in both the forward- and reverse-biased conditions.

- **Fig. 8.19** The pictures to show the ESD failure location (indicated by the arrows) on the smart card IC with the p- doped polysilicon diodes after the pad1 pin is zapped with a 4-kV HBM ESD stress in (a) the VSS(+), and (b) the VDD(-), ESD test conditions.

- **Fig. 8.20** The picture to show the ESD failure location (indicated by the arrow) on the smart card IC with the n- doped polysilicon diodes after a negative 700V CDM ESD stress.

- **Fig. 8.21** The alternative input ESD protection design with the polysilicon diodes in a multi-stage configuration to achieve better ESD protection.

- **Fig. 8.22** The measured I-V curve from VDD to VSS of the new proposed VDD-to-VSS ESD clamp circuit with 8-stacked n- doped polysilicon diodes.

- **Fig. 8.23** The measured voltage waveform at the pad1 when a 0-to-8V voltage pulse is applied to the pad1 with the VSS grounded.

- **Fig. 8.24** (a) The ESD clamp circuit with stacked polysilicon diodes; and the equivalent circuits of (b) a diode, and (c) an NMOS, for model calculation.

## INTRODUCTION

#### 1.1 BACKGROUND

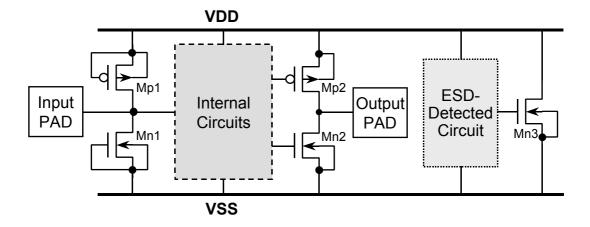

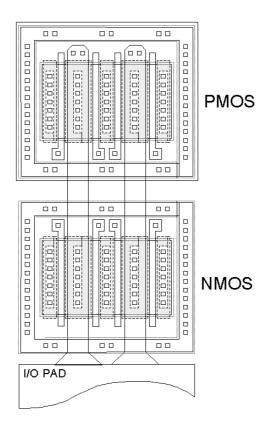

Electrostatic discharge (ESD) has become the main reliability concern on semiconductor products, especially in the scaled-down CMOS technologies [1], [2]. Due to low breakdown voltage of the thinner gate oxide in deep-submicron CMOS technologies, efficient on-chip ESD protection circuit should be designed and placed on each pad to clamp the overstress voltage across internal circuits. To sustain reasonable ESD robustness in deep-submicron CMOS IC's, on-chip ESD protection circuits must be added into the chips [1]. ESD level of commercial IC products is generally required to be higher than 2kV in the human-body-model (HBM) ESD stress [3]-[5]. The typical design of efficient ESD protection circuits in a CMOS IC is shown in Fig. 1.1 to protect the internal circuits against ESD damage [6]. But, circuit designers often confuse on how to optimize those ESD protection devices such as Mn1, Mn2, Mn3, Mp1, and Mp2 in Fig. 1.1. To design area-efficient ESD protection circuits, the ESD protection devices are desired as robust as possible in a limited layout area. To sustain the required ESD level, on-chip ESD protection circuits are often drawn with larger device dimensions. Such ESD protection devices with larger device dimensions are often realized with multiple fingers, as that shown in Fig. 1.2, to reduce total layout area [7].

To enhance the ESD robustness of CMOS IC's, the lateral SCR (LSCR) can be used in the ESD protection design [8]-[10]. The LSCR has been developed in some modifications, such as LVTSCR [11]-[12], MLSCR [13]-[14], and gate-coupled LVTSCR [15]-[16]...etc [17]-[31], to design in the ESD protection circuit of CMOS IC's. Due to the low holding voltage (~1V), the SCR devices in the on-chip ESD protection circuit can sustain much higher ESD voltage within smaller layout area, as comparing to the other ESD protection devices in the CMOS IC's. But, the lower trigger current may cause the SCR devices being accidentally triggered on by the external noise pulses while the CMOS IC is in the normal operating conditions. In order to safely apply the SCR device for ESD protection, the SCR device must have a lower triggered voltage and an enough noise margin for CMOS IC's in the noisy

environments [32]-[37]. In a system-level ESD/EMC [38] event easily causes the transient-induced latchup failure in the CMOS IC's. If the SCR devices are used as the ESD clamp devices between the VDD and VSS power lines of the CMOS IC's [18], [26], such ESD-protection SCR devices are easily triggered on by the system-level ESD/EMC transient pulses to cause very serious latchup problem in the CMOS IC's. So, the MOSFET devices are still popularly used in the ESD protection design of CMOS IC's.

But, the effectiveness of the ESD protection circuits is seriously degraded by the advanced CMOS fabrication technologies, especially when the LDD (Lightly-Doped Drain) structure and the silicide diffusion are used [39]. Therefore, salicide-blocking [40]-[45] and ESD-implantation [46]-[55] process modifications had been added into the CMOS processes to improve ESD robustness of MOSFET. These additional process modifications in CMOS technology must be done with extra process steps and mask layers, which increase the fabrication cost and slow down the throughput of production. Moreover, because the layout parameters can affect the geometrical structure of finger-type MOSFET, the turn-on efficiency of the parasitic devices in MOSFET under ESD stress must be changed by the different layout parameters. To optimize the best turn-on efficiency of CMOS devices during ESD stress, the turn-on mechanisms of CMOS devices with different layout parameters under high current stress must be understood and analyzed. To improve the ESD robustness of CMOS devices, the layout modifications of CMOS device have been discussed in some papers [56]-[61]. But, the non-uniform turn-on effect on the CMOS device is still a major problem during ESD stress.

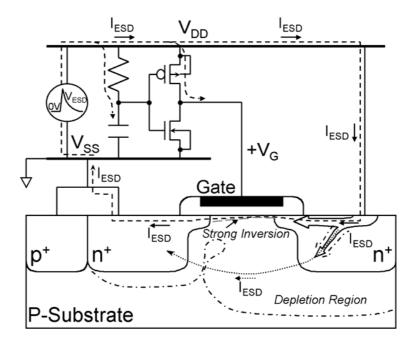

To improve the turn-on uniformity among those multiple fingers of the CMOS devices, the gate-driven design [62]-[67] or substrate-triggered design [68]-[74] had been reported to increase ESD robustness of the large-device-dimension NMOS. Recently, ESD robustness of the gate-driven NMOS had been found to be decreased dramatically when the gate voltage is somewhat increased [44], [64], [75]. The gate-driven design causes ESD current mainly discharging through the strong-inversion channel of NMOS, therefore NMOS is easily burned out by ESD energy. However, with the substrate-triggered design, the parasitic lateral bipolar junction transistor (BJT) of MOSFET can sustain higher ESD current than the gate-driven MOSFET. To analyze and explain the failure mechanisms of device under ESD stress, some simulation methods have been developed [76], [77].

These prior arts, such as some SCR structures, process modifications, layout modifications, and triggered techniques, for ESD protection design are summarized in Table

1.1. The references for each item are also listed in this table. Generally, the SCR structures with smaller silicon area can sustain higher ESD voltage stress than CMOS devices, but the low holding voltage of SCR structures will cause the latchup issue in IC's. So, the SCR structures cannot be publicly used in the ESD protection circuits of IC's. Although some process modifications can improve the ESD robustness of MOSFET, the non-uniformly turn-on effect can cause the unexpected ESD level of MOSFET device with large dimension. Some layout parameters of MOSFET devices can mainly dominate the turn-on behavior of MOSFET devices during ESD stress. To improve the uniform turn-on behavior of MOSFET devices, those layout parameters must be finely investigated.

In this work, the dependences of layout parameters on the ESD robustness of NMOS and PMOS devices are investigated through the fabricated testchips. Besides, the gate-driven design and the substrate-triggered design used to improve ESD robustness of the ESD protection circuits are also investigated in more details [78]. To clearly understand the physical mechanisms on ESD current distribution in the device, the transmission-line-pulse (TLP) [79]-[83] measured results and energy band diagram are used to explain the potential distribution along MOSFET under the gate-driven or substrate-triggered designs. The ESD current distribution among the MOSFET with different layout parameters, gate-driven, or substrate-triggered designs can be well explained by the TLP measured results and the analysis of energy band diagram. Depending on the theory of the substrate-triggered technique, some substrate-triggered ESD protection circuits for input, output, and power-rail of on-chip integrated circuits are designed in this thesis to implement the applications of substrate-triggered technique.

For some high-precision analog circuits, the input capacitance of an analog input pin including ESD protection circuit and a bond pad is required as constant as possible. A major distortion in analog circuits, especially in the single-ended input implementations, comes from the voltage-dependent nonlinear input capacitance of ESD clamp devices connected to the analog input pin. The typical degradation on analog circuit performance due to the nonlinear input capacitance of ESD clamp devices had been reported in [84], where the input capacitance was varying from 4pF to 2pF due to the input voltage increasing from 0V to 2V. Thus for high-precision analog applications, the input capacitance generated from ESD clamp devices on the input pad needs to be kept as constant as possible. A design model to find the optimized device dimensions and layout spacings on the input ESD clamp devices is developed in this work to keep the total input capacitance almost constant, even if the analog

signal has a varying input voltage. An analog ESD protection circuit has been designed to solve ESD protection challenge on the analog pins for high-frequency applications in this thesis. By using the optimized layout design to draw the layout of ESD protection NMOS and PMOS devices with a suitable power-rail ESD clamp circuit, the device dimension (W/L) of ESD protection device connected to the I/O pad can be reduced to smaller silicon area with almost constant capacitance, but it can sustain more HBM ESD robustness.

The diodes or diode string can be designed as ESD protection device or some application in CMOS IC. When the on-chip diodes is realized in a CMOS IC with a p-type substrate, the diodes are often made by the p-n junctions across P+ diffusion and N-well. Due to the common p-substrate of a CMOS IC, there are some parasitic BJT's in the physical structure with the common p-substrate. Therefore, these parasitic BJT's would cause the degradation of signal or high leakage current in really applications. In some modified design, the diodes may be changed to NMOS or PMOS devices in the integrated circuit for realization in CMOS IC [85]. The parasitic vertical or lateral BJT's still exist among these device structures to degrade its transformation efficiency of signal. If the diodes in the CMOS IC are realized by the polysilicon diodes, which have no any parasitic BJT in their device structures, the aforementioned problem can be totally eliminated. However, due to the low heat dissipation capability of the polysilicon layer, the polysilicon diodes result in a very low human-body-model (HBM) ESD level. To understand the characteristics of the polisilicon diodes, different process splits have been experimentally evaluated to find the suitable doping concentration for optimizing the polysilicon diodes for both on-chip ESD protection design and the application requirements of the CMOS IC's. The secondary breakdown current (It2) [86]-[88] of the polysilicon diodes under the forward- and reverse-bias conditions has been measured by the TLP generator to investigate its ESD robustness in this thesis. Moreover, by adding an efficient VDD-to-VSS clamp circuit into the CMOS IC, the HBM ESD robustness of the IC with polysilicon diodes as the ESD clamp devices has been successfully improved. This design has been practically applied in a mass-production smart card IC.

#### 1.2 ESD TESTING COMBINATIONS ON IC

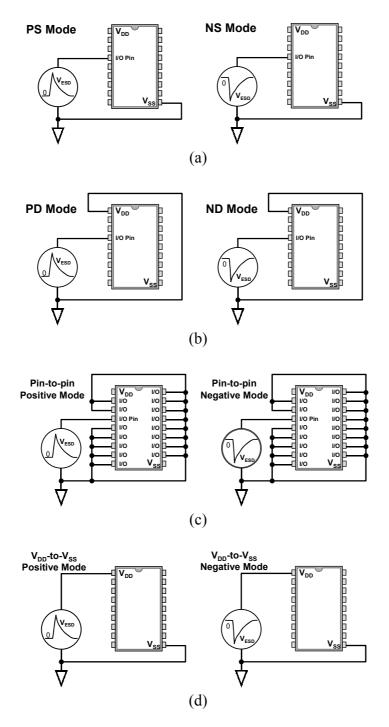

Since the ESD stress may have positive or negative voltage on an input (or output) pin with respect to the grounded VDD or VSS pins, there are four different ESD-testing pin

combinations at each input (output) pin, which are shown in Fig. 1.3(a) and Fig. 1.3(b). For a comprehensive ESD verification, two additional ESD-testing pin combinations, the pin-to-pin ESD stress and the VDD-to-VSS ESD stress in Fig. 1.3(c) and Fig. 1.3(d), had been also specified to verify the whole-chip ESD reliability [6]. These two additional ESD-testing pin combinations often lead to more complex ESD current paths from the input or output pins through the power lines into the internal circuits, which will cause some unexpected damages on the internal circuits even if there are input and output ESD protection circuits in the IC's [89]-[93]. The ESD current discharging paths in an IC during the pin-to-pin ESD stress is illustrated in Fig. 1.4(a), where a positive ESD voltage is applied to an input pin with some output pin relatively grounded, but the VDD and VSS pins are floating. The ESD current will be diverted from the input pad to the floating VDD power line through the forward-biased diode in the input ESD protection circuit. The ESD current flowing on the VDD power line can be conducted into the internal circuits through the connection of VDD metal line. Then, the ESD current is discharged through the internal circuits and may cause random ESD damage in the internal circuits, as the current Path 1 shown in Fig. 1.4(a). If there is an effective ESD clamp circuit across the VDD and VSS power lines, the ESD current can be discharged through the current Path 2 in Fig. 1.4(a). Therefore, the internal circuits can be safely protected against the ESD damages under a negative ESD stress, the similar ESD current paths are shown in Fig. 1.4(b). Thus, an effective ESD clamp circuit with a quick turn-on speed across the power rails is necessary for protecting the internal circuits against ESD damage. However, even if there were suitable ESD protection circuits around the input and output pads, the internal circuits were still vulnerable to ESD damages. Whole-chip electrostatic discharge (ESD) protection has become an important reliability design for deep-submicron CMOS IC's.

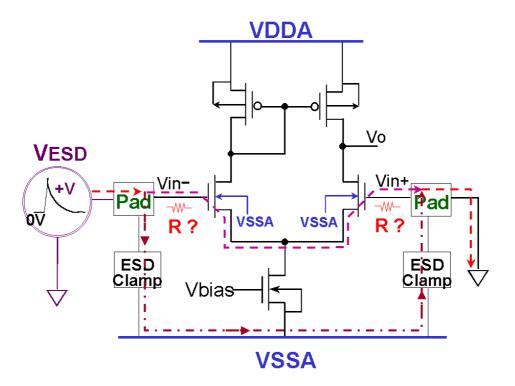

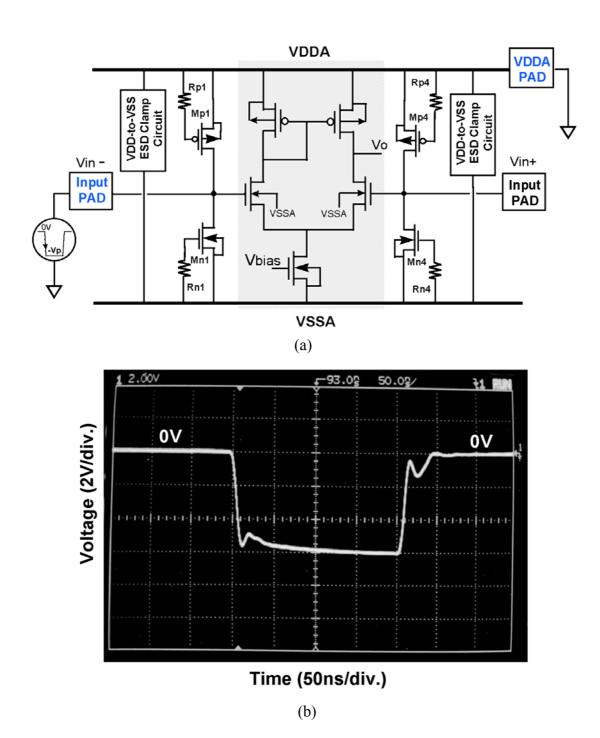

Except for such ESD-zapping pin combinations in Fig. 1.3, an additional analog pin-to-pin ESD stress had been especially specified in the standards for the analog circuits with operational amplifiers or differential input stages to verify the ESD level of the analog pins. The analog pin-to-pin ESD stress for the differential input pins of an operational amplifier is illustrated in Fig. 1.5, where the positive or negative ESD voltage is applied to the inverting input pin with the corresponding noninverting input pin relatively grounded. During such an analog pin-to-pin ESD stress, all the other pins including both the VDD and VSS pins are floating. The ESD current during such an analog pin-to-pin ESD stress is illustrated in Fig. 1.6 with the differential input stage of an operational amplifier. Because of the lack of series

resistor between the analog input pad and the input circuits, the overstress ESD current easily reaches to the thinner gate oxide of the differential input stage with a common-source circuit structure. If the VSSA power connection between the inverting input pin and the noninverting input pin has a long metal line in the IC layout, the gate oxide of the differential input stage is easily ruptured by the ESD voltage to generate an ESD current discharging path, as the dashed line shown in Fig. 1.6. The ESD clamp device with large dimension between the inverting input pad and the VSSA power line cannot provide effective ESD protection against this additional analog pin-to-pin ESD stress. Therefore, some advanced designs should be included into the analog ESD protection circuit to overcome this analog pin-to-pin ESD-stress issue

## 1.3 THESIS ORGANIZATION

To solve the turn-on efficiency and uniformity issues of on-chip ESD protection devices during ESD stress in deep-submicron CMOS IC's, the turn-on mechanisms of ESD protection device and some designs of ESD protection circuits are discussed in this thesis. The turn-on mechanisms of ESD protection device under ESD stress, gate-driven design, and substrate-triggered design are proposed in Chapter 2 and 3. Some novel substrate-triggered ESD protection designs are proposed from Chapter 4 to 6. The analog ESD protection design is proposed in Chapter 7. The application of polysilicon diodes is proposed in Chapter 8.

In Chapter 2, the dependence of layout spacings on the ESD robustness of finger-type CMOS devices in silicided CMOS process is detailedly investigated and discussed. The energy band diagrams, EMMI photographs, and TLP measurement have been used to analyze and explain the physical turn-on mechanisms of ESD protection device. From the explication of energy band diagrams, the larger channel current and smaller turn-on area of parasitic lateral BJT can cause the damage of MOSFET under ESD stress. This effect causes the degradation of ESD robustness in MOSFET's.

In Chapter 3, the gate-driven effect and substrate-triggered effect on ESD robustness of CMOS devices are measured and compared in this chapter. The operation principles of gate-driven design and substrate-triggered design for ESD protection are explained clearly by energy band diagrams and EMMI photographs. The gate-driven and substrate-triggered techniques can improve the turn-on uniformity of the large-dimension ESD protection devices. But, the higher gate bias can induce larger channel current and higher electric field across gate

oxide to damage MOSFET. This effect causes the degradation of ESD robustness in gate-driven devices. From energy band analysis, substrate-triggered design can continually increase the turn-on area for heat dissipation. Therefore, substrate-triggered design can effectively improve ESD robustness of the ESD protection devices.

In Chapter 4, a novel substrate-triggered design for input, output, and power-rail ESD protection, as comparing to the traditional gate-driven technique, is proposed. The novel on-chip substrate-triggered ESD protection circuits for the input, output, and power pins are designed and verified in a 0.18- $\mu$ m CMOS process. With the proposed substrate-triggered designs, the ESD protection devices with smaller layout dimension can sustain higher ESD stress than the traditional gate-driven design. The HBM ESD robustness of output ESD protection circuits with ESD protection NMOS of W/L =  $300\mu$ m/0.3 $\mu$ m can be improved from the original 0.65 kV with the traditional gate-driven design to become 3.2 kV by the proposed substrate-triggered design.

In Chapter 5, a substrate-triggered input ESD protection circuit for mixed-voltage application is realized in a 0.25- $\mu$ m salicided CMOS process without extra salicide-blocking and ESD-implantation modifications. By using layout technique, the proposed input ESD protection circuit can be merged into a compact device structure to enhance the substrate-triggered efficiency. The trigger voltage of such input ESD protection circuit with field oxide device (FOD) is lowered from original 11.9 V to only 6.4 V to effectively protect the thinner gate oxide (50Å) of input stage in the 0.25- $\mu$ m salicided CMOS process. The substrate-triggered input ESD protection circuit with a FOD of 150- $\mu$ m channel width can improve the HBM ESD robustness per unit silicon area from the original 1.2 V/ $\mu$ m<sup>2</sup> of traditional gate-grounded NMOS (gg-NMOS) with salicide-blocking process modification to 1.73 V/ $\mu$ m<sup>2</sup>.

In Chapter 6, four novel ESD clamp devices for using in power-rail ESD clamp circuits with the substrate-triggered technique are proposed to improve ESD level. The parasitic n-p-n and p-n-p bipolar junction transistors (BJT) in the CMOS devices are used to form the substrate-triggered devices for ESD protection. Four substrate-triggered devices are proposed and investigated in a 0.6-µm CMOS process, which are named as the substrate-triggered lateral BJT (STLB), the substrate-triggered vertical BJT (STVB), the substrate-triggered double BJT (DTDB). An *RC*-based ESD-detection circuit is used to generate the triggering current to turn on the proposed substrate-triggered devices. In the experimental results, the DTDB device has the best

performance among these four substrate-triggered devices. With suitable design on the substrate-triggered ESD-clamp circuit, the layout area of the ESD clamp circuit to achieve whole-chip ESD protection can be efficiently reduced to save the silicon cost of CMOS IC's.

In Chapter 7, a design model to find the optimized device dimensions and layout spacings on the input ESD clamp devices is developed, even if the analog signal has a varying input voltage. An analog ESD protection circuit has been designed to solve ESD protection challenge on the analog pins for high-frequency applications. The design model to optimize the device dimensions and layout spacings of ESD protection devices is clearly developed to keep the input capacitance as constant as possible in general CMOS processes. With suitable layout parameters on the input ESD clamp devices, the variation of total input capacitance of the analog ESD protection circuit can be designed below 1% while the analog input signal has an input voltage swing of 1V. The device dimension (W/L) of ESD protection device connected to the I/O pad can be reduced to only  $50\mu\text{m}/0.5\mu\text{m}$  in a  $0.35\mu$ - m silicided CMOS process, but it can sustain HBM (MM) ESD level up to 6kV (400V). With such a smaller device dimension, the input capacitance of this analog ESD protection circuit can be significantly reduced to only  $20\mu$ - for high-frequency applications.

In Chapter 8, a novel on-chip ESD protection design by using polysilicon diodes as the ESD clamp devices in CMOS process is first proposed. Different process splits have been experimentally evaluated to find the suitable doping concentration for optimizing the polysilicon diodes for both on-chip ESD protection design and the application requirements of the smart card IC's. The It2 of the polysilicon diodes under forward- and reverse-bias conditions and different layout parameters is clearly investigated. A novel power-rail ESD clamp circuit with the stacked polysilicon diodes as the turn-on control circuit is also designed and analyzed in this chapter. By adjusting the number of the stack diodes in the ESD detection circuit, the turn-on efficient VDD-to-VSS ESD clamp circuit can be applied in the IC with different VDD voltage levels. The HBM ESD level of the smart card IC with the polysilicon diodes as ESD protection devices has been successfully improved up to ≥ 3kV in cooperation with the turn-on efficient power-rail ESD clamp circuit.

Finally, the main results are summarized in Chapter 9. The future works about the turn-on mechanisms of ESD protection devices under ESD stress and substrate-triggered design are given in Chapter 9.

**Table 1.1**The summary of ESD protection design methods in CMOS IC's.

| Device | Category                | Methods                               |                                  | Characteristics I                                                                                                                 |                                                                                                                                                |           |

|--------|-------------------------|---------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| SCR    | Ι                       | LSCR                                  |                                  | <ul><li>(1) High triggered voltage</li><li>(2) Low holding voltage</li></ul>                                                      | [8]                                                                                                                                            |           |

|        | LV                      | TSCR                                  | Small Layout Size                | <ul><li>(1) Low triggered voltage</li><li>(2) Low holding voltage</li></ul>                                                       | [12]                                                                                                                                           |           |

|        | M                       | LSCR                                  |                                  | <ul><li>(1) Middle triggered voltage</li><li>(2) Low holding voltage</li></ul>                                                    | [13]                                                                                                                                           |           |

|        | Gate-coup               | pled LVTSCR                           |                                  | <ul><li>(1) Low triggered voltage</li><li>(2) Low holding voltage</li></ul>                                                       | [15]                                                                                                                                           |           |

|        | High-current-t          | riggered LVTSCR                       |                                  | <ul><li>(1) Low triggered voltage</li><li>(2) High triggered current</li><li>(3) Low holding voltage</li></ul>                    | [37]                                                                                                                                           |           |

|        | High-holding            | -voltage LVTSCR                       |                                  | <ul><li>(1) Epitaxial structure</li><li>(2) Low triggered voltage</li><li>(3) High holding voltage</li></ul>                      | [33]                                                                                                                                           |           |

|        | Process<br>Modification | Silicide Blocking                     | diffusi                          |                                                                                                                                   | [40]-[45]                                                                                                                                      |           |

|        |                         | Modification                          | ESD Implantation (2) Reduce junc | evice without LDD peak structure duce junction breakdown voltage                                                                  | [46]-[55]                                                                                                                                      |           |

|        | Layout<br>Modification  | Multi-finger Type                     | (2) No                           | sy layout<br>on-uniformly turn-on effect                                                                                          | [7]                                                                                                                                            |           |

|        |                         | Polygon Type                          | (2) Co                           | prove uniform turn-on behavior omplicated layout                                                                                  | [60]                                                                                                                                           |           |

| MOSFET |                         | Multi-finger Type with Butting Pickup | (2) Hi                           | prove uniform turn-on behavior<br>gher triggered current<br>w turn-on efficiency                                                  | [61]                                                                                                                                           |           |

|        |                         | Gate-driven<br>Design                 | (2) Im<br>(3) Ov                 | ry low triggered voltage<br>prove uniform turn-on behavior<br>ver voltage on the gate will cause<br>dden degradation on ESD level | [62]-[67]                                                                                                                                      |           |

|        |                         | Triggered<br>Design                   | Substrate-triggere<br>d Design   | (2) Im<br>(3) Co<br>of<br>(4) Sm                                                                                                  | ry low triggered voltage prove uniform turn-on behavior ontinually improve ESD robustness MOSFET device hall layout area than gate-driven sign | [68]-[74] |

Fig. 1.1 Typical on-chip ESD protection circuits in a CMOS IC.

**Fig. 1.2** Illustration of the traditional finger-type ESD protection device layout for input or output pads.

Fig. 1.3

(a) Positive and negative ESD stress on an input (or output) pin with respect to the grounded VSS. (b) Positive and negative ESD stress on an input (or output) pin with respect to the grounded VDD. (c) The pin-to-pin ESD stress: the ESD voltage is applied to an input (or output) pin while all other input or output pins are grounded but the VDD and VSS pins are floating. (d) The VDD-to-VSS ESD stress: the ESD voltage is directly applied to the VDD pin with the VSS pin grounded but all input and output pins are floating.