# 國立交通大學

電子工程學系電子研究所

博士論文

具有基體觸發技術之矽控整流器 及其在積體電路晶片靜電放電防護上之應用

# SILICON-CONTROLLED RECTIFIER WITH SUBSTRATE-TRIGGERED TECHNIQUE FOR ON-CHIP ESD PROTECTION IN CMOS INTEGRATED CIRCUITS

研究生:徐國鈞

指導教授: 柯明道

中華民國 九十二年九月

# 具有基體觸發技術之矽控整流器 及其在積體電路晶片靜電放電防護上之應用

# SILICON-CONTROLLED RECTIFIER WITH SUBSTRATE-TRIGGERED TECHNIQUE FOR ON-CHIP ESD PROTECTION IN CMOS INTEGRATED CIRCUITS

研究生:徐國鈞 Student: Kuo-Chun Hsu

指導教授:柯明道 Advisor: Ming-Dou Ker

國立交通大學電子工程學系電子研究所博士論文

A Dissertation

Submitted to

Institute of Electronics

College of Electrical Engineering

And Computer Science

National Chiao Tung University

For the Degree of Doctor of Philosophy

in

Electronic Engineering

September 2003 Hsinchu, Taiwan, Republic of China

中華民國九十二年九月

# 具有基體觸發技術之矽控整流器 及其在積體電路晶片靜電放電防護上之應用

研究生:徐國鈞 指導教授:柯明道

#### 國立交通大學電子工程學系電子研究所

### 摘要

在眾多的靜電放電(Electrostatic Discharge, ESD)防護元件中[如:二極體 (Diode)、矽控整流器(SCR)、雙載子電晶體(BJT)、金氧半場效電晶體 (MOSFET)或者是場氧化層電晶體(Field Oxide Device, FOD)],矽控整流器在互補式金氧半導體(CMOS)製程技術中,具有最高的靜電放電防護能力,應用在晶片上當靜電放電防護元件也有一段很長的時間。矽控整流器(SCR)基本特性是由電流觸發而導通的元件,所以當有一電流施加於矽控整流器的基體時,矽控整流器可以很快地經由正回授再生機制(Positive-Feedback Regeneration Mechanism)觸發進入閉鎖狀態,而不需透過原本的纍增崩潰機制(Avalanche Breakdown Mechanism)。本論文深入研究矽控整流器與電流觸發的基本關係,利用電流觸發的概念並進一步設計出相關的控制電路,並實際應用在積體電路晶片上之靜電放電防護電路。

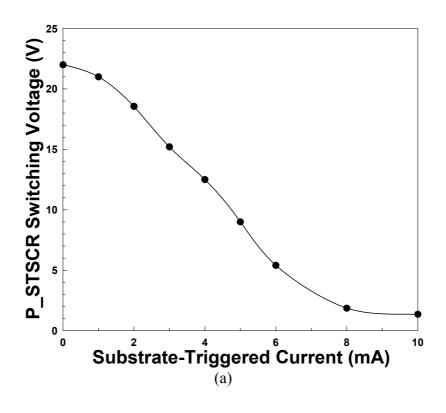

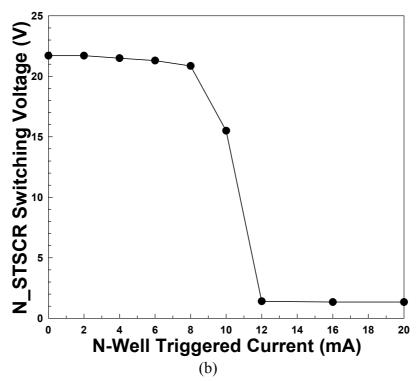

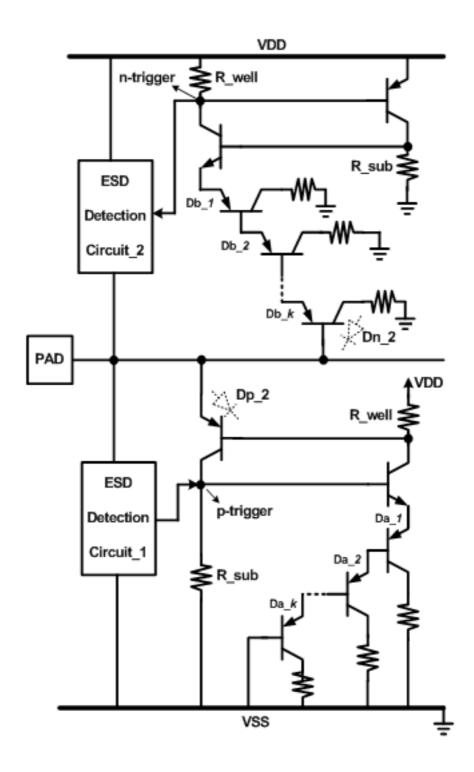

在本論文中,首先提出具有互補電路型式的基體觸發矽控整流器,用來排放焊墊到 VDD 或 VSS 電源腳位的靜電放電電流。此新型的互補式基體觸發矽控整流器具有以下優點:可調整的切換電壓(Switching Voltage)、低持有電壓(Holding Voltage)、較快的導通速度(Turn-on Speed)、以及製程步驟完全相容於一般互補式金氧半導體的製程,不需增加額外的光罩如遮蔽金屬矽化物光罩(Silicide-Blocking Mask)和離子佈植(ESD Implantation)光

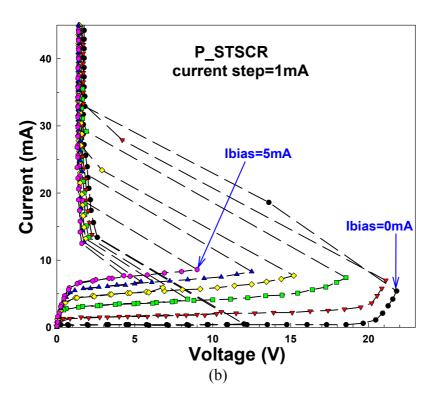

罩。在 0.25 微米全金屬矽化的互補式金氧半導體製程中,當基體觸發電流由零增加到 8 mA 時,基體觸發矽控整流器的切換電壓會由原本高達 22 V 的電壓準位降到只有 1.85 V,非常接近其持有電壓(約 1.35 V)。而且,當觸發脈衝電壓的準位由 1.5 V 增加到 4 V 時,基體觸發矽控整流器的導通時間 (Turn-on Time)可由 27.4 ns 縮短到只有 7.8 ns,具有明顯增進導通速度的效果。

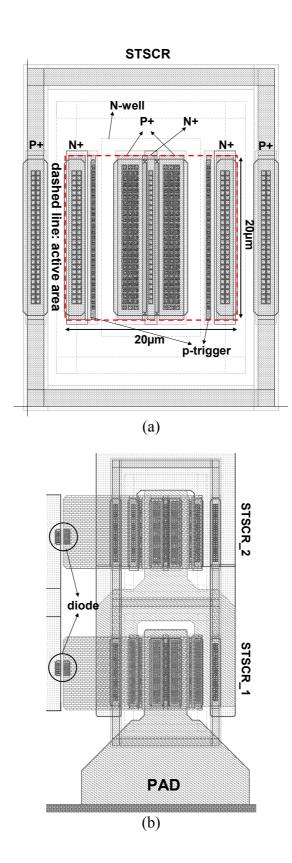

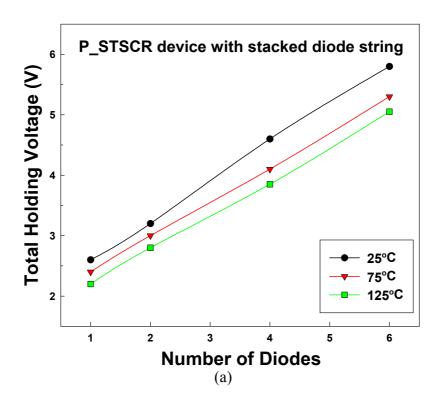

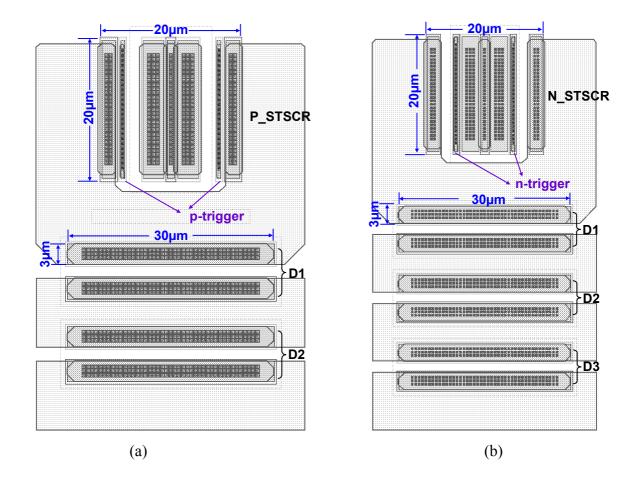

基體觸發矽控整流器在本論文實際製作中具有的主動面積(Active Area) 只有 20 微米×20 微米的大小,這麼小的佈局面積使得基體觸發矽控整流器 在靜電放電防護電路設計中可以被堆疊以避免暫態過程所引發的閉鎖效應 (Transient-Induced Latchup Issue)。對於 VDD 為 2.5 V 的 0.25 微米全金屬矽化的互補式金氧半積體電路應用而言,具有兩個基體觸發矽控整流器堆疊結構的靜電放電防護電路,其箝制電壓約為 3.2 V,可免於閉鎖效應的危險,且仍可承受大於 8 kV 的人體放電模式(Human-Body-Model, HBM)及 700 V 的機械放電模式(Machine-Model, MM)的靜電放電耐受能力。此外,基體 觸發矽控整流器的整體持有電壓也可藉由疊接二極體串來達到線性的增加。由互補式基體觸發矽控整流器搭配兩個二極體所設計的靜電放電防護電路,不具有閉鎖效應的疑慮,並可應用在輸出輸入焊垫(I/O Pads) 及 VDD/VSS 電源焊垫使用之靜電放電防護電路,在 0.25 微米全金屬矽化的互補式金氧半導體製程中也實際被製作,在很小的佈局面積下具有 7.25 kV 的人體放電模式及 500 V 的機械放電模式的靜電放電耐受能力。

導通效率一直是矽控整流器作為晶片上靜電放電防護電路的主要隱憂,特別是在未來奈米製程中具有超薄閘氧化層的互補式金氧半導體製程。也由於矽控整流器的元件結構中,包含了一横向的 NPN 及一縱向的 PNP 雙載子電晶體,於是本論文另外提出了創新的雙觸發技術,同時觸發 NPN 和 PNP 電晶體,更能增快矽控整流器的導通速度,用作於晶片上的靜電放電防護電路,能更有效地保護在未來奈米互補式金氧半導製程中的超薄閘氧化層。從 0.25 微米互補式金氧半製程中的實驗結果得知,具有 20 微米×20 微米佈局面積的雙觸發矽控整流器,其切換電壓和導通時間均會

因雙觸發技術而更有效地降低。雙觸發矽控整流器的切換電壓,在N井觸發電流為-3 mA之下,會進一步地由21 V降低至1.5 V,當基體觸發電流由0 mA增加至3 mA 時。在P型觸發端施加固定的一1.5 V正的脈衝電壓,且施加在N型觸發端負電壓脈衝的絕對脈衝高度由0 V增加到5 V的條件下,雙觸發矽控整流器的導通時間會由37.6 ns 大幅縮短至11.8 ns。

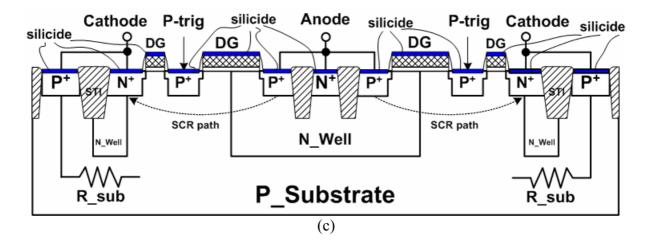

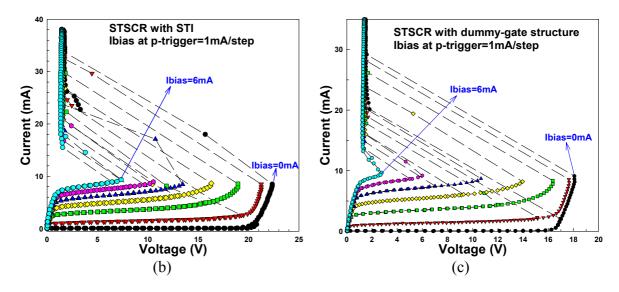

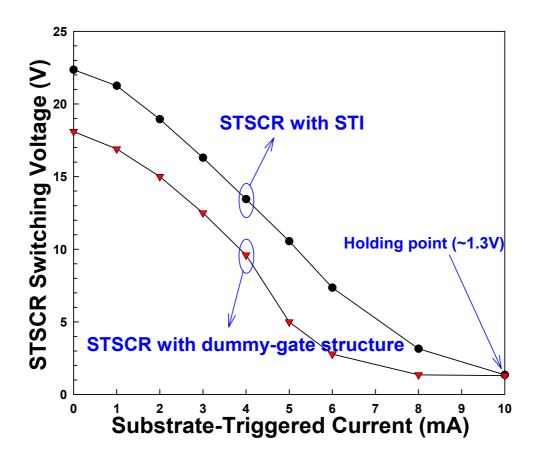

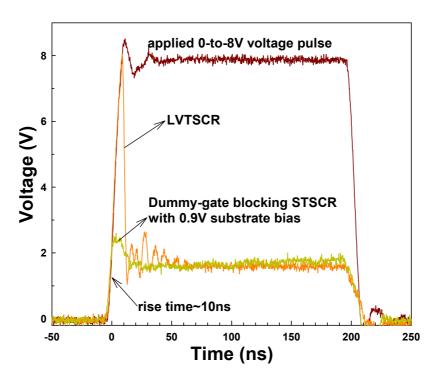

本論文另外也提出了一種帶有基體觸發技術和假閘極阻隔結構的矽控整流器用來改善矽控整流器的導通速度,用於晶片上的靜電放電防護電路,可為較薄的閘氧化層提供更有效的防護。這種具有假閘極結構的矽控整流器其製程是完全相容於一般互補式金氧半導體的製程,不需增加額外的光罩及製程步驟。從閘氧化層厚度為 50 埃的 0.25 微米互補式金氧半製程中的實驗結果得知,和一般具有淺溝槽隔離(Shallow Trench Isolation, STI)結構的矽控整流器相比,具有假閘極結構的基體觸發矽控整流器其切換電壓、導通速度、導通電阻(Turn-on Resistance)和元件充電放電模式(Charged-Device-Model, CDM)的靜電放電耐受能力均有顯著的改善。當施加於P型觸發端的基體觸發電流由 0 mA 增加至 6 mA 時,具有淺溝槽隔離結構的矽控整流器其切換電壓會由 22 V 降低至 7 V,但具有假閘極結構的矽控整流器其切換電壓會由 22 V 降低至 7 V,但具有假閘極結構的矽控整流器其切換電壓卻會由 18 V 大大地降低至 3 V。

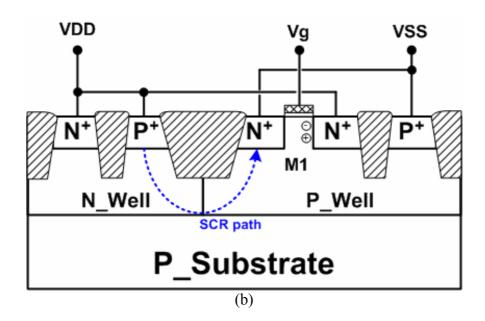

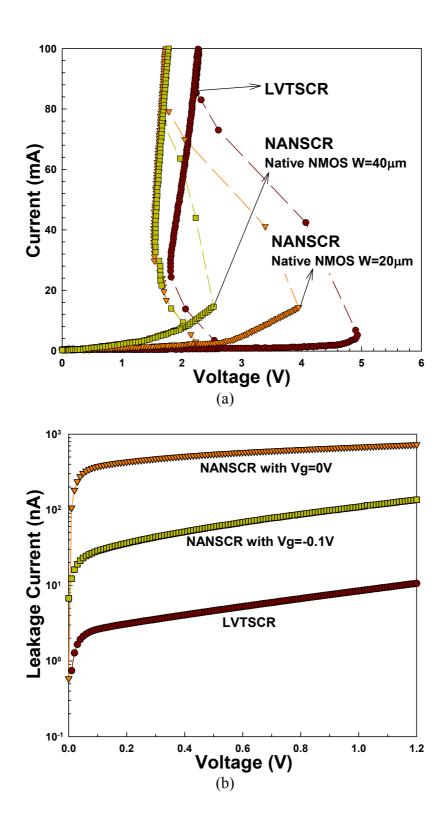

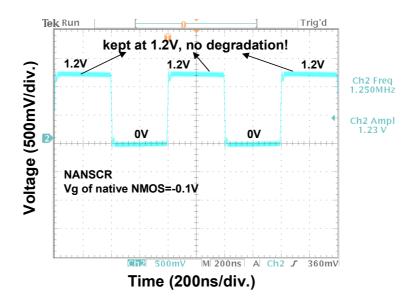

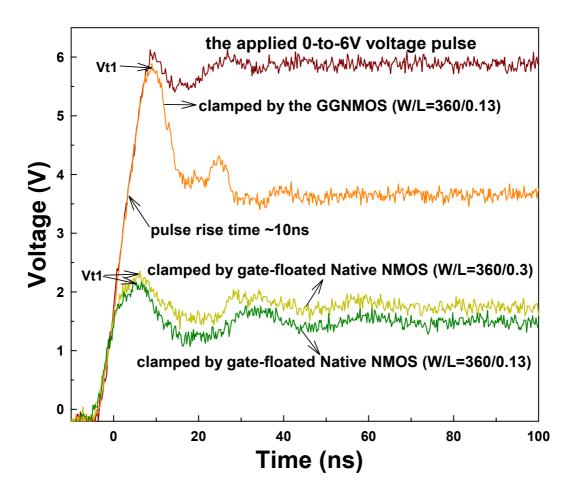

為了能快速地將靜電放電能量排放及有效率地保護超薄閘氧化層,本論文另外提出了一種新型的原生性 N 型金氧半電晶體觸發矽控整流器 (Native-NMOS-Triggered SCR, NANSCR),作為晶片上的靜電放電防護。在靜電放電發生的情況下,原生性 N 型金氧半電晶體(Native NMOS)是一已導通的元件,故可以快速地引導靜電放電電流去觸發矽控整流器進入閉鎖狀態,最後,靜電放電電流便可透過導通的原生性 N 型金氧半電晶體觸發矽控整流器排放掉。從供應電壓為 1.2 V 的 0.13 微米互補式金氧半製程中的實驗結果得知,和傳統的低壓觸發矽控整流器(Low-Voltage Triggering SCR, LVTSCR)相比,原生性 N 型金氧半電晶體觸發矽控整流器的切換電壓、持有電壓、導通電阻、導通速度和元件充電放電模式的靜電放電耐受能力均有明顯的改善,更能保護超薄閘氧化層對抗靜電放電的應力(ESD Stress)。

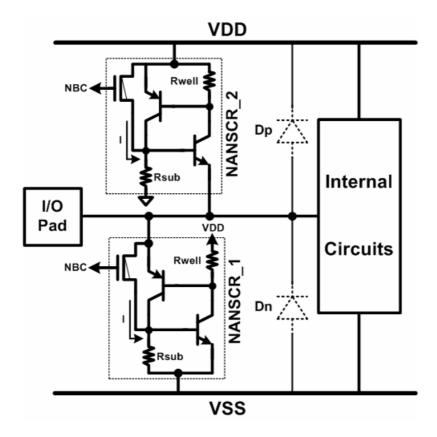

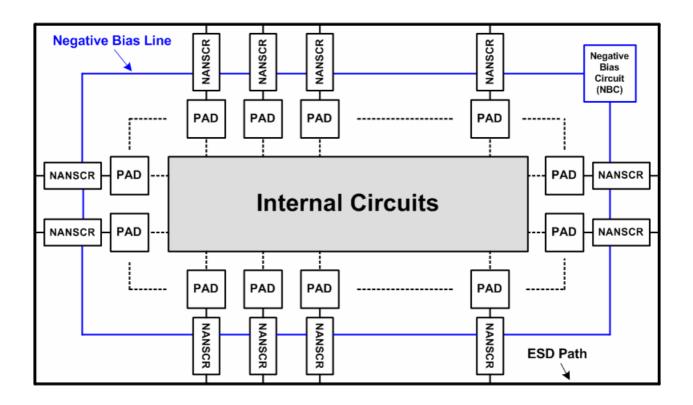

所提出的原生性N型金氧半電晶體觸發矽控整流器可被運用在輸入、輸出和電源線間的靜電放電防護電路且可免於閉鎖效應的危險。利用所提出的原生性N型金氧半電晶體觸發矽控整流器設計而成的全晶片靜電放電防護架構(Whole-Chip ESD Protection Scheme),也已經藉有針腳對針腳(Pin-to-Pin)靜電放電測試的數據去驗證其保護效能。對於具有多電源準位的超大型互補式金氧半積體電路而言,所提出具有原生性N型金氧半電晶體觸發矽控整流器和靜電放電路徑(ESD Path)的全晶片靜電放電防護架構,是一種可以快速地排放所有靜電放電應力和有效保護內部電路的創新解決方案。

在本博士論文中,共計有五種利用基體觸發技術所設計出的矽控整流器元件,每一種元件之效能均已在實際晶片上成功驗證,並有相對應的國際期刊論文發表。本論文所研發之基體觸發矽控整流器及其相關電路設計,非常適合應用在深次微米以及未來奈米半導體製程所製作的積體電路晶片上,以有效提昇積體電路對靜電放電的防護能力。

# SILICON-CONTROLLED RECTIFIER WITH SUBSTRATE-TRIGGERED TECHNIQUE FOR ON-CHIP ESD PROTECTION IN CMOS INTEGRATED CIRCUITS

Student: Kuo-Chun Hsu Advisor: Ming-Dou Ker

Department of Electronics Engineering and Institute of Electronics National Chiao Tung University

#### **ABSTRACT**

With the highest electrostatic discharge (ESD) robustness in the smallest layout area, the silicon-controlled rectifier (SCR) device had been used in the on-chip ESD protection circuits for a long time among various ESD protection devices (such as the diode, SCR, BJT, MOS, or field oxide device) in CMOS technologies. The turn-on mechanism of a SCR device is essentially a current triggering event. While a current is applied to the base or substrate of the SCR device, it can be quickly triggered on into its latching state through the positive-feedback regeneration mechanism without involving the original avalanche breakdown mechanism. In this thesis, the dependence of the device characteristics of SCR on the triggering current is investigated in details. Then, based on the current triggering mechanism of SCR device, the corresponding ESD detection circuits are proposed to generate the triggering currents. Finally, the on-chip ESD protection circuit with the SCR devices and current-triggering circuits are realized to protect the CMOS ICs.

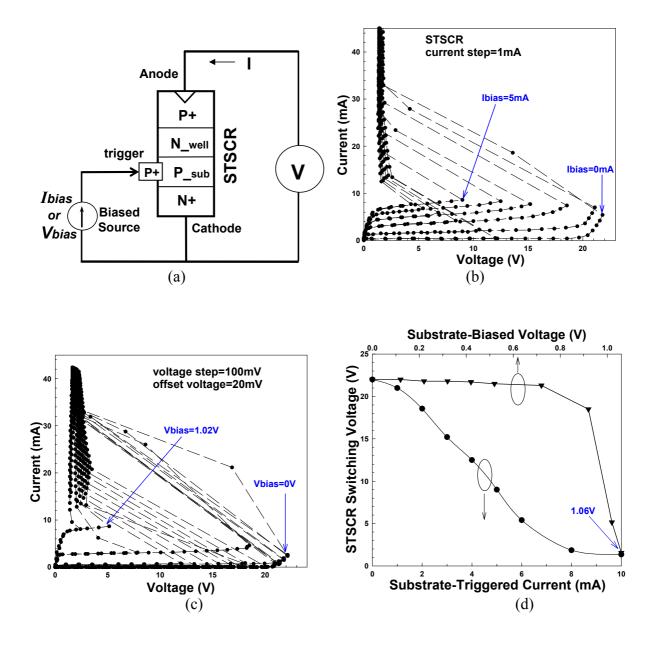

First, a complementary circuit style with the substrate-triggered SCR (STSCR) devices is designed to discharge both of the pad-to-VSS and pad-to-VDD ESD stresses. The novel complementary STSCR devices have the advantages of controllable switching voltage, lower holding voltage, faster turn-on speed, and fully process-compatible to general CMOS processes without extra process modification such as the silicide-blocking mask and ESD

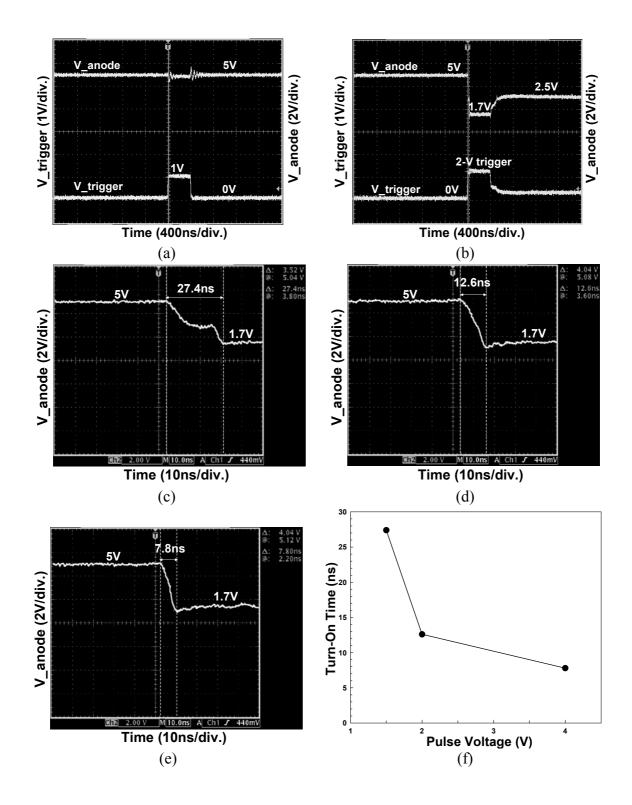

implantation. The switching voltage of the fabricated STSCR device can be reduced from ~22 to only 1.85 V, which almost equals to the holding voltage (~1.35 V) of the STSCR, when the substrate-triggered current is increased to 8 mA in a 0.25-μm fully salicided CMOS process. The turn-on time of the STSCR device can be reduced from 27.4 to 7.8 ns, while the pulse height of the triggering voltage pulse is increased from 1.5 to 4 V.

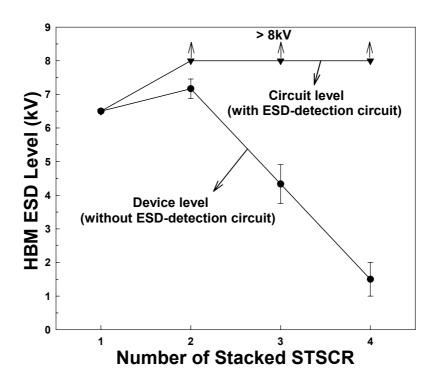

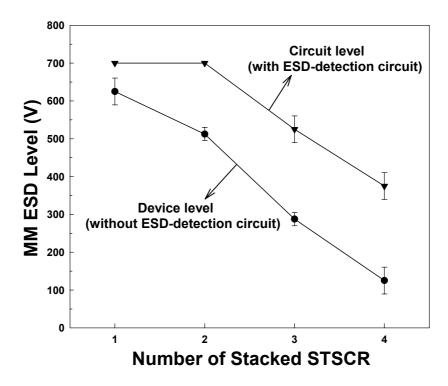

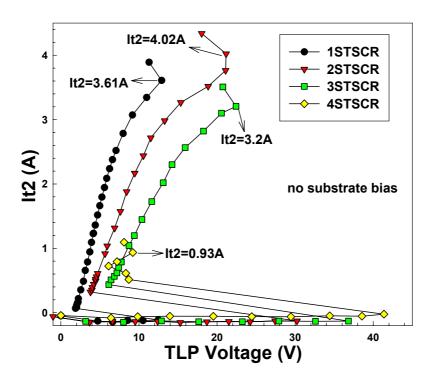

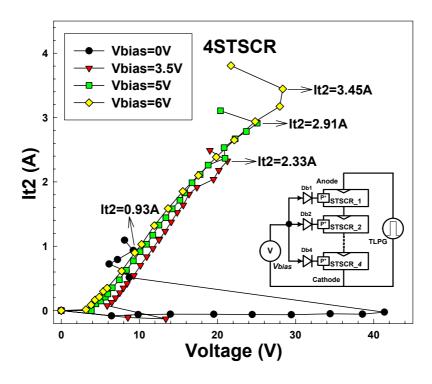

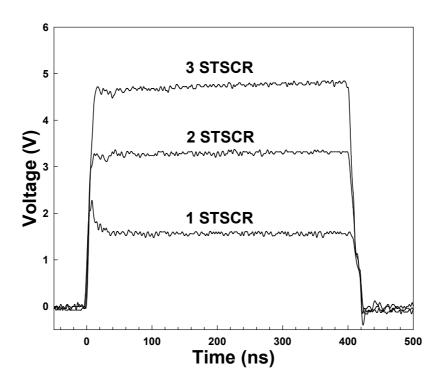

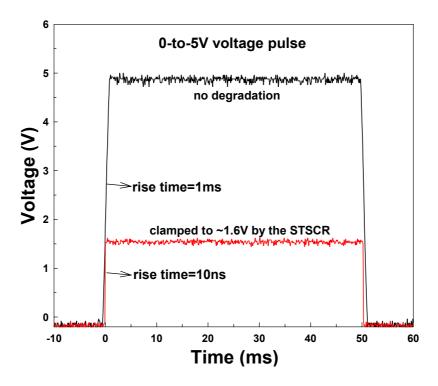

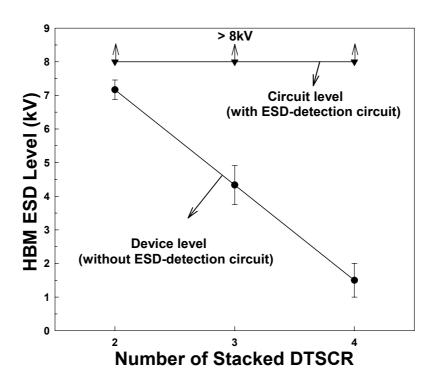

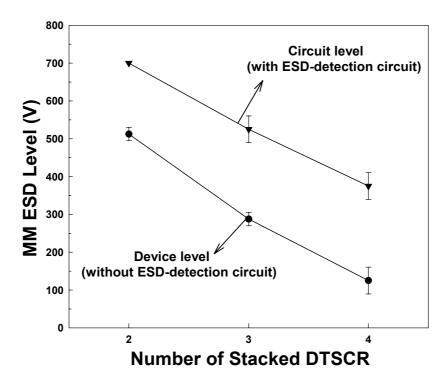

The STSCR device with a small active area of only 20  $\mu$ m×20  $\mu$ m can be stacked in the ESD protection circuits to avoid the transient-induced latch-up issue. For the IC application with VDD of 2.5 V, the ESD protection circuit designed with two STSCR devices in stacked configuration has a clamp voltage of ~3.2 V, free from latchup issue, and the human-body-model (HBM) (machine-model (MM)) ESD level of > 8 kV (700 V) in a 0.25- $\mu$ m fully salicided CMOS process. In addition, the total holding voltage of the STSCR device can be linearly increased by adding the stacked diode string. The on-chip latchup-free ESD protection circuits designed with the proposed complementary STSCR devices and two stacked diode string for the I/O pads and power pad have been successfully verified in a 0.25- $\mu$ m salicided CMOS process with the HBM (MM) ESD level of ~7.25 kV (500 V) in a small layout area.

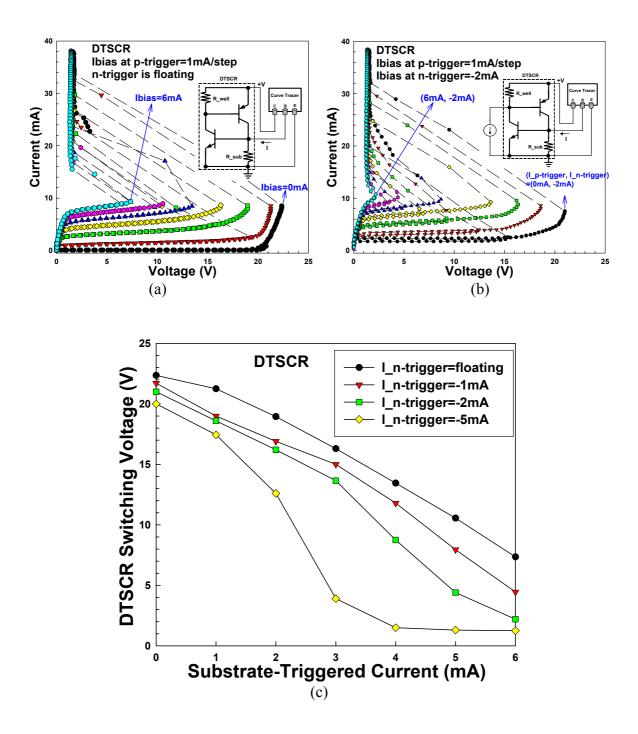

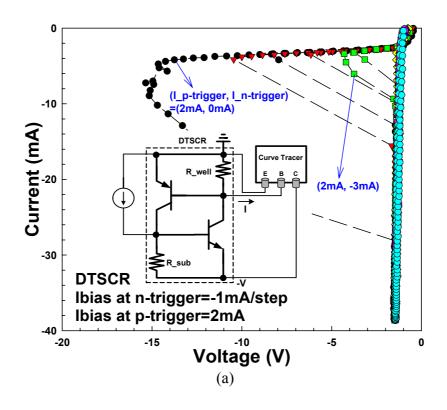

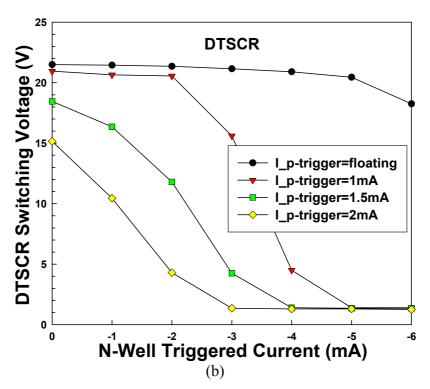

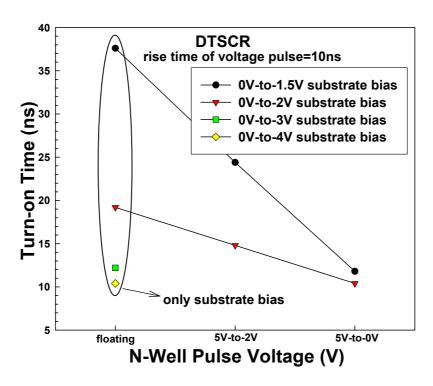

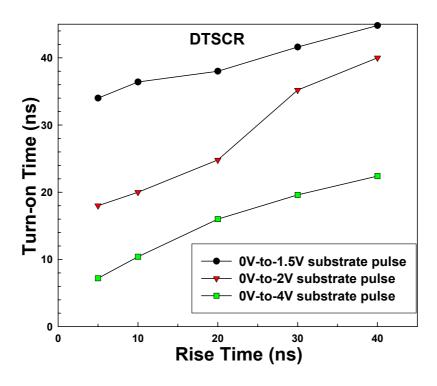

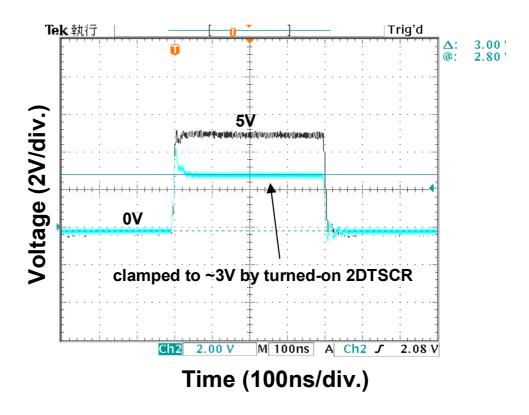

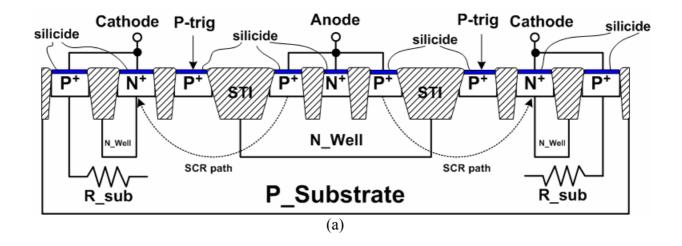

Turn-on efficiency is the main concern for SCR devices used as on-chip ESD protection circuit, especially in future nanoscale CMOS processes with ultra-thinn gate oxide. The SCR device consists of a lateral NPN and a vertical PNP bipolar transistors, which is inherent in the CMOS processes. In this thesis, a novel double-triggered technique, used to synchronously trigger the NPN and PNP transistors in the SCR structure, is also proposed to further improve the turn-on speed of SCR devices for using in on-chip ESD protection circuit to effectively protect the much thinner gate oxide in nanoscale CMOS processes. From the experimental results in a 0.25- $\mu$ m salicided CMOS process, the switching voltage and turn-on time of such double-triggered SCR (DTSCR) device, which is drawn as 20  $\mu$ m×20  $\mu$ m, has been confirmed to be reduced more efficiently by this double-triggered technique. The switching voltage of DTSCR under the N-well triggered current of -3 mA is further reduced from ~21 to ~1.5 V, when the substrate-triggered current is increased from 0 to 2 mA. Under the positive voltage pulse of 1.5 V at p-trigger node, the turn-on time of DTSCR can be reduced from 37.6 to 11.8 ns, while the absolute pulse height of negative voltage pulse applied to the n-trigger node is increased from 0 to 5 V.

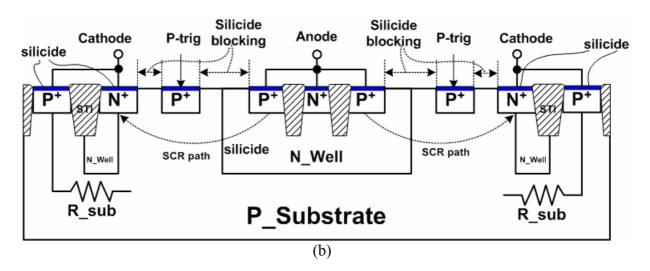

A novel dummy-gate-blocking SCR device with substrate-triggered technique is also

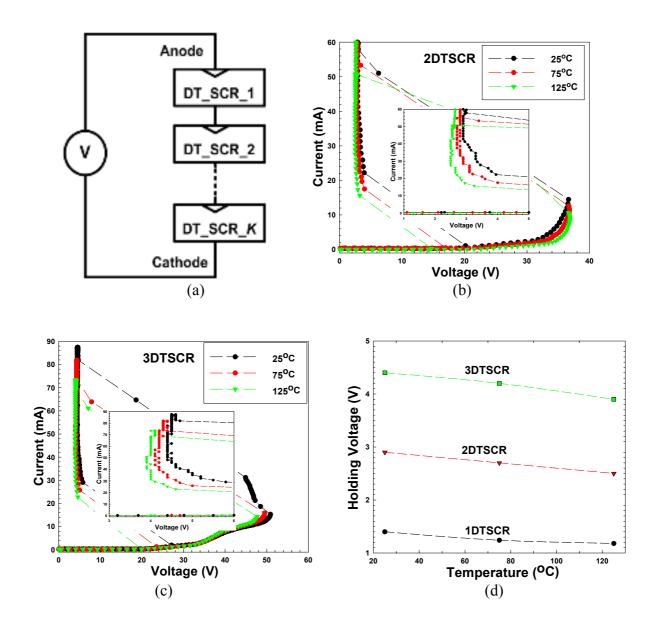

proposed to improve the turn-on speed of SCR device for using in the on-chip ESD protection circuit to effectively protect the much thinner gate oxide. The fabrication of the proposed SCR device with dummy-gate structure is fully process-compatible to general CMOS process, without using extra mask layer or increasing process step. From the experimental results in a 0.25-µm CMOS process with the gate-oxide thickness of ~50 Å, the switching voltage, turn-on speed, turn-on resistance, and charged-device-model (CDM) ESD levels of the SCR device with dummy-gate structure have been greatly improved, as compared to the normal SCR with shallow trench isolation (STI) structure. When the substrate-triggered current applied at the p-trigger node is increased from 0 to 6 mA, the switching voltage of STSCR with STI is reduced from ~22 to ~7 V, whereas that of STSCR with dummy-gate structure is greatly reduced from ~18 to ~3 V.

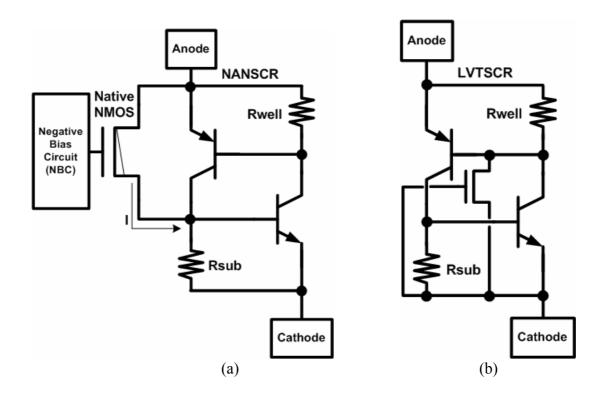

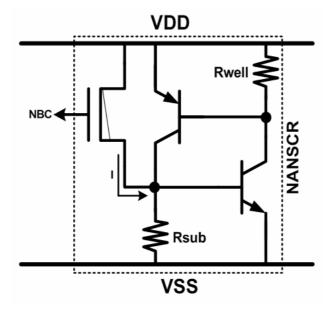

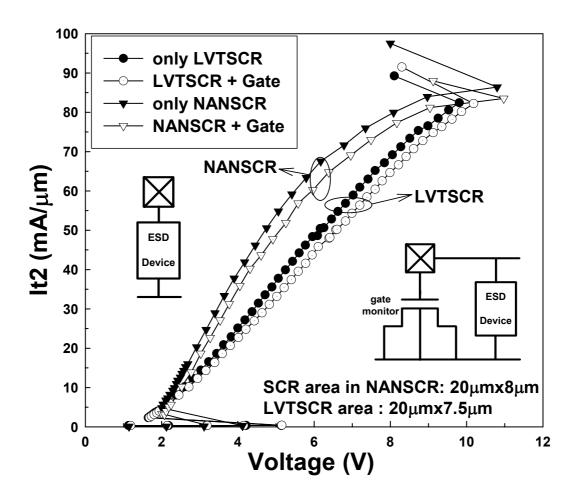

In order to quickly discharge the ESD energy and to efficiently protect the ultra-thin gate oxide, a novel native-NMOS-triggered SCR (NANSCR) is proposed for on-chip ESD protection. Native NMOS is an already-on device under ESD events, so it can quickly conduct some ESD current to trigger SCR into latching state. Then, ESD current can be quickly discharged through the turned-on NANSCR device. From the experimental results in a 0.13-µm CMOS process with voltage supply of 1.2 V, the switching voltage, holding voltage, turn-on resistance, turn-on speed, and CDM ESD level of NANSCR can be greatly improved to protect the ultra-thin gate oxide against ESD stresses, as compared with the traditional low-voltage triggering SCR (LVTSCR). The proposed NANSCR can be designed for the input, output, and power-rail ESD protection circuits without latchup danger. A new whole-chip ESD protection scheme realized with the proposed NANSCR devices is also demonstrated with the consideration of pin-to-pin ESD zapping. For ultra large-scale CMOS ICs with multiple power pins, the proposed whole-chip ESD protection scheme with NANSCR and ESD path is an overall solution to quickly discharge all kinds of ESD stresses and to provide efficient protection for the internal circuits.

In summary, there are totally 5 different designs on substrate-triggered SCR devices developed in this thesis. Each of the substrate-triggered SCR devices and its corresponding circuit for ESD protection have been successfully verified in the testchips and also published in the International Journals or Transactions. The developed substrate-triggered SCR devices are highly useful for on-chip ESD protection in the sub-quarter-micron CMOS integrated circuits without process modification.

## 誌謝

首先要感謝我的指導教授柯明道教授三年來的耐心指導與鼓勵,使我 能順利完成博士學業。專業上,在指導教授循序漸進的教誨下,讓我得以 在積體電路靜電放電防護設計的領域中,由入門到能夠獨立解決問題;人 格上,指導教授認真的研究態度及嚴謹的處事原則,也讓我學習了挑戰困 難及解決問題的正確態度與方法。雖然在過程中倍感艱辛,然而卻獲益良 多,更促使我成長。此外還要感謝實驗室中另外四位教授,吳重雨、吳介 琮、吳錦川及陳巍仁教授給我的許多指導與建議。

在這段求學的過程中,『奈米電子與晶片系統實驗室』是孕育我成長的溫床,由學長、同學及學弟們在長期的努力下,使得我們無論在軟體及硬體的需求上能夠一應俱全。而在如此優良的環境下,無論與學長、同學及學弟間在學業上的互相切磋,或共同為實驗室的運作而付出心力,都使得我在學業及處事上,能有更深一層的受惠,也因此我的論文才得以順利完成。在此感謝陳東暘、羅文裕、王文泰、林子超、鄭秋宏、廖以義、施育全、徐建昌、周儒明、黃冠勳、林俐如、周忠昀、傅昶綜、范啟威、林昆賢、徐新智、鄧至剛、陳世倫、王文傑諸位實驗室學長、同學及學弟妹們,在我博士班的這一個階段,於各方面給了我不少的幫忙,而使得我能順利也完成我的論文以及在知識及處事上有所成長。也感謝實驗室助理:李婷媛小姐以及卓慧真小姐在實驗室行政事務上的許多協助。

在此還要特別感謝工業技術研究院系統晶片技術中心的姜信欽、彭政傑、張智毅、莊哲豪、曾當貴、蔡燿城、陳子平、侯春麟在實驗晶片下線 及量測上的幫忙,使得我的研究論文能在台灣及國際上順利發表,獲得肯 定。

最後,我要致上我最深最深的感謝給予我的父親徐義忠先生,母親曾 鳳嬌女士,沒有您們無怨悔、永無止境的付出、鼓勵、支持與照顧,就沒 有我今日的成就,在此衷心地感謝您們。另外,要祝福所有在這幾年與我 相處過的師長、朋友、學弟妹們,有緣與您們同在這一個階段成長,是我 一生的榮幸,願大家都能順心如意,心想事成!

> 徐 國 鈞 謹誌於竹塹交大 九十二年 九月

### **CONTENTS**

| ABSTR              | ACT (CHINESE)                                           | i   |  |  |  |

|--------------------|---------------------------------------------------------|-----|--|--|--|

| ABSTRACT (ENGLISH) |                                                         |     |  |  |  |

| ACKN               | ACKNOWLEDGEMENTS CONTENTS                               |     |  |  |  |

| CONTI              |                                                         |     |  |  |  |

| TABLE CAPTIONS     |                                                         |     |  |  |  |

| FIGUR              | E CAPTIONS                                              | xiv |  |  |  |

| СНАРТ              | TER 1 INTRODUCTION                                      | 1   |  |  |  |

| 1.1                | BACKGROUND                                              | 1   |  |  |  |

| 1.2                | TURN-ON MECHANISM OF SCR DEVICE                         | 2   |  |  |  |

| 1.3                | SCR-BASED DEVICES FOR CMOS ON-CHIP ESD PROTECTION       | 3   |  |  |  |

| 1.4                | SCR LATCHUP ENGINEERING                                 | 10  |  |  |  |

| 1.5                | THESIS ORGANIZATION                                     | 13  |  |  |  |

| TA                 | BLES                                                    | 16  |  |  |  |

| FIC                | GURES                                                   | 17  |  |  |  |

| CHAPT              | TER 2 DEVICE CHARACTERISTICS OF SUBSTRATE-TRIGGERED SCR | 29  |  |  |  |

| 2.1                | SUBSTRATE-TRIGGERED SCR (STSCR) DEVICE                  | 29  |  |  |  |

| 2.2                | ON-CHIP ESD PROTECTION CIRCUITS WITH STSCR DEVICES      | 33  |  |  |  |

|                    | 2.2.1 ESD Protection Circuit for the Input/Output Pads  | 33  |  |  |  |

|                    | 2.2.2 ESD Clamp Circuit between the Power Rails         | 34  |  |  |  |

|                    | 2.2.3 Simulation Results                                | 34  |  |  |  |

| 2.3                | EXPERIMENTAL RESULTS                                    | 36  |  |  |  |

| 2.4                | SUMMARY                                                 | 39  |  |  |  |

| TA                 | BLES                                                    | 41  |  |  |  |

| FIC                | GURES                                                   | 42  |  |  |  |

| СН | IAPT        | TER 3 | DESIGN TECHNIQUE AND OPERATING PRINCIPLE OF ESD PROTECTION DESIGN WITH COMPLEMENTARY SUBSTRATE-TRIGGERED SCR DEVICES | 56  |

|----|-------------|-------|----------------------------------------------------------------------------------------------------------------------|-----|

|    | 3.1         | CON   | MPLEMENTARY SUBSTRATE-TRIGGERED SCR DEVICES                                                                          | 56  |

|    |             | 3.1.1 | Device Structure                                                                                                     | 56  |

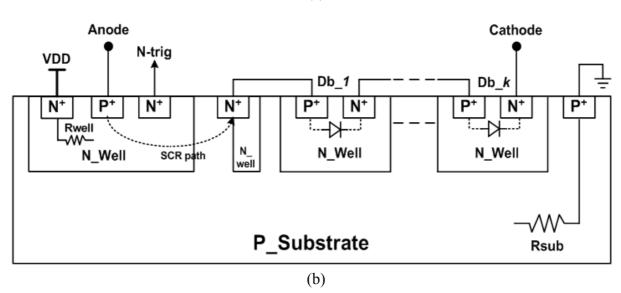

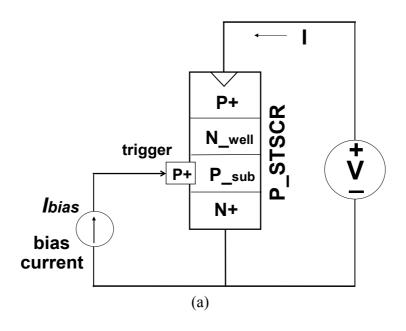

|    |             | 3.1.2 | I-V Characteristics of the STSCR Devices                                                                             | 57  |

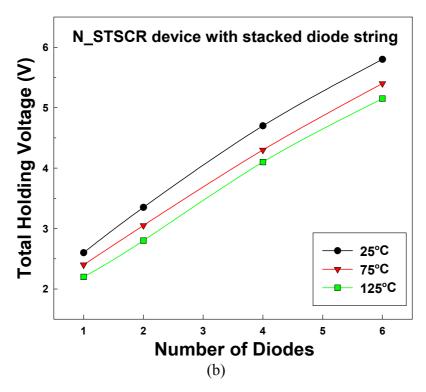

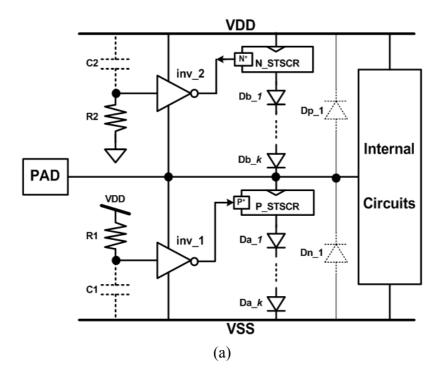

|    | 3.2         |       | CHIP ESD PROTECTION CIRCUITS WITH COMPLEMENTARY CR DEVICES                                                           | 59  |

|    |             | 3.2.1 | ESD Protection Circuit for the Input/Output Pads                                                                     | 59  |

|    |             | 3.2.2 | ESD Clamp Circuit between the Power Rails                                                                            | 62  |

|    | 3.3         | EXP   | ERIMENTAL RESULTS                                                                                                    | 63  |

|    |             | 3.3.1 | ESD Robustness                                                                                                       | 63  |

|    |             | 3.3.2 | Turn-On Verification                                                                                                 | 64  |

|    | 3.4         | SUM   | MMARY                                                                                                                | 66  |

|    | FIG         | URES  |                                                                                                                      | 67  |

| CH | <b>IAPT</b> | TER 4 | SCR DEVICE WITH DOUBLE-TRIGGERED TECHNIQUE FOR EFFECTIVE ON-CHIP ESD PROTECTION                                      | 84  |

|    | 4.1         | DOU   | JBLE-TRIGGERED SCR (DTSCR) DEVICE                                                                                    | 84  |

|    |             | 4.1.1 | Device Structure                                                                                                     | 84  |

|    |             | 4.1.2 | Device I-V Characteristics                                                                                           | 85  |

|    |             | 4.1.3 | Turn-On Speed                                                                                                        | 87  |

|    | 4.2         | APP   | LICATIONS FOR ON-CHIP ESD PROTECTION                                                                                 | 89  |

|    |             | 4.2.1 | ESD Protection Circuit for the Input/Output Pad                                                                      | 89  |

|    |             | 4.2.2 | ESD Clamp Circuit between the Power Rails                                                                            | 93  |

|    |             | 4.2.3 | ESD Robustness                                                                                                       | 93  |

|    |             | 4.2.4 | Turn-On Verification                                                                                                 | 94  |

|    | 4.3         | SUM   | MARY                                                                                                                 | 95  |

|    | FIG         | URES  |                                                                                                                      | 96  |

| СН | <b>IAPT</b> | TER 5 | SCR DEVICE FABRICATED WITH DUMMY-GATE STRUCTURE                                                                      | 110 |

|    | 5.1         | SCR   | DEVICE WITH DUMMY-GATE STRUCTURE                                                                                     | 110 |

|        | 5.2 | EXPERIMENTAL RESULTS                                              | 112 |

|--------|-----|-------------------------------------------------------------------|-----|

|        |     | 5.2.1 Device Characteristics                                      | 112 |

|        |     | 5.2.2 Turn-On Speed                                               | 113 |

|        |     | 5.2.3 ESD Robustness                                              | 115 |

|        | 5.3 | SUMMARY                                                           | 117 |

|        | TAI | BLES                                                              | 118 |

|        | FIG | FURES                                                             | 119 |

| СН     | APT | TER 6 ON-CHIP ESD PROTECTION DESIGN WITH NATIVE-NMOSTRIGGERED SCR | 127 |

|        | 6.1 | NATIVE-NMOS-TRIGGERED SCR (NANSCR) DEVICE                         | 127 |

|        |     | 6.1.1 Device Structure                                            | 127 |

|        |     | 6.1.2 Characteristics of NANSCR                                   | 128 |

|        | 6.2 | ON-CHIP ESD PROTECTION DESIGN WITH NANSCR                         | 129 |

|        |     | 6.2.1 ESD Protection Circuit for Input/Output Pads                | 129 |

|        |     | 6.2.2 ESD Clamp Circuit between Power Rails                       | 130 |

|        |     | 6.2.3 Whole-Chip ESD Protection Scheme                            | 131 |

|        | 6.3 | EXPERIMENTAL RESULTS                                              | 132 |

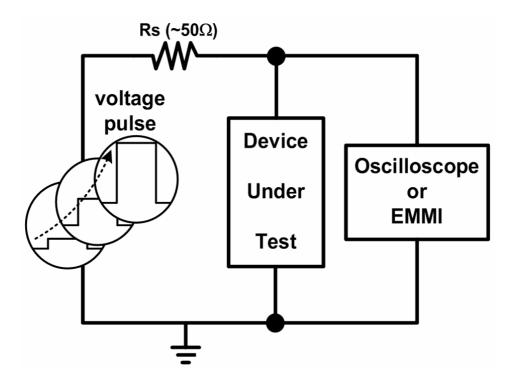

|        |     | 6.3.1 Turn-On Verification                                        | 132 |

|        |     | 6.3.2 EMMI Photographs                                            | 134 |

|        |     | 6.3.3 TLP Measurement                                             | 135 |

|        |     | 6.3.4 ESD Robustness                                              | 136 |

|        | 6.4 | SUMMARY                                                           | 137 |

| TABLES |     |                                                                   |     |

|        | FIG | URES                                                              | 139 |

| СН     | APT | TER 7 CONCLUSIONS AND FUTURE WORKS                                | 151 |

|        | 7.1 | MAIN RESULTS OF THIS THESIS                                       | 151 |

|        | 7.2 | FUTURE WORKS                                                      | 153 |

| REFERENCES       | 154 |

|------------------|-----|

| VITA             | 160 |

| PUBLICATION LIST | 161 |

## **TABLE CAPTIONS**

#### **CHAPTER 1**

**TABLE 1.1** Comparison among the SCR-based devices for on-chip ESD protection.

#### **CHAPTER 2**

**TABLE 2.1** Comparison on the ESD robustness between the stacked STSCR devices and the GGNMOS.

#### **CHAPTER 5**

**TABLE 5.1** Comparison on the ESD robustness between the STSCR with STI and dummy-gate structures.

#### **CHAPTER 6**

**TABLE 6.1** Comparison on the ESD robustness between NANSCR and LVTSCR.

### FIGURE CAPTIONS

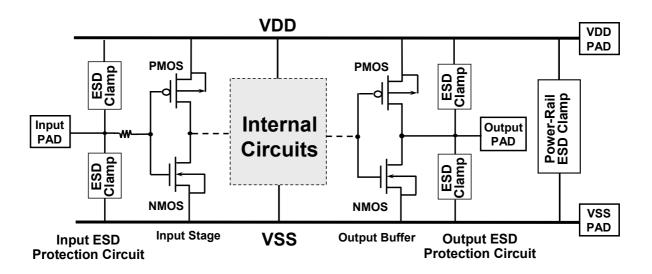

- **Fig. 1.1** The typical design of on-chip ESD protection circuits in CMOS ICs.

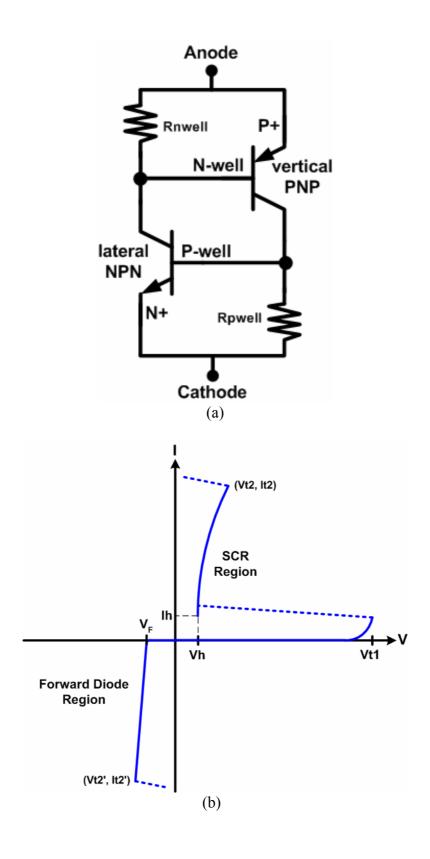

- **Fig. 1.2** (a) The equivalent circuit schematic of a SCR device. (b) The I-V characteristics of SCR device in CMOS process under positive and negative voltage biases.

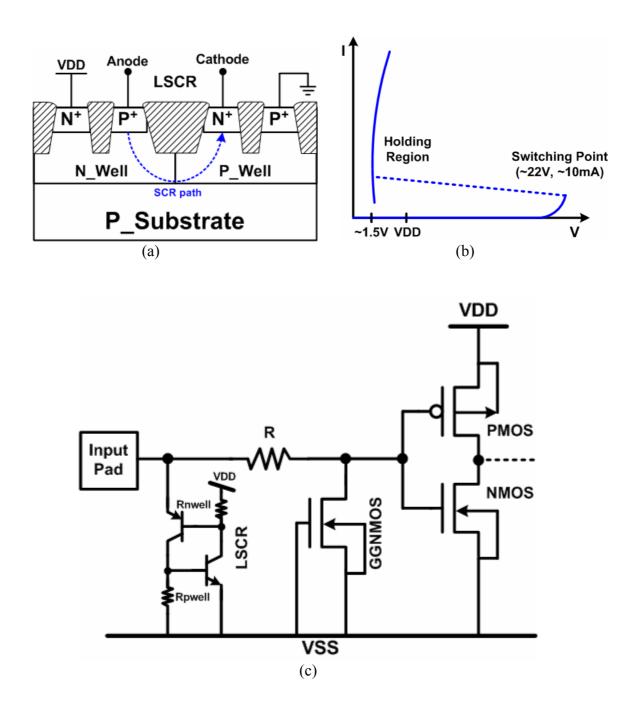

- **Fig. 1.3** (a) The device structure of the lateral SCR (LSCR) in CMOS process. (b) The I-V characteristics of the LSCR in a 0.25-μm CMOS process. (c) The input ESD protection circuit with the LSCR device.

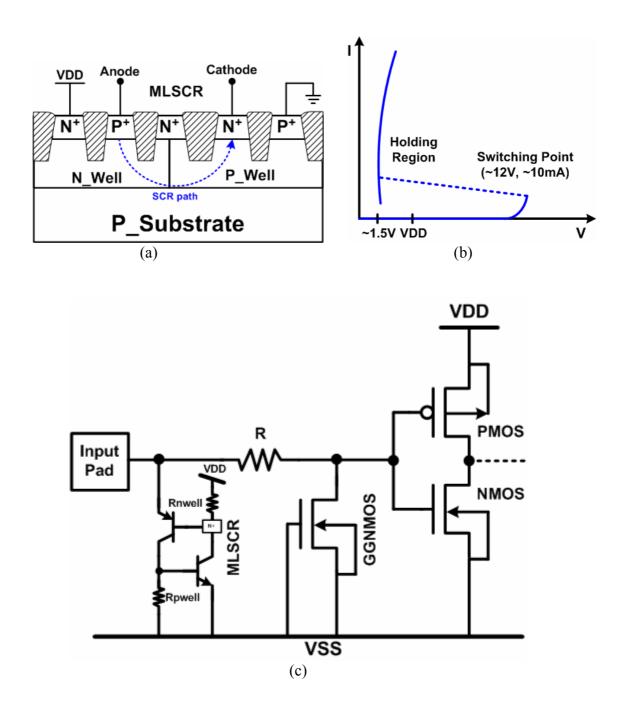

- **Fig. 1.4** (a) The device structure of the modified LSCR (MLSCR) in CMOS process. (b) The I-V characteristics of the MLSCR in a 0.25-μm CMOS process. (c) The input ESD protection circuit with the MLSCR device.

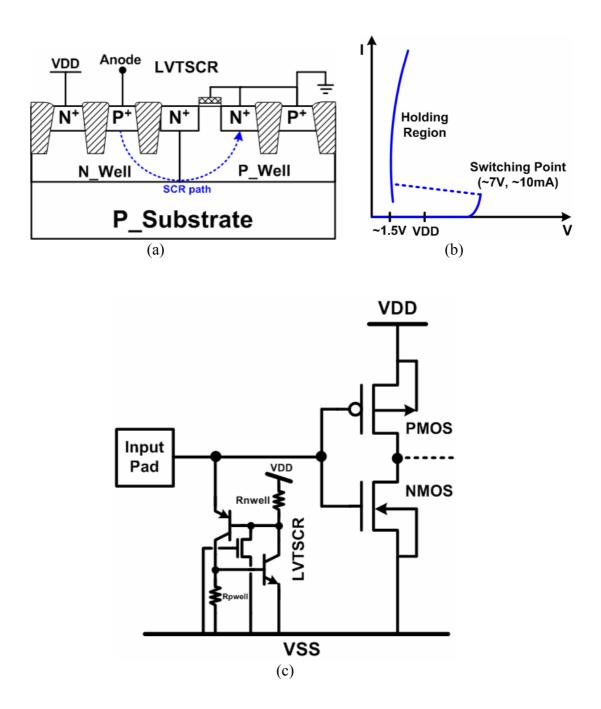

- Fig. 1.5 (a) The device structure of the low-voltage triggering SCR (LVTSCR) in CMOS process. (b) The I-V characteristics of the LVTSCR in a 0.25-μm CMOS process.(c) The example of input ESD protection circuit with the LVTSCR device.

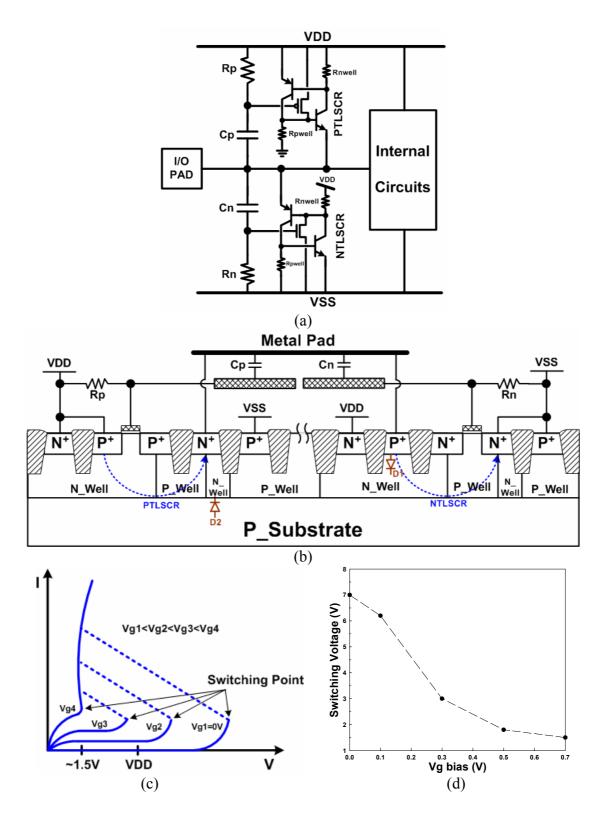

- **Fig. 1.6** (a) The ESD protection circuit with the gate-coupled NTLSCR and PTLSCR devices. (b) The device structure of the gate-coupled NTLSCR / PTLSCR devices in CMOS process. (c) The I-V characteristics of the gate-coupled NTLSCR device in a 0.25-μm CMOS process. (d) The dependence of switching voltage of SCR device on the gate bias voltage of the NTLSCR device.

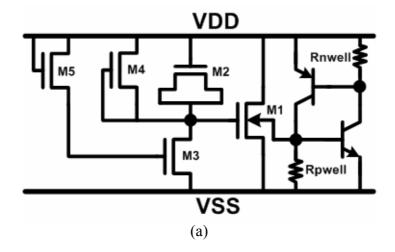

- **Fig. 1.7** (a) The power-rail ESD clamp circuit with the hot-carrier triggered SCR (HCTSCR) device. (b) The device structures of primary protection devices including SCR and NMOS M1.

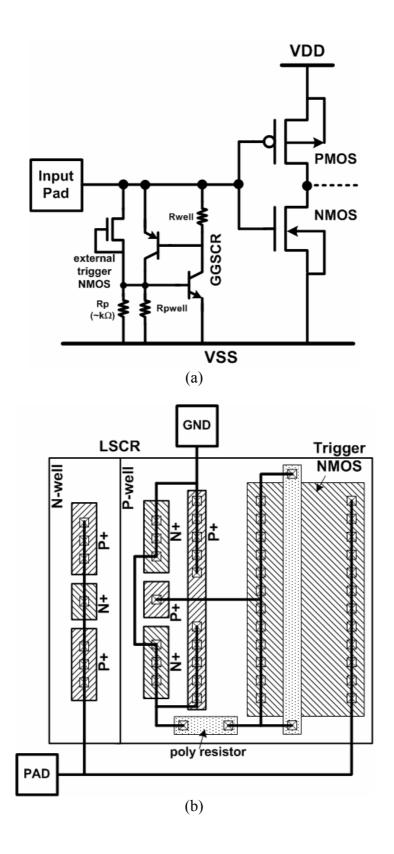

- **Fig. 1.8** (a) The input ESD protection circuit with the grounded-gate NMOS triggered SCR (GGSCR) device. (b) The layout top view of the GGSCR in a CMOS process.

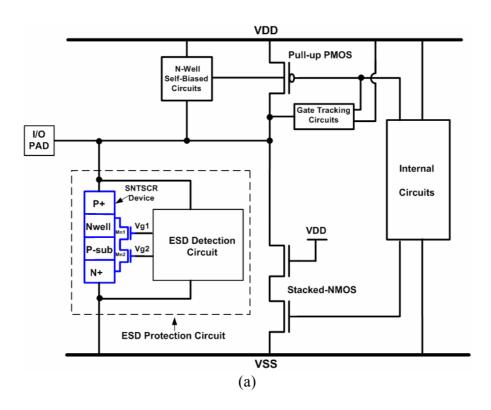

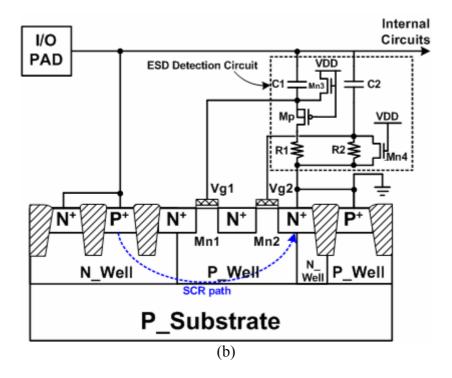

- **Fig. 1.9** (a) The ESD protection circuit with stacked-NMOS triggered SCR (SNTSCR) device for mixed-voltage I/O interface. (b) The ESD detection circuit and the device structure of the SNTSCR.

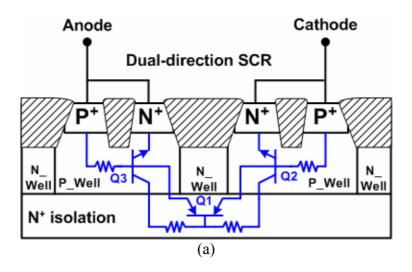

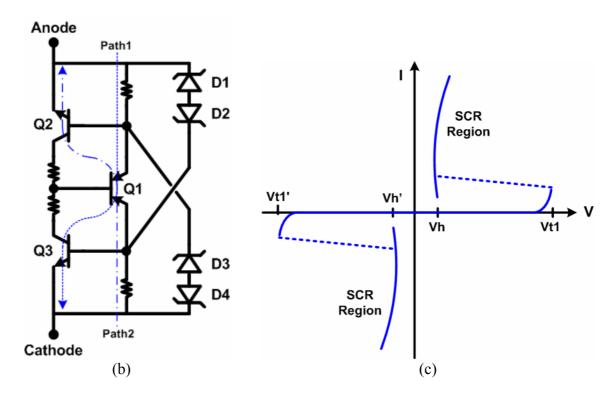

- **Fig. 1.10** (a) The device structure of the dual-direction SCR. (b) The circuit schematic of the low-trigger-voltage ESD protection circuit consists of a core dual-direction

- SCR and two back-to-back Zener diodes. (c) The I-V characteristics of the dual-direction SCR device.

- **Fig. 1.11** Two solutions to overcome latchup issue in the ESD protection design with SCR-based device. (a) Increasing the trigger current and (b) increasing holding voltage to avoid the SCR-based devices being accidentally triggered on by noise pulse.

- **Fig. 1.12** (a) The device structure of dynamic holding voltage SCR (DHVSCR) in CMOS process. (b) The I-V characteristics of the DHVSCR under normal circuit operating conditions and ESD-zapping conditions in a 0.25-μm CMOS process.

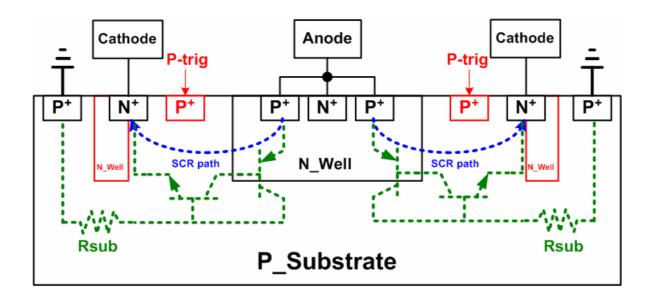

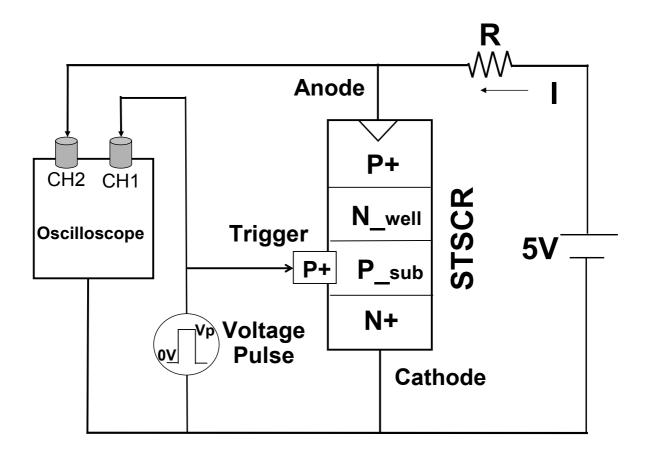

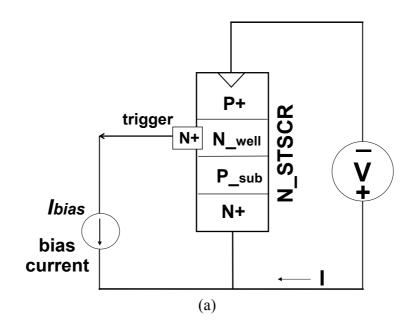

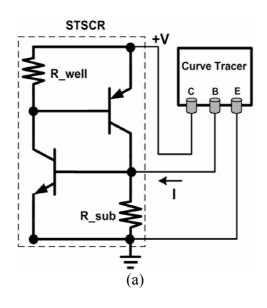

- Fig. 2.1 Device structure of the proposed substrate-triggered SCR (STSCR) device.

- Fig. 2.2 (a) The experimental measurement setup used to measure the I-V curves of the STSCR device. The measured I-V curves of the STSCR device under (b) different substrate-triggered currents and (c) different substrate bias voltages. (d) The dependence of the switching voltage of the STSCR on the substrate-triggered current and substrate bias voltage in the STSCR device.

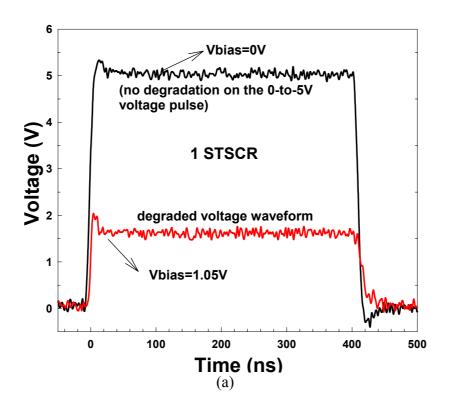

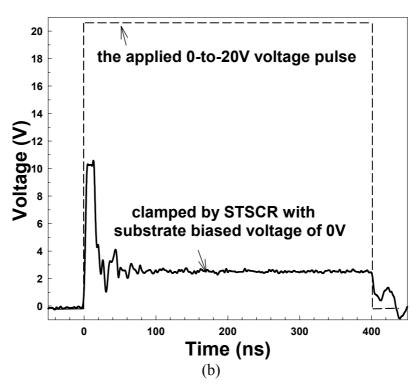

- **Fig. 2.3** (a) Under substrate bias of 0V and 1.05V, the measured voltage waveforms on the anode of STSCR device when a 0-to-5V voltage pulse is applied to the anode of the STSCR with the cathode grounded. (b) The measured voltage waveform on the anode, clamped by the stand-alone STSCR device when a 0-to-20V voltage pulse is applied to the anode with the cathode grounded.

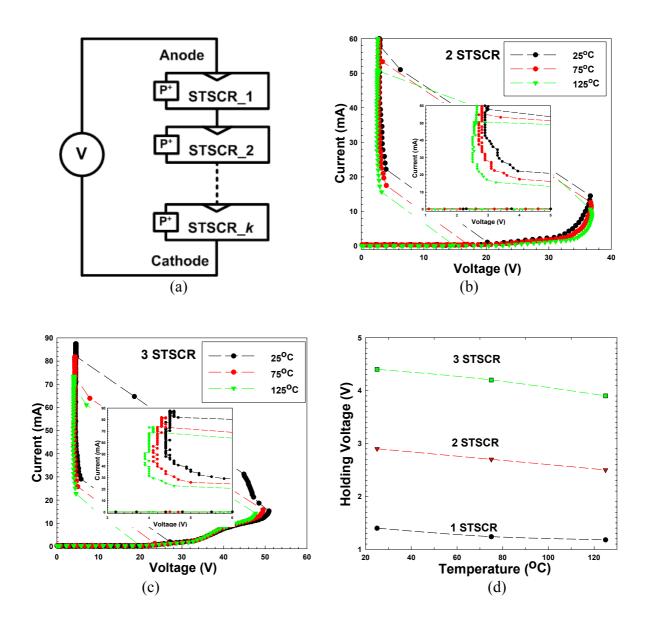

- Fig. 2.4 The temperature dependence on the total holding voltage of the stacked STSCR devices with different stacked number. (a) Experimental measurement setup, (b) the measured I-V curves of two STSCR devices in stacked configuration (2STSCR), (c) the measured I-V curves of three STSCR devices in stacked configuration (3STSCR), and (d) the relation between the holding voltage and operating temperature under different number of stacked STSCR devices.

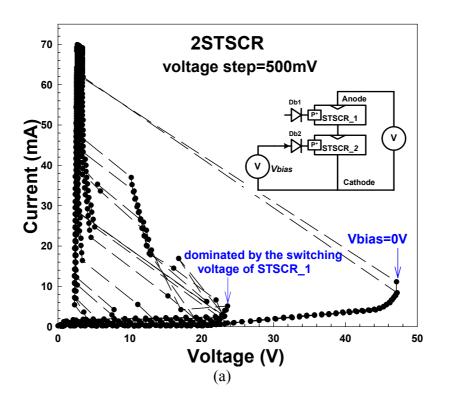

- **Fig. 2.5** The measured I-V curves of the two STSCR devices in stacked configuration (2STSCR) when the substrate bias voltages are applied to (a) only one trigger node, and (b) all trigger nodes.

- Fig. 2.6 The ESD protection circuits for (a) the input pad, and (b) the output pad, by using

- the proposed STSCR devices in stacked configuration.

- Fig. 2.7 The VDD-to-VSS ESD clamp circuit realized with the stacked STSCR devices.

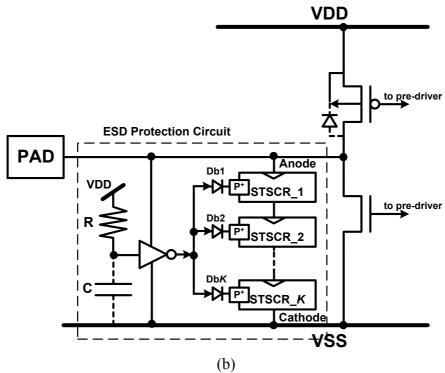

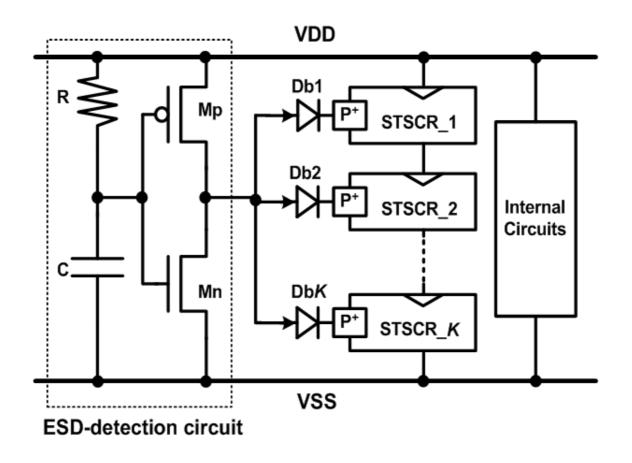

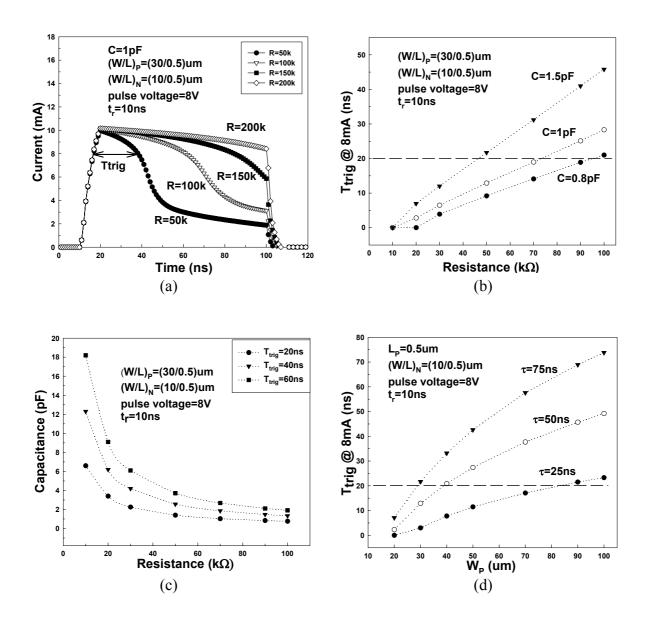

- Fig. 2.8 HSPICE simulation. (a) The dependence of output current of ESD-detection circuit on time under different resistances. (b) The dependence of "Ttrig" on resistance under different capacitances. (c) The dependence of capacitance on resistance under different "Ttrigs". (d) The dependence of "Ttrig" on channel width of PMOS under different time constants.

- **Fig. 2.9** The layout views of (a) one substrate-triggered SCR (STSCR), and (b) two STSCR devices in stacked configuration (2STSCR) with blocking diodes.

- Fig. 2.10 Dependence of the HBM ESD levels of stacked STSCR configuration on the number of the stacked STSCR devices (Failure criterion:  $I_{Leakage} > 1 \mu A$  @ 2.5V bias).

- Fig. 2.11 Dependence of the MM ESD levels of stacked STSCR configuration on the number of the stacked STSCR devices (Failure criterion:  $I_{Leakage} > 1 \mu A$  @ 2.5V bias).

- **Fig. 2.12** The TLP-measured I-V curves of the stacked STSCR configuration without substrate bias under different numbers of the stacked STSCR devices.

- **Fig. 2.13** The TLP-measured I-V curves of the four STSCR devices in stacked configuration (4STSCR) with different substrate bias voltages.

- **Fig. 2.14** Experimental setup to measure the turn-on time of one stand-alone STSCR device.

- **Fig. 2.15** The turn-on verification of STSCR device under different substrate biases. The measured voltage waveforms on the anode and trigger nodes of the STSCR device under (a) 1-V voltage triggering, and (b) 2-V voltage triggering. The close-up views of the V\_anode at the falling edge while the STSCR is triggering by the voltage pulse of (c) 1.5V, (d) 2V, and (e) 4V into the P+ trigger node. (f) The relation between the turn-on time and the triggering pulse voltage.

- **Fig. 2.16** The measured voltage waveforms on the VDD line, clamped by different stacked STSCR devices with ESD-detection circuit, when a 0-to-8V voltage pulse is applied to the VDD line of the VDD-to-VSS ESD clamp circuit with the VSS grounded.

- Fig. 2.17 The verification of ESD-detection function in the VDD-to-VSS ESD clamp circuit

with one STSCR under the triggering of 0-to-5V voltage pulse with different rise time.

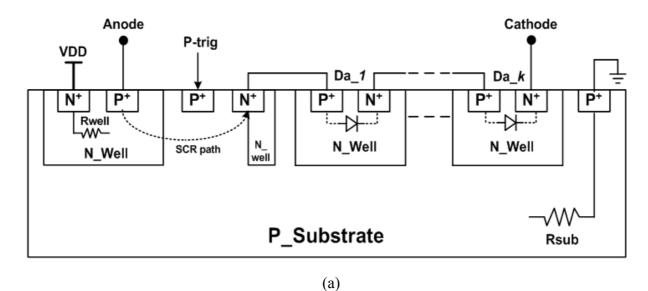

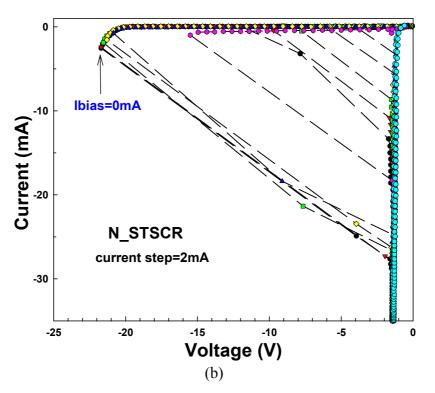

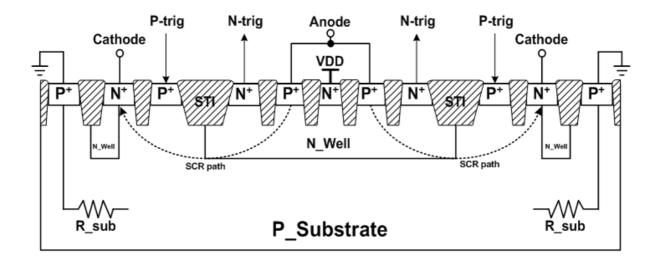

- **Fig. 3.1** Device structures of (a) the p-type substrate-triggered SCR device (P\_STSCR), and (b) the n-type substrate-triggered SCR device (N\_STSCR), with stacked diode string.

- **Fig. 3.2** (a) The experimental measurement setup to measure the I-V curves of the P\_STSCR device, and (b) the measured I-V curves of the P\_STSCR device under different substrate-triggered currents.

- **Fig. 3.3** (a) The experimental measurement setup to measure the I-V curves of the N\_STSCR device, and (b) the measured I-V curves of the N\_STSCR device under different well-triggered currents.

- **Fig. 3.4** Dependence of the switching voltage of (a) the P\_STSCR, and (b) the N\_STSCR, on the triggered current in P-substrate or in N-well.

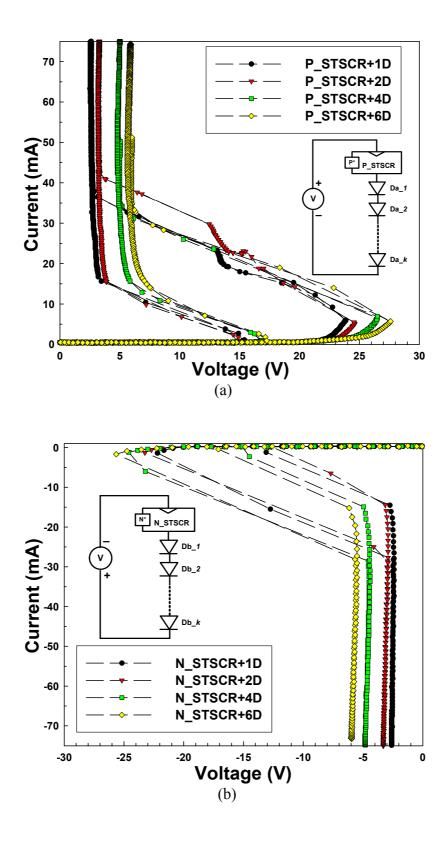

- **Fig. 3.5** The measured I-V curves of (a) the P\_STSCR, and (b) the N\_STSCR, with different numbers of stacked diodes under the temperature of 25°C.

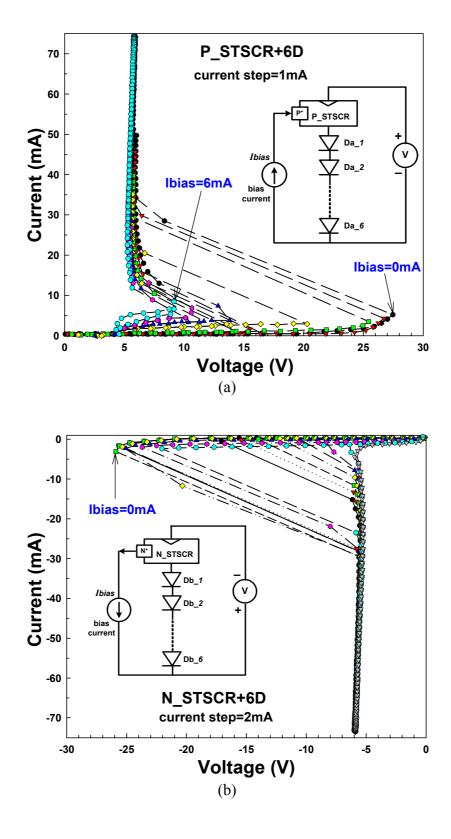

- **Fig. 3.6** The measured turn-on I-V curves of (a) the P\_STSCR, and (b) the N\_STSCR, with six stacked diodes under different triggered currents.

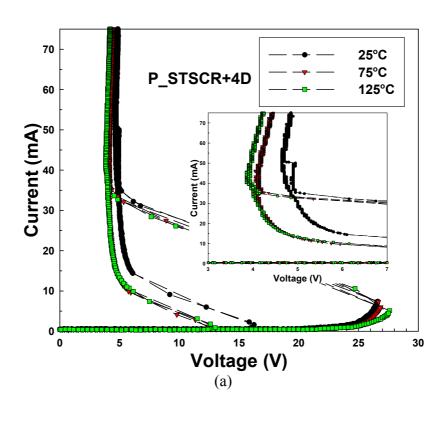

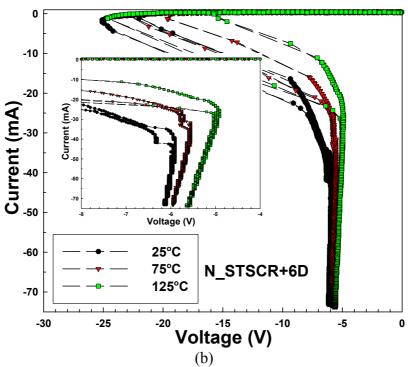

- **Fig. 3.7** The measured I-V curves of (a) the P\_STSCR with four stacked diodes, and (b) the N\_STSCR with six stacked diodes, under different temperatures.

- **Fig. 3.8** Dependence of the total holding voltage of (a) the P\_STSCR with stacked diode string, and (b) the N\_STSCR with stacked diode string, on the number of stacked diodes under different temperatures.

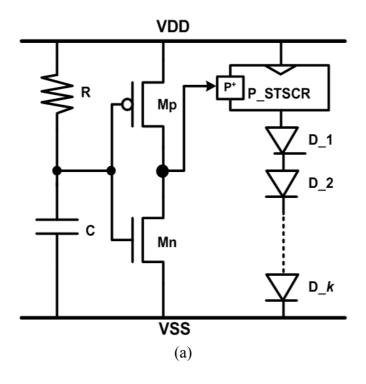

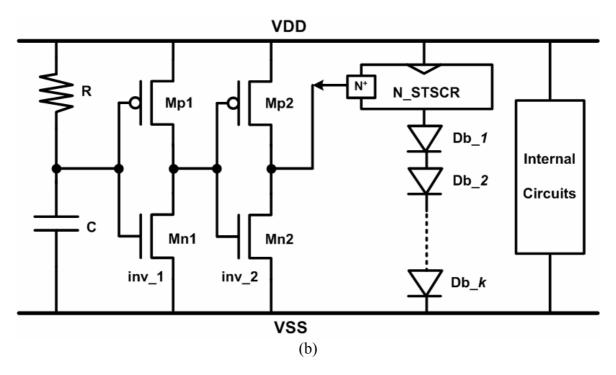

- **Fig. 3.9** Design of ESD protection circuits for the input or output pads with the proposed complementary-STSCR devices and stacked diode string by using (a) RC delay, and (b) gate coupled, circuit techniques.

- **Fig. 3.10** The equivalent circuit of the complementary-STSCR devices with stacked diode string for the input and output pads.

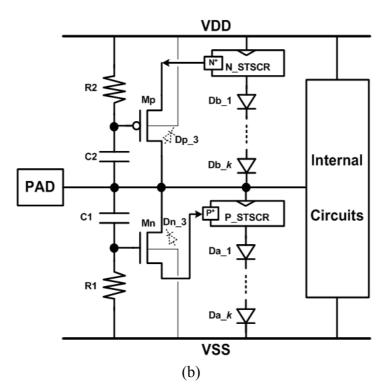

- **Fig. 3.11** The VDD-to-VSS ESD clamp circuits realized with (a) the P\_STSCR, and (b) the N\_STSCR, with stacked diode sting.

- Fig. 3.12 The layout top views of (a) the P STSCR with two stacked diodes, and (b) the

- N\_STSCR with three stacked diodes, in a 0.25-µm salicided CMOS process.

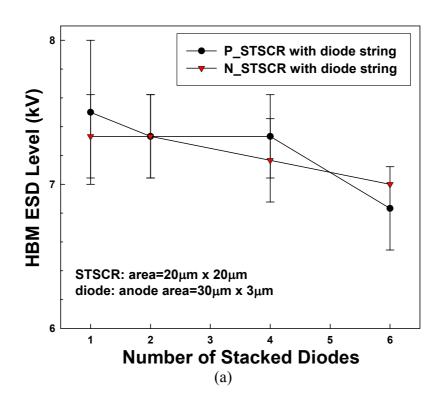

- Fig. 3.13 Dependence of the (a) HBM, and (b) MM, ESD levels of the complementary STSCR devices with stacked diode sting on the number of the stacked diodes (Failure criterion:  $I_{Leakage} > 1 \mu A @ 2.5 V bias$ ).

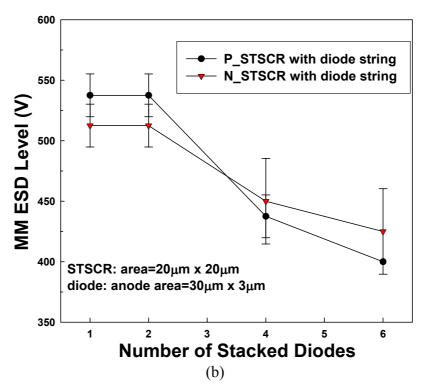

- **Fig. 3.14** The comparison of turn-on time between LVTSCR and P\_STSCR with 1.5-V substrate bias under an applied 0-to-8 V voltage pulse.

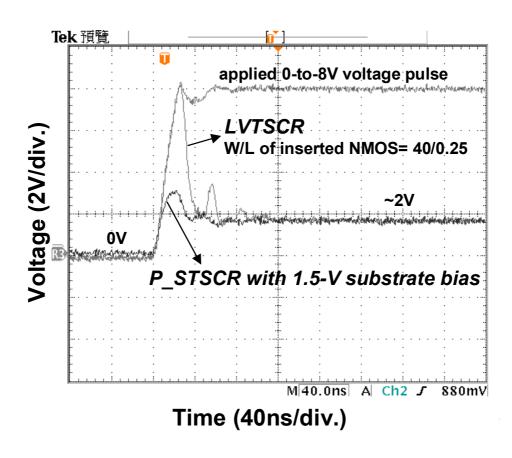

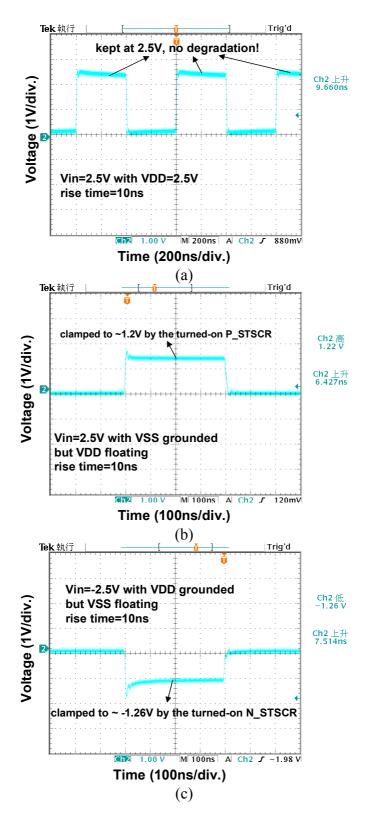

- **Fig. 3.15** The measured voltage waveforms on the I/O pad of Fig. 3.9(a) under (a) the normal circuit operating conditions, (b) the positive-to-VSS ESD zapping condition, when a 2.5-V voltage pulse is applied to the I/O pad, and (c) the negative-to-VDD ESD zapping condition when a -2.5-V voltage pulse is applied to the I/O pad.

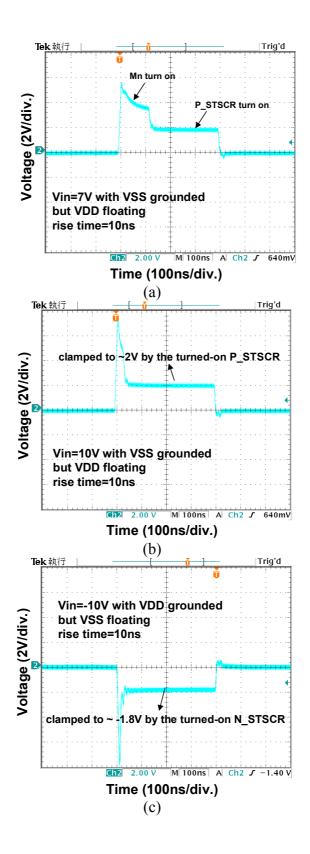

- **Fig. 3.16** The measured voltage waveforms on the I/O pad of Fig. 3.9(b) under (a) the 7-V positive-to-VSS ESD zapping condition, (b) the 10-V positive-to-VSS ESD zapping condition, and (c) the -10V negative-to-VDD ESD zapping condition.

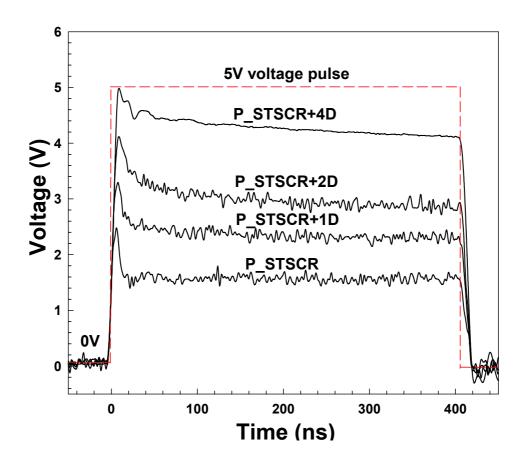

- **Fig. 3.17** The voltage waveforms clamped by the VDD-to-VSS ESD clamp circuit designed with the P\_STSCR device and different numbers of stacked diodes, when a 0-to-5 V voltage pulse is applied.

- **Fig. 4.1** Device structure of the double-trigger SCR (DTSCR) device.

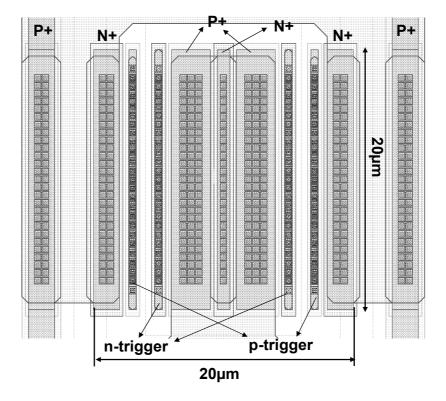

- **Fig. 4.2** The layout top view of the DTSCR device.

- **Fig. 4.3** (a) The measurement setup and measured DC I-V curves of DTSCR under different substrate-triggered currents but no N-well triggered current. (b) The measured DC I-V curves of DTSCR under different substrate-triggered currents and the additional N-well triggered current of -2 mA. (c) The dependence of switching voltage of DTSCR on substrate-triggered current under different N-well triggered currents.

- **Fig. 4.4** (a) The measurement setup and measured DC I-V curves of DTSCR under different n-trigger currents and the substrate-triggered current of 2 mA. (b) The dependence of switching voltage of DTSCR on the N-well triggered current under different substrate-triggered currents.

- Fig. 4.5 The temperature dependence on the total holding voltage of the stacked DTSCR

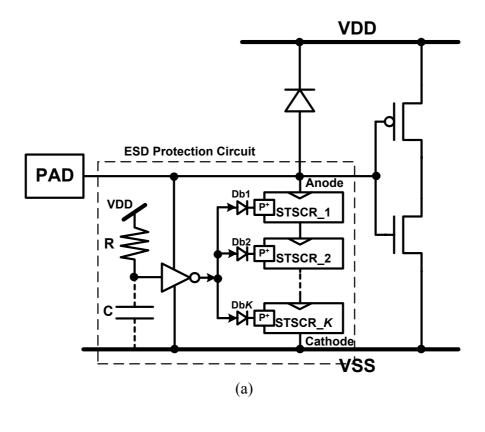

- devices with different stacked numbers. (a) Experimental measurement setup, (b) the measured I-V curves of two DTSCR devices in stacked configuration (2DTSCR), (c) the measured I-V curves of three DTSCR devices in stacked configuration (3DTSCR), and (d) the relation between the holding voltage and the temperature under different numbers of stacked DTSCR devices.

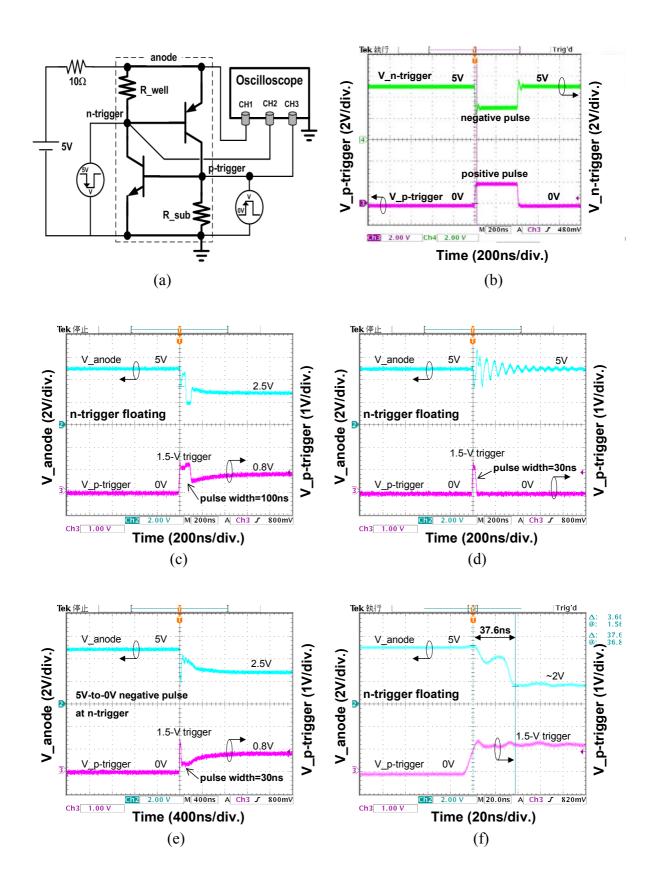

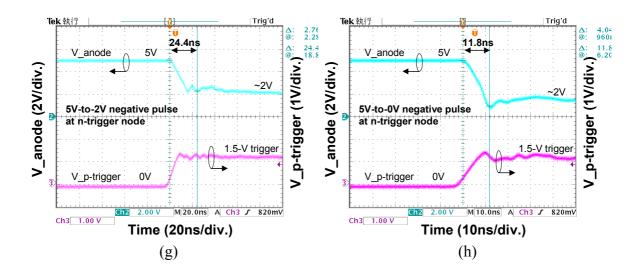

- **Fig. 4.6** The turn-on verification of DTSCR under different voltage pulses. (a) The measurement setup. (b) Synchronous positive and negative voltage pulses. The measured voltage waveforms on the anode and p-trigger nodes of the DTSCR device under 1.5-V positive voltage pulse with pulse width of (c) 100 ns, (d) 30 ns, while n-trigger is floating, and (e) 30 ns while 5-to-0 V negative voltage pulse is applied to n-trigger. The close-up views of the V\_anode at the falling edge while the DTSCR is synchronously triggering by the 1.5-V positive voltage pulse and under the negative voltage pulse of (f) floating, (g) 5-to-2 V, and (h) 5-to-0 V.

- **Fig. 4.7** The dependence of turn-on time of DTSCR on the N-well biases under different substrate bias conditions with a fixed rise time of 10 ns.

- **Fig. 4.8** The dependence of turn-on time of DTSCR on the rise time of voltage pulse under different substrate bias conditions.

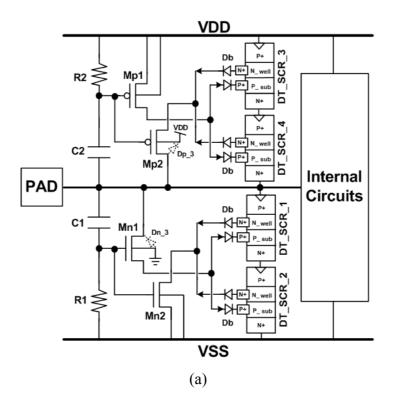

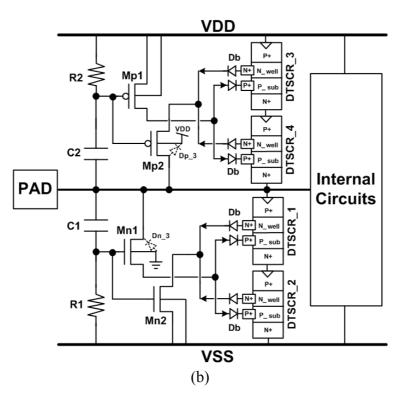

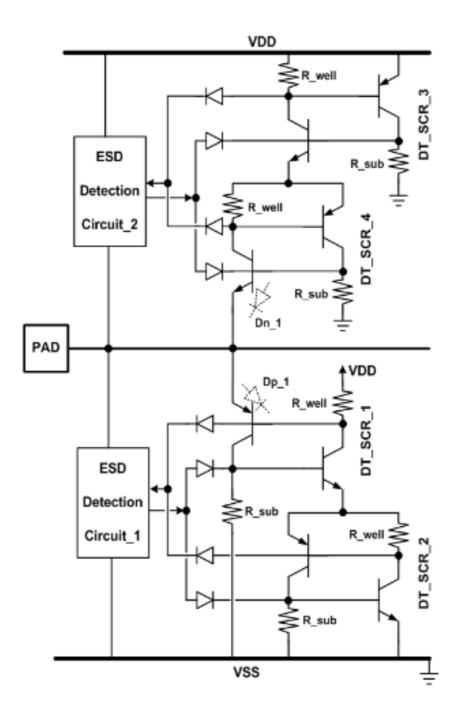

- **Fig. 4.9** Design of ESD protection circuits for the input or output pad with the proposed DTSCR devices by using (a) RC delay, and (b) gate coupled, circuit techniques.

- Fig. 4.10 The equivalent circuit of the stacked DTSCR devices for the input or output pad.

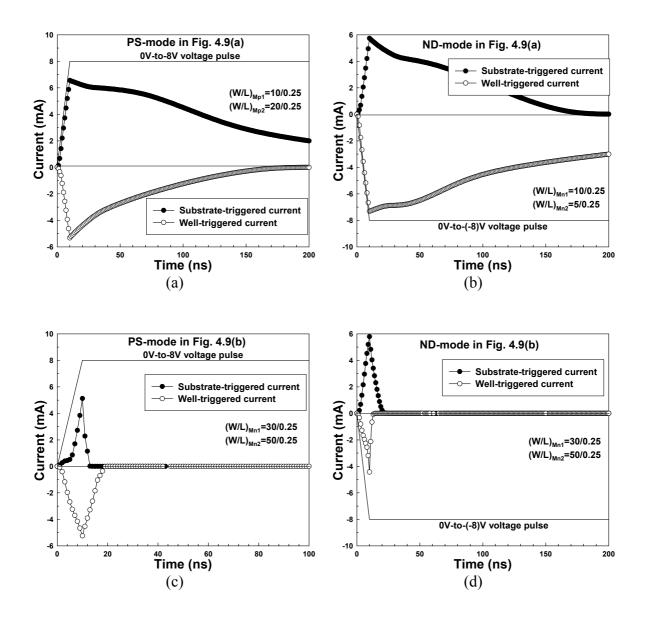

- **Fig. 4.11** HSPICE simulation. The transient simulation on the ESD-detection circuit in Fig. 4.9(a) under (a) PS-mode, and (b) ND-mode, ESD-zapping conditions and in Fig. 4.9(b) under (c) PS-mode, and (d) ND-mode, ESD-zapping conditions.

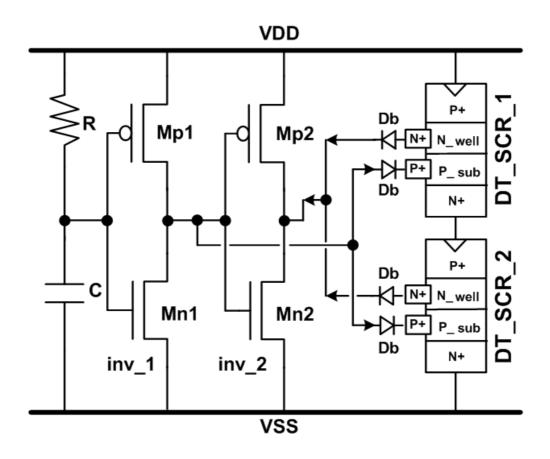

- **Fig. 4.12** The power-rail ESD clamp circuit designed with two stacked DTSCR devices and ESD-detection circuit.

- Fig. 4.13 Dependence of the HBM ESD levels of stacked DTSCR configuration on the number of the stacked DTSCR devices (Failure criterion:  $I_{Leakage} > 1 \mu A$  @ 2.5 V bias).

- Fig. 4.14 Dependence of the MM ESD levels of stacked DTSCR configuration on the number of the stacked DTSCR devices (Failure criterion:  $I_{Leakage} > 1 \mu A$  @ 2.5 V bias).

- Fig. 4.15 The TLP-measured I-V curves of the two stacked DTSCR devices with or without

- ESD-detection circuit (Failure criterion:  $I_{Leakage} > 1 \mu A @ 2.5 \text{ V bias}$ ).

- **Fig. 4.16** The measured voltage waveforms to verify the turn-on efficiency of the power-rail ESD clamp circuit with two stacked DTSCR devices.

- **Fig. 5.1** Device structures of (a) the substrate-triggered SCR (STSCR) device with shallow trench isolation (STI), (b) the STSCR device with extra silicide-blocking mask, and (c) the proposed STSCR device with dummy-gate structure.

- **Fig. 5.2** (a) The measurement setup to find the DC I-V curves of STSCR devices. The DC I-V curves of STSCR with (b) STI, and (c) dummy-gate, structures under different substrate-triggered currents.

- **Fig. 5.3** The dependences of the switching voltages of STSCR devices with STI or dummy-gate structure on the substrate-triggered current.

- **Fig. 5.4** The comparison of turn-on speed between the LVTSCR and the dummy-gate blocking STSCR with 0.9-V substrate bias under an applied 0-to-8 V voltage pulse.

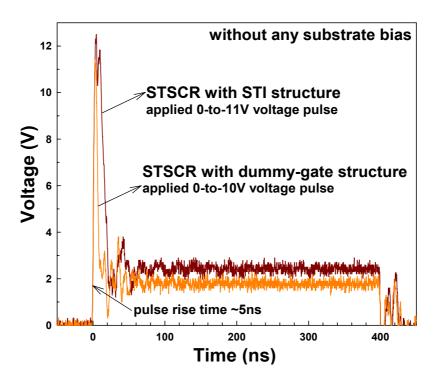

- **Fig. 5.5** The comparison of turn-on speed between the STSCR with STI and dummy-gate structures without any substrate bias applied at p-trigger node.

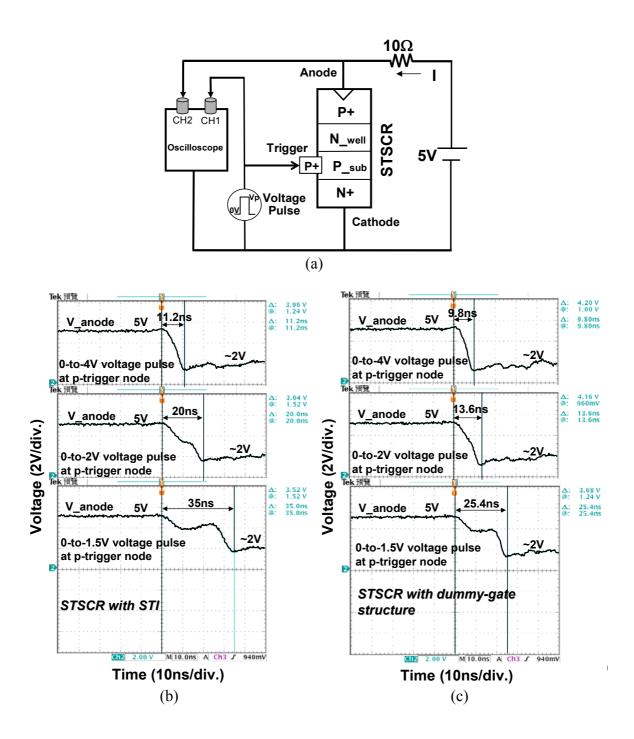

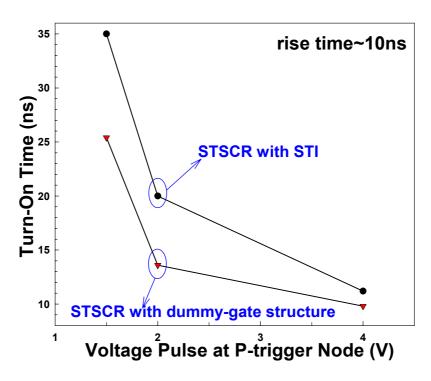

- **Fig. 5.6** Measurement on the turn-on time of STSCR with STI and dummy-gate structures under different voltage pulses. (a) The measurement setup. The measured voltage waveforms on the anode of the STSCR with (b) STI, and (c) dummy-gate structure, while the STSCR is triggering by the voltage pulse of 1.5V, 2V, and 4V into the trigger node.

- **Fig. 5.7** The comparison on the turn-on time between STSCR with STI and dummy-gate structures under different voltage pulses with 10-ns rise time applied at the p-trigger node.

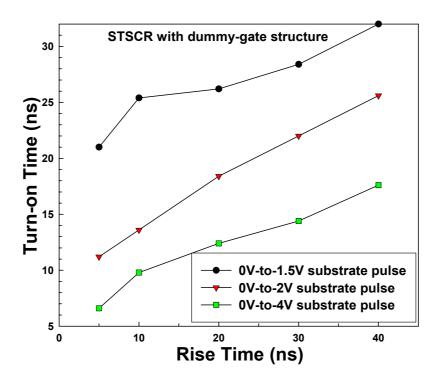

- **Fig. 5.8** The dependence of the turn-on time of STSCR with dummy-gate structure on the rise time of voltage pulse under different substrate bias conditions.

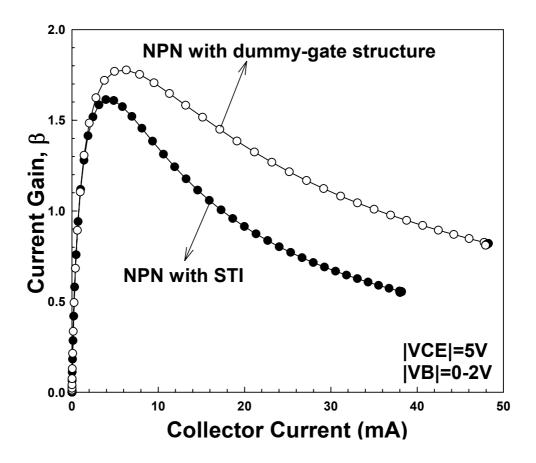

- **Fig. 5.9** The dependence of current gains of the NPN bipolar transistors in the STSCR devices with STI or dummy-gate structures on its collector current.

- **Fig. 5.10** The TLP-measured I-V curves of the STSCR with STI and dummy-gate structures.

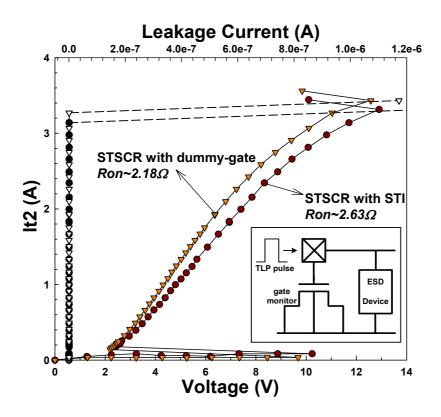

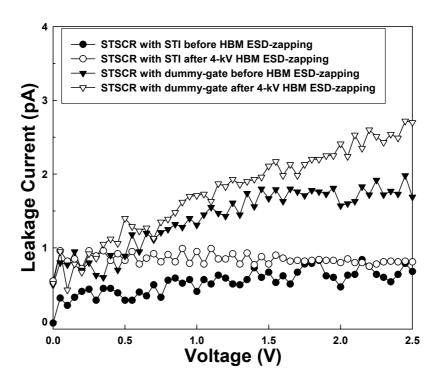

**Fig. 5.11** The comparison of leakage current between the STSCR with STI and dummy-gate structures before and after 4-kV HBM ESD zapping.

- **Fig. 6.1** The device cross-sectional views of the NMOS, PMOS, and native NMOS in a P-substrate twin-well CMOS technology.

- **Fig. 6.2** The circuit schematics of (a) the proposed native-NMOS-triggered SCR (NANSCR) and (b) the traditional LVTSCR.

- **Fig. 6.3** (a) The DC I-V curves and (b) the leakage currents of the NANSCR and LVTSCR.

- **Fig. 6.4** Design of ESD protection circuit for the input or output pads with the proposed NANSCR devices.

- **Fig. 6.5** The VDD-to-VSS ESD clamp circuit realized with the NANSCR device.

- **Fig. 6.6** The new whole-chip ESD protection scheme realized with the NANSCR devices.

- **Fig. 6.7** The measured voltage waveform of input signal on the pad with the NANSCR device under normal circuit operating conditions, when a 1.2-V voltage signal is applied to the pad.

- **Fig. 6.8** Experimental setup to measure the turn-on speed or EMMI photograph of turn-on behavior among ESD devices.

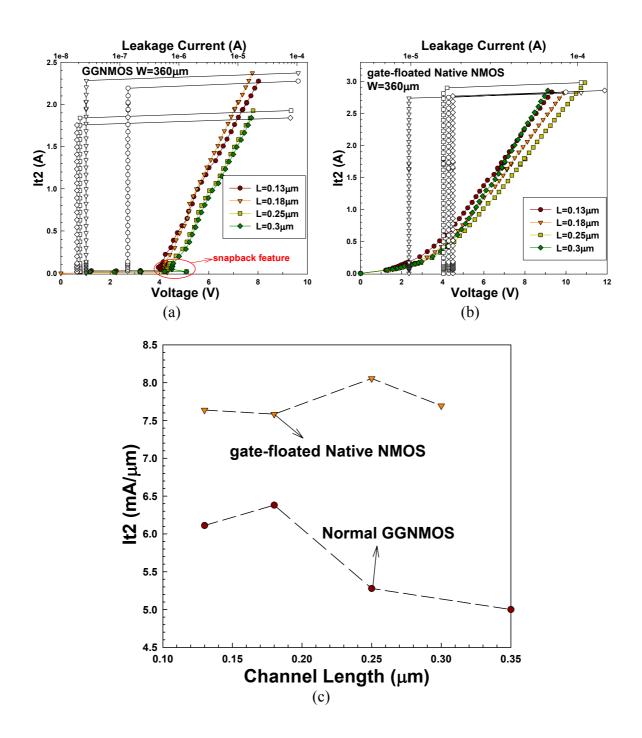

- **Fig. 6.9** The comparison of turn-on speeds between the GGNMOS and the gate-floated native NMOS under different channel lengths.

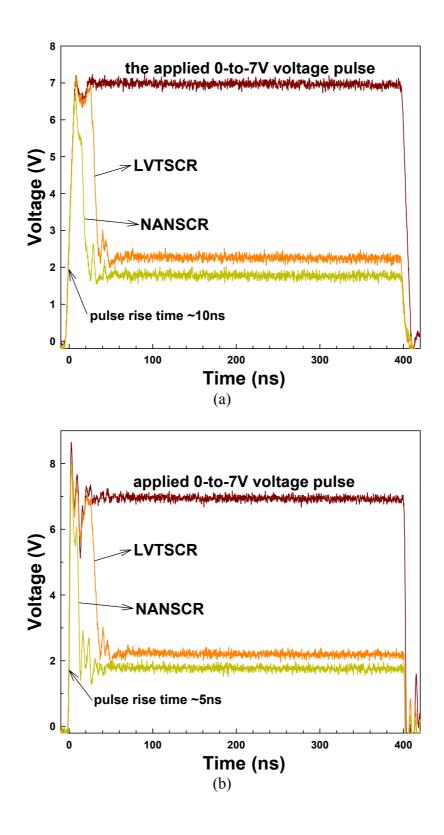

- **Fig. 6.10** The comparison of turn-on speeds between NANSCR and LVTSCR under 0-to-7 V voltage pulse with (a) 10-ns rise time and (b) 5-ns rise time.

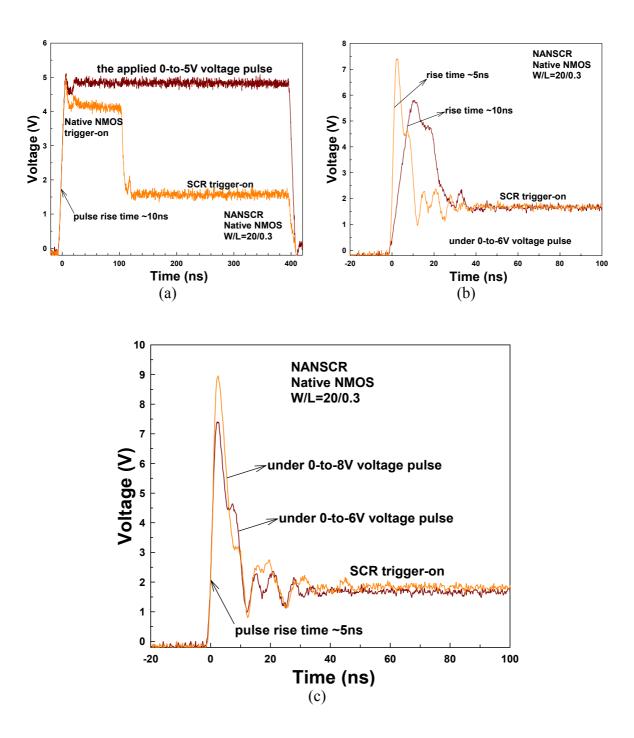

- **Fig. 6.11** (a) The turn-on waveform of NANSCR under 5-V voltage pulse with rise time of 10 ns. The comparison of turn-on speeds of NANSCR (b) under 6-V voltage pulse with different rise times and (c) under different pulse voltages with the same rise time of 5 ns.

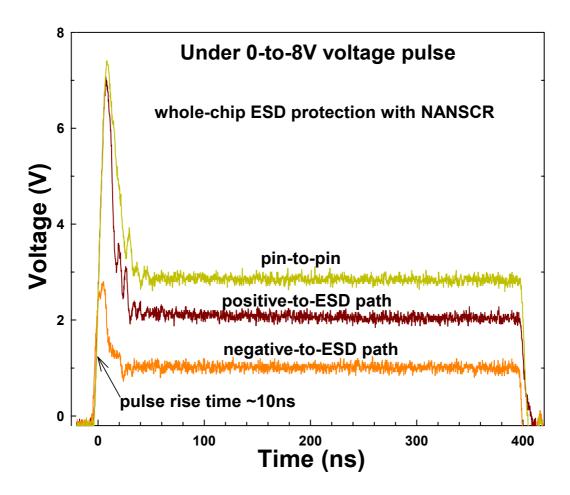

- **Fig. 6.12** The clamped voltage waveforms of the whole-chip ESD protection scheme with NANSCR under positive-to-ESD path, negative-to-ESD path, and pin-to-pin ESD-zapping conditions.

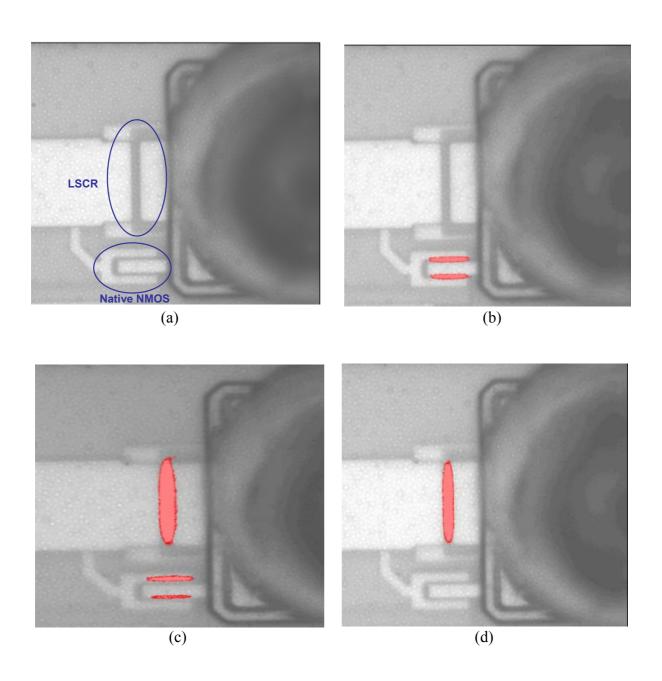

- **Fig. 6.13** The measured EMMI photographs on the turn-on behavior of NANSCR device under the pulsed voltage stresses of (a) 0 V, (b) 5 V, (c) 5.8 V, and (d) 6 V.

- **Fig. 6.14** The TLP-measured I-V curves of (a) the normal GGNMOS and (b) the gate-floated native NMOS under channel width of 360 μm and different channel lengths. (c) The comparison of It2 per micron between the normal GGNMOS and the gate-floated native NMOS under different channel lengths.

- **Fig. 6.15** The TLP-measured I-V curves of NANSCR and LVTSCR under the conditions with or without the gate monitor device.

#### **CHAPTER 1**

#### **INTRODUCTION**

#### 1.1 BACKGROUND

Electrostatic discharge (ESD) phenomenon originates from the transfer of electrostatic charges between two objects with different electrical potentials, which results in damage to integrated circuits (ICs) due to large energy dissipation in an extremely short time less than 150 ns. ESD failure will become more and more serious reliability concern in nanoscale CMOS IC products. Common ESD failures are catastrophic, leading to immediate malfunction of IC chips caused by either thermal breakdown in silicon and/or metal interconnects due to high-current transient, or dielectric breakdown in gate oxide due to high-voltage overstress [1]. The ESD specifications of commercial IC products are generally required to be higher than 2 kV in human-body-model (HBM) [2] ESD stress and 200 V in machine-model (MM) [3] ESD stress. Therefore, in order to provide efficient ESD protection for CMOS ICs against unexpected ESD damages in the internal circuits of CMOS ICs [4]-[11], the on-chip ESD protection circuits have to be designed and placed around the input, output, and power pads to clamp the overstress voltage across the internal circuits, and to provide a low impendence path to discharge the ESD current of several Ampere to ground. The locations of the ESD protection circuits to achieve whole-chip ESD protection for CMOS ICs are illustrated in Fig. 1.1.

Due to the low holding voltage (Vh, about  $\sim$ 1.5 V in general CMOS processes) of silicon controlled rectifier (SCR) device [12], [13], the power dissipation (power  $\cong$  I<sub>ESD</sub>×Vh) located on the SCR device during ESD stress is significantly less than that located on other ESD protection devices, such as the diode, MOS, BJT, or field-oxide device. The SCR device can sustain a much higher ESD level within a smaller layout area in CMOS ICs, so it had been used to protect the internal circuits against ESD damage for a long time. But, the SCR device still has a higher switching voltage (i.e., trigger voltage,  $\sim$ 22 V) in the sub-quarter-micron CMOS technology, which is generally greater than the gate-oxide

breakdown voltage of the input stages. Furthermore, the gate oxide thickness, its time-to-breakdown (t<sub>BD</sub>), or charge-to-breakdown (Q<sub>BD</sub>) will also be decreased with the shrinkage of CMOS technologies. So, it is imperative to reduce the switching voltage of SCR and to enhance the turn-on speed of SCR for efficiently protecting the ultra-thin gate oxide from latent damage or rupture [14], especially against the fast charged-device-model (CDM) [15] ESD events. Therefore, to provide more effective on-chip ESD protection, the modified lateral SCR (MLSCR) [16] and the low-voltage triggering SCR (LVTSCR) [17], [18] had been invented to reduce the switching voltage of SCR device. Moreover, some advanced trigger-assist circuit techniques had been also reported to reduce the switching voltage and to enhance the turn-on speed of SCR device, such as the gate-coupled technique [19], the hot-carrier triggered technique [20], the GGNMOS-triggered technique [21], [22], the substrate-triggered technique [23]-[26], double-triggered technique [27],native-NMOS-trigger technique [28], etc. For mixed-voltage I/O buffer, the stacked-NMOS triggered SCR was invented to improved the ESD level of stacked NMOS [29], [30].

The review of SCR-based devices for on-chip ESD protection is investigated and compared in this chapter [31]. In addition, the solutions to avoid the transient-induced latchup issue [32] of SCR-based devices in CMOS IC products with maximum voltage supply greater than 1.5 V are also discussed. However, such latchup issue will vanish certainly when the maximum voltage supply of IC products is smaller than the holding voltage of SCR devices. For example, a single SCR with holding voltage of  $\sim 1.6$  V can be safely used as ESD protection without latchup danger in a 0.13- $\mu$ m CMOS process with maximum voltage supply of 1.2 V.

#### 1.2 TURN-ON MECHANISM OF SCR DEVICE

The equivalent circuit schematic of a SCR device is shown in Fig. 1.2(a). SCR device consists of a lateral NPN and a vertical PNP bipolar transistors and forms a 2-terminal and 4-layer PNPN (P+/N-well/P-well/N+) structure, which is inherent in the CMOS processes. The switching voltage of the SCR device is dominated by the avalanche breakdown voltage of N-well/P-well junction, which is about ~22 V in a 0.25-µm CMOS process, or ~18 V in a 0.13-µm CMOS process. When a positive voltage applied on the anode of SCR is greater

than the breakdown voltage and its cathode is relatively grounded, for example, the hole and electron current will be generated through the avalanche breakdown mechanism [33], [34]. The hole current will flow through the P-well to P+ diffusion connected to ground, whereas the electron current will flow through the N-well to N+ diffusion connected to the anode of SCR. As long as the voltage drop across the P-well resistor (Rpwell) (N-well resistor (Rnwell)) is greater than 0.7 V, the NPN (PNP) transistor will be turned on to inject the electron (hole) current to further bias the PNP (NPN) transistor and initiates the SCR latching action. Finally, the SCR will be successfully triggered on into its latching state to discharge ESD current through the positive-feedback regenerative mechanism [35], [36].

The DC I-V characteristic of SCR device is shown in Fig. 1.2(b). Once the SCR is triggered on, the required holding current to keep the NPN and PNP transistors on can be generated through the positive-feedback regenerative mechanism of latchup without involving the avalanche breakdown mechanism. So, the holding voltage (Vh) of SCR can be reduced to a lower voltage level of ~1.5 V, typically. When a negative voltage is applied on the anode terminal of SCR, the parasitic diode (N-well/P-well junction) inherent in SCR structure will be forward biased to clamp the negative voltage at a lower voltage level of ~-1 V (cut-in voltage of a diode). Whatever the ESD energy is positive or negative, the SCR device can clamp ESD overstresses to a lower voltage level, so the SCR device can sustain the highest ESD robustness within a smaller layout area in CMOS ICs.

#### 1.3 SCR-BASED DEVICES FOR CMOS ON-CHIP ESD PROTECTION

#### 1.3.1 Lateral SCR (LSCR) [12], [13]

The lateral SCR (LSCR) device was used as an effective input ESD protection element in CMOS ICs. The device structure of the LSCR is illustrated in Fig. 1.3(a), and the corresponding I-V characteristic of the LSCR in a 0.25-μm CMOS process is shown in Fig. 1.3(b). The example of the LSCR device in the input ESD protection circuit is shown in Fig. 1.3(c). In some applications, the N-well of LSCR is connected to the input pad, but not to VDD, to eliminate the forward-bias diode from the pad to VDD. The LSCR has the higher switching voltage (~22 V) in a 0.25-μm CMOS process, which is generally greater than the

gate-oxide breakdown voltage of the input stages. Therefore, the SCR device needs the additional secondary protection circuit (the series resistor and the gate-grounded NMOS, GGNMOS, in Fig. 1.3(c)) to perform the overall ESD protection function to protect the input stages. The secondary protection circuit has to sustain the ESD stress before the LSCR is triggered on to discharge the ESD current on the input pad. The relationship among the LSCR's switching voltage (Vt1\_SCR), series resistor (R), secondary breakdown voltage of GGNMOS (Vt2\_GGNMOS), and secondary breakdown current of GGNMOS (It2\_GGNMOS) can be approximated as following:

Vt1 SCR

$$<$$

(It2 GGNMOS  $\times$  R)  $+$  Vt2 GGNMOS (1.1)

Because the LSCR is hard to be triggered on in time, the secondary ESD protection circuit was designed with larger-sized GGNMOS and series resistor to protect itself from ESD damage, and to make the LSCR be triggered on successfully. This secondary ESD protection circuit with large device dimensions often occupies more layout area. If the secondary protection circuit was not properly designed, it had caused the fail window in the ESD test scanning from the low voltage to high voltage [37]. Such input ESD protection circuit was found to pass the ESD stress with low voltage level or high voltage level, but it was failed when the ESD stress with a middle voltage level [37]. So, the design of the secondary protection circuit with the LSCR for the overall input ESD protection circuit is somewhat critical in the CMOS ICs.

#### 1.3.2 Modified Lateral SCR (MLSCR) [16]

In order to reduce the switching voltage of LSCR device to provide more effective ESD protection for the internal circuits, the modified lateral SCR (MLSCR) was invented. The device structure of the MLSCR is illustrated in Fig. 1.4(a), and the corresponding I-V characteristic of the MLSCR in a 0.25-µm CMOS process is shown in Fig. 1.4(b). The example of using the MLSCR device as the input ESD protection circuit is shown in Fig. 1.4(c). In some applications, the N-well of MLSCR is connected to the input pad. The MLSCR is made by adding an N+ diffusion across the N-well/P-well junction to lower the avalanche breakdown voltage of N-well/P-well junction. However, the switching voltage (~12 V) of the MLSCR is still greater than the gate-oxide breakdown voltage of input stages in the same process. Therefore, the MLSCR has to be still cooperated with the secondary

protection circuit to perform the overall ESD protection functions to the input stages. Due to the lower switching voltage (~12 V) in the MLSCR in the 0.25-µm CMOS process, the secondary protection circuit could have smaller device dimensions to save total layout area. Unsuitable design or layout on the secondary protection circuit still causes the ESD damage located on the secondary protection circuit rather than the MLSCR device. For output stage, the two-stage ESD protective configuration will cause some signal delay under normal circuit operating conditions, so the LSCR and MLSCR devices are seldom used in the output ESD protection designs.

#### 1.3.3 Low-Voltage Triggering SCR (LVTSCR) [17], [18]

To more effectively protect the input stages and even the output stages, the low-voltage triggering SCR (LVTSCR) had been invented. The device structure of the LVTSCR is illustrated in Fig. 1.5(a), and the corresponding I-V characteristic of the LVTSCR in a 0.25-µm CMOS process is shown in Fig. 1.5(b). The example of using the LVTSCR device as the input ESD protection circuit is shown in Fig. 1.5(c). In some applications, the N-well of LVTSCR is connected to the input pad. The switching voltage of the LVTSCR (~7 V) is equivalent to the drain breakdown or punchthrough voltage of the short-channel NMOS device, which is inserted into the LSCR structure, rather than the original switching voltage of LSCR device (~22 V). With such a low switching voltage, the LVTSCR can provide effective ESD protection for the input or output stages of CMOS ICs without secondary ESD protection circuit. Therefore, the total layout area of the ESD protection circuits with the LVTSCR can be significantly saved. Furthermore, to protect both PMOS and NMOS in the input or output stage of CMOS ICs, the complementary-LVTSCR structure [18] had been invented to provide the better ESD protection.

#### 1.3.4 Gate-Coupled LVTSCR [19]

To effective protect the ultra-thin gate oxide in deep-submicron CMOS process, the gate-coupling technique was applied to further reduce the switching voltage of the LVTSCR without involving avalanche breakdown mechanism. The ESD protection circuit for input or output pad with the complementary gate-coupled LVTSCR devices (NMOS-triggered LSCR (NTLSCR) and PMOS-triggered LSCR (PTLSCR)) is shown in Fig. 1.6(a). The device

structure of the complementary gate-coupled NTLSCR / PTLSCR is illustrated in Fig. 1.6(b), and the I-V characteristics of the gate-coupled NTLSCR in a 0.25-µm CMOS process is shown in Fig. 1.6(c). The dependence of the switching voltage of SCR device on the gate-bias voltage of the NTLSCR device is shown in Fig. 1.6(d). The capacitances (Cn and Cp) in Fig. 1.6(a) must be designed at some suitable value, where the coupled voltage under normal circuit operating conditions is smaller than the threshold voltage of NMOS / PMOS, but greater than the threshold voltage of NMOS / PMOS under ESD zapping conditions [38]. The switching voltage of the gate-coupled NTLSCR (PTLSCR) can be adjusted with the coupled voltage on the gate of the short-channel NMOS (PMOS) in the SCR device structure. The higher coupled voltage on the gate of the short-channel NMOS / PMOS in the NTLSCR / PTLSCR leads the lower switching voltage of NTLSCR / PTLSCR. Therefore, the gate-coupled NTLSCR / PTLSCR devices can quickly discharge ESD current to more effectively protect the ultra-thin gate oxide of the input or output stages.

#### 1.3.5 Hot-Carrier Triggered SCR (HCTSCR) [20]

The power-rail ESD clamp protection circuit with hot-carrier triggered SCR (HCTSCR) is shown in Fig. 1.7(a). The device structures of primary protection devices including the SCR and trigger NMOS (M1) are shown in Fig. 1.7(b). The triggering mechanism of HCTSCR is initiated by the substrate hole current generated from the hot carrier effect of M1 during an ESD event. To ensure the proper operation of HCTSCR, M1 the must be active to provide sufficient substrate current to trigger on the SCR before other devices connected to VDD are damaged by ESD energy. The switching voltage of HCTSCR is dependent on the substrate hole current, which is the function of gate length, gate voltage, and drain voltage of the M1 [39]. The smaller gate length of M1 results in the lower switching voltage of HCTSCR. The gate voltage coupled through the capacitor (M2) has to be carefully designed to gain the peak substrate current. The device dimensions of M2 and M3 have to be optimized to ensure that the gate voltage of M1 is greater than its threshold voltage to trigger the HCTSCR on during ESD stresses. In addition, a double guardring has to be used around the perimeter of HCTSCR to prevent the SCR from being accidentally triggered on by the current injected from the exterior. With a SCR as the power-rail ESD clamp circuit, it can effectively clamp the ESD overstress voltage to avoid ESD damage on internal circuits.

However, this SCR in power-rail ESD clamp circuit could be triggered on by transient-induced latchup [32], when IC is under normal operating conditions. This will cause serious latchup failure on the CMOS IC, if the holding voltage of SCR device is smaller than the VDD voltage level.

#### 1.3.6 Grounded-Gate NMOS Triggered SCR (GGSCR) [21], [22]

The grounded-gate NMOS triggered SCR (GGSCR) is another choice for on-chip ESD protection circuit. A NMOS transistor, which resembles a GGNMOS configuration, is used as an external trigger device to trigger on the GGSCR. In contrast to the LVTSCR, the drain of the external trigger NMOS in GGSCR is directly coupled to the pad and its gate and source are coupled into the P-substrate (the base of NPN). The example of using the GGSCR device as the input ESD protection circuit is shown in Fig. 1.8(a). The layout top view of the GGSCR is illustrated in Fig. 1.8(b) [22]. When an ESD zapping is applied to the I/O pad in Fig. 1.8(a), the external trigger NMOS will enter avalanche breakdown first to inject the triggering current into the P-substrate and poly resistor. As long as the base voltage of NPN is greater than 0.7 V, the GGSCR will be triggered on. The poly resistor in Fig. 1.8(b) allows to control the triggering and holding current and to prevent the false trigger of GGSCR. From the experimental results, the GGSCR, designed with a shorter anode-to-cathode spacing, will have the lower holding voltage, higher It2, better dV/dt triggering ability, and faster turn-on speed than those of LVTSCR with a longer anode-to-cathode spacing.

#### 1.3.7 Substrate-Triggered SCR (STSCR) [23]-[26]

The turn-on mechanism of an SCR device is essentially a current triggering event. SCR can be quickly triggered on into its latching state, while a current is applied to its base or substrate. With the substrate-triggered technique, the p-type substrate-triggered SCR (P\_STSCR) and n-type substrate-triggered SCR (N\_STSCR) devices for ESD protection are proposed and investigated in Chapters 2 and 3 in this thesis. Furthermore, the STSCR device with dummy-gate structure to further reduce the switching voltage and to improve the turn-on speed of STSCR [40]-[42] is discussed in Chapter 5 in this thesis.

#### 1.3.8 Double-Triggered SCR (DTSCR) [27]

Another method, to reduce the switching voltage of LSCR device and to further enhance the turn-on speed of LSCR device more efficiently, is the double-triggered technique, which is used to synchronously trigger the NPN and PNP bipolar transistors in SCR structure. The device characteristics, turn-on properties, and the corresponding ESD detection circuits of DTSCR device are investigated in detail in Chapter 4 in this thesis. The dummy-gate structure used to block the STI in SCR device can be applied to the DTSCR structure to further reduce the switching voltage and to enhance the turn-on speed of DTSCR more efficiently.

#### 1.3.9 Native-NMOS-Triggered SCR (NANSCR) [28]

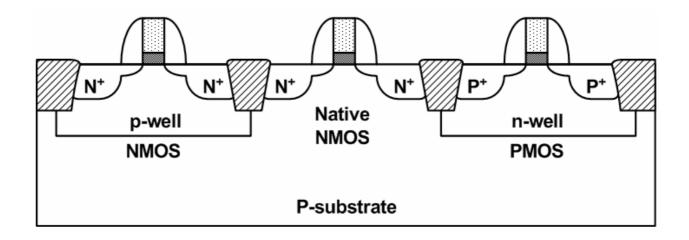

The native NMOS is directly built in a lightly-doped p-type substrate in sub-quarter-micron CMOS process, whereas the normal NMOS (PMOS) is in a heavily-doped P-well (N-well) in a P-substrate twin-well CMOS technology. The native NMOS and lateral SCR can be merged together to be a new ESD protection device, native-NMOS-triggered SCR (NANSCR), which is discussed in detail in Chapter 6 in this thesis.

# 1.3.10 Stacked-NMOS Triggered SCR (SNTSCR) for Mixed-Voltage I/O Buffer [29], [30]

To improve the ESD robustness of stacked NMOS in mixed-voltage I/O buffer, the stacked-NMOS triggered SCR (SNTSCR) had been reported without using the thick gate oxide. The ESD protection circuit combined gate coupling circuit with SNTSCR for mixed-voltage I/O buffer is shown in Fig. 1.9(a). The ESD detection circuit and the device structure of SNTSCR are shown in Fig. 1.9(b). Such an ESD protection circuit with only thin gate oxide is fully process-compatible with general CMOS processes without causing the gate-oxide reliability issue. During normal circuit operating conditions, the Mn3 in Fig. 1.9(b) acts as a resistor to bias the gate voltage (Vg1) of Mn1 at VDD. But, the gate of Mn2 is grounded through the resistor R2. So, all the devices in the ESD protection circuit can meet the electrical-field constraint of gate-oxide reliability in the normal circuit operation

condition. Under the positive-to-VSS (PS) ESD-zapping condition (with grounded VSS but floating VDD), the Mp is turned on but Mn3 is off since the initial voltage level on the floating VDD line is zero. The capacitors C1 and C2 are designed to couple ESD transient voltage from the I/O pad to the gates of Mn1 and Mn2, respectively. The coupled voltage should be designed greater than the threshold voltage to turn on Mn1 and Mn2 for triggering on the SNTSCR device, before the devices in the mixed-voltage I/O circuit are damaged by ESD stress. With the gate-coupling circuit technique, the switching voltage of SNTSCR can be nearly reduced to its holding voltage, so the SNTSCR can be quickly triggered on to discharge ESD current. From the experimental results in 0.35-µm CMOS process, the HBM ESD level of the mixed-voltage I/O buffer with this ESD protection circuit can be greatly improved to 8 kV, as compared with that (~2 kV) of the traditional mixed-voltage I/O buffer with only stacked NMOS device.

#### 1.3.11 Dual-Direction SCR [43]

A typical ESD protection scheme must protect each I/O pad against ESD events in all stressing modes with respect to both VDD and VSS power lines (i.e., PS, negative-to-VDD (ND), positive-to-VDD (PD), and negative-to-VSS (NS) ESD-zapping conditions). The dual-direction SCR device was invented in BiCMOS technology to provide the ESD protection in all stressing modes through the active SCR current paths to discharge ESD current. The device structure of a dual-direction SCR device illustrated in Fig. 1.10(a) is a symmetrical 5-layer NPNPN structure comprising one lateral PNP (Q1) and two vertical NPN (Q2 and Q3) in the BiCMOS process. The trigger-assist circuit to reduce the switching voltage of dual-direction SCR comprises two pairs of Zener diodes (D1~D4) with back-to-back connection, as shown in Fig. 1.10(b). When a positive ESD pulse is applied to the anode of dual-direction SCR and its cathode is relatively grounded (e.g., PS or ND ESD-zapping condition), the Zener diode D1 will be reverse breakdown first to conduct some ESD current to trigger on the NPN bipolar Q3 and then in turn turns on the PNP bipolar Q1. The positive ESD current can be discharged through the current path1 in Fig. 1.10(b). Similarly, when a negative ESD pulse is applied to anode of dual-direction SCR with its cathode grounded (e.g., PD or NS ESD-zapping condition), the negative ESD current can be discharged through the current path2 in Fig. 1.10(b). The I-V characteristic of the dual-direction SCR is shown in Fig. 1.10(c). Such a dual-direction SCR can provide the desired low holding voltage and low impedance path to protect the internal circuit under positive and negative ESD zapping. To realize the dual-direction SCR device in the CMOS process, an extra deep N-well mask will be added into the process flow. In the earlier literature, the full-SCR protection design for I/O pad with four SCR in CMOS IC had been reported [44].

#### 1.3.12 SCR Devices in Other Applications

Except the standard CMOS process, SCR devices can be used as the ESD protection circuits in other applications, such as high-voltage process. The drain-extended NMOS (DENMOS) or lateral DMOS (LDMOS) had been well studied and used in mature high-voltage processes to tolerant the large gate-to-drain voltage. However, the area-efficient ESD robustness of DENMOS or LDMOS is very poor to sustain the required ESD specifications under the limitation of parasitic capacitance. The DENMOS merged with an SCR [45], [46] and the embedded SCR LDMOS (ESCR-LDMOS) [47] had been reported to improve ESD level of high-voltage IC products. Another ESD protection device for high-voltage applications is the mirrored lateral SCR (MILSCR) [48]. The MILSCR, which is designed with dual-direction active SCR current paths, comprises two vertical NPN transistors, one vertical, and one lateral PNP transistors in N-epi P-substrate high-voltage CMOS process. The MILSCR was designed for high-voltage applications [48], but its switching voltage can also be adjusted to meet the requirements of the low-voltage CMOS ICs as the MLSCR or the LVTSCR. Although the SCR-based devices can elevate the ESD levels of high-voltage CMOS IC products, how to avoid the transient-induced latchup issue [32] of SCR-based devices under normal circuit operating conditions in high-voltage process is another serious concern.

#### 1.4 SCR LATCHUP ENGINEERING

In order to make SCR-based devices with low enough switching voltage for effective ESD protection, transient-induced latchup issue [32] must be avoided. There are two solutions to avoid the SCR-based devices with low switching voltage being accidentally

triggered on by noise pulse when CMOS ICs are in normal circuit operating conditions. As shown in Fig. 1.11(a), one is to increase the triggering current of the low-voltage-trigger SCR-based devices, but the switching voltage and the holding voltage are kept the same. With higher triggering current, the low-voltage-trigger SCR-based devices such as LVTSCR has enough noise margin against the overshooting or undershooting noise pulses on the pads. A high-current NMOS-trigger lateral SCR (HINTSCR) [49] device has been successfully designed by adding a bypass diode into the LVTSCR structure to increase its triggering current up to 218.5 mA in a 0.6- $\mu$ m CMOS process. Such HINTSCR has a noise margin greater than VDD+12 V in the 3-V application. In addition, a high holding current SCR (HHI-SCR) device, which is modified from the GGSCR, was reported with a holding current of ~70 mA in a 0.1- $\mu$ m CMOS process by adjusting the external poly resistance from ~k $\Omega$  in GGSCR to only ~10  $\Omega$  in HHI-SCR.

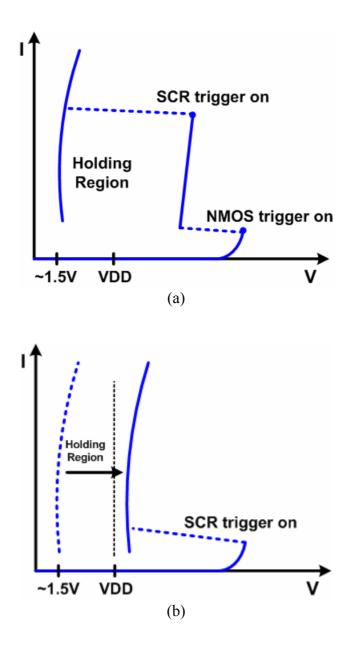

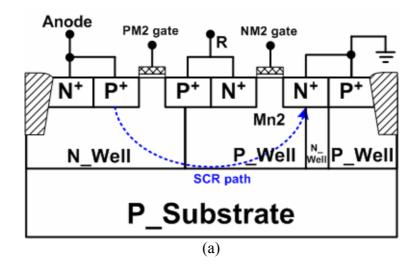

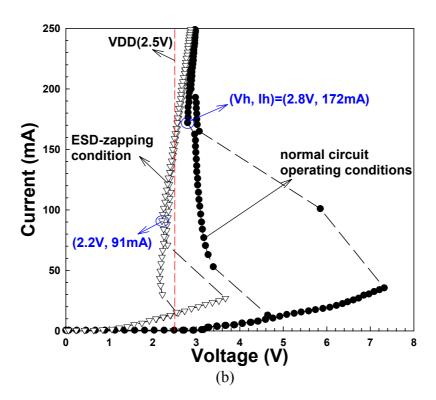

Another method immune from latchup is to increase the holding voltage of the SCR-based devices to be greater than the maximum voltage level of VDD, as shown in Fig. 1.11(b). By using the epi-substrate, the holding voltage of SCR device can be increased to avoid latchup problem [50]. But, the fabrication cost of CMOS wafer will be also increased. By stacking the voltage drop elements (such as diode or the SCR devices) with the SCR-based device can elevate its total holding voltage in the bulk CMOS process. The switching voltage and current can be still kept at a lower voltage level by suitable trigger-assist circuit design. A cascaded-LVTSCR [51] structure was designed to increase the holding voltage (> VDD) without degrading its ESD robustness in a 0.35-µm silicided CMOS technology. In addition, the ESD protection circuits designed with stacked STSCR devices [24], or designed with a STSCR device and stacked diode string [26], had been reported to have 7-kV HBM ESD level and free to latchup issue in a 0.25-um silicided CMOS technology. Recently, the holding voltage of a single SCR device can be dynamically adjusted for ESD protection (with low holding voltage) and for normal circuit operation (with higher holding voltage) [52]. A dynamic holding voltage SCR (DHVSCR) was reported to be an ESD protection device with high latchup immunity. The device structure of DHVSCR is shown in Fig. 1.12(a). A PMOS and a NMOS are inserted into the DHVSCR device structure, as compared with LSCR structure. The I-V characteristics of the DHVSCR under normal circuit operating conditions and ESD-zapping conditions in a 0.25-µm CMOS process are shown in Fig. 1.12(b). Under normal circuit operating conditions, the gates (Vg1 and Vg2) of PMOS and NMOS are biased at 2.5 V (VDD), but at 0 V under ESD-zapping conditions. The holding voltage and holding current of DHVSCR under normal circuit operating conditions are 2.8 V and 172 mA, respectively. Thus, the DHVSCR will not be kept in the latchup state in normal circuit operating conditions. However, the holding voltage and holding current of DHVSCR under ESD-zapping conditions are dropped to 2.2 V and 91 mA, respectively. So, the DHVSCR can also clamp the ESD overstress to a lower voltage level to sustain the higher ESD levels. The holding voltage and holding current of DHVSCR can be adjusted by controlling the gate voltages of PMOS and NMOS, which are merged with the SCR structure.

However, with the scaled-down CMOS technologies, the power-supply voltages in CMOS ICs have also been scaled downwards to follow the constant-field scaling requirement and to reduce power consumption. For CMOS IC products realized in a 0.13-μm silicided CMOS process, the maximum supply voltage for the internal circuit has been reduced to 1.2 V, so the latchup concern inherent in SCR-based device will vanish certainly. Therefore, SCR-based device with lower switching voltage can be a great candidate for on-chip ESD protection due to its highest ESD robustness, smallest layout area, and free to latchup danger, as compared with other ESD protection devices. However, in such a 0.13-μm CMOS process with ultra thinner gate oxide, the turn-on speed of SCR devices should be enhanced to quickly discharge ESD overstress voltage for protecting such thinner gate oxide. The NANSCR [28] and the dummy-gate structure [40] to improve the turn-on speed of SCR-based device will be a better choice to protect such an ultra thinner gate oxide in nanoscale CMOS processes.

The comparison among various SCR-based devices for on-chip ESD protection has been summarized in Table 1.1. The HBM and MM ESD levels of SCR-based devices are always superior to other non-SCR ESD protection devices. The switching voltage and the turn-on speed of SCR-based devices must be finely designed to fully and effectively protect the ultra-thin gate oxide of input stages, especially against the fast CDM ESD events. The switching voltage and turn-on speed of SCR-based devices will be the dominated factors on the overall performances of on-chip ESD protection circuits with SCR-based devices in nanoscale CMOS process with the maximum voltage supply smaller than 1.2 V.

### 1.5 THESIS ORGANIZATION

To reduce the switching voltage and to improve the turn-on speed of SCR device for effective ESD protection, some advanced trigger-assist circuits applied to SCR device are proposed and discussed in this thesis. This thesis contains seven chapters. Chapter 1 introduces the background of ESD events and the turn-on mechanism of SCR device. An overview of the ESD protection circuit with SCR-based devices for general or high-voltage CMOS processes is presented. Moreover, two practical problems (such as higher switching voltage and transient-induced latchup issue) limiting the use of SCR-based devices in on-chip ESD protection are discussed. Some modified device structures and trigger-assist circuit techniques to reduce the switching voltage of SCR-based devices are reported. The solutions (increase the triggering current or holding voltage) to overcome latchup-issue in the SCR-based devices are also discussed to safely apply the SCR-based devices in the ESD protection circuits of CMOS IC products.

In Chapter 2, an SCR device with substrate-triggered technique is first proposed for effective on-chip ESD protection. The DC I-V characteristics of a single STSCR device or stacked STSCR devices are investigated and discussed in detail in a 0.25-µm CMOS process. The ESD-like voltage pulses are applied to the STSCR device to verify its turn-on time under different substrate biases. The ESD-zapping and TLP measurements have been used to verify the ESD robustness of the STSCR devices under different substrate-triggered currents. For CMOS IC applications with maximum voltage level of 2.5 V, the on-chip ESD protection circuit with two STSCR devices in stacked configuration has a clamp voltage of ~3.2V, the HBM (MM) ESD level of > 8 kV (700 V), and free to latchup issue.

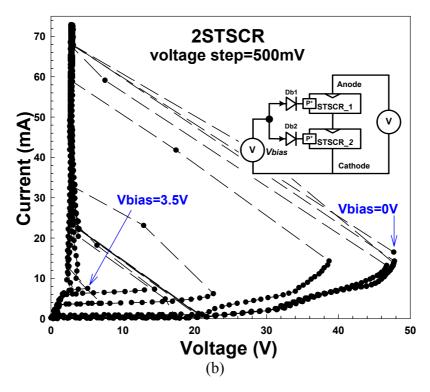

In Chapter 3, a complementary circuit style with the substrate-triggered SCR devices is designed to discharge both of the pad-to-VSS and pad-to-VDD ESD stresses. The DC I-V characteristics of an STSCR device with stacked diode string are investigated and discussed in detail in a 0.25-µm CMOS process. The advanced ESD detection circuits are proposed to provide the substrate- and well-triggered currents according to the principle of RC delay (used to distinguish ESD-zapping events or the normal circuit operating conditions) or the gate-coupled circuit technique (used to generate the trigger current) to turn on this STSCR device during ESD zapping. To verify the functions of the input, output, and power-rail ESD protection circuits, the turn-on waveforms on the I/O pad and power pad are measured under

normal circuit operating conditions and ESD-zapping conditions. For the CMOS IC applications with VDD of 2.5V, the latchup-free ESD protection circuits designed with complementary-STSCR devices and two stacked diodes can sustain the HBM (MM) ESD level of  $\sim 7.25 \mathrm{kV}$  (500V) in a 0.25- $\mu$ m fully salicided CMOS process without using silicide-blocking mask.

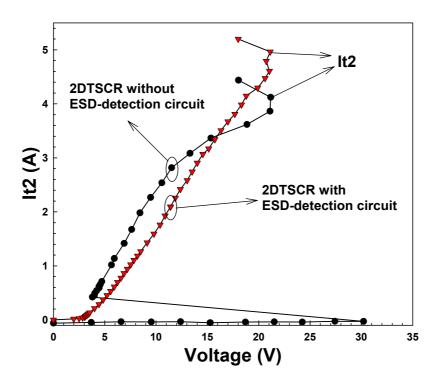

In Chapter 4, to further enhance the turn-on speed of SCR device, a double-triggered technique is proposed to synchronously trigger the NPN and PNP transistors in the SCR structure. With the double-triggered technique, the switching voltage and turn-on time of SCR device can be reduced more efficiently and quickly. Moreover, the required pulse widths to trigger on the SCR device can be significantly reduced by double-triggered technique. A series of turn-on waveforms used to verify the turn-on efficiency of the double-triggered SCR (DTSCR) device are investigated in this chapter. The corresponding ESD-detection circuits to synchronously generate the substrate and well triggered currents are also proposed for input, output, and power-rail ESD protection circuits.

In Chapter 5, a novel dummy-gate structure is used to block the shallow trench isolation (STI) and silicide between the diffusion regions in the SCR device, and therefore to further enhance its turn-on speed and CDM ESD levels. The DC I-V curves, turn-on waveforms, ESD-zapping, and TLP measurements are applied to verify the characteristics of STSCR with dummy-gate structure. From the experimental results in a 0.25-µm CMOS process with the gate-oxide thickness of ~50 Å, the switching voltage, turn-on speed, turn-on resistance, and CDM ESD levels of the SCR device with dummy-gate structure have been greatly improved, as compared to the normal SCR with STI structure.

In Chapter 6, a novel native-NMOS-triggered SCR (NANSCR) is proposed for on-chip ESD protection in a 0.13-µm CMOS process with voltage supply of 1.2 V. From the experimental results, the switching voltage, holding voltage, turn-on resistance, turn-on speed, and CDM ESD level of NANSCR can be greatly improved to protect the ultra-thin gate oxide against ESD stresses, as compared with the traditional low-voltage triggering SCR (LVTSCR). The emission microscope (EMMI) photographs are used to verify the turn-on process of NANSCR device under different ESD voltages. The proposed NANSCR can be designed for the input, output, and power-rail ESD protection circuits without latchup danger. In addition, a new whole-chip ESD protection scheme realized with the proposed NANSCR devices is also proposed to provide efficient and overall protection for the internal circuits in

the ultra large-scale CMOS ICs with multiple power pins.

Finally, the main results of this thesis are summarized in Chapter 7. Some suggestions for the future works are also addressed in this chapter.

TABLE 1.1 Comparison among the SCR-based devices for on-chip ESD protection.

| Application             | SCR Category                                           | Switching<br>Voltage | Turn-on<br>Speed | *Latchup<br>Issue | Protection<br>Circuit<br>Complexity | Overall<br>Performance |

|-------------------------|--------------------------------------------------------|----------------------|------------------|-------------------|-------------------------------------|------------------------|

| Standard CMOS Process   | Lateral SCR (LSCR) [12], [13]                          | high                 | slow             | Yes               | hard                                | poor                   |

|                         | Modified LSCR (MLSCR) [16]                             | middle               | slow             | Yes               | hard                                | middle                 |

|                         | Low-Voltage-Triggered SCR<br>(LVTSCR) [17], [18]       | low                  | middle           | Yes               | easy                                | good                   |

|                         | Gate-Coupled<br>PTLSCR/NTLSCR [19]                     | lower +<br>tunable   | fast             | Yes               | middle                              | better                 |

|                         | High-Current-Triggered<br>LVTSCR (HINTSCR) [49]        | low                  | middle           | No                | middle                              | better                 |

|                         | High-Holding-Voltage<br>LVTSCR [51]                    | low                  | middle           | No                | hard                                | good                   |

|                         | Hot-Carrier-Triggered SCR<br>(HCTSCR) [20]             | low +<br>tunable     | slow             | Yes               | hard                                | middle                 |

|                         | GGNMOS-Triggered SCR<br>(GGSCR) [21], [22]             | low                  | fast             | Yes               | easy                                | better                 |

|                         | High-Holding-Current SCR<br>(HHI-SCR) [22]             | low                  | slow             | No                | middle                              | better                 |

|                         | Dual-Direction SCR [43]                                | low                  | middle           | Yes               | hard                                | good                   |

|                         | Stacked-NMOS-Triggered SCR<br>(SNTSCR) [29], [30]      | lower +<br>tunable   | middle           | Yes               | hard                                | better                 |

|                         | Substrate-Triggered SCR<br>(STSCR) [23]-[26]           | lower +<br>tunable   | fast             | Yes               | middle                              | better                 |

|                         | Double-Triggered SCR<br>(DTSCR) [27]                   | lower +<br>tunable   | faster           | Yes               | middle                              | better                 |

|                         | Dummy-Gate-Blocking<br>STSCR [40]-[42]                 | lower +<br>tunable   | faster           | Yes               | middle                              | better                 |

|                         | Native-NMOS-Triggered SCR<br>(NANSCR) [28]             | lower +<br>tunable   | faster           | Yes               | easy                                | best                   |

|                         | Dynamic-Holding-Voltage SCR<br>(DHVSCR) [52]           | lower                | fast             | No                | middle                              | better                 |

| High-Voltage<br>Process | Mirrored Lateral SCR<br>(MILSCR) <sup>[48]</sup>       | high                 | slow             | Yes               | easy                                | middle                 |

|                         | DENMOS with Self-Aligned<br>STI-Blocked SCR [45], [46] | high                 | slow             | Yes               | easy                                | middle                 |

| High                    | Embedded SCR LDMOS [47]                                | high                 | slow             | Yes               | easy                                | middle                 |

<sup>\*</sup>Some of latchup issue can be solved by stacking the multiple SCR devices to have a total holding voltage greater than the maximum voltage level of VDD or signals of CMOS ICs.

Fig. 1.1 The typical design of on-chip ESD protection circuits in CMOS ICs.