# 具有 LVDS 與 RSDS 低電壓差動訊號傳輸規格之平面顯示器高速輸入輸出緩衝器設計

學生: 莊 凱 嵐 指導教授: 柯 明 道 博士

國立交通大學

電子工程學系 電子研究所碩士班

## 摘要

今日平面顯示器持續在提供其色彩濃度與解析度的增加。很多面板製造業者都已經可以量產解析度超過 SVGA (800×600 像素) 和 XGA (1024×768 像素)的平面顯示器。隨著平面顯示器解析度的快速增加,位於平面顯示器系統裡直接連接顯示卡到液晶顯示時脈控制器以及液晶顯示時脈控制器到面板驅動電路的介面應該操作於更高的資料傳輸速度。因此,位於平面顯示器系統介面的高速輸入輸出緩衝器設計是有其必要的。本論文共包含三個設計子項,透過三個獨立下線的晶片來驗證這些設計。

第一個設計為採用 0.25-µm 1P5M CMOS 製程技術所實現的一個相位鎖相 迴路,其電源電壓為 2.5 V。其所設計的輸出時脈頻率為 200 MHz 而由於使用 一個除八的除頻器故輸入參考時脈頻率為 25 MHz。

第二個設計為採用 0.25-µm 1P5M CMOS 製程技術所實現的三個輸入輸出 緩衝器,其電源電壓為 3.3 V。這些輸入輸出緩衝器可跟低電壓差動訊號傳輸規 格和更小擺幅差動訊號傳輸規格完全相容。此兩種低電壓差動訊號傳輸規格和更 小擺幅差動訊號傳輸規格都是用來定義平面顯示器系統裡的介面傳輸。這些輸入 輸出緩衝器的資料傳輸速度可以到達每秒 1.2 十億位元 (1.2 Gb/s),其可以支援 解析度為 UXGA (1600×1200 像素) 的平面顯示器。

第三個設計為一個可以將 28 位元的大擺幅 (3.3 V) 並列資料轉換成四條

低電壓差動訊號傳輸資料流或更小擺幅差動訊號傳輸資料流的傳送器,其採用 0.25-µm 1P5M CMOS 製程技術而其電源電壓為 3.3 V。位於傳送器的相位鎖相 迴路擁有七個不同的時脈相位以便將輸入的資料做並列轉串列的轉換。傳送器的資料操作速度可以到達每秒 1.05 十億位元 (1.05 Gb/s),其可以支援解析度為 SXGA (1280×1024 像素)的平面顯示器。

Co-Design on High-Speed I/O Buffers With

**Both LVDS and RSDS Standards for**

**Flat Panel Display Applications**

Student: Kai-Lan Chuang

Advisor: Prof. Ming-Dou Ker

Department of Electronics Engineering & Institute of Electronics

*National Chiao-Tung University*

**ABSTRACT**

Flat panel displays (FPDs) continue to offer an increase in color depth and

resolution, today. Beyond the SVGA ( $800 \times 600$  pixels) and XGA ( $1024 \times 768$  pixels)

resolutions of flat panel displays are ready for production by many flat panel

manufacturers. As the resolution of FPDs is increasing rapidly, the interfaces that

directly connect a graphics card to a liquid crystal display (LCD) timing controller

and a LCD timing controller to flat panel column drivers in FPD systems should be

operated at a higher data rate. Therefore, high-speed I/O buffers designed for

interfaces in FPD systems are necessary. This thesis includes three topics, which were

verified through 3 individual chips.

In the first topic, a phase-locked loop (PLL) has been implemented in a 0.25-um

1P5M CMOS process and the power supply is 2.5 V. The designed output clock

frequency is 200 MHz and the input reference clock frequency is 25 MHz due to the

divided by eight divider.

In the second topic, three I/O buffers have been fabricated in a 0.25-µm 1P5M

- iii -

CMOS process and the power supply is 3.3 V. These I/O buffers are fully compatible with both low-voltage differential signaling (LVDS) standard and reduced-swing differential signaling (RSDS) standard. Both LVDS and RSDS standards are defined for interface transmission in FPD systems. The data rates of these I/O buffers are up to 1.2 Gb/s which can support the UXGA ( $1600 \times 1200$  pixels) resolution of flat panel displays.

In the third topic, a transmitter which converts 28 bits of full-swing (3.3 V) parallel data into four LVDS or RSDS data streams has been implemented in a 0.25- $\mu$ m 1P5M CMOS process and the power supply is 3.3 V. The PLL in the transmitter has seven different clock phases in order to perform parallel-to-serial conversion of incoming data. The data rate of the transmitter is up to 1.05 Gb/s which can support the SXGA (1280 × 1024 pixels) resolution of flat panel displays.

### 誌謝

回顧快兩年的碩士求學生涯,這過程真可以酸甜苦辣、五味雜陳來形容。這 其中最苦的時期在於碩一剛入學時,由於當時心態尚未調適過來以至於在修課方 面充滿著極大的挫折感與無力感。幸而在實驗室周千譯學長適時的精神鼓勵讓我 能在幾乎要放棄的情況下咬緊牙根撐過最苦的日子,這不但讓我對日後的修課不 再畏懼也對未來所面臨到更困難的挑戰具有更高的抗壓性。回顧這段往事真使我 覺得自己何其幸運,能在最無助的時候得到實驗室師長最正面的幫助,這也使我 懷著最真誠的心,深深感謝生活中每一個貴人。

首先要感謝的是我的指導教授柯明道博士。老師以其本身嚴謹的研究態度以及超乎常人的研究熱情,讓我於這兩年中獲得最珍貴的研究心態與方法。而在老師開明的指導以及豐沛的研究資源下,我不但能盡情將研究的電路下線驗證,也由於所從事的論文研究具實用性而於日後國防役能找到不錯的公司。除此之外,老師亦提供相當充裕的研究經費使我在這兩年中不至於生活匱乏而能更努力的從事我的碩士論文研究。畢業之後無論從事任何研究我都將會僅記老師的至理名言:Smart = 做事要有效率,成果要有水準。

接著要感謝的是一起打拼的同學們,昌震、政賢、阿瑞、秦豪、權哲、如琳、大師兄、韋霆、紀豪、秉捷、瑋仁、旻珓、大頭、丁董、阿文、宗霖,大家一起做研究、出遊、唱歌、在實驗室講垃圾話,讓我在苦悶的研究生活中增添不少樂趣。我也要感謝實驗室陳世倫學長、陳榮昇學長、黃鈞正學長、徐新智學長、徐國鈞學長、林昆賢學長、黃彥霖學長、鄧至剛學長、林大新同學、黃冠勝同學以及甘瑞銘同學。他們無論是在論文研究的瓶頸或是晶片量測的疑難雜症上都給了我很多的方向及幫助,使我能更順利的完成我的碩士論文。

接著要感謝我於打工公司裡的簡丞星學長、繆俊偉學長、楊統貴學長、林巧茹學姐、蕭素美學姐以及林安源學長。感謝他們一年多來的照顧使我能更加順利的完成我的論文研究以及對科技業界工作的更深一層體會。

最後要感謝我的父母以及我的女友徐文慈小姐。感謝他們多年來默默的關心 與支持,在我最需要的時候給予最大的幫助,使我能勇往向前,一路走來直至今 日。生命中的貴人甚多,不可勝數,我將秉持著感恩的心,盡最大的能力幫助也 即將展開論文研究的學弟妹們。

> 莊凱嵐 九十三年六月

# **CONTENTS**

| ABST               | RACI    | (CHINESE)                            | i      |  |  |

|--------------------|---------|--------------------------------------|--------|--|--|

| ABST               | RACI    | Γ (ENGLISH)                          | iii    |  |  |

| ACKN               | IWO     | LEDGEMENT                            | v      |  |  |

| CONT               | ENTS    | S                                    | vi     |  |  |

| TABL               | E CA    | PTIONS                               | ix     |  |  |

| FIGURE CAPTIONSx   |         |                                      |        |  |  |

| Chapt              | er 1 Iı | ntroduction                          | 1      |  |  |

| 1.1                | Мотг    | VATION                               | 1      |  |  |

| 1.2                | BASIC   | SERIAL-LINK TRANSCEIVER ARCHITECTURE | 2      |  |  |

| ABSTRACT (ENGLISH) |         |                                      |        |  |  |

| 1.4                | THESI   | S ORGANIZATION                       | 3      |  |  |

| Chapt              | Si      | ignaling (LVDS) Standard and Reduced | -Swing |  |  |

| 2.1                |         |                                      |        |  |  |

|                    |         |                                      |        |  |  |

| 2.2                |         |                                      |        |  |  |

|                    |         |                                      |        |  |  |

| 2.3                |         |                                      |        |  |  |

|                    |         |                                      |        |  |  |

|                    |         | -                                    |        |  |  |

|                    |         | -                                    |        |  |  |

|                    |         | , <u> </u>                           |        |  |  |

|                    |         |                                      |        |  |  |

|                    | 2.3.6   |                                      |        |  |  |

|     |     | 2.3.7  | Advantages and Applications                       | 14      |

|-----|-----|--------|---------------------------------------------------|---------|

|     |     | 2.3.8  | Conclusion                                        | 15      |

| 2   | 2.4 | Intro  | DDUCTION TO RSDS                                  | 15      |

|     |     | 2.4.1  | Scope                                             | 15      |

|     |     | 2.4.2  | Electrical Specifications and Bus Configurations  | 16      |

|     |     | 2.4.3  | Applications                                      | 18      |

| 2   | 2.5 | COMP   | ARISON BETWEEN LVDS AND RSDS                      | 18      |

| Cha | pt  | er 3 P | hase-Locked Loop                                  | 31      |

| 3   | 3.1 | Intro  | DDUCTION                                          | 31      |

| 3   | 3.2 | BASIC  | PLL Architecture                                  | 32      |

| 3   | 3.3 | PLL C  | CIRCUIT IMPLEMENTATION                            | 32      |

|     |     | 3.3.1  | Phase Frequency Detector                          | 33      |

|     |     | 3.3.2  | Charge Pump                                       | 34      |

|     |     | 3.3.3  | Loop Filter                                       | 35      |

|     |     | 3.3.4  | Bias Generator                                    | 36      |

|     |     | 3.3.5  | Voltage-Controlled Oscillator                     | 38      |

|     |     | 3.3.6  | Differential-to-Single-Ended Converter            | 40      |

|     |     | 3.3.7  | DividerES                                         | 40      |

| 3   | 3.4 | PLL P  | PARAMETER DESIGN                                  | 41      |

| 3   | 3.5 | PLL N  | NOISE ANALYSIS AND STABILITY                      | 44      |

| 3   | 3.6 | PLL N  | MEASUREMENT RESULTLUSION                          | 46      |

| 3   | 3.7 | Conc   | LUSION                                            | 47      |

| Cha | pt  | er 4 H | ligh-Speed I/O Interface Circuits                 | 65      |

| ۷   | 4.1 | Intro  | DDUCTION                                          | 65      |

| ۷   | 4.2 | TAPER  | R Buffer                                          | 65      |

|     |     | 4.2.1  | Basic Concept                                     | 65      |

|     |     | 4.2.2  | Measurement Result                                | 66      |

|     |     | 4.2.3  | Conclusion                                        | 66      |

| ۷   | 4.3 | LVDS   | OUTPUT BUFFER                                     | 67      |

|     |     | 4.3.1  | Basic Concept                                     | 67      |

|     |     | 4.3.2  | Measurement Result                                | 68      |

|     |     | 4.3.3  | Conclusion                                        | 69      |

| ۷   | 4.4 | Co-di  | ESIGNED I/O BUFFERS WITH BOTH LVDS AND RSDS STAND | ARDS 69 |

|     |     | 4.4.1  | Basic Concept                                     | 69      |

|     |     | 4.4.2  | Measurement Result                                |         |

|     |     | 113    | Conclusion                                        | 7/      |

| Chapt | er 5 Transmitter                                | 94  |

|-------|-------------------------------------------------|-----|

| 5.1   | Introduction                                    | 94  |

| 5.2   | BUILDING BLOCKS OF THE TRANSMITTER              |     |

|       | 5.2.1 Pseudo Random Binary Sequence             | 94  |

|       | 5.2.2 Phase-Locked Loop                         |     |

|       | 5.2.3 Multiplexer and Co-Designed Output Buffer |     |

| 5.3   | MEASUREMENT RESULT                              | 96  |

| 5.4   | CONCLUSION                                      | 98  |

| Chapt | er 6 Summary and Future Works                   | 122 |

| 6.1   | Summary                                         | 122 |

| 6.2   | FUTURE WORKS                                    | 123 |

| REFE  | RENCES                                          | 124 |

| VITA  | 127                                             |     |

# **TABLE CAPTIONS**

| Table 1.1 | Industrial standards for high-speed serial link.             | 4  |

|-----------|--------------------------------------------------------------|----|

| Table 1.2 | Comparison between different transmission technologies       | 4  |

|           | that are applied for different I/O interfaces.               | 4  |

| Table 2.1 | The electrical-only ANSI/TIA/EIA-644 (LVDS) standard of LVDS | 20 |

| Table 2.2 | The scope of LVDS applications.                              | 20 |

| Table 2.3 | Merits and drawbacks of different I/O interface technologies | 21 |

| Table 2.4 | Electrical specifications of RSDS transmitter and receiver.  | 21 |

| Table 3.1 | The simulated and measured parameters of the designed PLL    | 48 |

| Table 4.1 | The measured parameters of the LVDS output buffer.           | 75 |

| Table 4.2 | The measured parameters of the co-designed I/O buffers.      | 75 |

| Table 5.1 | The simulated and measured parameters of the designed PLL.   | 99 |

# FIGURE CAPTIONS

| Fig. 1.1  | Basic serial-link transceiver architecture                                      |  |

|-----------|---------------------------------------------------------------------------------|--|

| Fig. 1.2  | Reduce noise and suppress EMI effect by using the differential transmission     |  |

|           | technology5                                                                     |  |

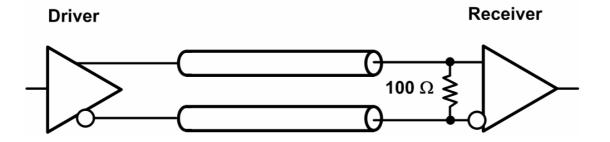

| Fig. 2.1  | The simplified diagram of LVDS driver and receiver connected via 100 $\Omega$   |  |

|           | differential impedance media                                                    |  |

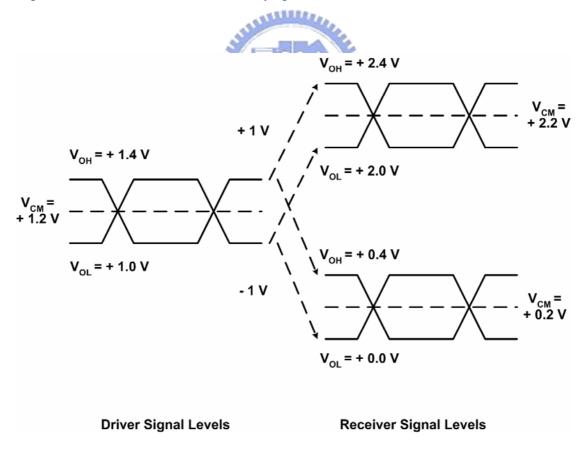

| Fig. 2.2  | The signaling levels of LVDS. 22                                                |  |

| Fig. 2.3  | Point-to-point configuration of LVDS. 23                                        |  |

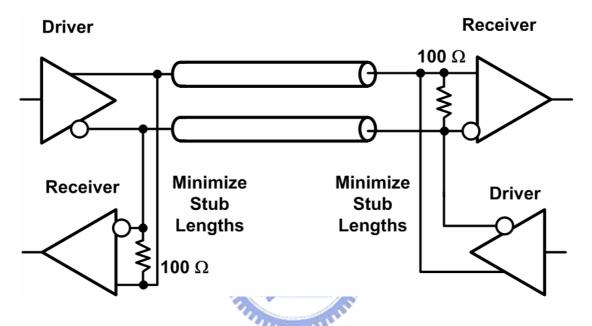

| Fig. 2.4  | Bi-directional configuration of LVDS. 23                                        |  |

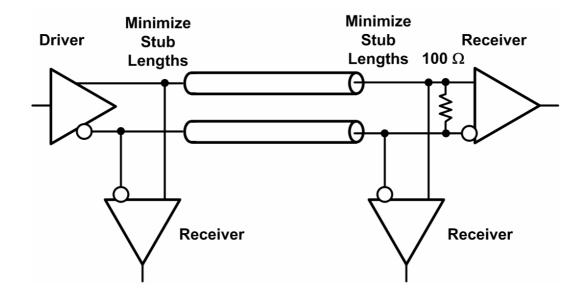

| Fig. 2.5  | Multi-drop configuration of LVDS                                                |  |

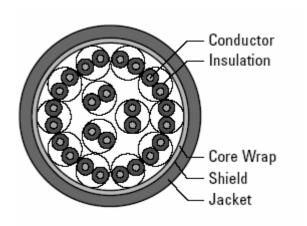

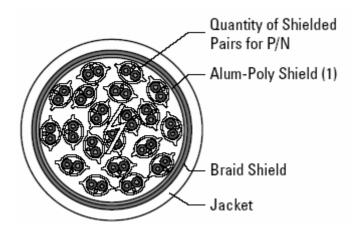

| Fig. 2.6  | Cross section drawing of a twisted pair cable. 24                               |  |

| Fig. 2.7  | Cross section drawing of a twin-ax cable. 24                                    |  |

| Fig. 2.8  | Cross section drawing of a flex circuit. 24                                     |  |

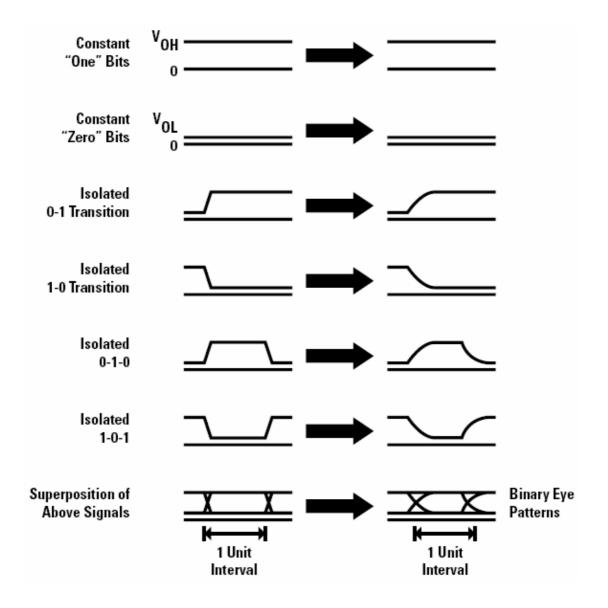

| Fig. 2.9  | Formation of an eye pattern by superposition. The left hand side is the eye     |  |

|           | pattern at the input of the cable and the right hand side is the eye pattern at |  |

|           | the end of the cable                                                            |  |

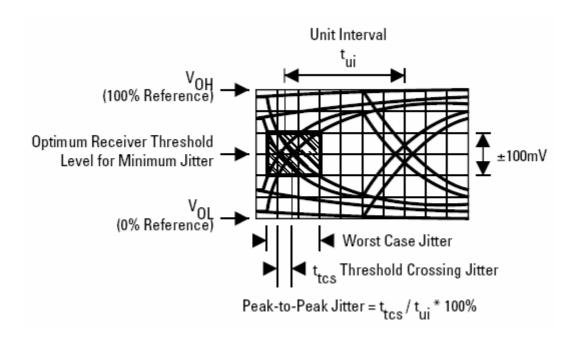

| Fig. 2.10 | Jitter measurements in an eye pattern of NRZ data                               |  |

| Fig. 2.11 | The common mode voltage range of the LVDS receiver                              |  |

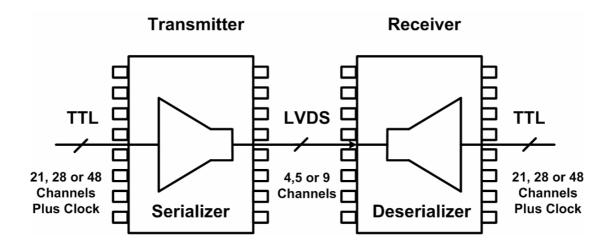

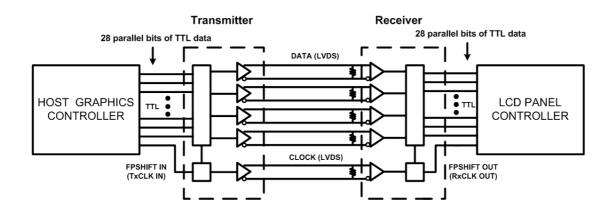

| Fig. 2.12 | The LVDS channel links which convert a TTL bus into a compact LVDS              |  |

|           | data stream and back to a TTL bus                                               |  |

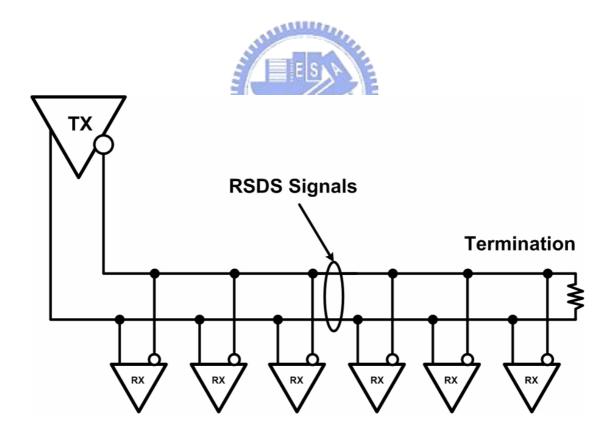

| Fig. 2.13 | The RSDS interface configuration. The interface contains three parts: a         |  |

|           | transmitter, receivers and a balanced interconnecting medium with a             |  |

|           | termination. 27                                                                 |  |

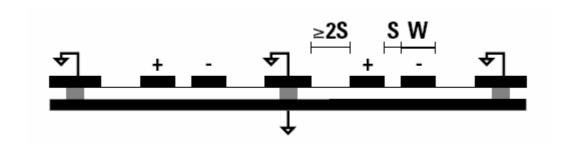

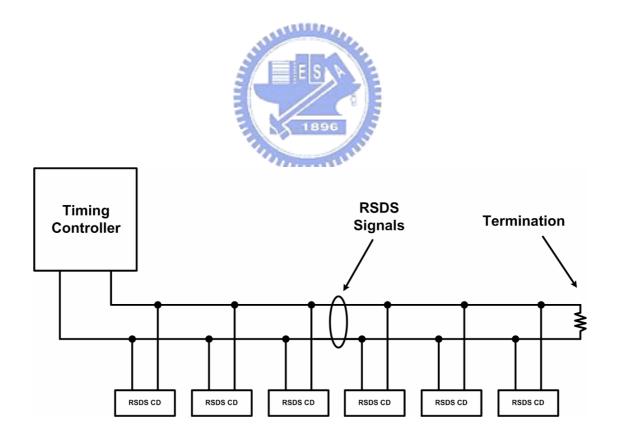

| Fig. 2.14 | Type 1 bus configuration of RSDS                                                |  |

| Fig. 2.15 | Type 2 bus configuration of RSDS                                                |  |

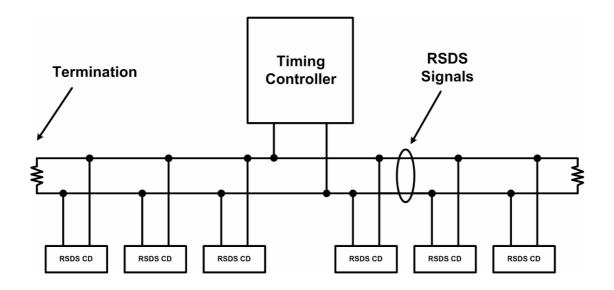

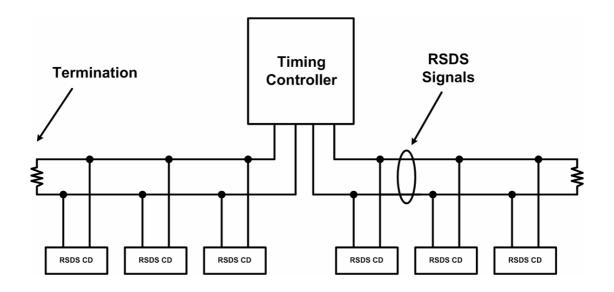

| Fig. 2.16 | Type 3 bus configuration of RSDS. 29                                            |  |

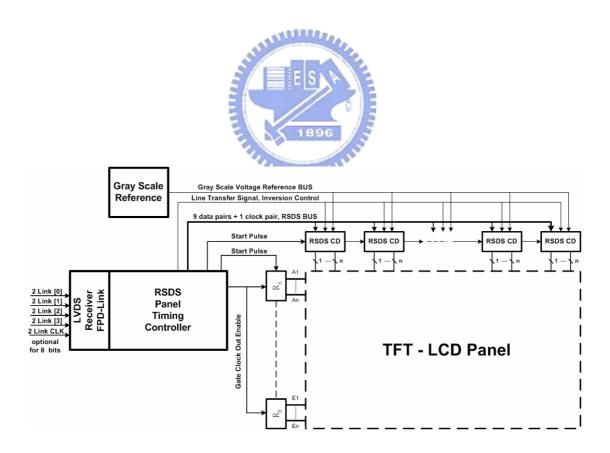

| Fig. 2.17 | The RSDS interface utilized in the flat panel display systems29                 |  |

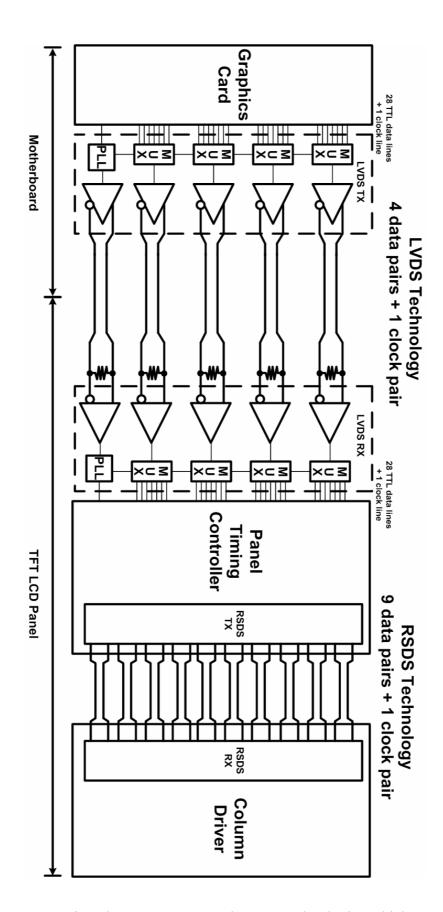

| Fig. 2.18 | Comparison between LVDS and RSDS technologies which are utilized in             |  |

|           | the interfaces of flat panel display systems                                    |  |

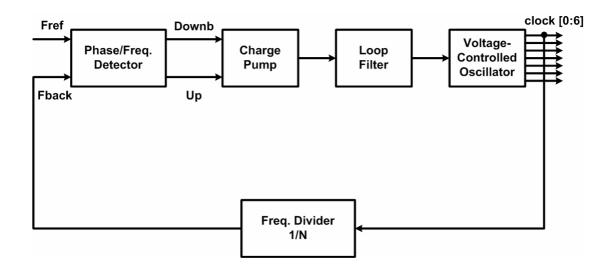

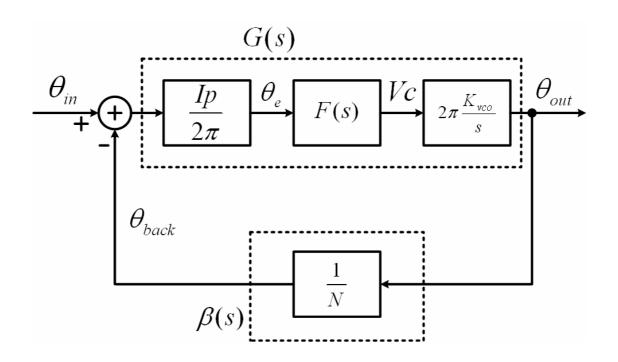

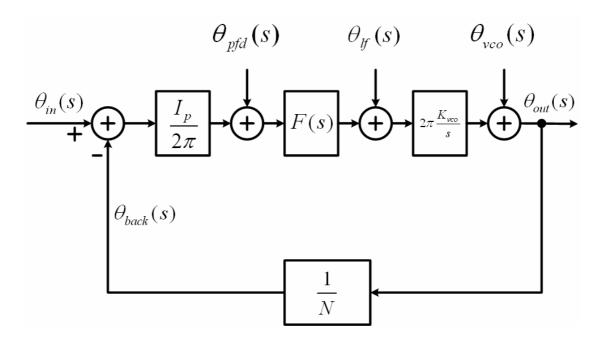

| Fig. 3.1  | The basic architecture of PLL. 49                                               |  |

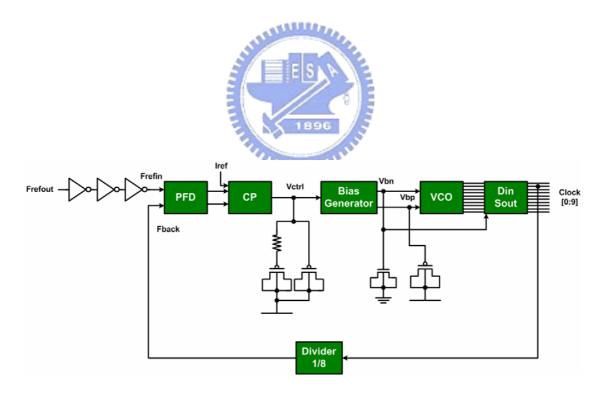

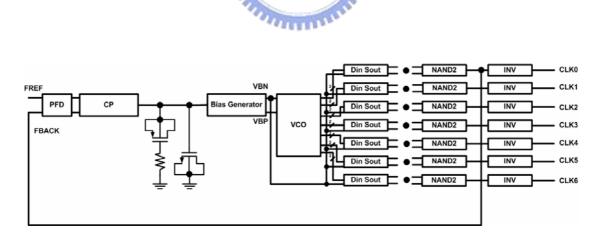

| Fig. 3.2  | The architecture of the designed PLL. The input reference clock frequency       |  |

|           | is 25 MHz and the output clock frequency is 200 MHz due to the frequency        |  |

|           | divider which is divided by eight49                                             |  |

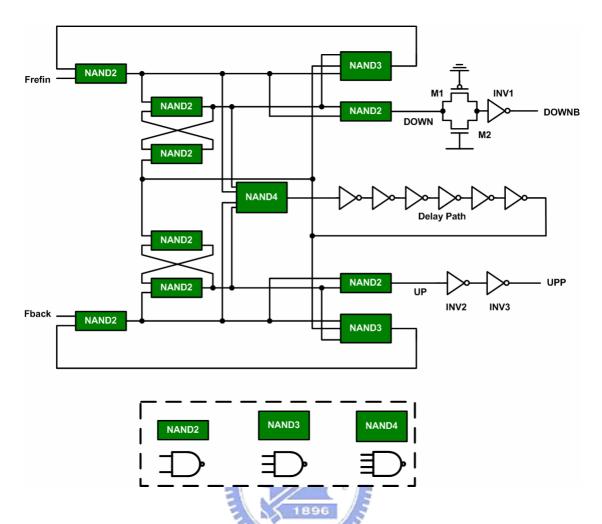

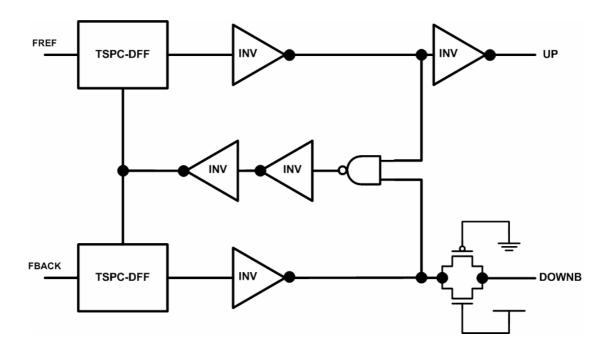

| Fig. 3.3  | The circuit implementation of the PFD                                           |  |

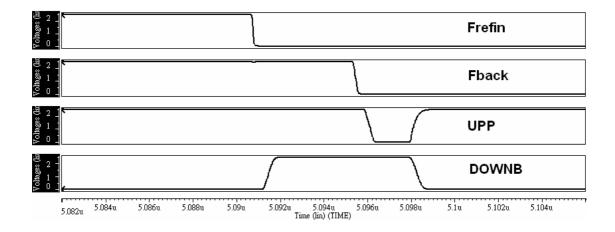

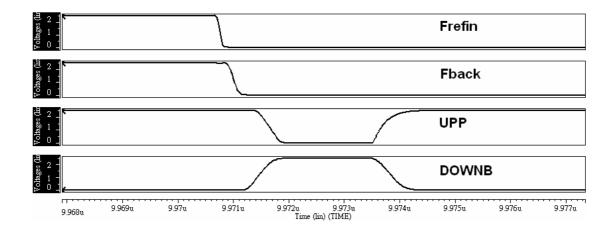

| Fig. 3.4  | The reference signal (Frefin) is earlier than the feedback signal (Fback). The  |  |

|           | output signal (UPP) is set to ground for a short duration after another output  |  |

|           | signal (DOWNB) was asserted for a while, and then both output signals     |     |

|-----------|---------------------------------------------------------------------------|-----|

| E:- 2.5   | reset to their initial states.                                            |     |

| Fig. 3.5  | The reference signal (Frefin) and the feedback signal (Fback) are in-pha  |     |

|           | Both output signals (UPP and DOWNB) are altered from their initial sta    |     |

| F: 2.6    | on every cycle in order to eliminate the dead zone region.                |     |

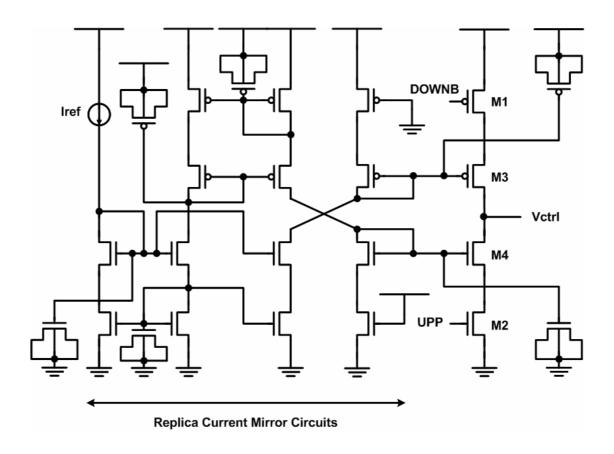

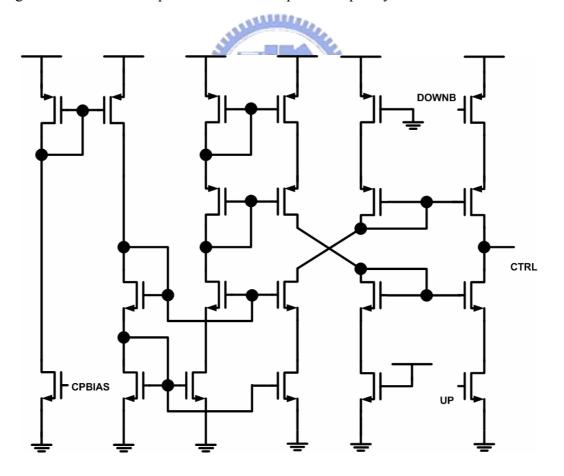

| Fig. 3.6  | The circuit implementation of the charge pump.                            |     |

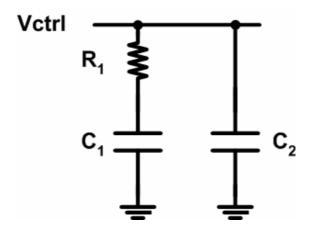

| Fig. 3.7  | Schematic of the loop filter.                                             | .52 |

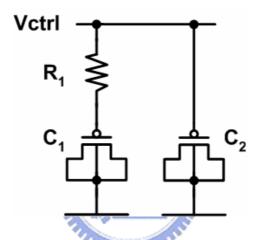

| Fig. 3.8  | The loop filter which consists of one N-well resistor and two MOS         |     |

| F: 2.0    | capacitors.                                                               | .52 |

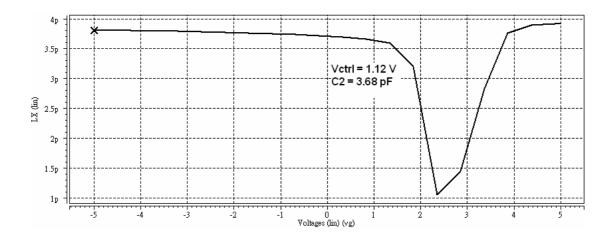

| Fig. 3.9  | Simulation of the MOS capacitor. The Vctrl is 1.12 V when the PLL is      |     |

|           | locked and the MOS capacitor $C_2$ is in the accumulation region with the |     |

| F: 2.10   | capacitor value 3.68 pF.                                                  | .52 |

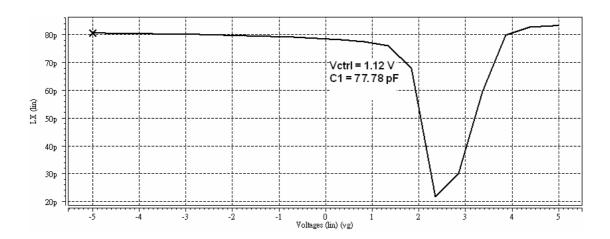

| Fig. 3.10 | Simulation of the MOS capacitor. The Vctrl is 1.12 V when the PLL is      |     |

|           | locked and the MOS capacitor $C_1$ is in the accumulation region with the |     |

| E: 0.11   | capacitor value 77.78 pF.                                                 | .53 |

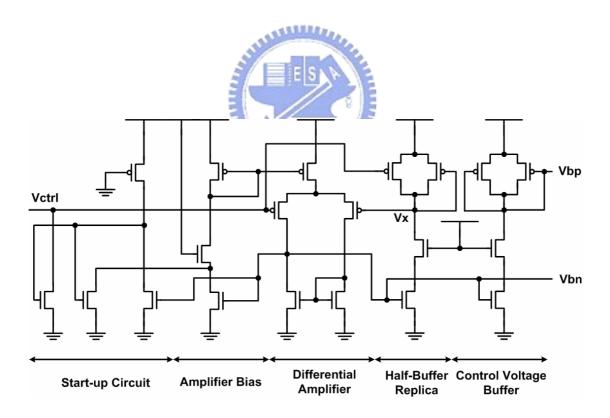

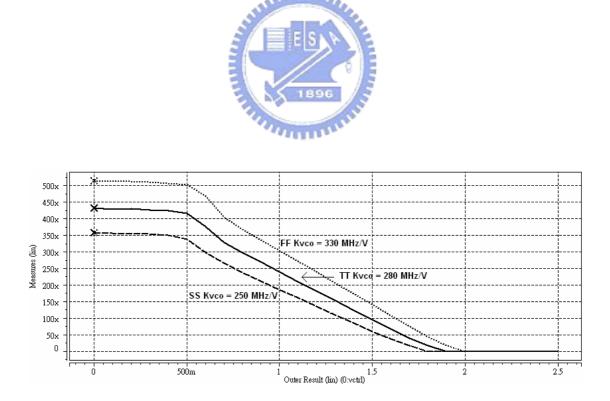

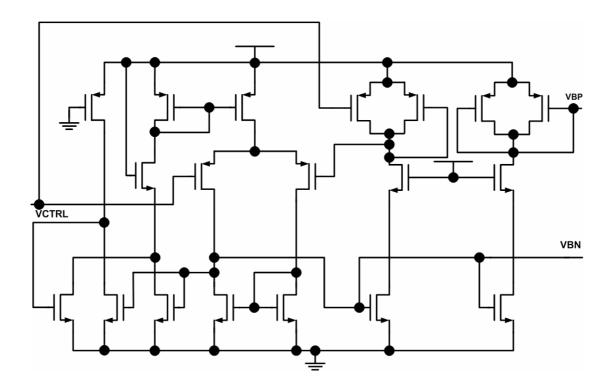

| Fig. 3.11 | The circuit implementation of the self-biased replica-feedback bias       |     |

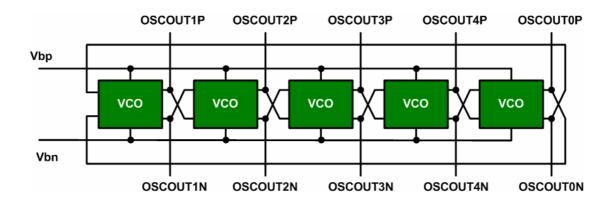

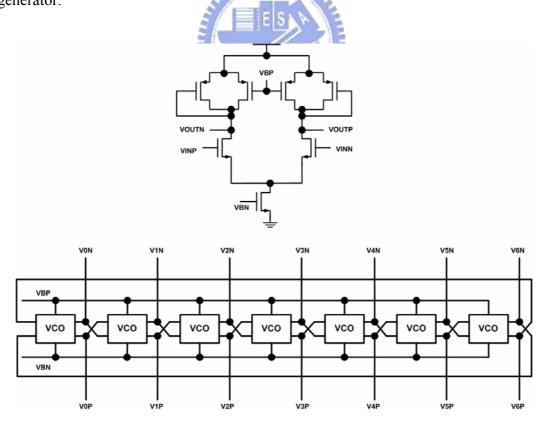

| E: 0.10   | generator.  Schematic of the five stages VCO                              | .53 |

| Fig. 3.12 |                                                                           |     |

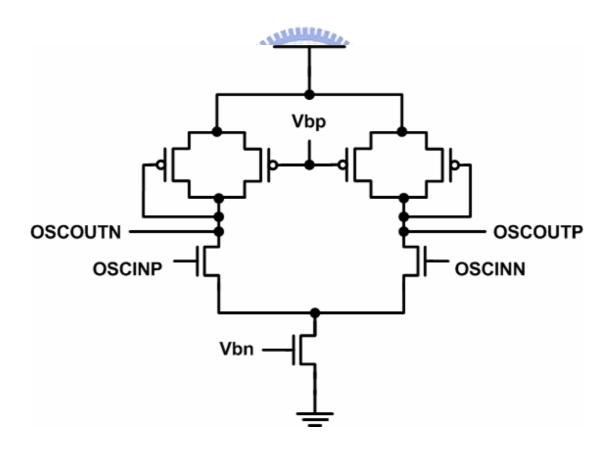

| Fig. 3.13 | The circuit implementation of the individual delay cell.                  |     |

| Fig. 3.14 | I-V curve of the symmetric load.                                          |     |

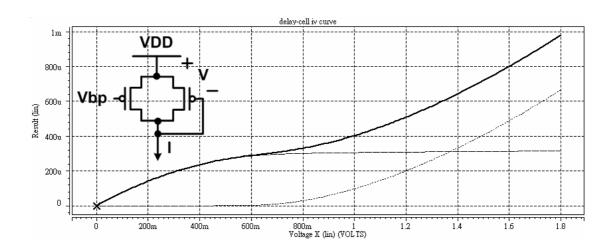

| Fig. 3.15 | Transfer curve of the VCO.                                                |     |

| Fig. 3.16 | The circuit implementation of the differential-to-single-ended converter  |     |

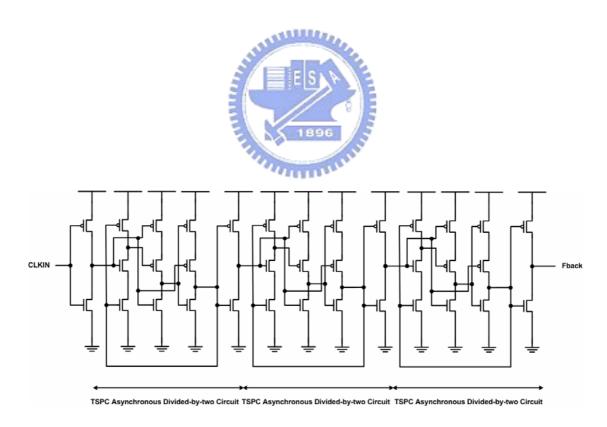

| Fig. 3.17 | The circuit implementation of the divided-by-eight divider which consists |     |

| T: 2.10   | of three divided-by-two dividers                                          |     |

| Fig. 3.18 |                                                                           |     |

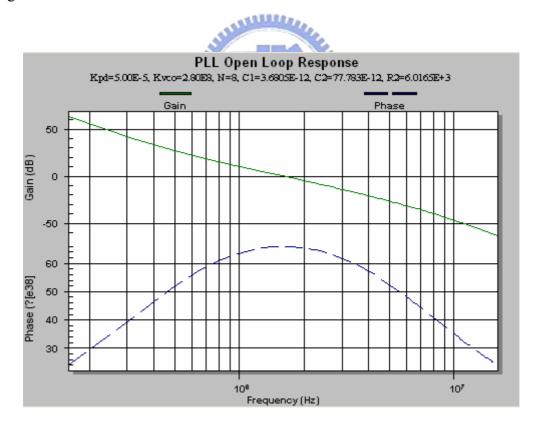

| _         | The simulation of the PLL open loop using the parameters in Table 3.1.    |     |

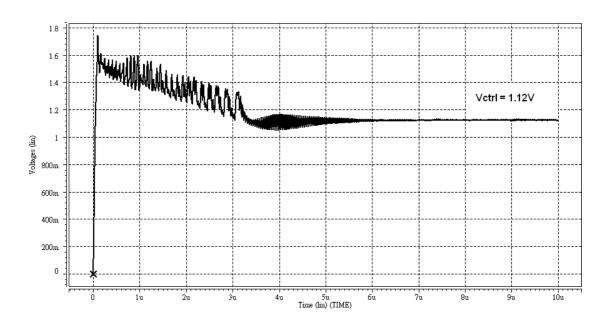

| Fig. 3.20 | The SPICE simulation of the PLL closed-loop control voltage Vctrl         |     |

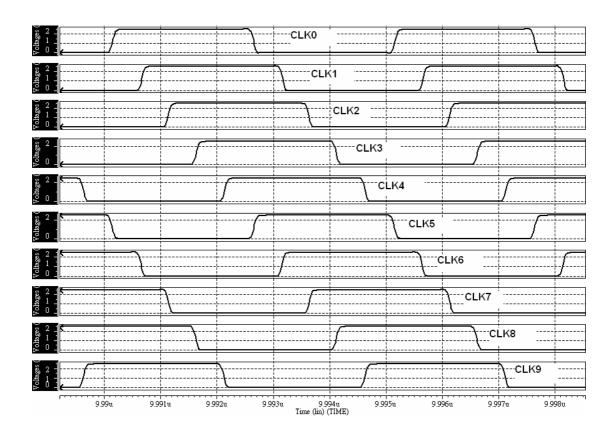

| Fig. 3.21 | The SPICE simulation of the ten even-spaced output phases of the PLL.     |     |

| Fig. 3.22 | The linear model of the PLL with different noise sources                  |     |

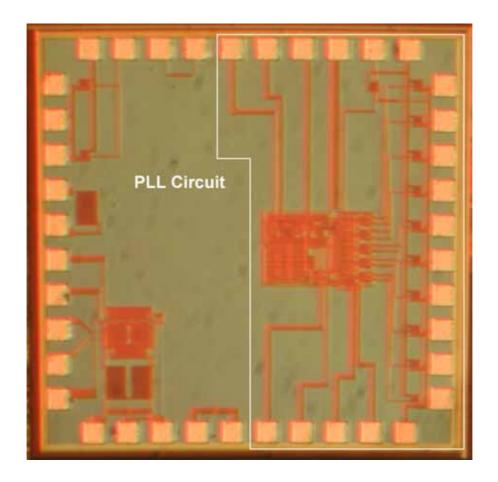

| Fig. 3.23 | The die photo of the PLL.                                                 |     |

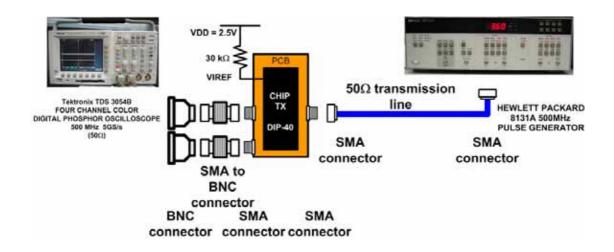

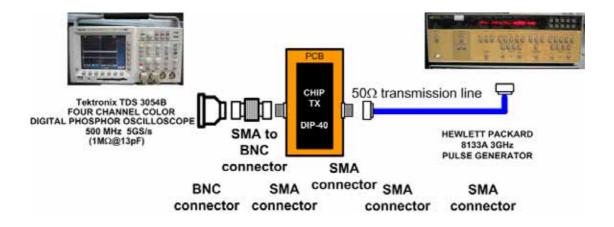

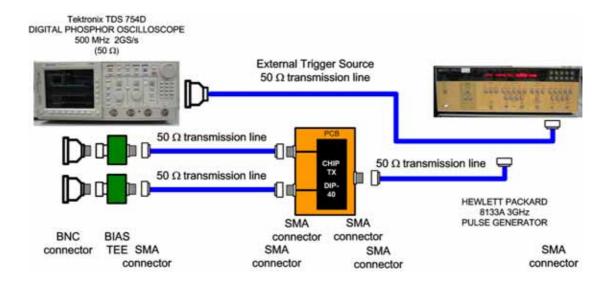

| Fig. 3.24 | The measurement setup of the PLL.                                         |     |

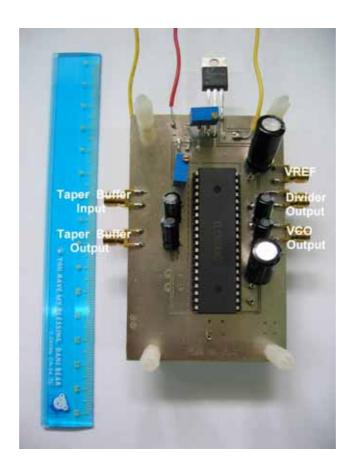

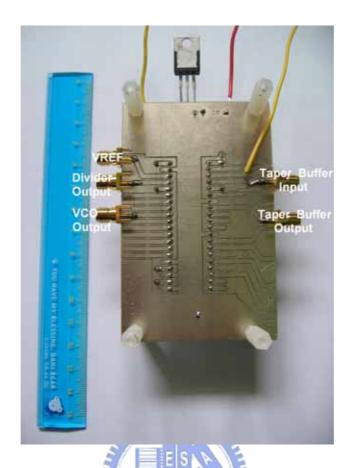

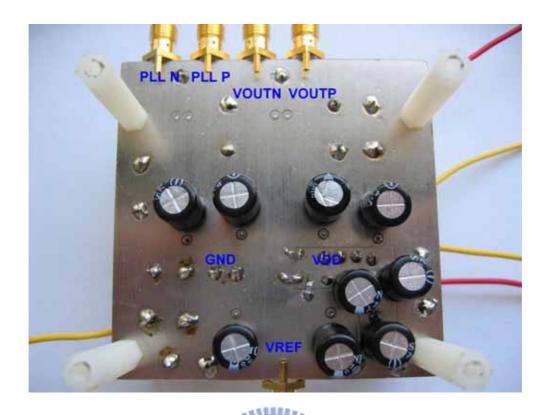

| Fig. 3.25 | The top view of the testing PCB photo.                                    |     |

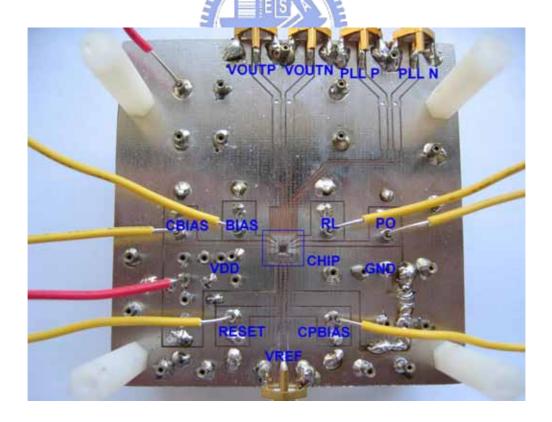

| Fig. 3.26 | The bottom view of the testing PCB photo.                                 |     |

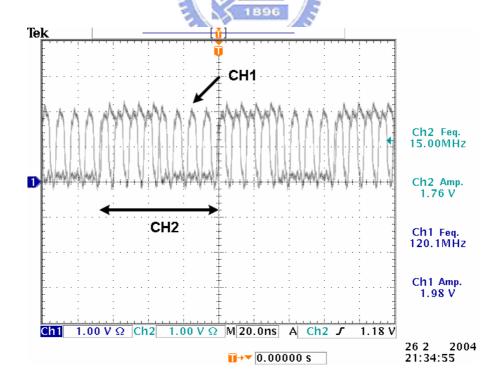

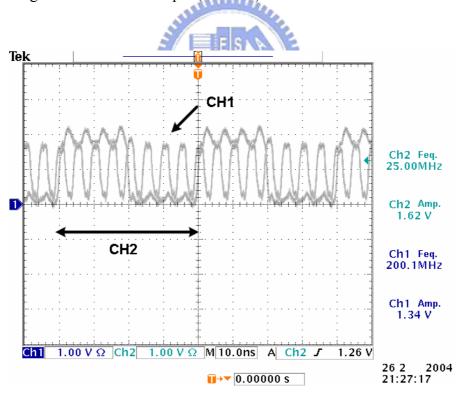

| Fig. 3.27 | Ch1 is the measured signal of the VCO output (120 MHz) and Ch2 is th      |     |

|           | measured signal of the divider output (15 MHz).                           |     |

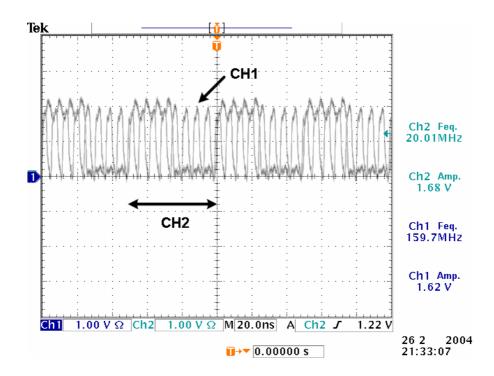

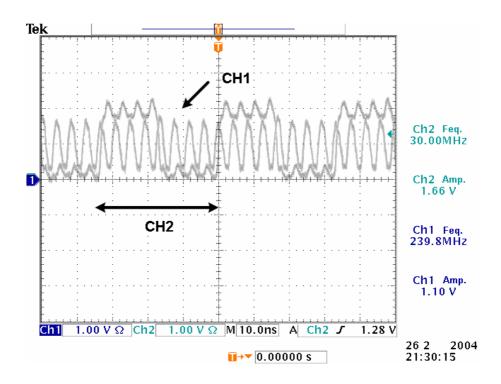

| Fig. 3.28 | Ch1 is the measured signal of the VCO output (160 MHz) and Ch2 is th      |     |

|           | measured signal of the divider output (20 MHz).                           |     |

| Fig. 3.29 | Ch1 is the measured signal of the VCO output (200 MHz) and Ch2 is th      | e   |

|           | measured signal of the divider output (25 MHz)62                               |

|-----------|--------------------------------------------------------------------------------|

| Fig. 3.30 | Ch1 is the measured signal of the VCO output (240 MHz) and Ch2 is the          |

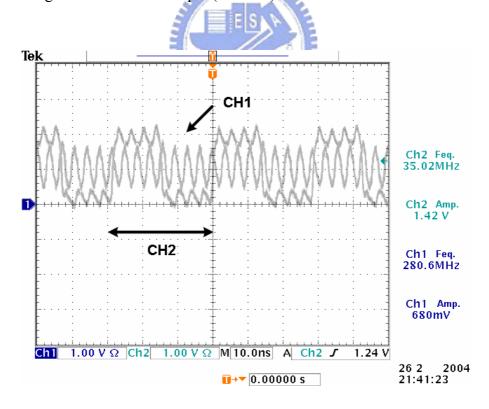

|           | measured signal of the divider output (30 MHz)63                               |

| Fig. 3.31 | Ch1 is the measured signal of the VCO output (280 MHz) and Ch2 is the          |

|           | measured signal of the divider output (35 MHz)63                               |

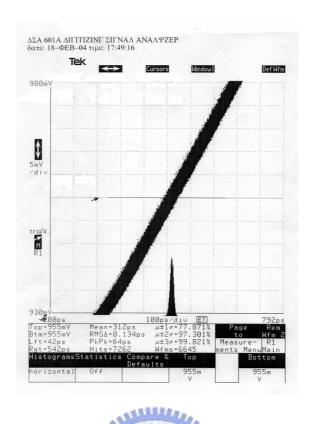

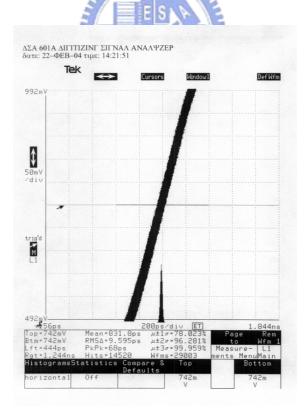

| Fig. 3.32 | The jitter histogram of the divider output signal at 25 MHz64                  |

| Fig. 3.33 | The jitter histogram of the VCO output signal at 200 MHz64                     |

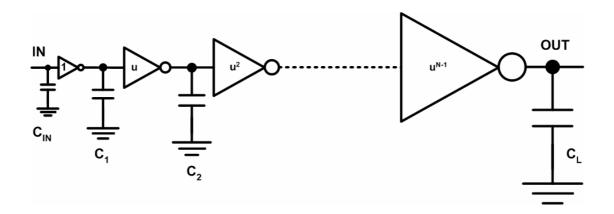

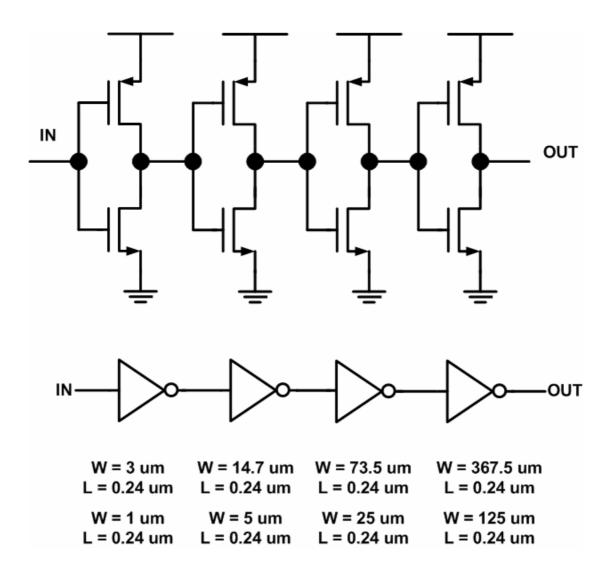

| Fig. 4.1  | Schematic of the taper buffer                                                  |

| Fig. 4.2  | The circuit design of the taper buffer76                                       |

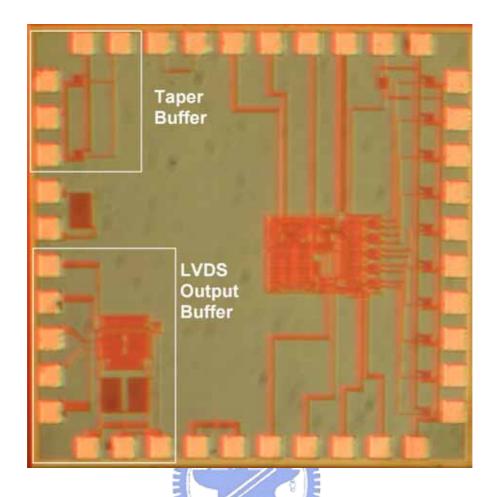

| Fig. 4.3  | The die photo of the taper buffer and the LVDS output buffer77                 |

| Fig. 4.4  | The measurement setup of the taper buffer                                      |

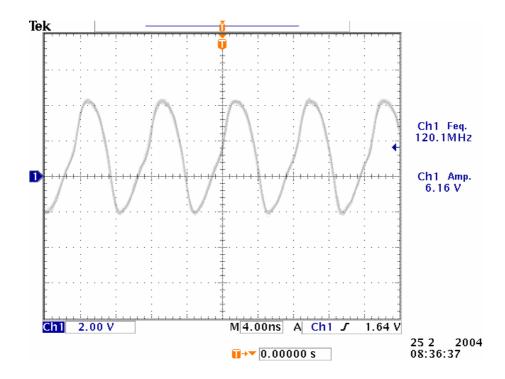

| Fig. 4.5  | The output signal of the taper buffer at 120 MHz. The capacitive loading of    |

|           | the oscilloscope is 13 pF (@1 M $\Omega$ ).                                    |

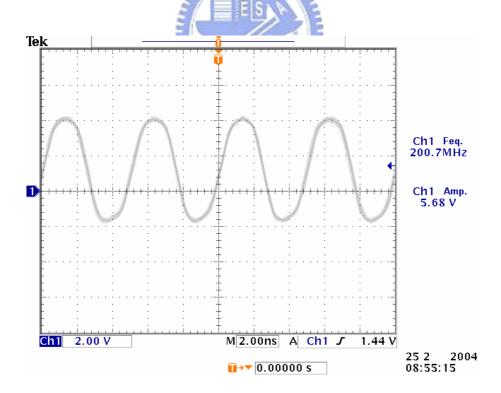

| Fig. 4.6  | The output signal of the taper buffer at 200 MHz. The capacitive loading of    |

|           | the oscilloscope is 13 pF (@1 M $\Omega$ ).                                    |

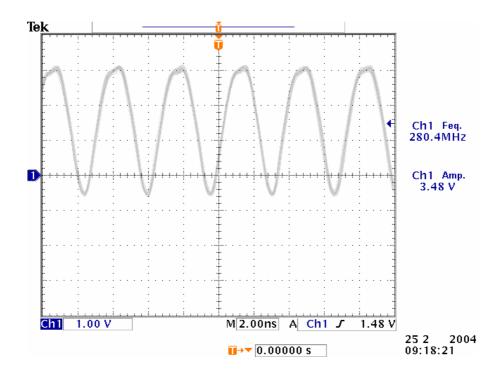

| Fig. 4.7  | The output signal of the taper buffer at 280 MHz. The capacitive loading of    |

|           | the oscilloscope is 13 pF (@1 M $\Omega$ )                                     |

| Fig. 4.8  | Schematic diagram of the LVDS output buffer                                    |

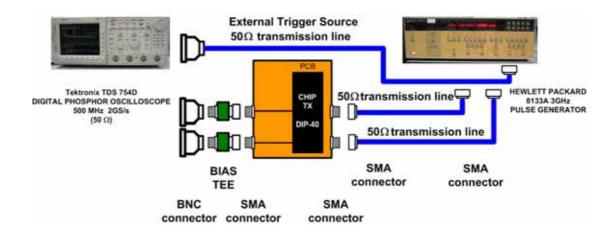

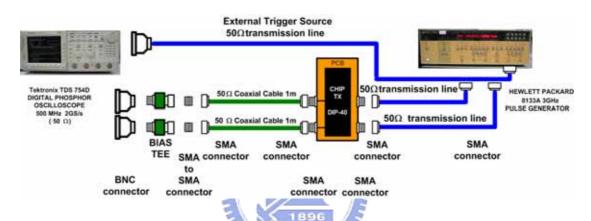

| Fig. 4.9  | The measurement setup of the LVDS output buffer                                |

| Fig. 4.10 | The measurement setup of the LVDS output buffer which uses two coaxial         |

|           | cables 80                                                                      |

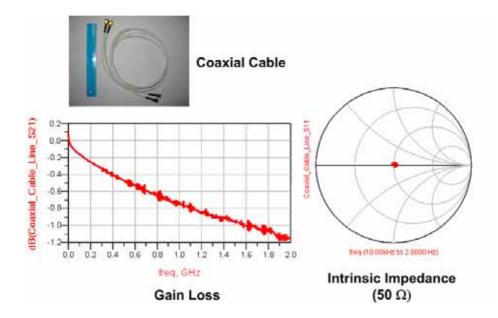

| Fig. 4.11 | Measurement of the coaxial cable80                                             |

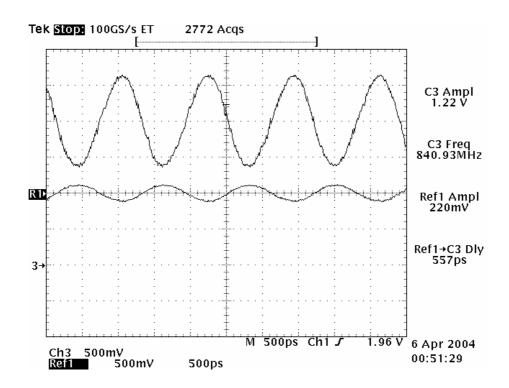

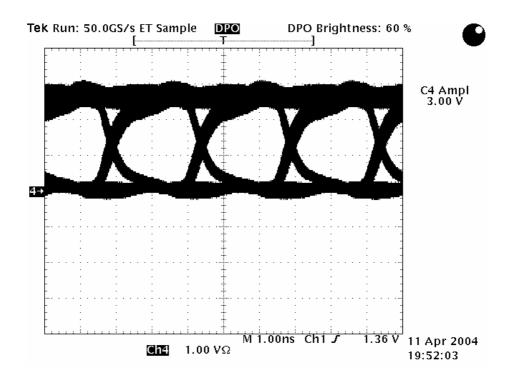

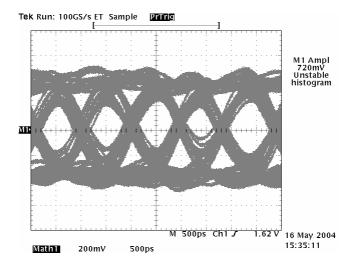

| Fig. 4.12 | The measured eye diagram of the output buffer at 840 Mb/s without coaxia       |

|           | cables. The peak-to-peak jitter is 9.19 % and the worst case jitter is 17 %.   |

|           | 81                                                                             |

| Fig. 4.13 | The measured eye diagram of the output buffer at 840 Mb/s with coaxial         |

|           | cables. The peak-to-peak jitter is 10.5 % and the worst case jitter is 21.5 %  |

|           | 81                                                                             |

| Fig. 4.14 | The measured eye diagram of the output buffer at 1.2 Gb/s without coaxial      |

|           | cables. The peak-to-peak jitter is 18.75 % and the worst case jitter is 30 %.  |

|           | 82                                                                             |

| Fig. 4.15 | The measured eye diagram of the output buffer at 1.2 Gb/s with coaxial         |

|           | cables. The peak-to-peak jitter is 23.25 % and the worst case jitter is 35.6 % |

|           | 82                                                                             |

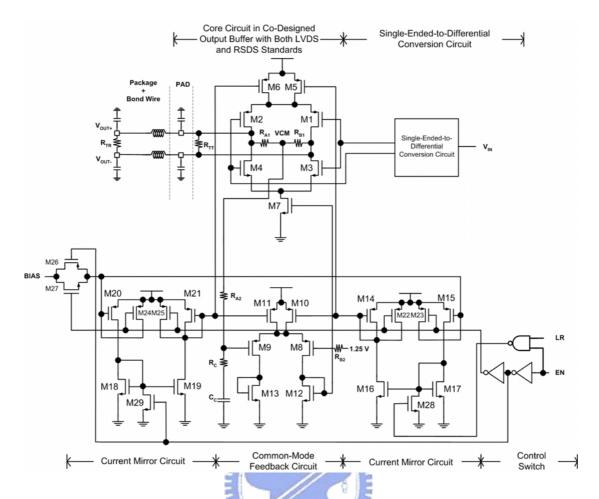

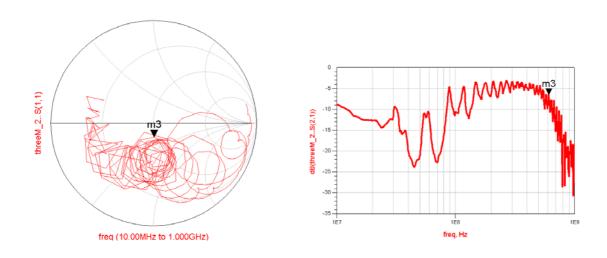

| Fig. 4.16 |                                                                                |

| -         | RSDS standards.                                                                |

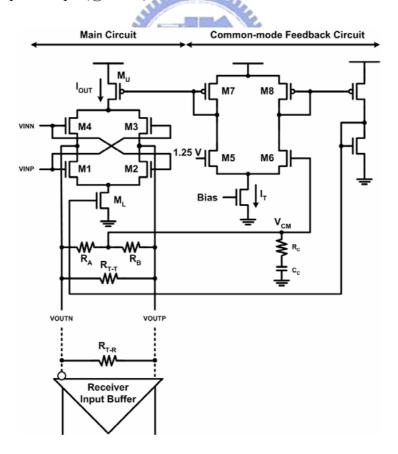

| Fig. 4.17 |                                                                                |

| Č         | circuit 83                                                                     |

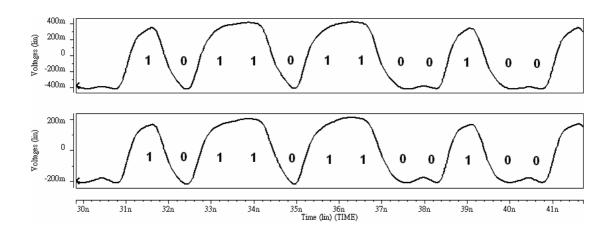

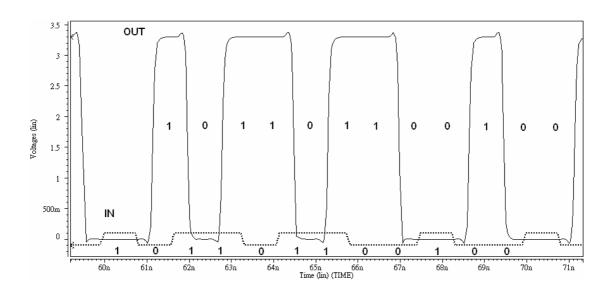

| Fig. 4.18 | Simulation of both LVDS standard (top) and RSDS standard (bottom)                               |

|-----------|-------------------------------------------------------------------------------------------------|

|           | output voltage swings with a 101101100100 input pattern transmitted at 1.2                      |

|           | Gb/s84                                                                                          |

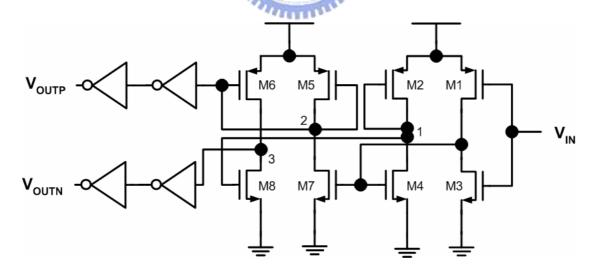

| Fig. 4.19 | Schematic diagram of the co-designed receiver input buffer with both                            |

|           | LVDS and RSDS standards. 84                                                                     |

| Fig. 4.20 | Simulation of the co-designed receiver input buffer at 1.2 Gb/s. The dotted                     |

|           | line is a 101101100100 differential input pattern provided to the input                         |

|           | buffer. The solid line is a recovered single full-swing output pattern85                        |

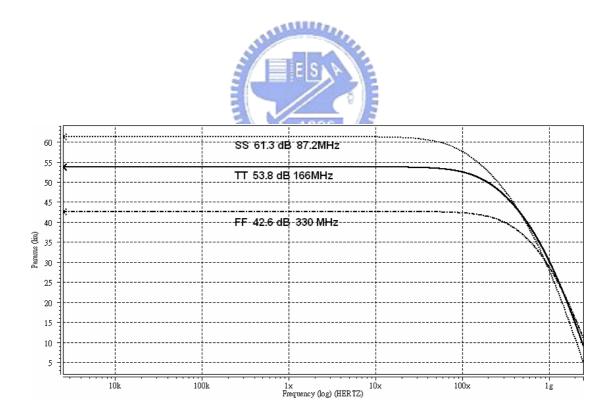

| Fig. 4.21 | AC response of the receiver input buffer                                                        |

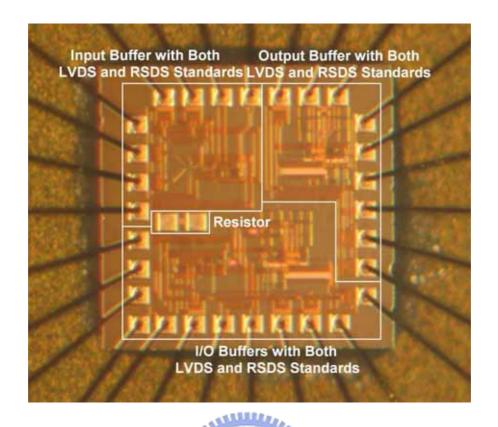

| Fig. 4.22 | The die photo of the co-designed I/O buffers86                                                  |

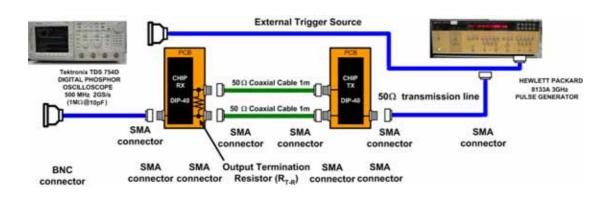

| Fig. 4.23 | The measurement setup of the co-designed I/O buffers                                            |

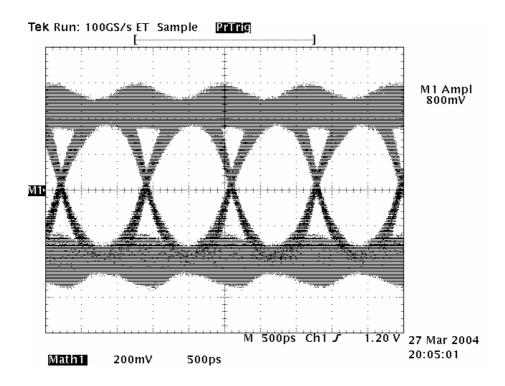

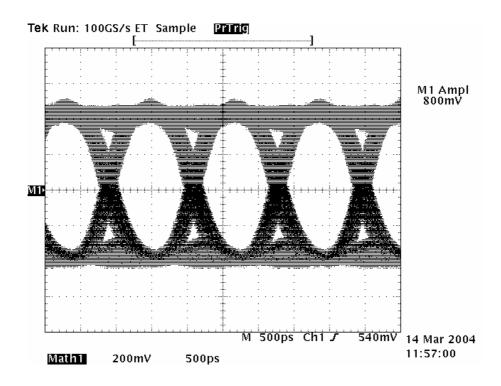

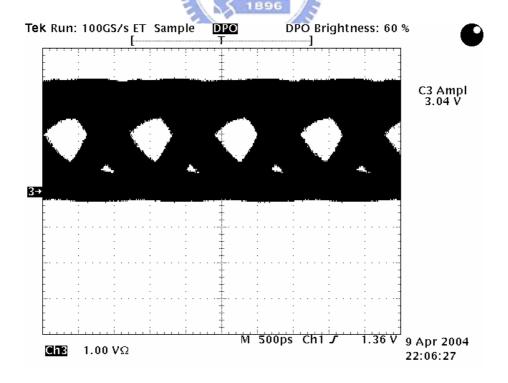

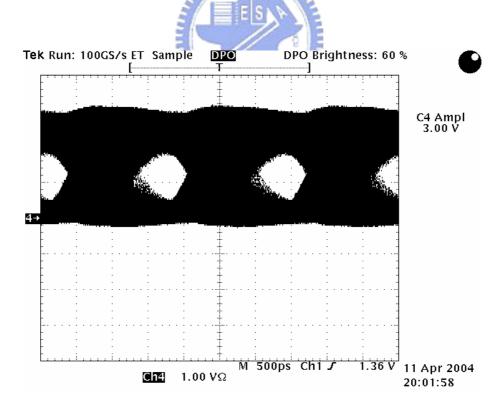

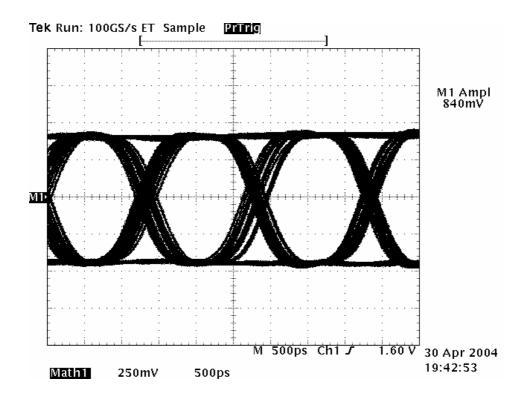

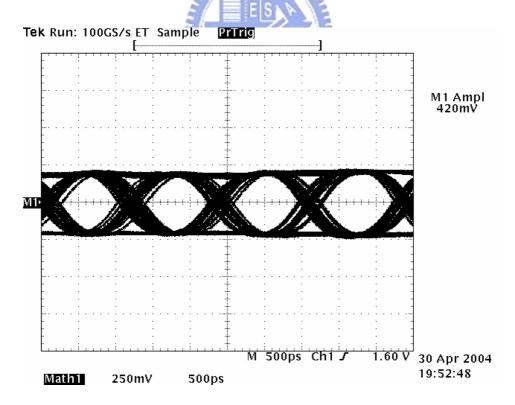

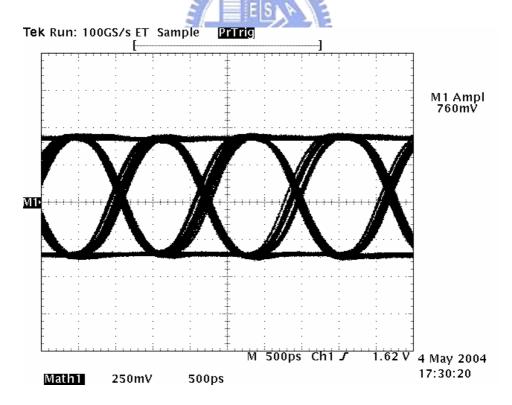

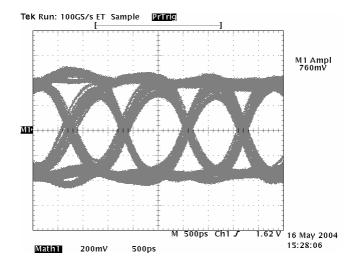

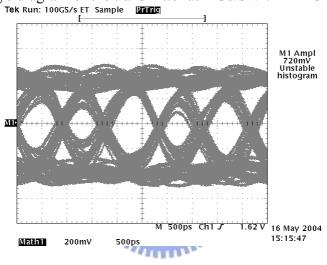

| Fig. 4.24 | The measured eye diagram of the output buffer operating in the LVDS                             |

|           | standard at 840 Mbps with 2 <sup>23</sup> -1 PRBS. The measured power consumption               |

|           | is 42 mW. The peak-to-peak jitter is 23.6 %                                                     |

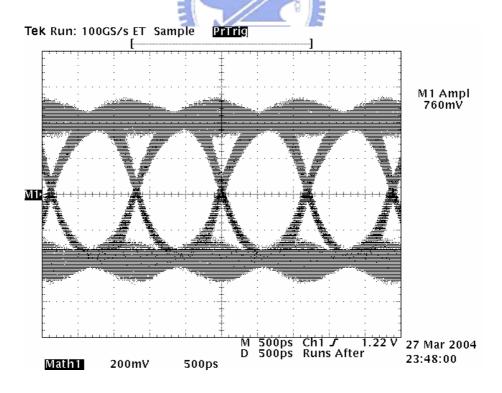

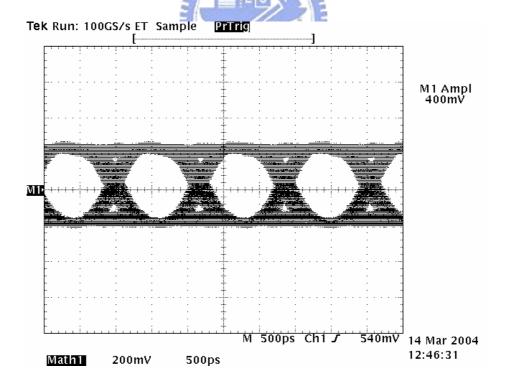

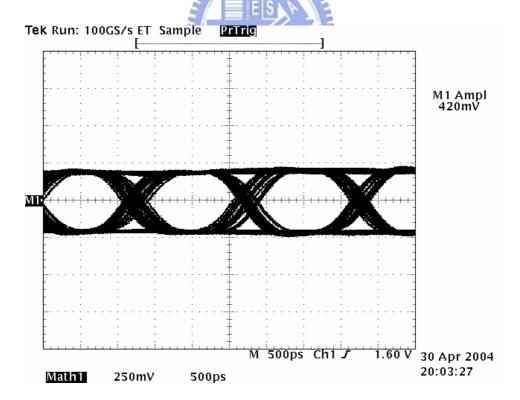

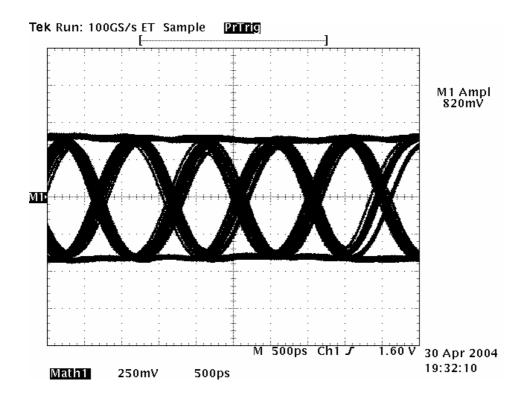

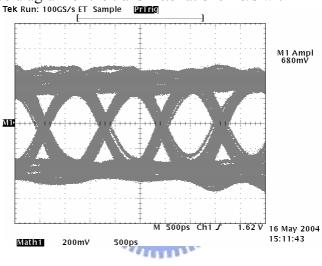

| Fig. 4.25 | The measured eye diagram of the output buffer operating in the RSDS                             |

|           | standard at 840 Mbps with 2 <sup>23</sup> -1 PRBS. The measured power consumption               |

|           | is 28 mW. The peak-to-peak jitter is 26.26 %                                                    |

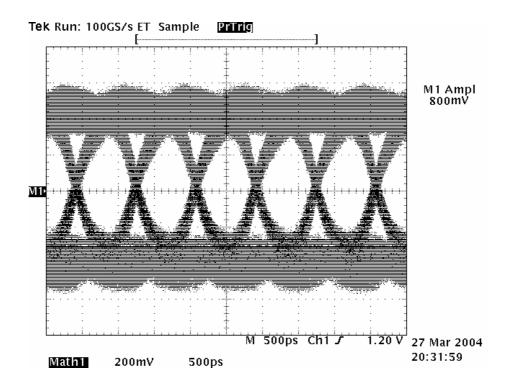

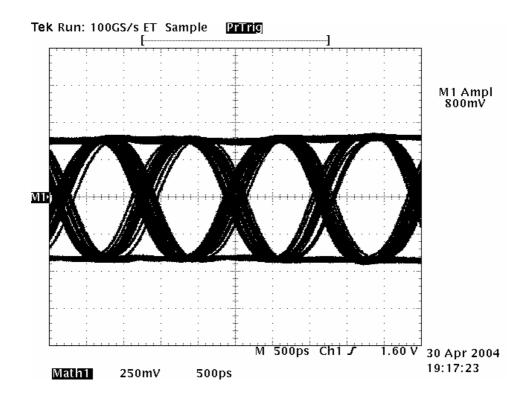

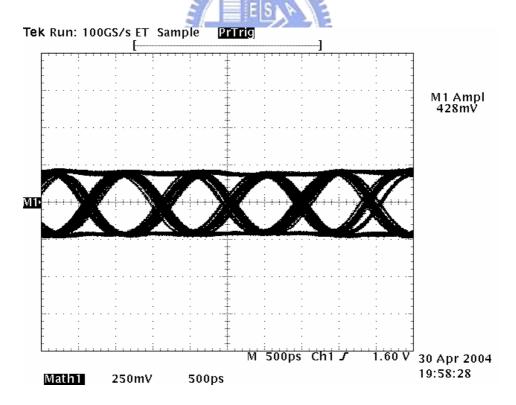

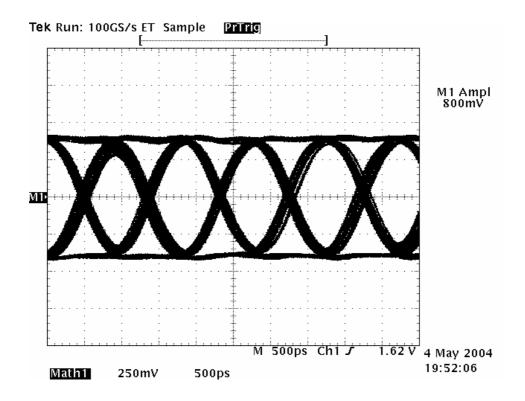

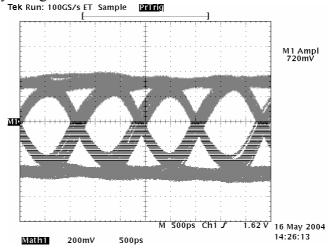

| Fig. 4.26 | The measured eye diagram of the output buffer operating in the LVDS                             |

|           | standard at 1.2 Gbps with 2 <sup>23</sup> -1 PRBS. The measured power consumption is            |

|           | 44 mW. The peak-to-peak jitter is 33.75 %                                                       |

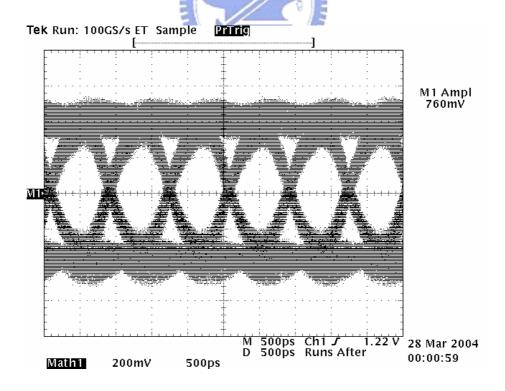

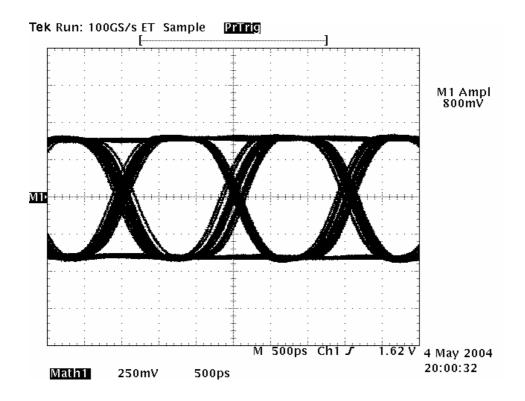

| Fig. 4.27 | The measured eye diagram of the output buffer operating in the RSDS at 1.2                      |

|           | Gbps with 2 <sup>23</sup> -1 PRBS. The measured power consumption is 30 mW. The                 |

|           | peak-to-peak jitter is 37.5 %                                                                   |

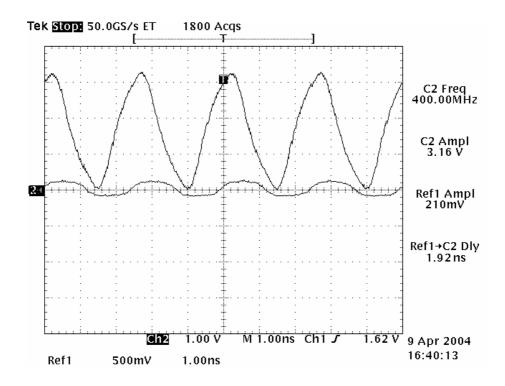

| Fig. 4.28 | The measured output signal of the receiver input buffer at 400 MHz. The                         |

|           | output signal is a single-ended full-swing signal with 50 % duty cycle and                      |

|           | the input differential signal is at the worst case ( $V_{OD} = \pm 100 \text{ mV}$ ) defined in |

|           | LVDS and RSDS standards89                                                                       |

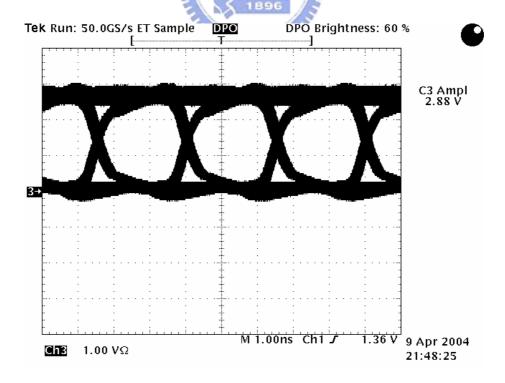

| Fig. 4.29 | The measured eye diagram of the receiver input buffer at 400 Mb/s. The                          |

|           | peak-to-peak jitter is 12.94 %                                                                  |

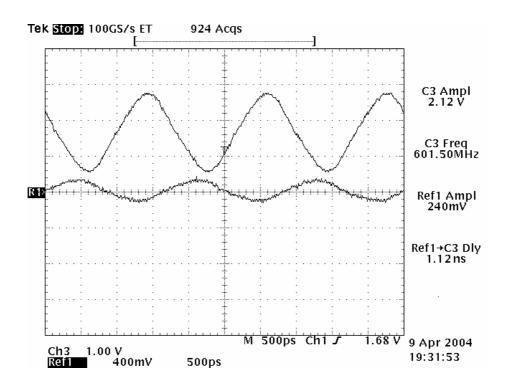

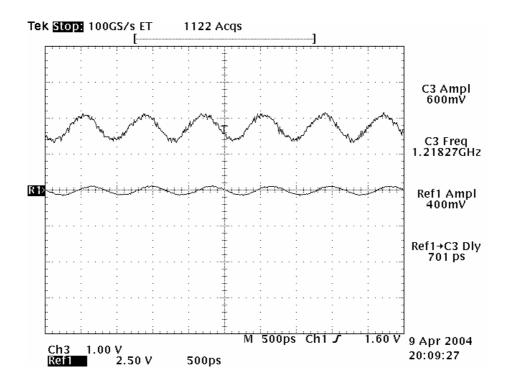

| Fig. 4.30 | The measured output signal of the receiver input buffer at 600 MHz. The                         |

|           | output signal is a single-ended full-swing signal with 50 % duty cycle and                      |

|           | the input differential signal is at the worst case ( $V_{OD} = \pm 100 \text{ mV}$ ) defined in |

|           | LVDS and RSDS standards90                                                                       |

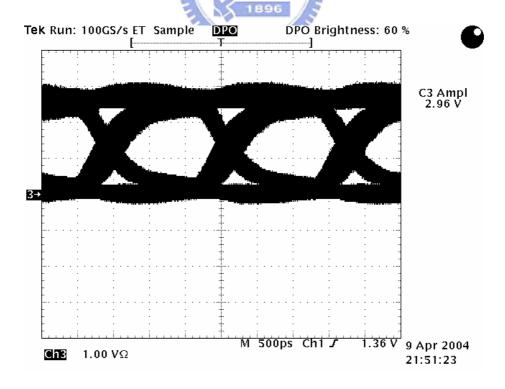

| Fig. 4.31 | The measured eye diagram of the receiver input buffer at 600 Mb/s. The                          |

|           | peak-to-peak jitter is 26.47 %90                                                                |

| Fig. 4.32 | The measured output signal of the receiver input buffer at 840 MHz. The                         |

|           | output signal is a single-ended full-swing signal with 50 % duty cycle and                      |

|           | the input differential signal is at the worst case ( $V_{OD} = \pm 100 \text{ mV}$ ) defined in |

|           | LVDS and RSDS standards91                                                                       |

|-----------|-------------------------------------------------------------------------------------------------|

| Fig. 4.33 | The measured eye diagram of the receiver input buffer at 840 Mb/s. The                          |

|           | peak-to-peak jitter is 48.2 %91                                                                 |

| Fig. 4.34 | The measured output signal of the receiver input buffer at 1.2 GHz. The                         |

|           | output signal is a single-ended full-swing signal with 50 % duty cycle and                      |

|           | the input differential signal is at the worst case ( $V_{OD} = \pm 100 \text{ mV}$ ) defined in |

|           | LVDS and RSDS standards92                                                                       |

| Fig. 4.35 | The measured eye diagram of the I/O buffers which are connected together                        |

|           | via two coaxial cables at 300 Mb/s. The peak-to-peak jitter is 12.8 %92                         |

| Fig. 4.36 | The measured eye diagram of the I/O buffers which are connected together                        |

|           | via two coaxial cables at 400 Mb/s. The peak-to-peak jitter is 13.7 %93                         |

| Fig. 4.37 | The measured eye diagram of the I/O buffers which are connected together                        |

|           | via two coaxial cables at 600 Mb/s. The peak-to-peak jitter is 58.2 %93                         |

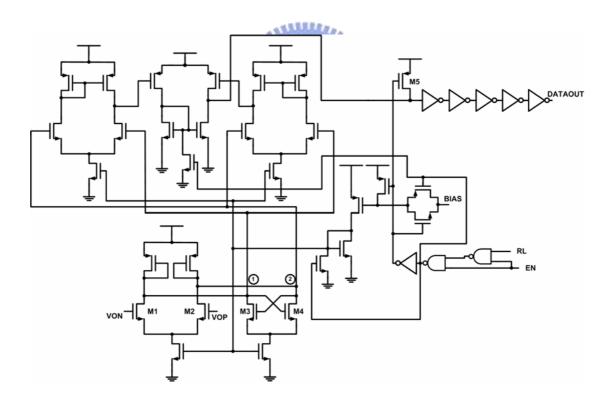

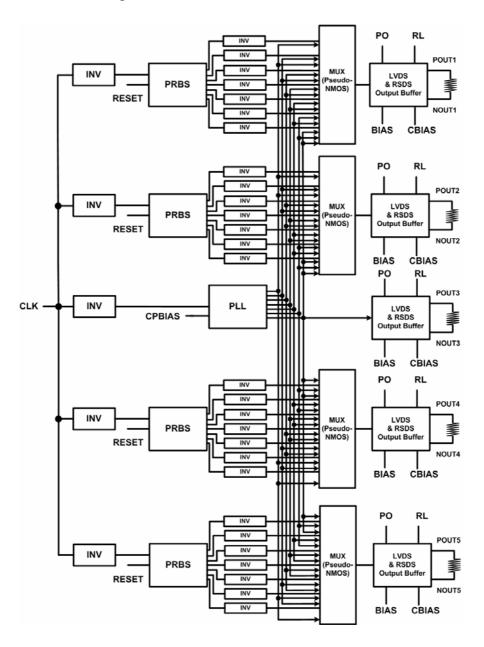

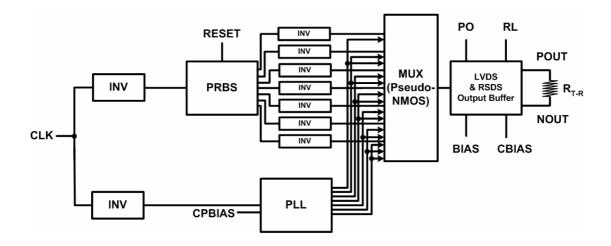

| Fig. 5.1  | The block diagram of the transmitter                                                            |

| Fig. 5.2  | The more detail circuit blocks of the transmitter                                               |

| Fig. 5.3  | The circuit block of the transmitter which converts seven parallel TTL data                     |

|           | to one serial LVDS or RSDS data stream. 101                                                     |

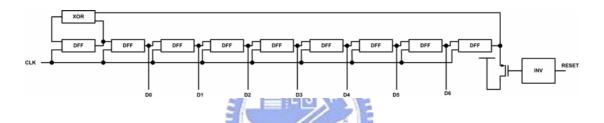

| Fig. 5.4  | The circuit implementation of the pseudo random binary sequence (PRBS).                         |

|           |                                                                                                 |

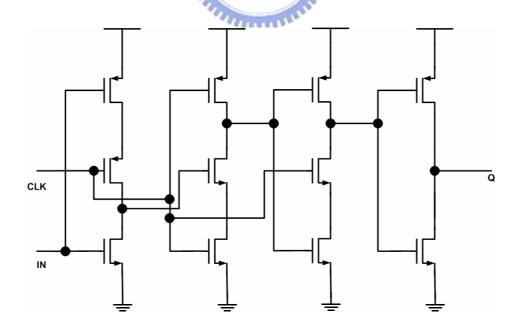

| Fig. 5.5  | The circuit implementation of the positive edge-triggered D-type flip-flop                      |

|           | using true single-phase clock logic (TSPC)                                                      |

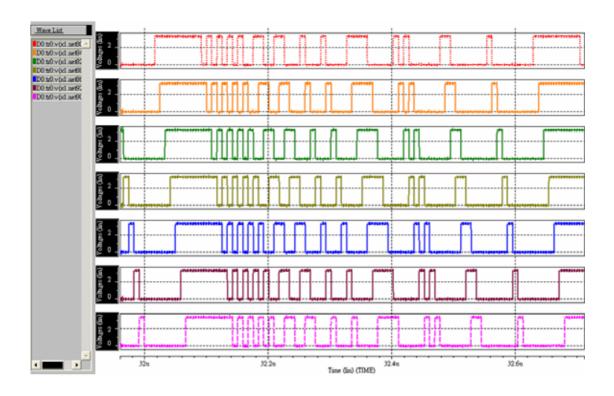

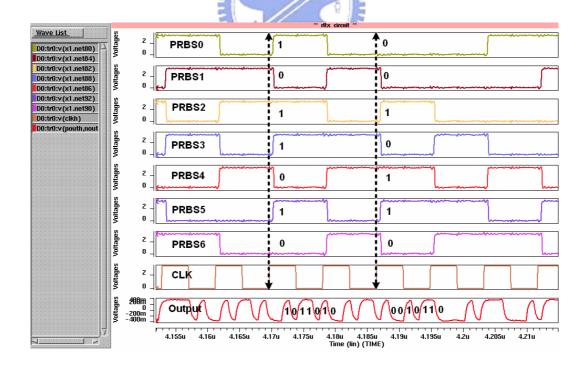

| Fig. 5.6  | The simulated patterns of the pseudo random binary sequence (PRBS). 102                         |

| Fig. 5.7  | The architecture of the PLL which is used in the transmitter                                    |

| Fig. 5.8  | The circuit implementation of the phase frequency detector                                      |

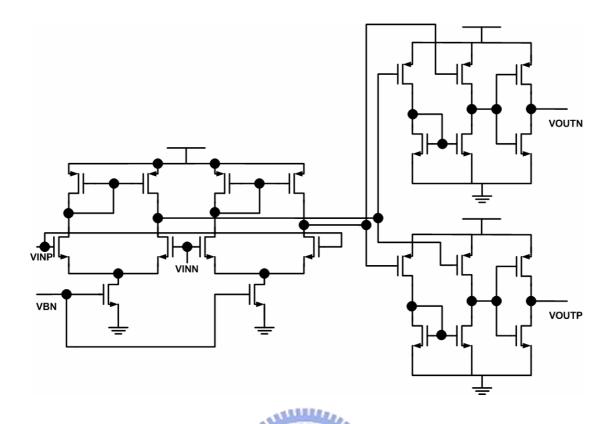

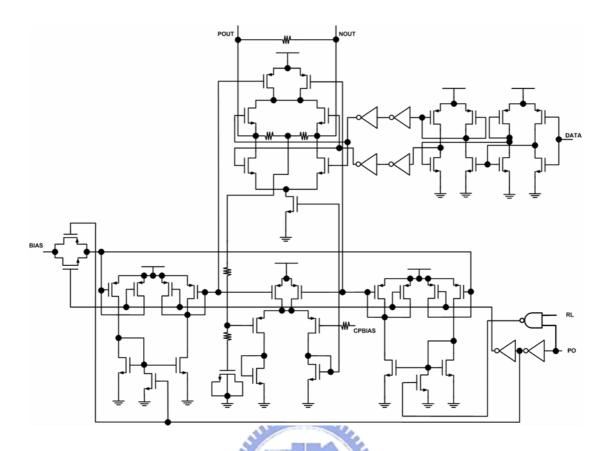

| Fig. 5.9  | The circuit implementation of the charge pump                                                   |

| Fig. 5.10 | The circuit implementation of the self-biased replica-feedback bias                             |

|           | generator. 104                                                                                  |

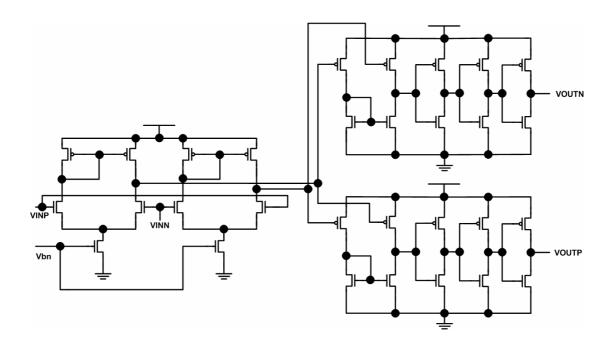

| Fig. 5.11 | The circuit implementation of the voltage-controlled oscillator104                              |

| Fig. 5.12 | The circuit implementation of the differential-to-single-ended converter                        |

|           |                                                                                                 |

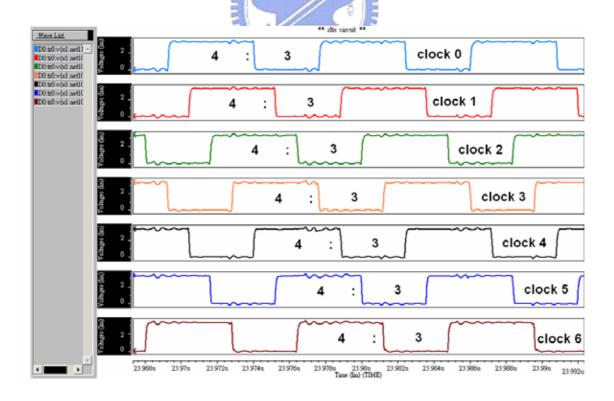

| Fig. 5.13 | The simulated seven output clocks with four to three duty cycle of the PLL.                     |

|           |                                                                                                 |

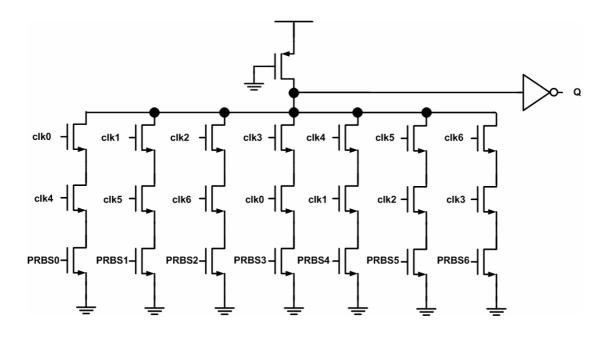

| Fig. 5.14 | The circuit implementation of the multiplexer                                                   |

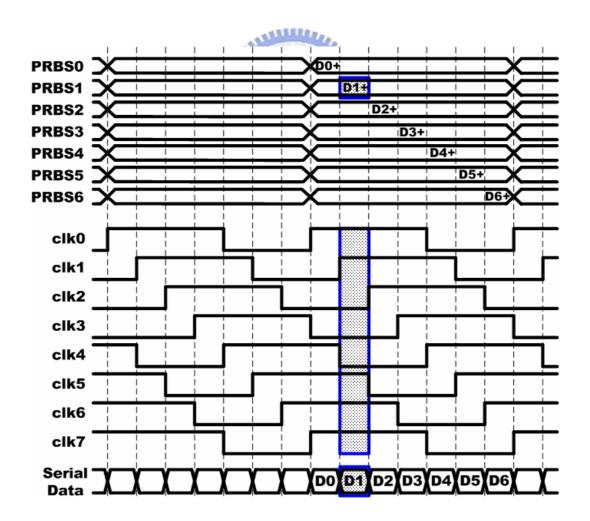

| Fig. 5.15 | The timing diagram of the multiplexer. 106                                                      |

| Fig. 5.16 | The circuit implementation of the co-designed output buffer107                                  |

| Fig. 5.17 | The parallel to serial conversion of the seven parallel PRBS data to one                        |

|           | serial LVDS data stream. 107                                                                    |

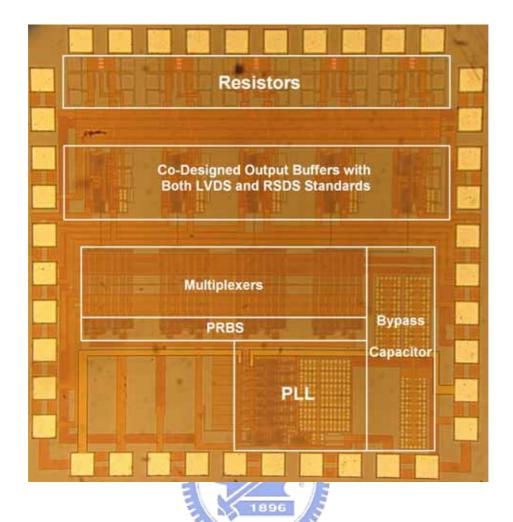

| Fig. 5.18 | Photograph of the transmitter in a 0.25-µm 1P5M 3.3-V CMOS process                              |

|           | 10                                                                        |

|-----------|---------------------------------------------------------------------------|

| Fig. 5.19 | Measurement setup of the transmitter                                      |

| Fig. 5.20 | The top view of the testing PCB photo for the transmitter                 |

| Fig. 5.21 | The bottom view of the testing PCB photo for the transmitter10            |

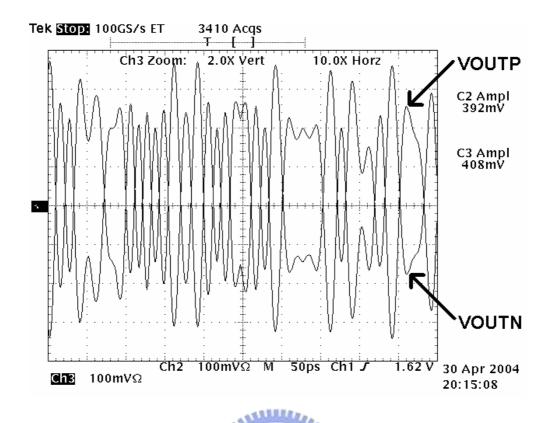

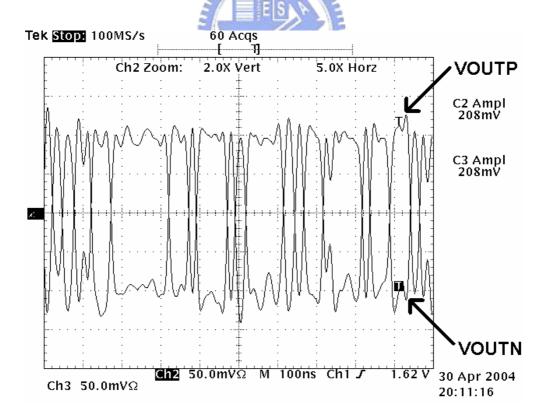

| Fig. 5.22 | The differential output signals of the transmitter in the LVDS mode11     |

| Fig. 5.23 | The differential output signals of the transmitter in the RSDS mode11     |

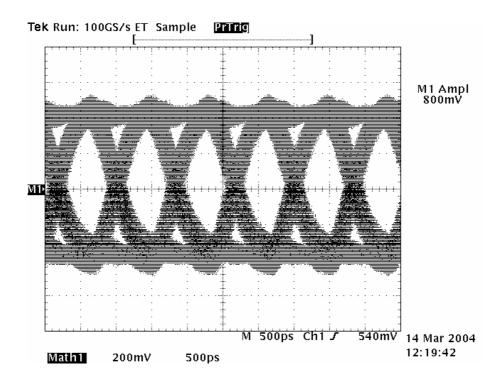

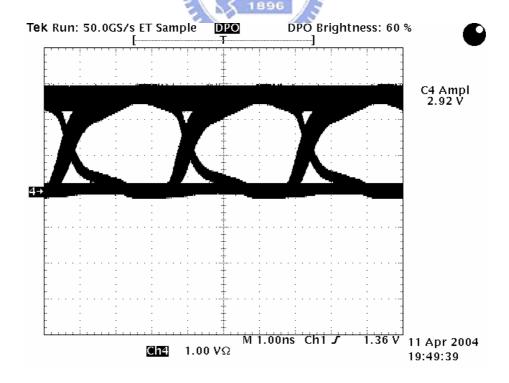

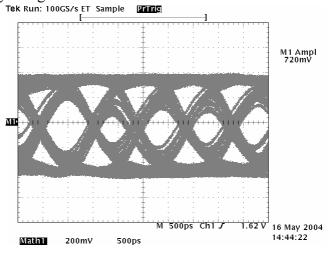

| Fig. 5.24 | The measured eye diagram of the transmitter at 700 Mb/s with package. Th  |

|           | peak-to-peak jitter is 24 %. The transmitter is in the LVDS mode11        |

| Fig. 5.25 | The measured eye diagram of the transmitter at 700 Mb/s with package. Th  |

|           | peak-to-peak jitter is 25.15 %. The transmitter is in the LVDS mode 11    |

| Fig. 5.26 | The measured eye diagram of the transmitter at 840 Mb/s with package. Th  |

|           | peak-to-peak jitter is 31.5 %. The transmitter is in the LVDS mode11      |

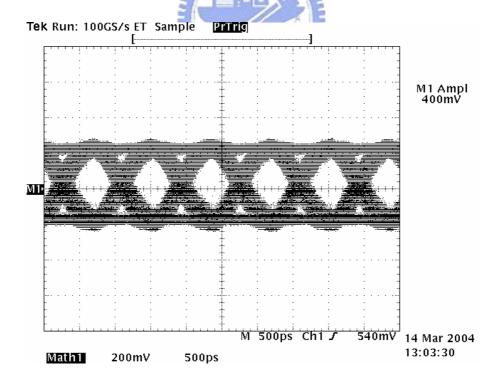

| Fig. 5.27 | The measured eye diagram of the transmitter at 840 Mb/s with package. Th  |

|           | peak-to-peak jitter is 32.8 %. The transmitter is in the RSDS mode 11     |

| Fig. 5.28 | The measured eye diagram of the transmitter at 1.05 Gb/s with package. Th |

|           | peak-to-peak jitter is 26.25 %. The transmitter is in the LVDS mode11     |

| Fig. 5.29 | The measured eye diagram of the transmitter at 1.05 Gb/s with package. Th |

|           | peak-to-peak jitter is 27.89 %. The transmitter is in the LVDS mode 11    |

| Fig. 5.30 | The measured eye diagram of the transmitter at 700 Mb/s without package   |

|           | The peak-to-peak jitter is 21.87 %. The transmitter is in the LVDS mode.  |

|           | 11                                                                        |

| Fig. 5.31 | The measured eye diagram of the transmitter at 840 Mb/s without package   |

|           | The peak-to-peak jitter is 18.4 %. The transmitter is in the LVDS mode.   |

|           |                                                                           |

| Fig. 5.32 | The measured eye diagram of the transmitter at 1.05 Gb/s without package  |

|           | The peak-to-peak jitter is 19.7 %. The transmitter is in the LVDS mode.   |

|           | 11                                                                        |

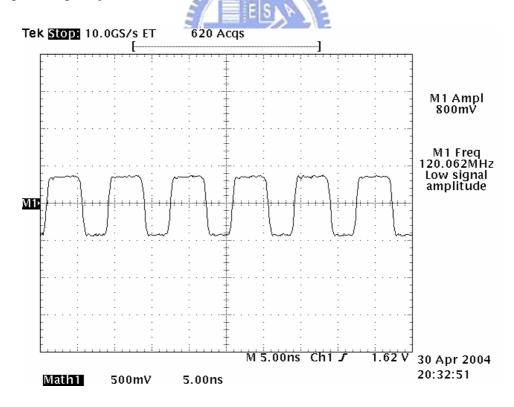

| Fig. 5.33 | The measured output clock of the PLL at 120 MHz with package. The dut     |

|           | cycle of the output clock is almost four to three                         |

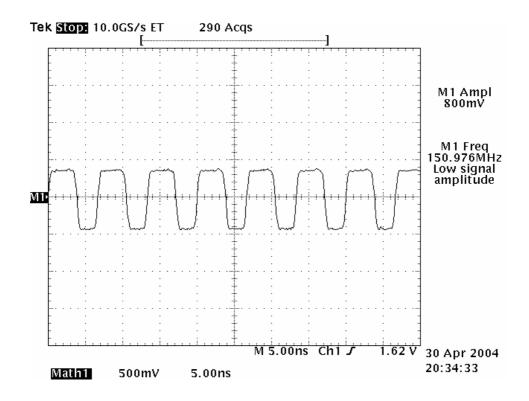

| Fig. 5.34 | The measured output clock of the PLL at 150 MHz with package. The dut     |

|           | cycle of the output clock is almost four to three                         |

| Fig. 5.35 | The jitter histogram of the PLL output clock at 120 MHz. The long term    |

| C         | peak-to-peak jitter is 88 ps                                              |

| Fig. 5.36 | The measurement setup of the transmitter with a 3-meter long UTP Cat.6    |

| C         | line                                                                      |

| Fig. 5.37 |                                                                           |

| Č         | boards11                                                                  |

| Fig. 5.38 | The eye diagram of the transmitter at 840Mb/s with 1-m UTP Cat.6 line     |

|           |                                                                        | 118 |

|-----------|------------------------------------------------------------------------|-----|

| Fig. 5.39 | The eye diagram of the transmitter at 840Mb/s with 2-m UTP Cat.6 line  |     |

|           |                                                                        | 118 |

| Fig. 5.40 | The eye diagram of the transmitter at 840Mb/s with 3-m UTP Cat.6 line  |     |

|           |                                                                        | 118 |

| Fig. 5.41 | The eye diagram of the transmitter at 1 Gb/s with 1-m UTP Cat.6 line.  | 119 |

| Fig. 5.42 | The eye diagram of the transmitter at 1 Gb/s with 2-m UTP Cat.6 line   | 119 |

| Fig. 5.43 | The eye diagram of the transmitter at 1 Gb/s with 3-m UTP Cat.6 line   | 119 |

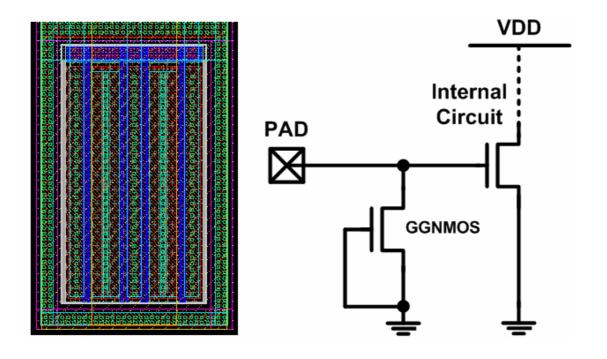

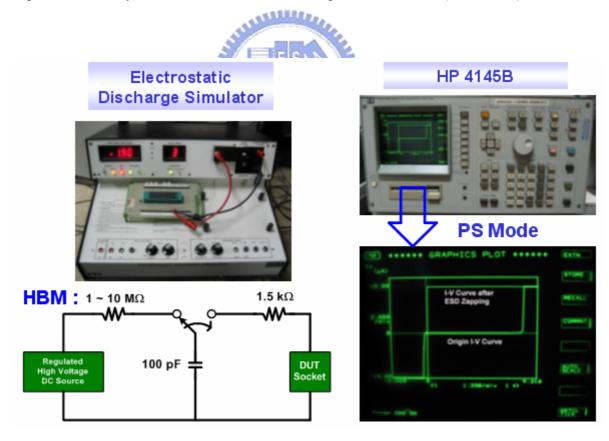

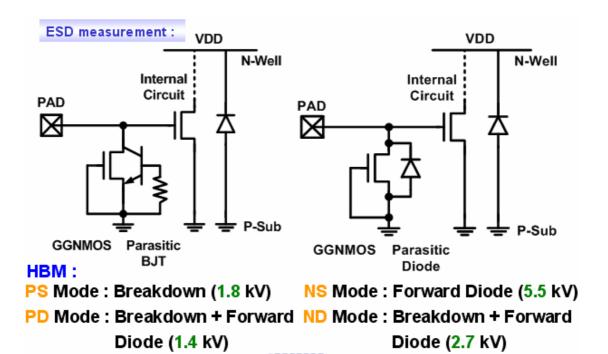

| Fig. 5.44 | The layout and schematic of the ESD protection circuit (GGNMOS)        | 120 |

| Fig. 5.45 | The measurement setup of the ESD testing. The ESD testing model is the | ne  |

|           | human body model (HBM)                                                 | 120 |

| Fig. 5.46 | The measurement results of the ESD testing.                            | 121 |

# **Chapter 1**

# Introduction

#### 1.1 MOTIVATION

With the rapid technology scaling and increasing operation frequencies, the internal clock frequency in microprocessors is up to gigabits-per-second range. However, unlike internal clocks, chip-to-chip or chip-to-board signaling gains little benefit in terms of operating frequency from the increased silicon integration. It means that the biggest bottleneck for designing the ever-increasing processing speed of microprocessor motherboards, optical transmission links, flat panel display systems, intelligent hubs and routers, etc., is the I/O interface transmission between chips to chips or chips to boards.

In the last decade, high-speed I/O interfaces were achieved by massive parallelism with the disadvantages of increased complexity and cost for the IC package and the printed circuit board (PCB). However, such method also consumes huge power and induces unavoidable electro-magnetic interference (EMI) during signal transmission [1]. In order to save power, area and cost, the number of I/O pads in systems should be reduced. Therefore, parallel-based technologies need to be changed to serial-based technologies.

The serial link technology can lower the numbers of transmission lines to decrease power, volumes, cost and EMI. The population applications are optical communication, USB, IEEE-1394, TMDS, PECL, LVDS and RSDS. Some industrial standards of high-speed serial link are listed in Table 1.1.

#### 1.2 BASIC SERIAL-LINK TRANSCEIVER ARCHITECTURE

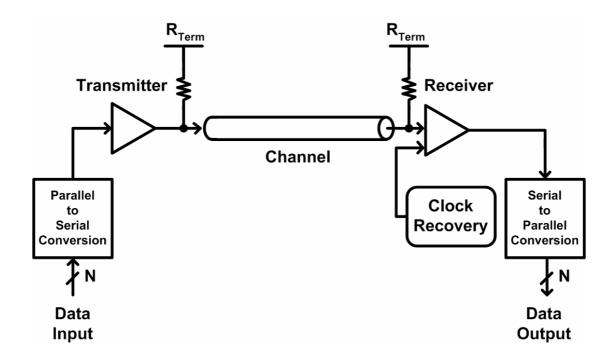

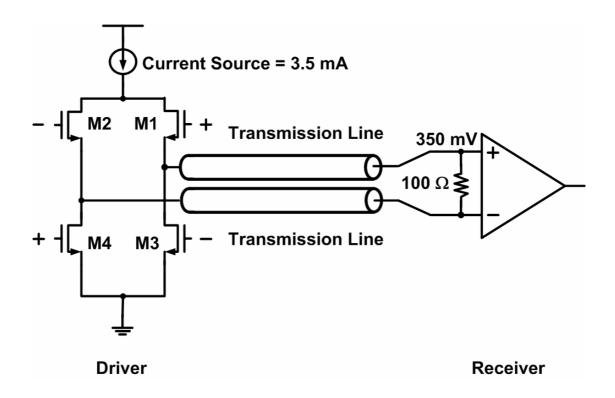

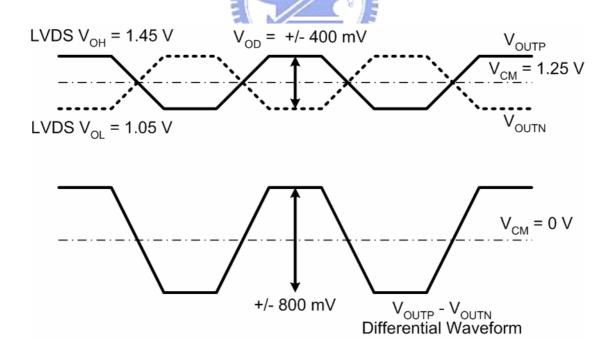

The components of basic serial-link transceiver architecture, as shown in Fig. 1.1, are a parallel-to-serial conversion circuit, a transmitter, a channel, a receiver, and a serial-to-parallel conversion circuit. The data before transmitted are usually parallel data stream in order to increase the bandwidth of the link. Therefore, a parallel-to-serial conversion circuit is needed before sending data to the transmitter. The transmitter converts digital information to analog signal on the transmission medium. This medium which signals travel on is commonly called the communication channel such as the coaxial cable or the twisted pair cable. The receiver on the other end of the channel recovers the signal to the original digital information by amplifying and sampling the signal. The termination resistors which match the impedance of the channel could minimize signal reflection in order to have better signal quality. The clock recovery circuit at the receiver is used to adjust the receiver clock based on the received data to let the sampling point at the middle of the received data. Then, a serial-to-parallel conversion circuit is used to convert the serial data back to N parallel bits in order to be processed by following digital circuits.

#### 1.3 HIGH-SPEED AND LOW-POWER TRANSCEIVER CIRCUITS DESIGN

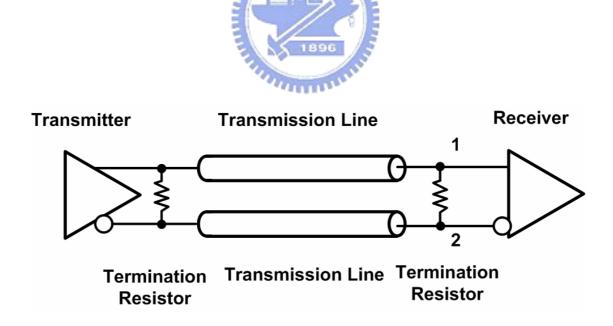

A high performance transceiver circuit must consider speed, power consumption, cost and noise. However, the four factors are trade-off to each other. On balance, the low output signal swing and differential data transmission are the good choice for designing a high performance transceiver circuit. Signals transmitted with low voltage swing can minimize power dissipation and enable operation at very high speed. The differential transmission can provide adequate noise margin in practical systems since

signals are transmitted with low voltage swing.

The controversial point is to use the differential transmission. It costs twice of connectors and transmission lines. However, reliable single-ended signals require many ground pins (many high-speed chips and/or backplanes provide one ground pin for every two signal pins) and run significantly slower. And for noise concern, any noise that is coupled into both transmission lines of the signal path will be rejected at node 1 and node 2 in receiver, as shown in Fig. 1.2, due to the common-mode rejection of the differential amplifier. Besides, for EMI aspect, differential signals tend to radiate less EMI than single-ended signals due to the canceling of magnetic fields.

There are currently many different transmission technologies that are applied for different I/O interfaces [2]. The comparison between these different transmission technologies is shown in Table 1.2.

#### 1.4 THESIS ORGANIZATION

The chapter 2 of the thesis discusses the low-voltage differential signaling (LVDS) standard and the reduced-swing differential signaling (RSDS) standard. The detail DC specifications and applications of both standards are presented. In the chapter 3, a phase-locked loop (PLL) is described and the simulation results are in the final section. In the chapter 4 and 5, three I/O buffers and the complete transmitter for flat panel display applications are implemented. The new proposed I/O buffers with both LVDS and RSDS standards are presented and detail circuit functions of the transmitter are discussed. The last chapter recapitulates the major consideration of this thesis and concludes with suggestion for future investigation.

Table 1.1

Industrial standards for high-speed serial link.

| Standard             | Speed               |

|----------------------|---------------------|

| USB 2.0 (High Speed) | 480 Mb/s            |

| RAM Bus              | 800 Mb/s            |

| IEEE 802.3           | 1 Gb/s              |

| IEEE 1394b           | 1.6 Gb/s ~ 3.2 Gb/s |

| SONET OC-48          | 2.4883 Gb/s         |

Table 1.2

Comparison between different transmission technologies

that are applied for different I/O interfaces.

| and the application of the state of the stat |          |          |          |          |         |         |         |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|---------|---------|---------|--|

| ES N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |          |          |          |         |         |         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RS-422   | PECL     | LVDS     | RSDS     | Optics  | GTL     | TTL     |  |

| Signaling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Diff.    | Diff.    | Diff.    | Diff.    | Single- | Single- | Single- |  |

| type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          | 1        | 2        | 115      | ended   | ended   | ended   |  |

| Transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | +/- 2000 | +/- 600  | +/- 250  | +/- 100  | n/a     | 1200    | 2400    |  |

| output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ~        | ~        | ~        | ~        |         |         |         |  |

| voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | +/- 5000 | +/-1000  | +/- 450  | +/- 400  |         |         |         |  |

| swing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (typical | (typical | (typical | (typical |         |         |         |  |

| (mV)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | +/-2000) | +/- 800) | +/- 350) | +/- 200) |         |         |         |  |

| Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | +/- 200  | +/- 200  | +/- 100  | +/- 100  | n/a     | 100     | 1200    |  |

| input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | ~        |          |          |         |         |         |  |

| threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | +/-300   |          |          |         |         |         |  |

| voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |          |          |          |         |         |         |  |

| (mV)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |          |          |          |         |         |         |  |

| Speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | < 30     | > 400    | > 400    | > 400    | > 1000  | < 200   | < 100   |  |

| (Mb/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |          |          |          |         |         |         |  |