# 國立交通大學

電子工程學系電子研究所

博士論文

適用於高低壓共容輸入輸出介面之積體電路 靜電放電防護設計

# ESD PROTECTION DESIGNS FOR MIXED-VOLTAGE I/O INTERFACES IN CMOS INTEGRATED CIRCUITS

研究生:林昆賢(Kun-Hsien Lin)

指導教授 :柯 明 道 (Ming-Dou Ker)

中華民國 九十四年一月

# 適用於高低壓共容輸入輸出介面之積體電路 靜電放電防護設計

# ESD PROTECTION DESIGNS FOR MIXED-VOLTAGE I/O INTERFACES IN CMOS INTEGRATED CIRCUITS

研究生:林昆賢 Student: Kun-Hsien Lin

指導教授:柯明道 Advisor: Ming-Dou Ker

A Dissertation

Submitted to

Institute of Electronics

College of Electrical Engineering

And Computer Science

National Chiao Tung University

For the Degree of Doctor of Philosophy

in

Electronic Engineering

January 2005 Hsinchu, Taiwan, Republic of China

中華民國九十四年一月

# 適用於高低壓共容輸入輸出介面之積體電路 靜電放電防護設計

研究生:林昆賢 指導教授:柯明道

## 國立交通大學電子工程學系電子研究所

## 摘要

適用於高低壓共容輸入輸出介面(Mixed-Voltage I/O Interfaces)或具有 省電模式(Power-Down-Mode)功能之互補式金氧半積體電路(CMOS ICs)將 使得靜電放電(Electrostatic Discharge, ESD)防護設計有更多的限制與困 難。適用於高低壓共容輸入輸出介面之積體電路,靜電放電防護設計必需 考慮在電路正常操作下, 閘極氧化層(Gate Oxide)的可靠度問題與避免額外 的漏電流路徑;而具有省電模式功能之積體電路,靜電放電防護設計必需 考慮在省電模式操作下,避免額外的漏電流路徑與內部電路誤動作的發 生。在靜電放電發生時,靜電放電防護電路必需能夠有效地保護內部電路 防止內部電路受到損傷。此外,在高壓互補式金氧半製程技術中,靜電放 電防護元件的低持有電壓(Holding Voltage)特性將使得高壓積體電路發生 閉鎖效應(Latchup)或類似閉鎖效應(Latchup-Like)的危險。此問題將使得高 壓積體電路之靜電放電防護設計更加困難。另一方面,在奈米互補式金氧 半製程技術中,如何設計具較快導通速度且較小佈局面積的電源間靜電放 電箝制電路(Power-Rail ESD Clamp Circuit)來保護超薄的閘極氧化層以應用 在系統單晶片(SOC)將是個挑戰。本論文將針對高低壓共容輸入輸出介 面、具有省電模式功能、高壓互補式金氧半製程技術、與奈米互補式金氧 半製程技術之積體電路靜電放電防護設計上的限制與困難作討論,並進一 步設計出有效的靜電放電防護電路在各相關應用之積體電路晶片。

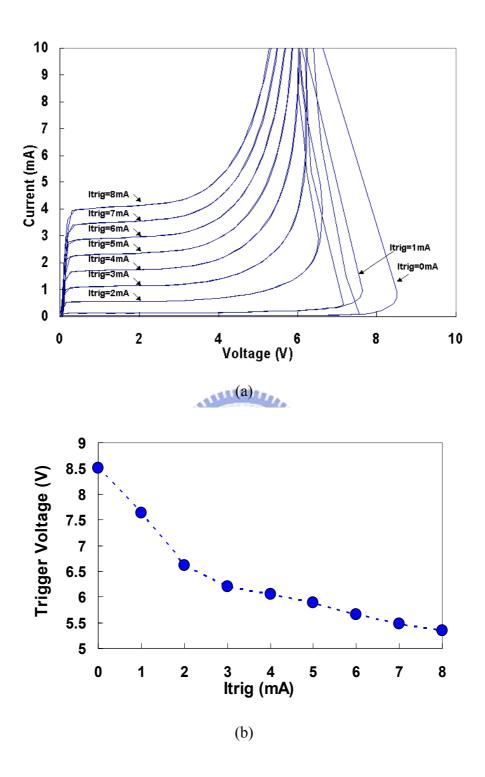

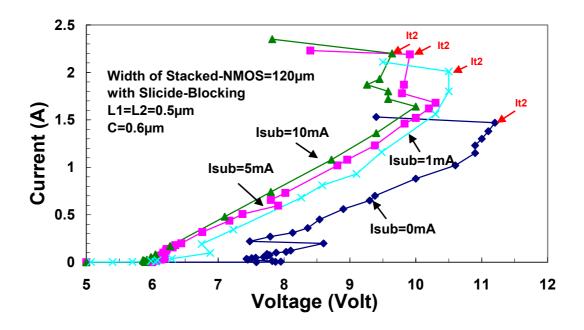

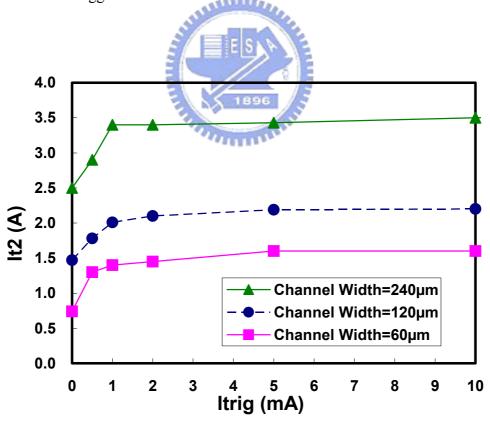

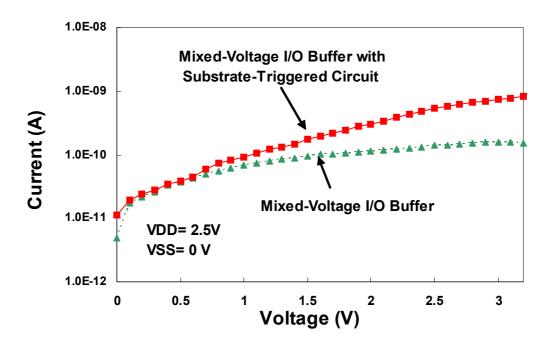

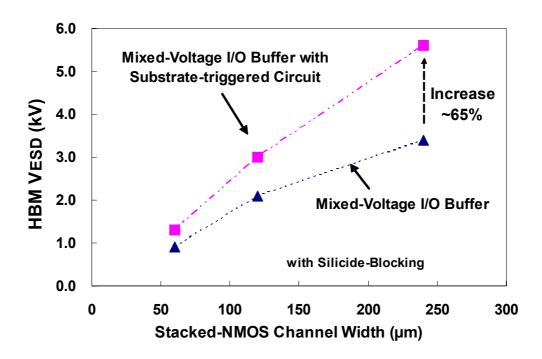

為了提供有效的靜電放電防護於高低壓共容輸入輸出電路,本論文提出利用基體觸發(Substrate Triggered)技術來提昇堆疊電晶體(Stacked-NMOS)的靜電放電防護能力。利用基體觸發技術可使得堆疊電晶體的觸發電壓(Trigger Voltage)降低,如此更能有效地保護高低壓共容輸入輸出電路。這種利用基體觸發技術所設計靜電放電防護電路其製程步驟完全相容於一般互補式金氧半導體的製程,且不需要使用厚的閘極氧化層。適用於2.5V/3.3V 共容高低壓輸入輸出電路的靜電放電防護電路已在0.25 微米互補式金氧半製程中實際被製作與驗證。實驗結果顯示利用基體觸發技術所設計靜電放電防護電路可使得堆疊電晶體的觸發電壓從8.5 V 降低到5.3 V;而高低壓共容輸入輸出電路在240 微米總寬度的堆疊電晶體條件下,其人體放電模式(Human-Body-Model, HBM)的靜電放電耐受能力可以從原來的3.4 kV 提昇到5.6 kV。

為了提供有效的靜電放電防護電路架構。此靜電放電防護電路晶片,本論文提出新型的靜電放電防護電路架構。此靜電放電防護電路架構包括一靜電放電匯流排(ESD Bus)與數個二極體(Diode),使得積體電路進入省電模式操作下,可避免從輸入輸出焊墊(I/O Pad)到 VDD 電源線間的漏電流路徑及內部電路誤動作的發生。當積體電路在正常操作下,此設計具有極低的漏電流且不會影響到內部電路的正常工作。在此靜電放電防護電路架構中,VDD 到 VSS 電源間以及靜電放電匯流排到 VSS 電源間,各有一組靜電放電箝制電路以達到全晶片靜電放電防護設計的目的。在 0.35 微米互補式金氧半製程中,此設計可達到 7.5 kV 的人體放電模式靜電放電耐受能力。此外,在此靜電放電防護電路架構中,本論文也提出了改善輸出端電壓準位的電路,使得內部電路在正常操作下輸出端的最高電壓可以達到 VDD 的電壓準位。

在高壓互補式金氧半製程技術中,金氧半場效電晶體(MOSFET)、矽控整流器(SCR)或者是雙載子電晶體(BJT),被廣泛的用作靜電放電防護元件。但是這些靜電放電防護元件在驟回崩潰(Snapback Breakdown)狀態下的持有電壓都遠小於高壓 Vcc 電源的電壓。此低持有電壓的元件特性將使得在實際系統應用下,高壓積體電路發生閉鎖效應或類似閉鎖效應的危

險,尤其是將這些元件用作電源間靜電放電箝制元件。本論文針對此問題作深入的研究,並進一步提出新型的電源間靜電放電箝制電路以避免高壓積體電路發生閉鎖效應或類似閉鎖效應的危險。此設計是藉由調整堆疊元件的數目,使得堆疊元件結構在驟迴崩潰狀態下的箝制電壓超過高壓 Vcc電源的電壓。如此,在不需要增加或改變製程步驟下,便可以達到避免高壓積體電路發生閉鎖效應或類似閉鎖效應的目的。利用此概念設計的堆疊場氧化層電晶體結構(Stacked Field-Oxide Structure)用在電源間靜電放電箝制電路已經在供應電壓為40 V的0.25 微米互補式金氧半製程中驗證,其能有效地防止高壓積體電路發生閉鎖效應或類似閉鎖效應的危險。

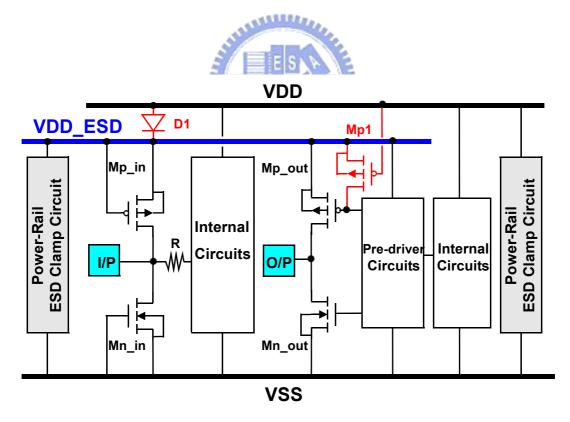

為了在奈米金氧半製程技術中實現具較高靜電放電耐受能力且較小佈局面積的輸入輸出單元(I/O Cell),本論文在 0.13 微米互補式金氧半製程中,提出使用電源間寄生矽控整流器來作為電源間靜電放電箝制元件的輸入輸出單元。本論文共提出兩種寄生矽控整流器結構,其在電路正常操作下並沒有閉鎖效應的問題。在佈局上,此寄生矽控整流器結構是放置於輸入輸出單元的輸入(或輸出)P 型電晶體與 N 型電晶體之間。此外,寄生矽控整流器的導通速度可經由基體觸發技術而明顯的提昇。在 0.13 微米互補式金氧半製程中,此設計可達到 5 kV 的人體放電模式靜電放電耐受能力。此設計讓每個輸入輸出單元都具有一個快導通速度且高靜電放電耐受能力的電源間靜電放電箝制元件,因此在單一的輸入輸出單元便可以提供全晶片靜電放電防護所需之放電路徑。利用此設計,晶片可在較小的佈局面積下具有更高的靜電放電耐受能力。

在本博士論文中,已經針對高低壓共容輸入輸出介面、具有省電模式功能、高壓互補式金氧半製程技術、與奈米互補式金氧半製程技術等應用之積體電路設計出高效能的靜電放電防護電路。所設計的靜電放電防護電路均已在實際晶片上成功驗證,並有相對應的國際期刊論文發表與專利申請。

# ESD PROTECTION DESIGNS FOR MIXED-VOLTAGE I/O INTERFACES IN CMOS INTEGRATED CIRCUITS

Student: Kun-Hsien Lin Advisor: Ming-Dou Ker

Department of Electronics Engineering and Institute of Electronics

National Chiao Tung University

#### **ABSTRACT**

For the CMOS integrated circuits (ICs) with the mixed-voltage I/O interfaces or power-down-mode application, the on-chip electrostatic discharge (ESD) protection circuits will meet more design constraints and difficulties. The on-chip ESD protection circuit for mixed-voltage I/O interfaces should meet the gate-oxide reliability constraints and prevent the undesired leakage current paths during normal circuit operating operation, whereas that for IC with power-down-mode operation should avoid the undesired leakage current paths and malfunction during power-down-mode operation. During ESD stress condition, the on-chip ESD protection circuit should provide effective ESD protection for the internal circuits. In high-voltage CMOS technology, the low-holding-voltage characteristic of ESD protection devices has been found to cause the high-voltage CMOS ICs susceptible to latchup or latchup-like danger during normal circuit operating condition. How to avoid the latchup or latchup-like failure in high-voltage CMOS ICs will be an important challenge to on-chip ESD protection design for high-voltage CMOS IC products. In nanoscale CMOS technology, how to realize the turn-on-efficient and area-efficient power-rail ESD clamp circuit to protect the ultra-thin gate oxide will be an important challenge to system-on-a-chip (SOC) applications with a much larger chip size. In this thesis, the ESD design constraints in mixed-voltage I/O interfaces, power-down-mode application, high-voltage CMOS technology, and nanoscale

CMOS technology are presented. Furthermore, the novel on-chip ESD protection circuits have been developed to overcome the design constraints in such applications.

To provide effective ESD protection in the mixed-voltage I/O interfaces, a new ESD protection design, by using the substrate-triggered stacked-nMOS device, is proposed to protect the mixed-voltage I/O circuits of CMOS ICs. The substrate-triggered technique is applied to reduce the trigger voltage of the stacked-nMOS device for ensuring effective ESD protection for the mixed-voltage I/O circuits. The proposed ESD protection circuit with the substrate-triggered technique is fully compatible to general CMOS process without causing the gate-oxide reliability problem. Without using the thick gate oxide, the new proposed design has been fabricated and verified for 2.5V/3.3V-tolerant mixed-voltage I/O circuit in a 0.25-μm salicided CMOS process. By using this substrate-triggered design, the trigger voltage of the stacked-nMOS device can be reduced from the original 8.5V to become 5.3V to ensure effective protection for the mixed-voltage I/O circuits. The human-body-model (HBM) ESD level of the mixed-voltage I/O buffer with a stacked-nMOS of 240-μm channel width can be improved from the original 3.4 kV up to 5.6 kV by this substrate-triggered circuit.

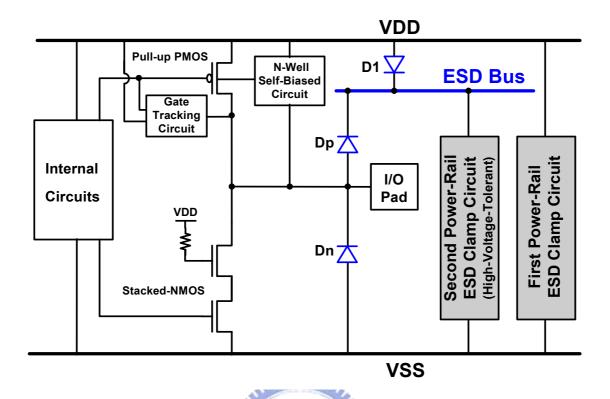

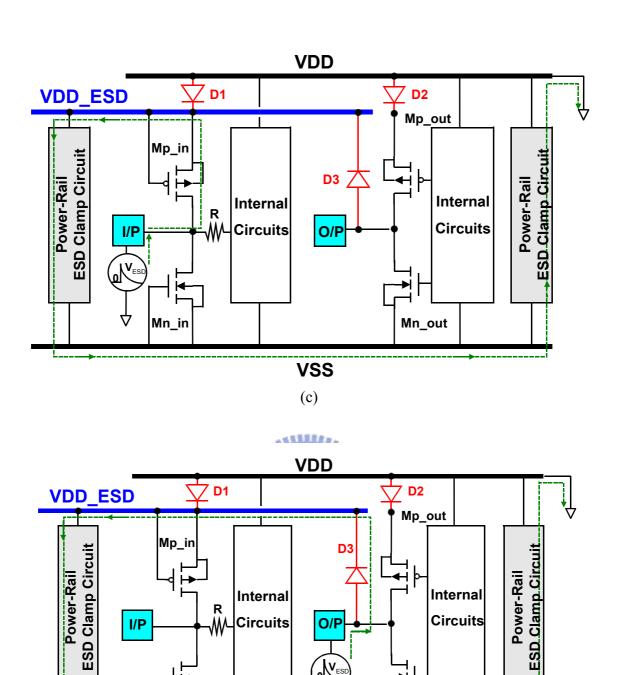

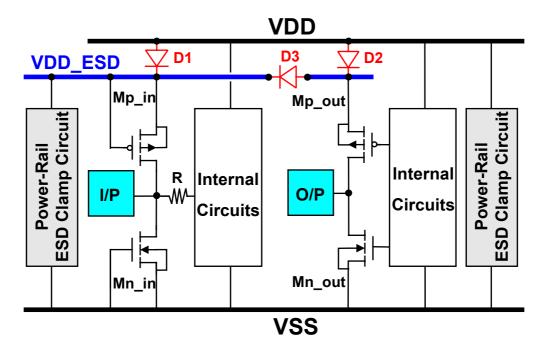

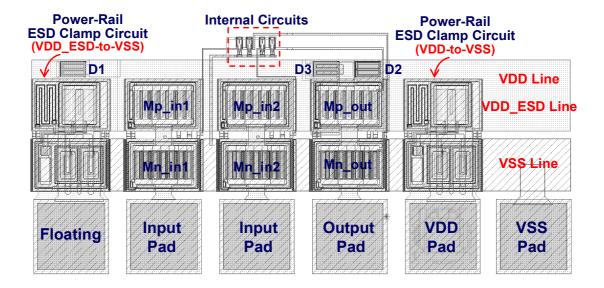

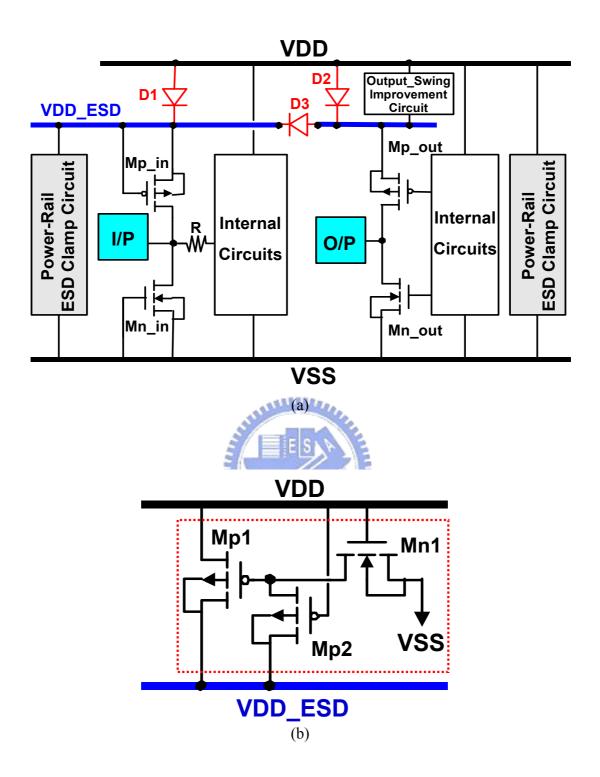

To provide effective ESD protection for power-down-mode application, a new design on the ESD protection schemes for CMOS IC operating in power-down-mode condition is proposed. By using an additional ESD bus and diodes, the new proposed ESD protection schemes can block the leakage current from I/O pad to VDD power line to avoid malfunction during power-down-mode operating condition. During normal circuit operating condition, the new proposed ESD protection schemes have no leakage path to interfere with the normal circuit functions. The whole-chip ESD protection design can be achieved by insertion of ESD clamp circuits between VSS power line and both VDD power line and VDD ESD bus line. Experimental results have verified that the HBM ESD level of the new schemes can be greater than 7.5kV in a 0.35-µm silicided CMOS process. Furthermore, the output signal of the proposed ESD protection schemes can be successfully pulled up to VDD again by the output-swing improvement circuit under normal circuit operating condition.

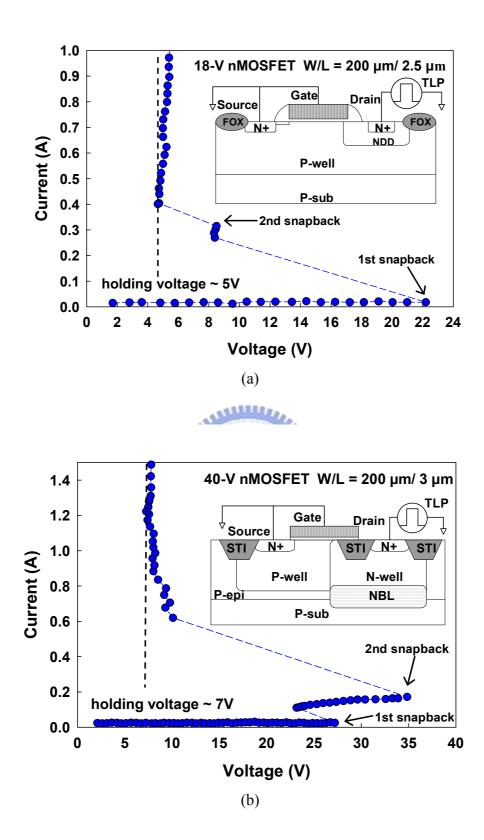

In high-voltage CMOS technology, high-voltage MOSFET, silicon controlled rectifier (SCR) device, and bipolar junction transistors have been widely used as on-chip ESD protection devices. The double snapback characteristic in the high-voltage nMOSFETs has been investigated and analyzed by both measured and simulation results. Furthermore, the holding voltage of the high-voltage devices in snapback breakdown condition has been found to be much smaller than the high-voltage power supply voltage. Such characteristics will

cause the high-voltage CMOS ICs susceptible to the latchup or latchup-like danger in the practical system applications, especially while these devices are used in the power-rail ESD clamp circuits between the high-voltage power lines. In this thesis, the latchup or latchup-like issues in high-voltage CMOS ICs have been investigated in details. By adjusting different numbers or different types of stacked ESD devices in the power-rail ESD clamp circuits, the total holding voltage of the stacked structure can be designed higher than the high-voltage supply voltage without using extra process modification in the high-voltage CMOS technology. A new latchup-free design on the high-voltage power-rail ESD clamp circuit with stacked field-oxide structure is proposed and successfully verified in a 0.25-µm 40-V CMOS process to achieve the desired ESD level. Therefore, latchup or latchup-like issues can be avoided by stacked field-oxide structures for the IC applications with power supply of 40V.

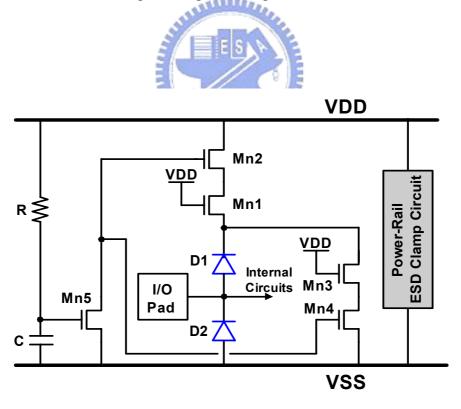

In order to realize the high-ESD-robust and high-area-efficient I/O cells in nanoscale CMOS technology, a new ESD protection design for I/O cells with embedded SCR structure as power-rail ESD clamp device in a 130-nm CMOS process is proposed. Two new embedded SCR structures without latchup danger are proposed to be placed between the input (or output) pMOS and nMOS devices of the I/O cells. Furthermore, the turn-on efficiency of embedded SCR can be significantly increased by substrate-triggered technique. Experimental results have verified that the HBM ESD level of this new proposed I/O cells can be greater than 5kV in a 130-nm fully salicided CMOS process. By including the efficient power-rail ESD clamp device into each I/O cell, whole-chip ESD protection scheme can be successfully achieved within a small silicon area of I/O cell. Such I/O cells are very suitable for SOC applications in nanoscale CMOS technology.

In summary, the novel ESD protection designs have been successfully developed for mixed-voltage I/O interfaces, power-down-mode application, high-voltage CMOS technology, and nanoscale CMOS technology with high ESD robustness. Each of the proposed ESD protection circuits has been practically verified in the silicon testchips.

# 誌謝

首先要感謝我的指導教授柯明道教授三年多來的耐心指導與鼓勵,使 我能夠順利完成博士學業。在指導教授循序漸進的教誨下,讓我得以在積 體電路靜電放電防護設計的領域中,由入門到能夠獨立解決問題。此外, 指導教授認真的研究態度與嚴謹的處事原則,也讓我學習到挑戰困難解決 問題的正確態度與方法。雖然在過程中倍感艱辛,也經歷了不少挫折,然 而卻讓我獲益良多,更促使我成長。此外還要感謝實驗室的吳重雨教授給 我的許多指導與建議。

在這段求學的過程中,『工研院系統晶片技術發展中心』的『產品與靜電防護技術部』給予我的研究最大的支持與協助,從實驗晶片的下線及量測設備的支援協助,都是使得我實驗研究能夠順利完成的主要原因。在此特別感謝吳文慶組長、江志強經理、翁季萍經理、彭政傑課長、莊哲豪課長所給予的支持與鼓勵,也要感謝陳子平、曾當貴、陳世宏、黃柏獅、林明芳、劉美竹、鍾瑞玲、劉玉珠以及曾任職於工研院的姜信欽博士、張智毅、蔡燿城、侯春麟在實驗上的協助,使我的研究論文能夠在國際上順利發表,獲得肯定。

此外,也要感謝『奈米電子與晶片系統實驗室』的陳東暘博士、徐國鈞博士、莊健暉、羅文裕、陳世倫、鄧至剛、徐新智、許勝福、張瑋仁、陳榮昇、陳穩義、吳偉琳諸位實驗室學長、同學及學弟妹們,在我博士班的這一個階段,於各方面給了我不少的幫忙,使得我能順利完成我的論文以及在知識及處事上有所成長。也感謝實驗室助理卓慧貞小姐在實驗室行政事務上的許多協助。

最後,我要致上我最深最深的感謝給予我的父親林昌德先生、母親賴 貴英女士、岳父戴文謁先生、岳母戴張足女士、哥哥林鼎晏先生、弟弟林 昀生先生、愛妻戴淑梅小姐,沒有你們無怨悔、永無止境的付出、鼓勵、 支持與照顧,就沒有我今日的成就,在此衷心地感謝你們。另外,要祝福 所有在這幾年與我相處過的師長、朋友、學弟妹們,有緣與你們同在這一 個階段成長,是我一生的榮幸,願大家都能順心如意,心想事成!

> 林 昆 賢 謹誌於竹塹交大 九十四年 一月

# **CONTENTS**

| ABSTRA                                   | CT ( | (CHINESE)                                           | i        |  |  |        |    |       |           |

|------------------------------------------|------|-----------------------------------------------------|----------|--|--|--------|----|-------|-----------|

| ABSTRA                                   | CT ( | (ENGLISH)                                           | iv       |  |  |        |    |       |           |

| ACKNOWLEDGEMENTS CONTENTS TABLE CAPTIONS |      |                                                     |          |  |  |        |    |       |           |

|                                          |      |                                                     |          |  |  | FIGURE |    |       | xi<br>xii |

|                                          |      |                                                     |          |  |  | FIGURE | CA | THORS | AII       |

| СНАРТЕ                                   | R 1  | INTRODUCTION                                        | 1        |  |  |        |    |       |           |

| 1.1                                      | Back | kground                                             | 1        |  |  |        |    |       |           |

| 1.                                       | 1.1  | Issue of Mixed-Voltage I/O Interface                | 1        |  |  |        |    |       |           |

| 1.                                       | 1.2  | Issue of Power-Down Application                     | 4        |  |  |        |    |       |           |

| 1.                                       | 1.3  | Issue of High-Voltage CMOS ICs                      | 5        |  |  |        |    |       |           |

| 1.                                       | 1.4  | Issue of Nanoscale CMOS Technology                  | 6        |  |  |        |    |       |           |

| 1.2                                      | ESD  | Protection Designs for Mixed-Voltage I/O Interfaces | 7        |  |  |        |    |       |           |

| 1.2                                      | 2.1  | Substrate-Triggered Stacked-NMOS Device             | 7        |  |  |        |    |       |           |

| 1.2                                      | 2.2  | Extra ESD Device between I/O pad and VSS            | 7        |  |  |        |    |       |           |

| 1.2                                      | 2.3  | Extra ESD Device between I/O pad and VDD            | 9        |  |  |        |    |       |           |

| 1.2                                      | 2.4  | ESD Protection Design with ESD Bus                  | 10       |  |  |        |    |       |           |

| 1.2                                      | 2.5  | Special Applications                                | 11       |  |  |        |    |       |           |

| 1.3                                      | Thes | sis Organization                                    | 12       |  |  |        |    |       |           |

| Figure                                   | es   |                                                     | 15       |  |  |        |    |       |           |

| СНАРТЕ                                   | R 2  | ESD PROTECTION DESIGN FOR MIXED-VOLTAGIO CIRCUITS   | SE<br>26 |  |  |        |    |       |           |

| 2.1                                      | Stac | cked-NMOS Device                                    | 26       |  |  |        |    |       |           |

| 2.2                                      | Stac | eked-NMOS with Substrate-Triggered Technique        | 28       |  |  |        |    |       |           |

| 2.2                                      | 2.1  | Substrate-Triggered Stacked-NMOS Device             | 28       |  |  |        |    |       |           |

| 2.2                                      | 2.2  | ESD Protection Circuit                              | 28       |  |  |        |    |       |           |

| 2.2                                      | 2.3  | Operating Principles                                | 29       |  |  |        |    |       |           |

| 2.3                                      | Exp  | erimental Results                                   | 31       |  |  |        |    |       |           |

|     | 2.     | 3.1           | Characteristics of the Substrate-Triggered Stacked-NMOS Device | 31 |  |  |  |  |

|-----|--------|---------------|----------------------------------------------------------------|----|--|--|--|--|

|     | 2.     | 3.2           | Leakage Current                                                | 32 |  |  |  |  |

|     | 2.     | 3.3           | ESD level                                                      | 33 |  |  |  |  |

|     | 2.4    | 2.4 Summary 3 |                                                                |    |  |  |  |  |

|     | Table  | S             |                                                                | 35 |  |  |  |  |

|     | Figure | es            |                                                                | 36 |  |  |  |  |

| CH. | APTE   | R 3           | ESD PROTECTION DESIGN FOR IC WITH POWER-DOWN-MODE OPERATION    | 45 |  |  |  |  |

|     | 3.1    | Nev           | w ESD Protection Schemes for IC with Power-Down-Mode Operation | 45 |  |  |  |  |

|     | 3.     | 1.1           | ESD Protection Scheme I                                        | 45 |  |  |  |  |

|     | 3.     | 1.2           | ESD Protection Scheme II                                       | 47 |  |  |  |  |

|     | 3.     | 1.3           | ESD Protection Scheme III                                      | 48 |  |  |  |  |

|     | 3.     | 1.4           | Layout Consideration                                           | 48 |  |  |  |  |

|     | 3.2    | Exp           | perimental Results                                             | 49 |  |  |  |  |

|     | 3      | 2.1           | Leakage Current                                                | 49 |  |  |  |  |

|     | 3      | 2.2           | Function Verification                                          | 50 |  |  |  |  |

|     | 3      | 2.3           | ESD Robustness                                                 | 51 |  |  |  |  |

|     | 3.3    | Out           | put-Swing Improvement Circuit                                  | 52 |  |  |  |  |

|     | 3.4    | Sur           | nmary                                                          | 53 |  |  |  |  |

|     | Table  | S             |                                                                | 54 |  |  |  |  |

|     | Figure | es            |                                                                | 55 |  |  |  |  |

| CH. | APTE   | R 4           | ESD PROTECTION DESIGN IN HIGH-VOLATGE CMOS PROCESS             | 67 |  |  |  |  |

|     | 4.1    | Dou           | uble Snapback Characteristics in High-Voltage NMOSFETs         | 67 |  |  |  |  |

|     | 4.     | 1.1           | Double-Snapback Characteristics                                | 67 |  |  |  |  |

|     | 4.     | 1.2           | Simulations and Analysis                                       | 68 |  |  |  |  |

|     | 4.2    | Hig           | h-Voltage ESD Protection Devices                               | 69 |  |  |  |  |

|     | 4.:    | 2.1           | TLP I-V Characteristics                                        | 69 |  |  |  |  |

|     | 4      | 2.2           | Transient Latchup Test                                         | 70 |  |  |  |  |

|     | 4.3    | Des           | sign of Latchup-Free Power-Rail ESD Clamp Circuits             | 71 |  |  |  |  |

|     | 4.     | 3.1           | TLP I-V Characteristics                                        | 72 |  |  |  |  |

|                                        | 4.3.2   |       | Transient Latchup Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 72  |  |  |

|----------------------------------------|---------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

|                                        |         | 4.3.3 | Latchup-Free Power-Rail ESD Clamp Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 73  |  |  |

|                                        | 4.4     | Sun   | ummary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 73  |  |  |

|                                        | Fig     | ures  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75  |  |  |

| CHA                                    | АРТ     | TER 5 | I/O CELLS WITH EMBEDDED SCR AS<br>POWER-RAIL ESD CLAMP DEVICE IN<br>NANOSCALE CMOS TECHNOLOGY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 88  |  |  |

|                                        | 5.1     | Emb   | pedded SCR Structures in I/O Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 88  |  |  |

|                                        | 5.2     | Exp   | erimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 91  |  |  |

|                                        |         | 5.2.1 | DC I-V Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 91  |  |  |

|                                        |         | 5.2.2 | TLP I-V Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 93  |  |  |

|                                        | 5.2.3   |       | ESD Robustness and Failure Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 95  |  |  |

|                                        |         | 5.2.4 | Turn-On Verification During Pin-to-Pin ESD Stress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 96  |  |  |

|                                        | 5.3     | Sun   | nmary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 96  |  |  |

|                                        | Tab     | oles  | STATE OF THE PARTY | 98  |  |  |

|                                        | Figures |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |  |  |

| CHAPTER 6 CONCLUSIONS AND FUTURE WORKS |         |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |  |  |

|                                        | 6.1     | Mai   | n Results of This Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 114 |  |  |

|                                        | 6.2     | Futu  | ure Works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 115 |  |  |

| REF                                    | ER      | NCES  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 117 |  |  |

| VIT                                    | 124     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |  |  |

|                                        | 125     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |  |  |

| IUL                                    | /1/1/   |       | ON LIST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 123 |  |  |

### **TABLE CAPTIONS**

#### **CHAPTER 2**

**TABLE 2.1** HBM ESD robustness of the mixed-voltage I/O buffers with or without the proposed substrate-triggered circuit under a fixed device dimension.

#### **CHAPTER 3**

**TABLE 3.1** HBM ESD robustness of the traditional ESD protection scheme and the new proposed ESD protection schemes.

#### **CHAPTER 5**

- **TABLE 5.1** HBM ESD robustness of the new proposed ESD protection scheme with embedded SCR structure in each I/O cell.

- **TABLE 5.2** Comparison on the HBM ESD robustness between the traditional I/O cell and the new proposed I/O cells with embedded SCR structures.

1896

#### FIGURE CAPTIONS

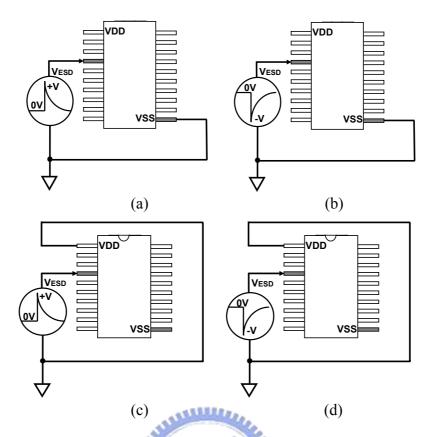

- **Fig. 1.1** The four pin-combination modes for ESD test on an IC product: (a) positive-to-VSS (PS-mode), (b) negative-to-VSS (NS-mode), (c) positive-to-VDD (PD-mode), and (d) negative-to-VDD (ND-mode).

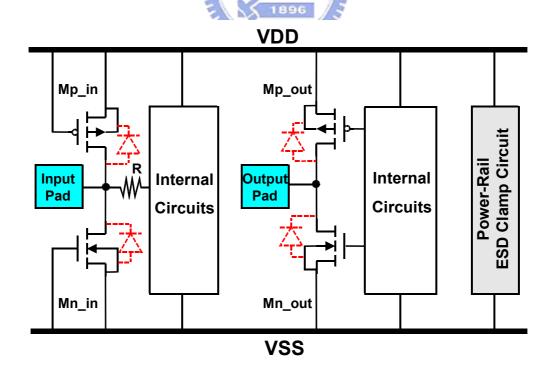

- Fig. 1.2 Typical on-chip ESD protection circuits in a CMOS IC.

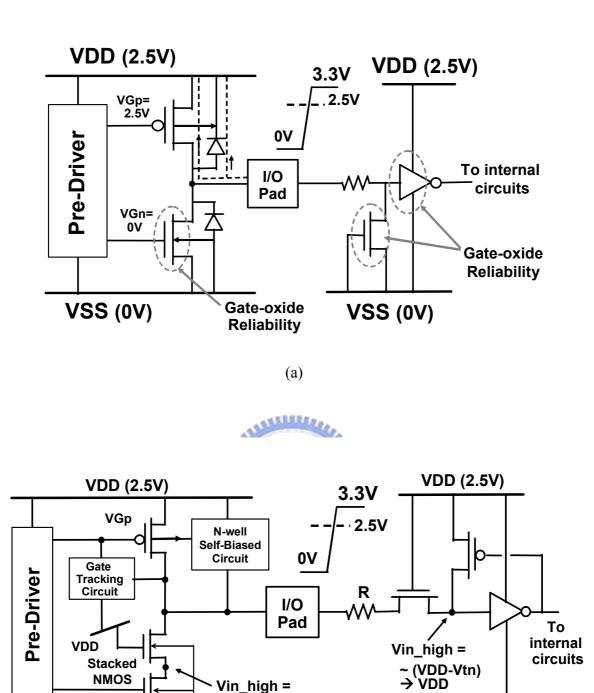

- **Fig. 1.3** Typical circuit diagrams for (a) the traditional CMOS I/O buffer, and (b) the mixed-voltage I/O circuits with the stacked-nMOS and the N-well self-biased pMOS.

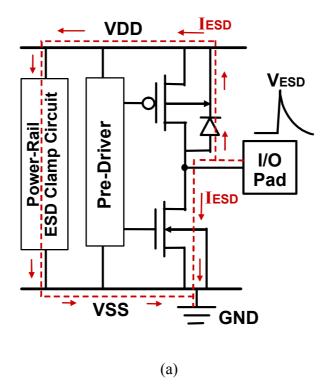

- **Fig. 1.4** The ESD current paths of (a) the traditional I/O pad with power-rail ESD clamp circuit, and (b) the mixed-voltage I/O pad with power-rail ESD clamp circuit, under the positive-to-VSS (PS-mode) ESD stress. The ESD current paths are indicated by the dashed lines.

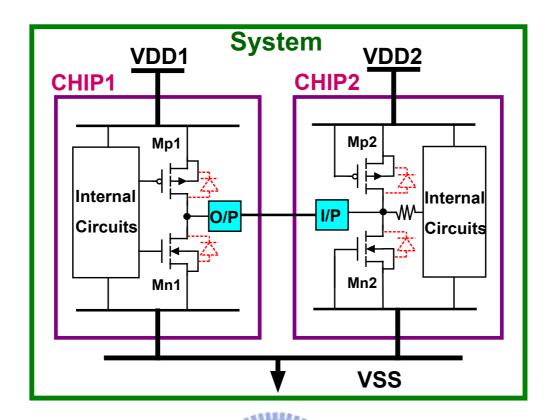

- **Fig. 1.5** An example to show the power-down-mode operation issue on a system with two chips, which are biased with separated VDD1 and VDD2 power supplies.

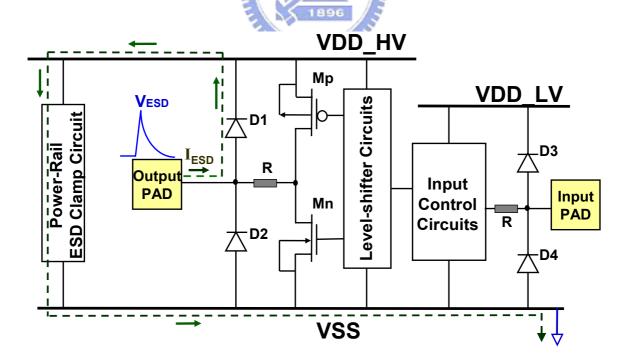

- Fig. 1.6 The typical ESD protection scheme for LCD driver ICs.

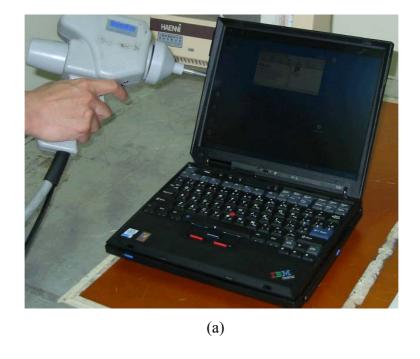

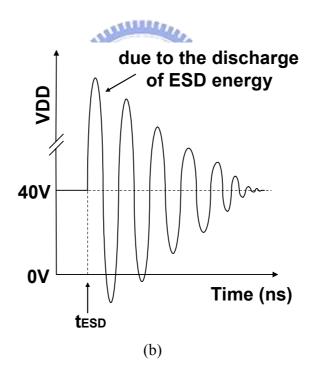

- Fig. 1.7 (a) The system-level EMC/ESD test on LCD panel of notebook by an ESD gun. (b) The transient overshooting/ undershooting voltage waveform on the VDD pin of the driver ICs during system-level EMC/ESD test.

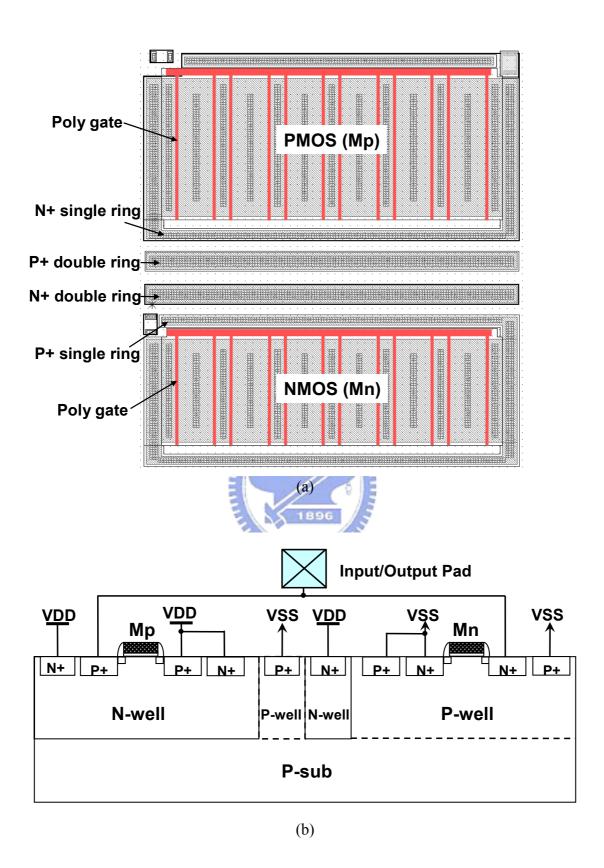

- **Fig. 1.8** (a) Layout view and (b) device structures of the traditional I/O cell with double guard rings inserted between input (or output) pMOS and nMOS devices.

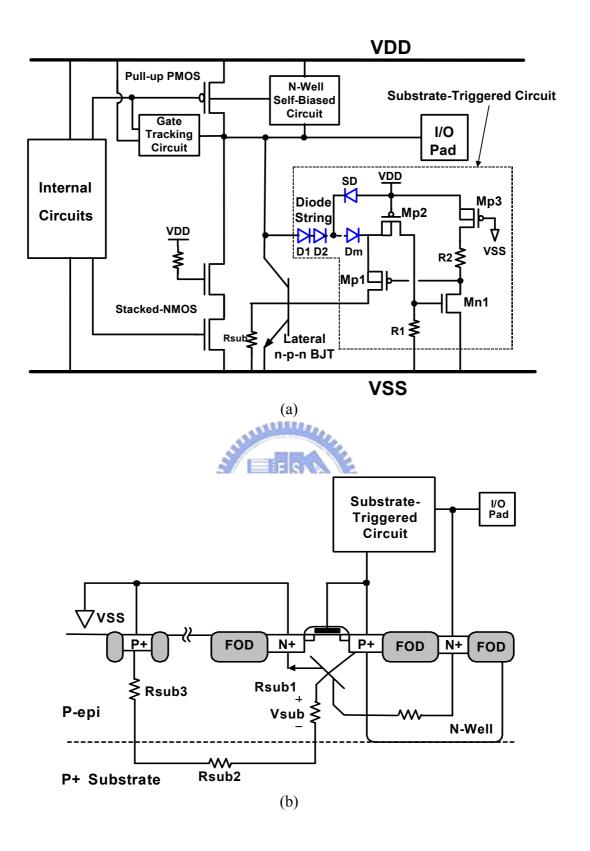

- **Fig. 1.9** (a) ESD protection design with substrate-triggered lateral n-p-n BJT device to protect the mixed-voltage I/O circuits. (b) Cross-sectional view of the lateral n-p-n BJT device in a thin-epi CMOS process.

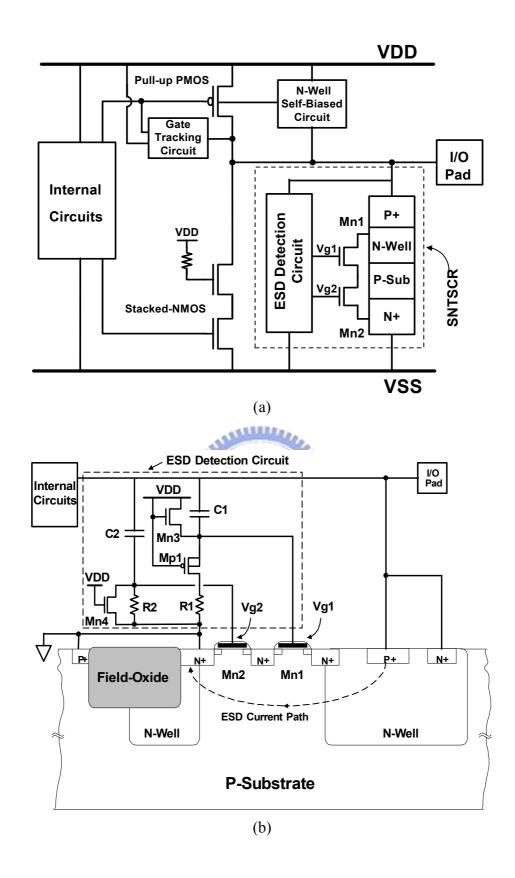

- **Fig. 1.10** (a) ESD protection circuit with the SNTSCR device to protect the mixed-voltage I/O circuits. (b) Realizations of the SNTSCR device and the ESD detection circuit with the gate-coupling technique to trigger on the SNTSCR device.

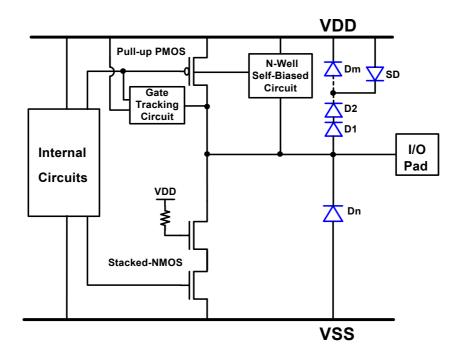

- **Fig. 1.11** ESD protection design with the diode string connected between the I/O pad and VDD power line to protect the mixed-voltage I/O circuits. An additional snubber diode (SD) is used to reduce the leakage current of the diode string due to the Darlington amplification.

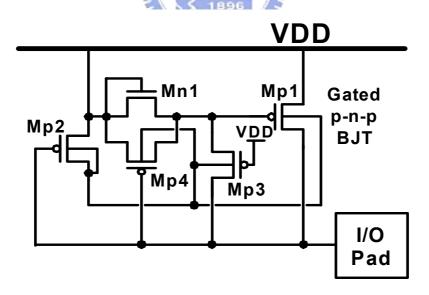

- **Fig. 1.12** ESD protection design with gated p-n-p BJT as the ESD clamp device connected between I/O pad and VDD to protect the mixed-voltage I/O circuits.

- **Fig. 1.13** The ESD protection network with the additional ESD bus line for the mixed-voltage I/O circuits. One power-rail ESD clamp circuit is connected between VDD power line and VSS power line. A second power-rail ESD clamp circuit is connected between ESD bus line and VSS power line.

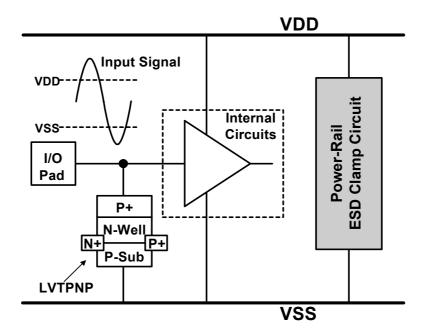

- **Fig. 1.14** ESD protection design with low-voltage-triggered p-n-p (LVTPNP) device for the I/O interfaces with input voltage level higher than VDD or lower than VSS.

- **Fig. 1.15** High-voltage-tolerant ESD protection design with the forward-biased diode in series with one stacked nMOS for analog ESD protection to reduce the input parasitic capacitance.

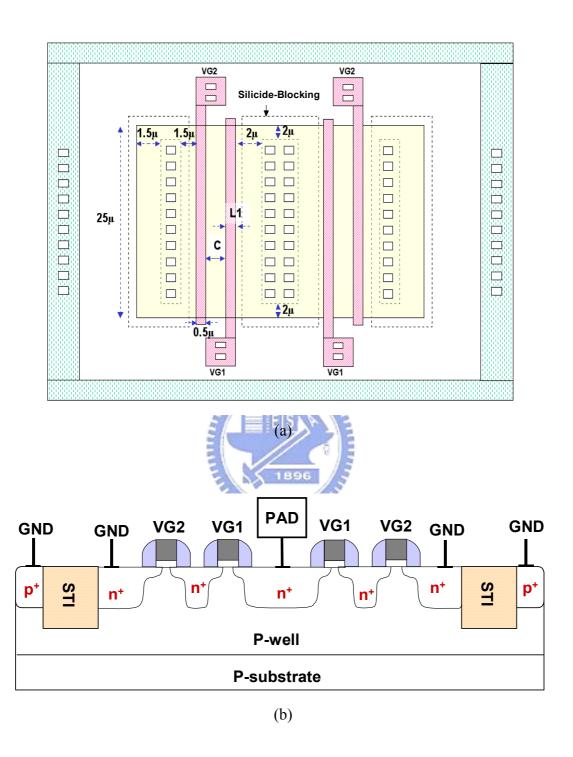

- **Fig. 2.1** (a) The finger-type layout pattern, and (b) the corresponding cross-sectional view, of the stacked-nMOS device for mixed-voltage I/O circuit in a p-substrate CMOS process.

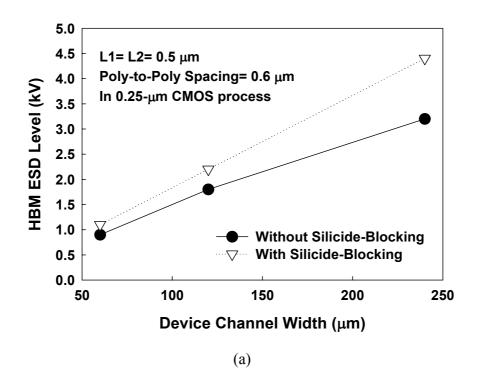

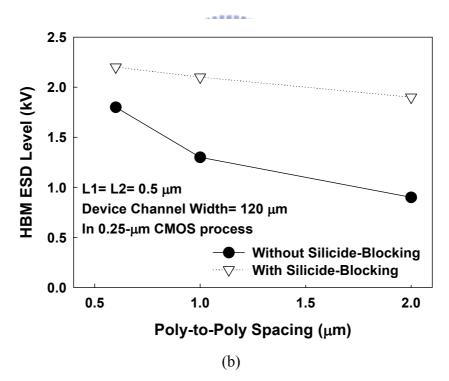

- Fig. 2.2 Comparisons of HBM ESD robustness of the stacked-nMOS device with or without the silicide-blocking process, under (a) different channel widths, and (b) different poly-to-poly spacings, of the stacked-nMOS device fabricated in a 0.25-μm CMOS process.

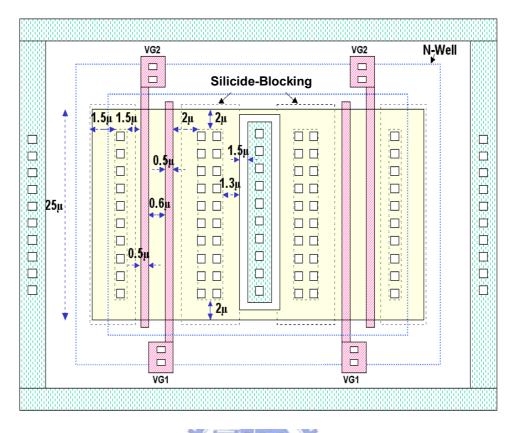

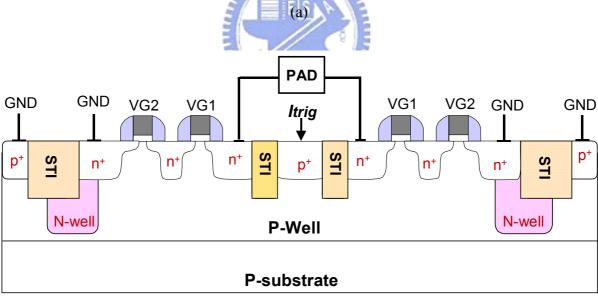

- **Fig. 2.3** (a) The finger-type layout pattern, and (b) the corresponding cross-sectional view, of the substrate-triggered stacked-nMOS device for mixed-voltage I/O circuit in a p-substrate CMOS process.

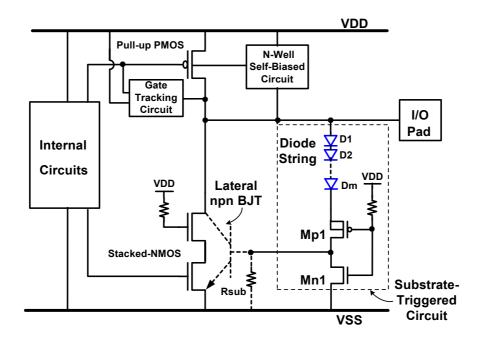

- **Fig. 2.4** The schematic circuit diagram of the substrate-triggered stacked-nMOS device with substrate-triggered circuit for the mixed-voltage I/O circuits.

- **Fig. 2.5** The cross-sectional view of the substrate-triggered stacked-nMOS device with substrate-triggered circuit for the mixed-voltage I/O circuits.

- **Fig. 2.6** The modified design of the substrate-triggered stacked-nMOS device with substrate-triggered circuit for the mixed-voltage I/O circuits without generating extra additional capacitance to the I/O pad.

- **Fig. 2.7** (a) The measured I-V characteristics of the substrate-triggered stacked-nMOS device with different substrate-triggered currents (Itrig). (b) The relation between the trigger voltage of the stacked-nMOS device and the substrate-triggered current (Itrig).

- Fig. 2.8 The TLP-measured I-V curves of the stacked-nMOS device with different

- substrate-triggered currents.

- **Fig. 2.9** The dependence of It2 level on the substrate-triggered current (Itrig) under the different channel widths of substrate-triggered stacked-nMOS device.

- **Fig. 2.10** Comparison of the leakage currents of the mixed-voltage I/O buffers with or without the proposed substrate-triggered circuit. The mixed-voltage I/O buffer in this measurement has a channel width of 240 μm in the stacked nMOS and a channel width of 480 μm in the pull-up pMOS.

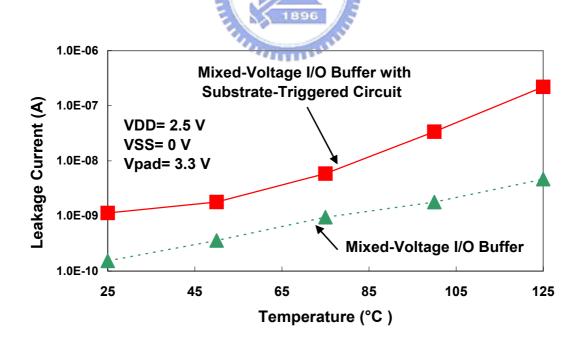

- **Fig. 2.11** The leakage currents of the mixed-voltage I/O buffers with or without the substrate-triggered circuit under different temperatures.

- Fig. 2.12 The positive-to-VSS (PS-mode) HBM ESD levels of the mixed-voltage I/O buffers with or without the substrate-triggered circuit, realized in a 0.25-μm CMOS process with silicide-blocking process.

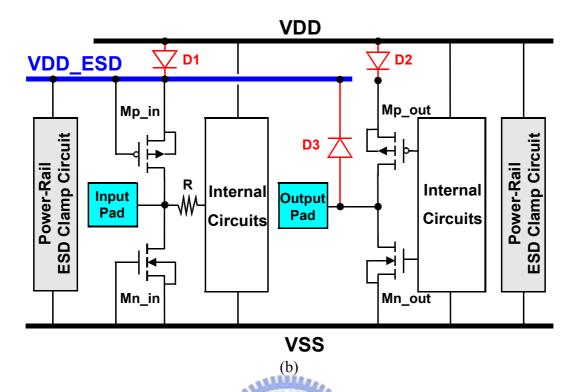

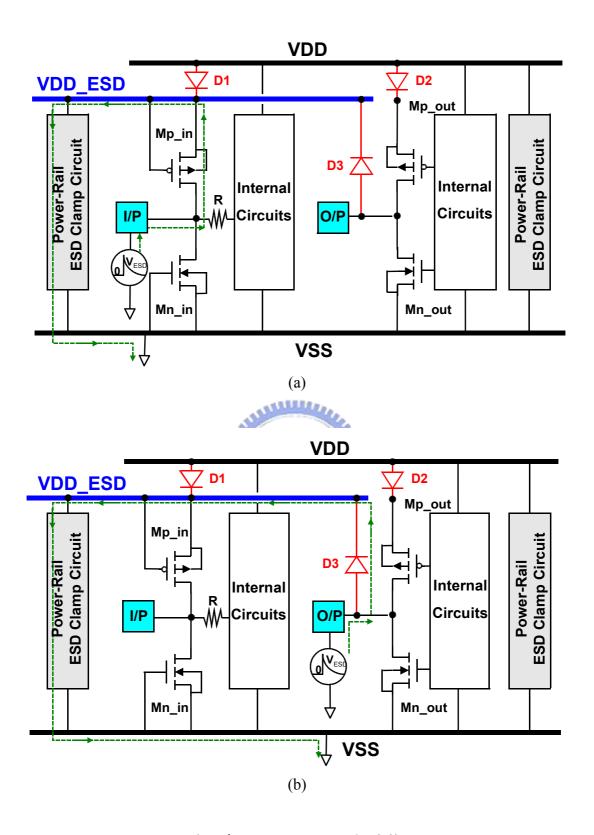

- Fig. 3.1 The new proposed ESD protection scheme I for the IC with power-down-mode operation.

- Fig. 3.2 The ESD current discharging paths of (a) the input pad under PS-mode ESD stress condition, (b) the output pad under PS-mode ESD stress condition, (c) the input pad under PD-mode ESD stress condition, and (d) the output pad under PD-mode ESD stress condition.

- **Fig. 3.3** The new proposed ESD protection scheme II for the IC with power-down-mode operation.

- **Fig. 3.4** The new proposed ESD protection scheme III for the IC with power-down-mode operation.

- **Fig. 3.5** The layout view of the new proposed ESD protection scheme I fabricated in a 0.35-μm silicided CMOS process.

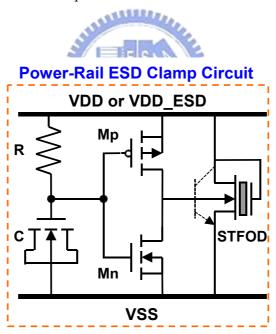

- Fig. 3.6 The circuit diagram of power-rail ESD clamp circuit.

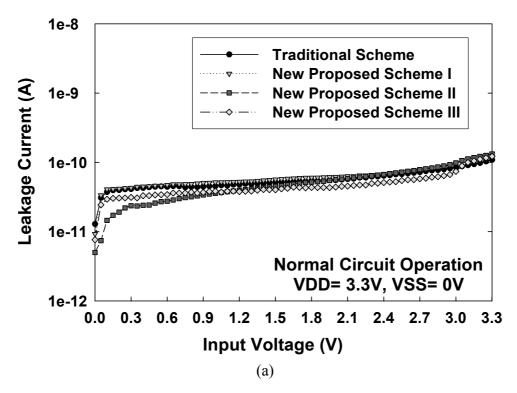

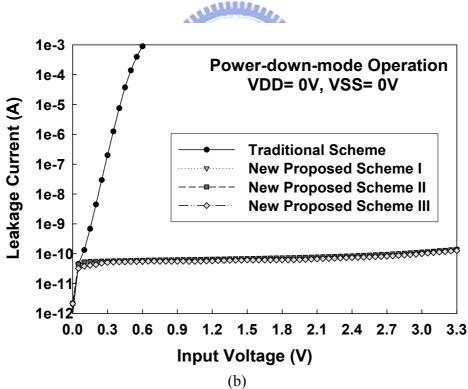

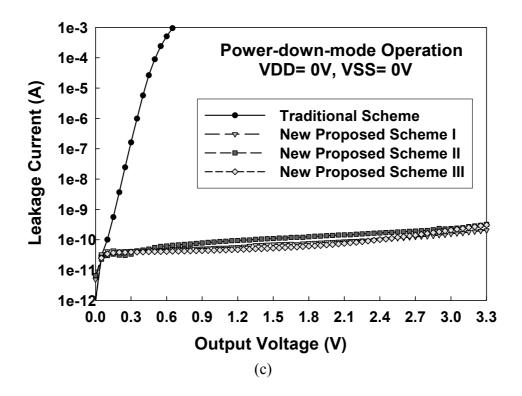

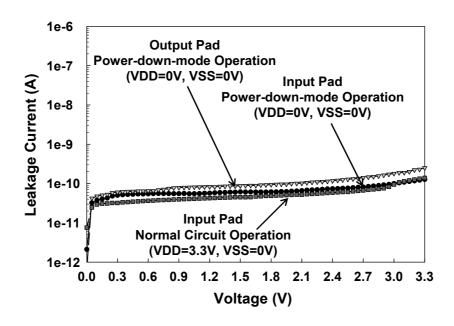

- **Fig. 3.7** Comparison of the measured leakage currents at (a) the input pad under normal circuit operating condition, (b) the input pad under power-down-mode operating condition, and (c) the output pad under power-down-mode operating condition, of the traditional and new proposed ESD protection schemes.

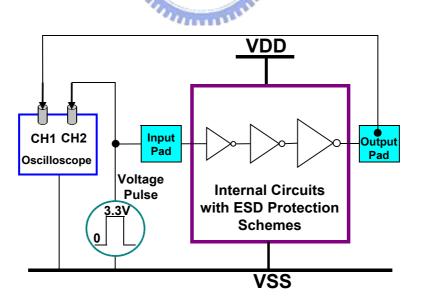

- **Fig. 3.8** The measurement setup to verify the function of I/O cells with the new proposed ESD protection schemes, or the traditional ESD protection scheme, under normal

- circuit operating condition and power-down-mode operating condition.

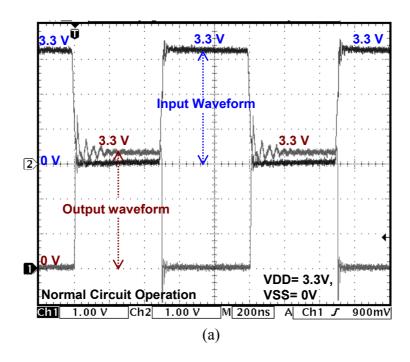

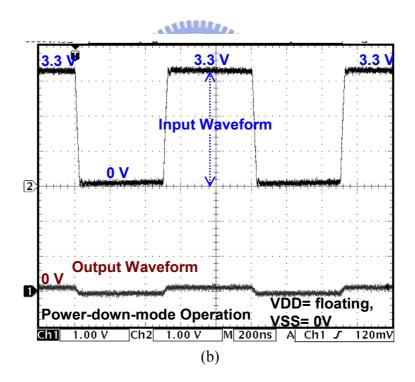

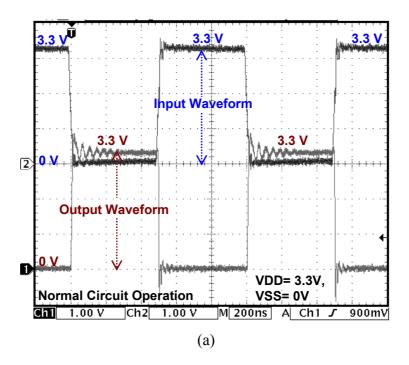

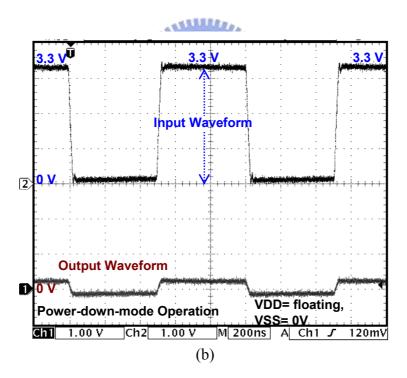

- **Fig. 3.9** The measured voltage waveforms on the input/output pad of IC with the traditional ESD protection scheme under (a) normal circuit operating condition with VDD= 3.3V and VSS= 0V, and (b) power-down-mode operating condition with VDD= floating and VSS= 0V. (*Y* axis= 1V/Div., *X* axis= 200ns/Div.)

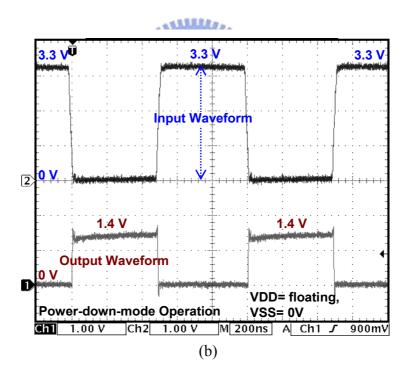

- **Fig. 3.10** The measured voltage waveforms on the input/output pad of IC with the proposed ESD protection scheme I under (a) normal circuit operating condition with VDD= 3.3V and VSS= 0V, and (b) power-down-mode operating condition with VDD= floating and VSS= 0V. (*Y* axis= 1V/Div., *X* axis= 200ns/Div.)

- **Fig. 3.11** (a) The output-swing improvement circuit connecting between the VDD power line and VDD\_ESD bus line in the ESD protection scheme II. (b) The circuit diagram of output-swing improvement circuit.

- **Fig. 3.12** The measured leakage currents at I/O pads of new proposed ESD protection scheme II with the output-swing improvement circuit under normal circuit operating condition and power-down-mode operating condition.

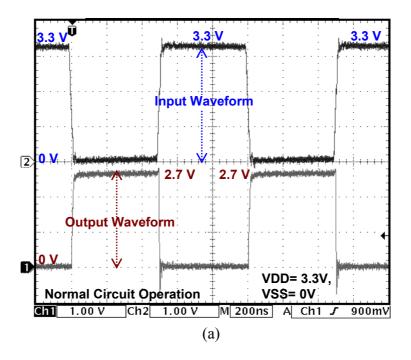

- Fig. 3.13 The measured voltage waveforms on the input/output pad of the proposed ESD protection scheme II with output-swing improvement circuit under (a) normal circuit operating condition with VDD= 3.3V and VSS= 0V, and (b) power-down-mode operating condition with VDD= floating and VSS= 0V. (*Y* axis= 1V/Div., *X* axis= 200ns/Div.)

- **Fig. 4.1** The TLP-measured I-V characteristics of (a) DDD MOS structure fabricated in a 0.35-μm 18-V CMOS process and (b) LDMOS structure fabricated in a 0.25-μm 40-V CMOS process.

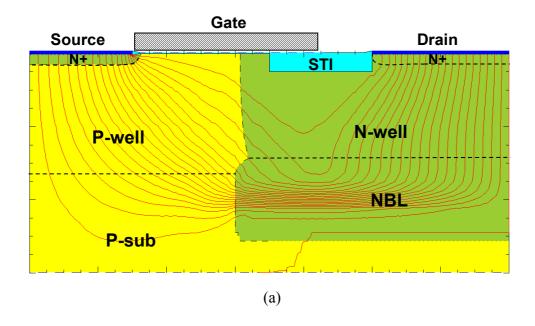

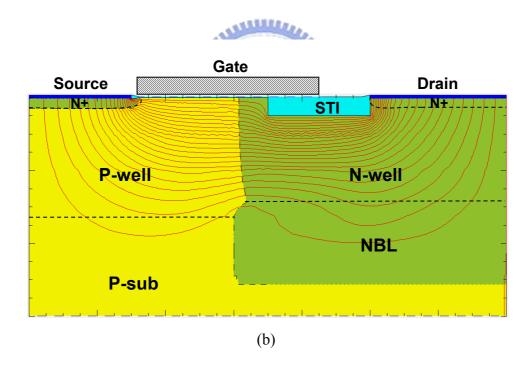

- **Fig. 4.2** Simulated current distributions in the 40-V nMOSFET under the (a) first snapback state, and (b) second snapback state.

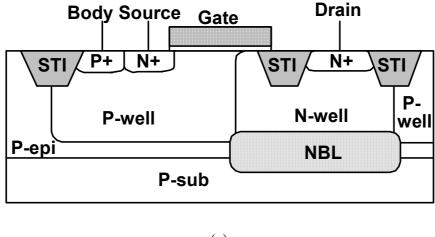

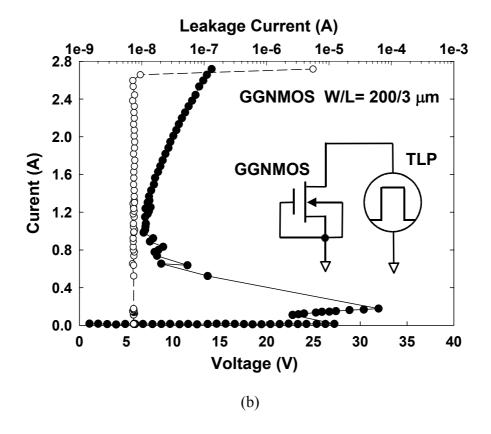

- **Fig. 4.3** The (a) cross-sectional view, and (b) TLP-measured I-V characteristic, of high-voltage gate-grounded nMOS (GGNMOS) device fabricated in a 0.25-μm 40-V CMOS process.

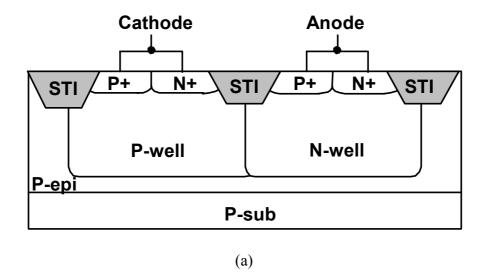

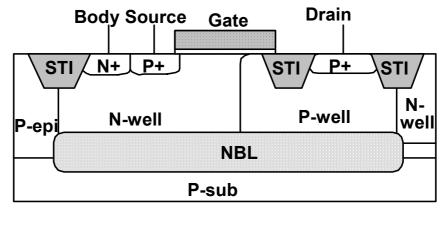

- **Fig. 4.4** The (a) cross-sectional view, and (b) TLP-measured I-V characteristic, of high-voltage silicon controlled rectifier (SCR) device fabricated in a 0.25-μm 40-V CMOS process.

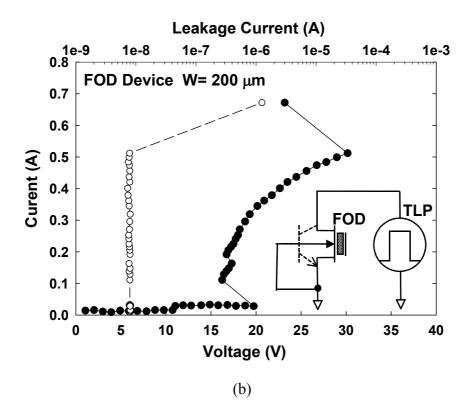

- **Fig. 4.5** The (a) cross-sectional view, and (b) TLP-measured I-V characteristic, of high-voltage field-oxide (FOD) device fabricated in a 0.25-μm 40-V CMOS process.

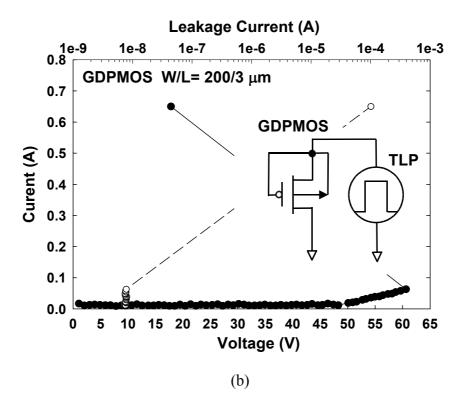

- **Fig. 4.6** The (a) cross-sectional view, and (b) TLP-measured I-V characteristic, of high-voltage gate-VDD pMOS (GDPMOS) device fabricated in a 0.25-μm 40-V CMOS process.

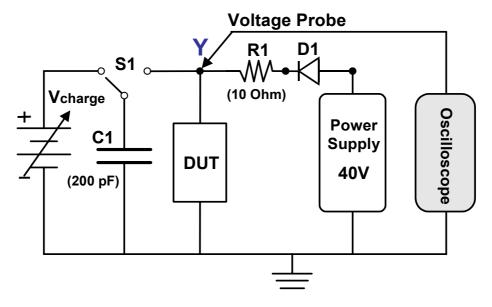

- **Fig. 4.7** The measurement setup for transient latchup (TLU) test.

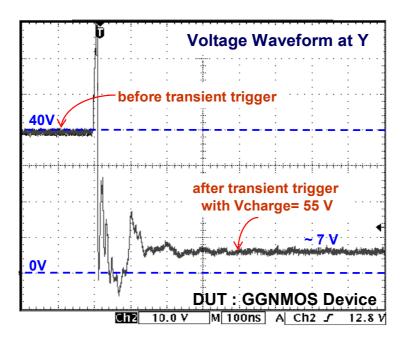

- **Fig. 4.8** The measured voltage waveform on the high-voltage GGNMOS device under TLU test. (Y axis= 10 V/Div., X axis= 100 ns/Div.)

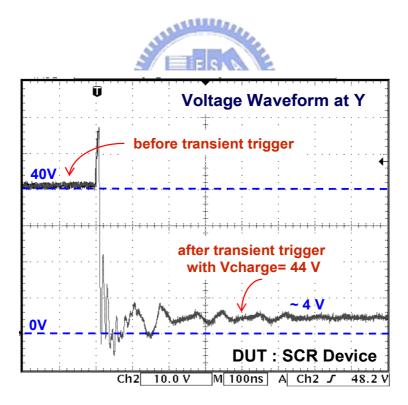

- Fig. 4.9 The measured voltage waveform on the high-voltage SCR device under TLU test. (Y axis = 10 V/Div., X axis = 100 ns/Div.)

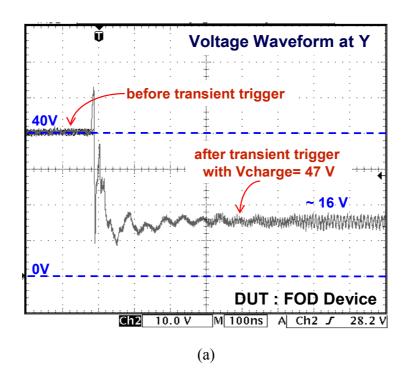

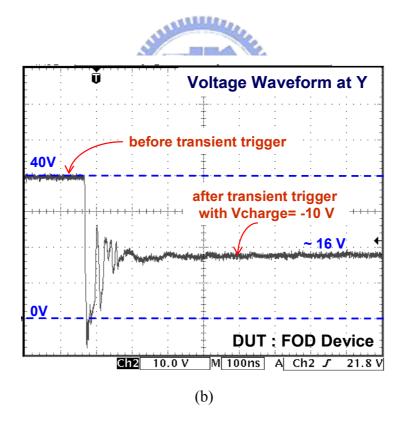

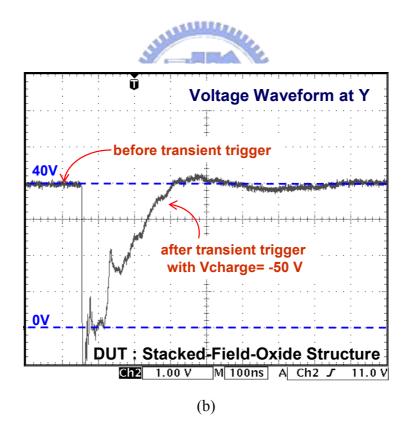

- **Fig. 4.10** The measured voltage waveforms on the high-voltage FOD device under TLU test with (a) positive charging voltage, and (b) negative charging voltage. (Y axis= 10 V/Div., X axis= 100 ns/Div.)

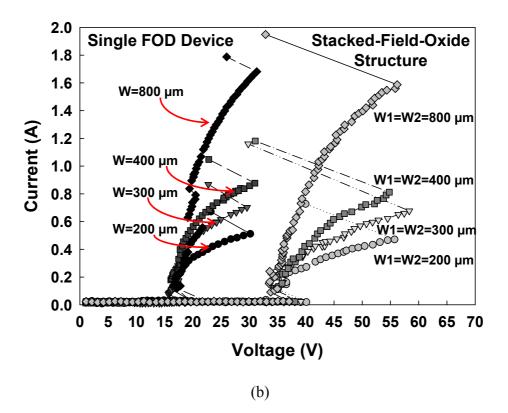

- **Fig. 4.11** (a) The measurement setup of single high-voltage FOD device and stacked-field-oxide structure under TLP stress. (b) The TLP-measured I-V characteristics of these devices with different device widths. W1 is the channel width of FOD1, and W2 is the channel width of FOD2.

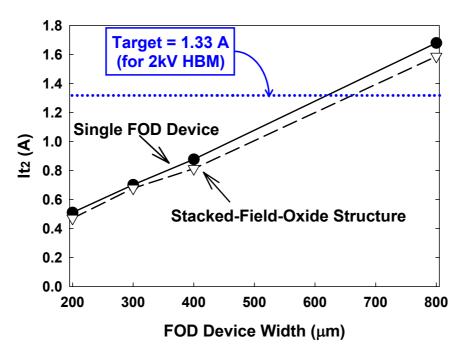

- **Fig. 4.12** It2 currents of single FOD device and stacked-field-oxide structure as a function of device channel width.

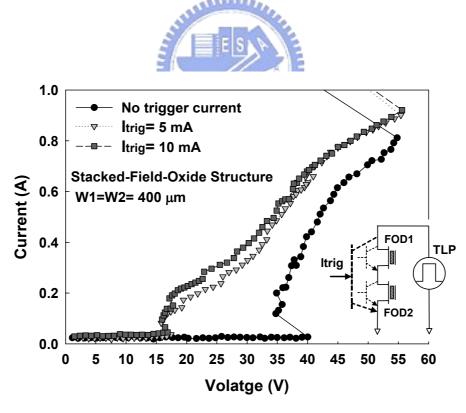

- **Fig. 4.13** The TLP-measured I-V curves of the stacked-field-oxide structure with different substrate-triggered currents.

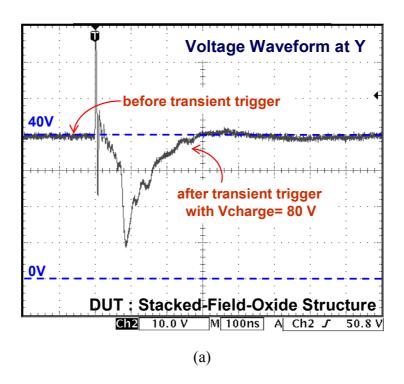

- **Fig. 4.14** The measured voltage waveforms on the stacked-field-oxide structure under TLU test with (a) positive charging voltage, and (b) negative charging voltage. (*Y* axis= 10 V/Div., *X* axis= 100 ns/Div.)

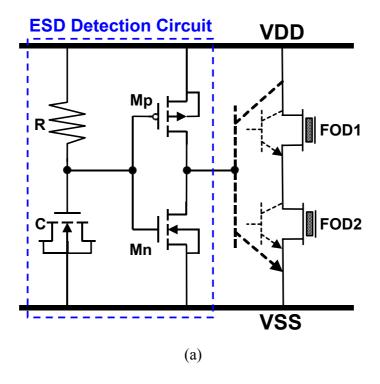

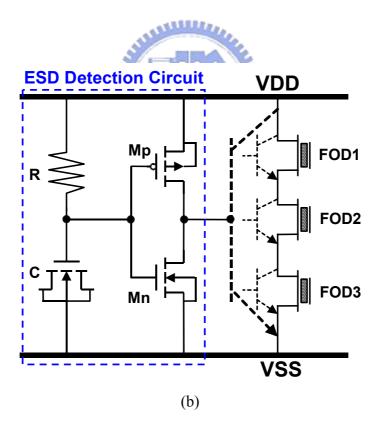

- **Fig. 4.15** The proposed power-rail ESD clamp circuits in high-voltage CMOS ICs with (a) two cascaded FOD devices, and (b) three cascaded FOD devices.

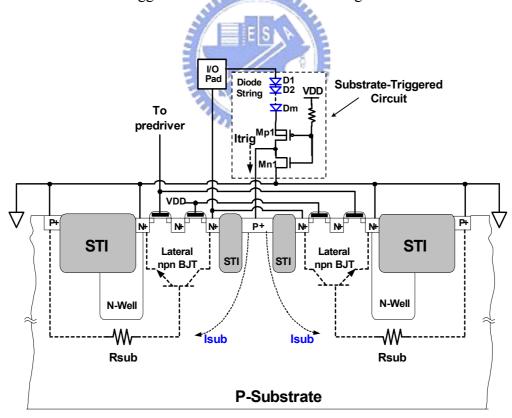

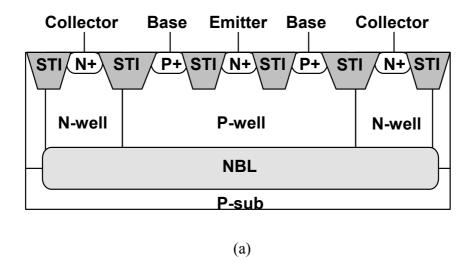

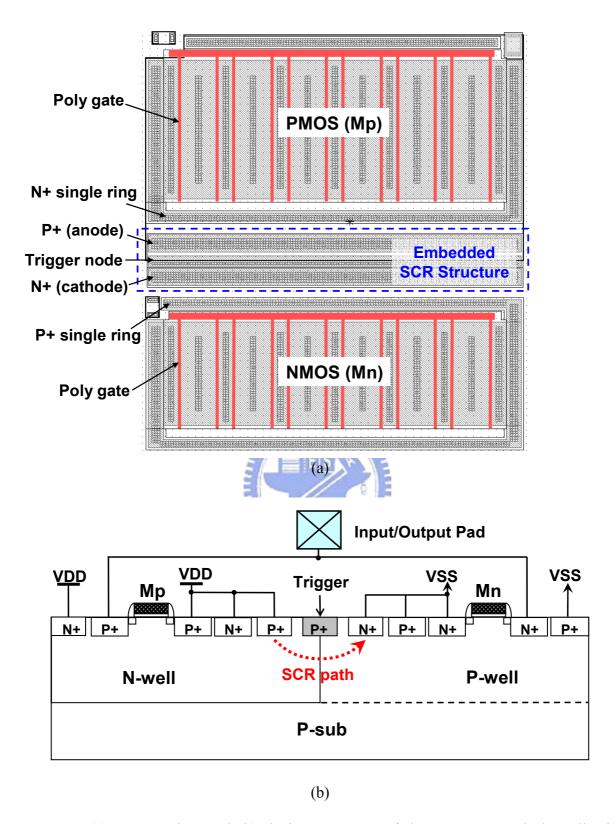

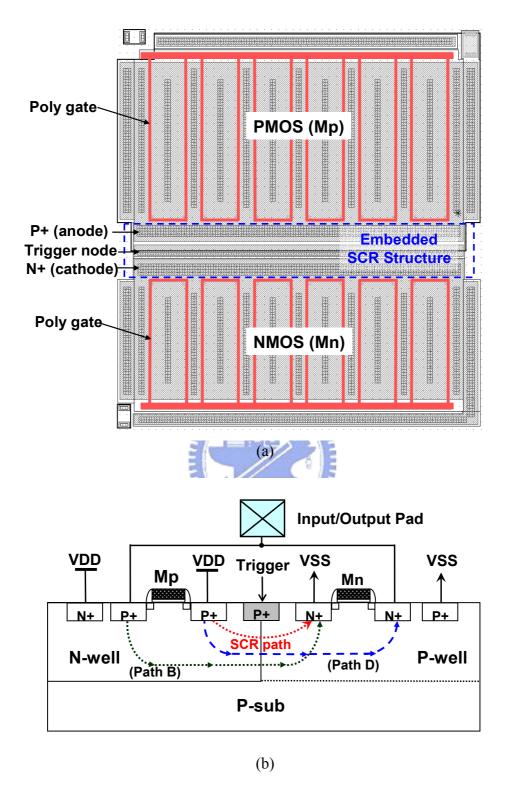

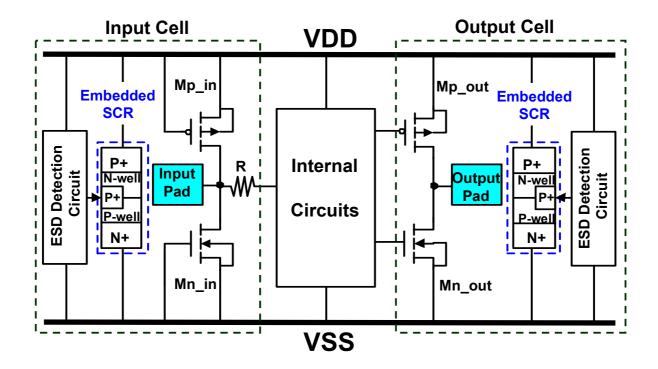

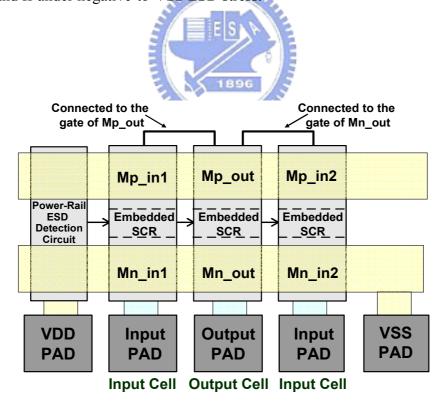

**Fig. 5.1** (a) Layout view and (b) device structures of the new proposed I/O cell with embedded SCR structure I. The anode and cathode of embedded SCR structure I are formed by inserting extra p+ diffusion in n-well and n+ diffusion in p-well, respectively.

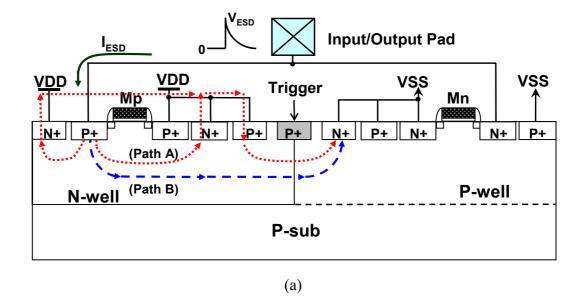

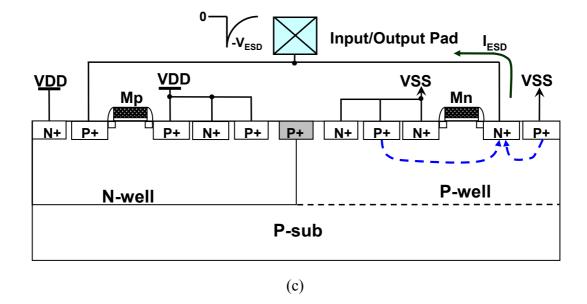

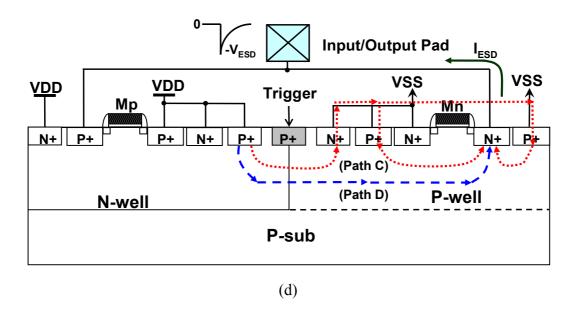

- **Fig. 5.2** The ESD current discharging paths of I/O cell with embedded SCR structure I under (a) positive-to-VSS ESD stress condition, (b) positive-to-VDD ESD stress condition, (c) negative-to-VSS ESD stress condition, and (d) negative-to-VDD ESD stress condition.

- **Fig. 5.3** (a) Layout view and (b) device structures of new proposed I/O cell with embedded SCR structure II. The anode and cathode of embedded SCR structure II are directly formed by the source of input (or output) pMOS and the source of nMOS, respectively.

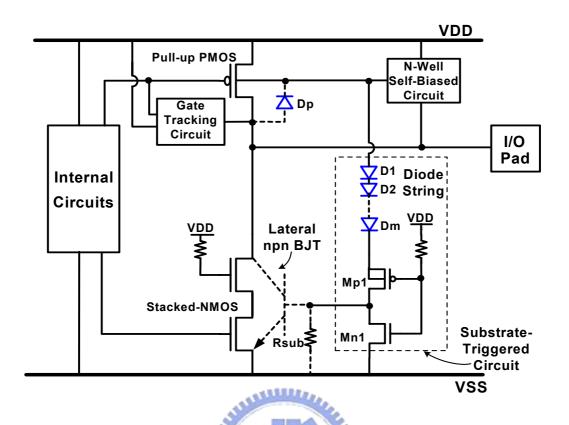

- **Fig. 5.4** The new proposed whole-chip ESD protection scheme with embedded SCR structure in each I/O cell. The substrate-triggered technique was realized by the RC-based ESD detection circuit.

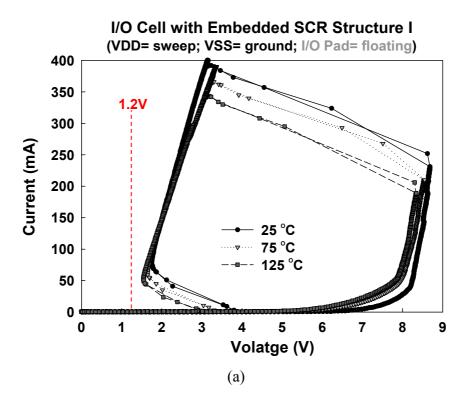

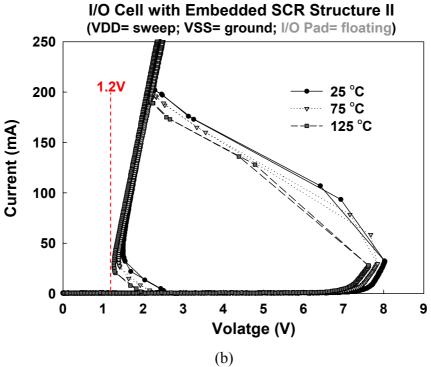

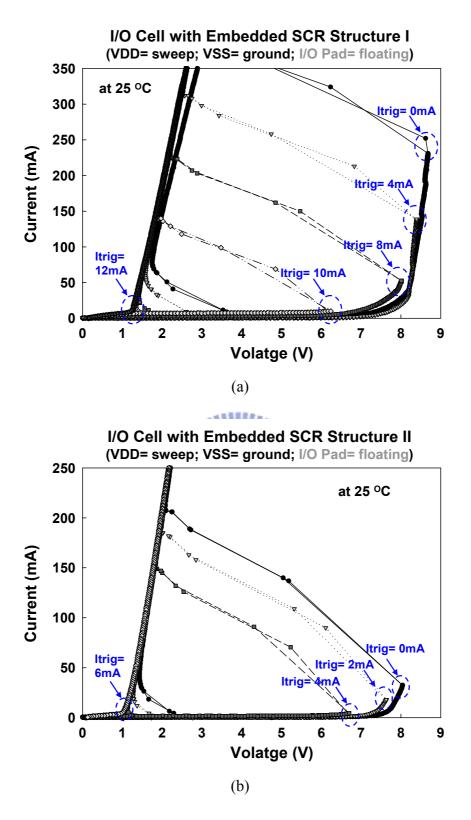

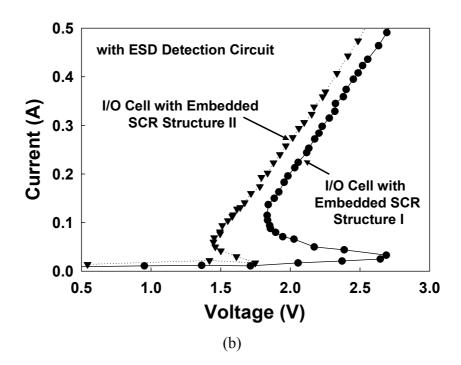

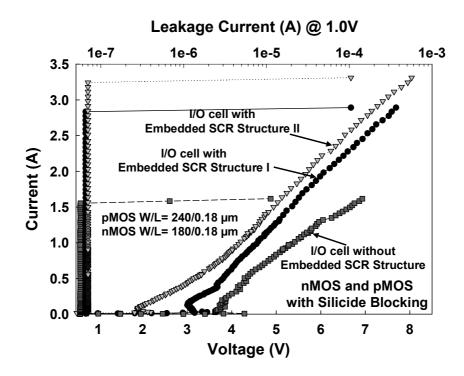

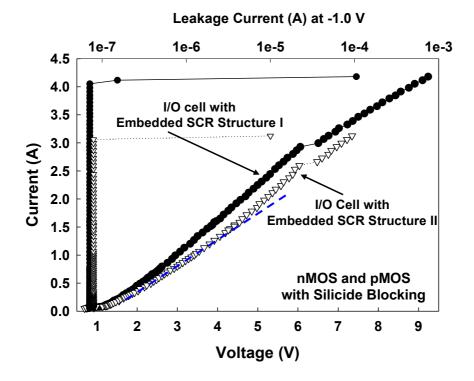

- **Fig. 5.5** The measured dc I-V characteristics of the (a) embedded SCR structure I, and (b) embedded SCR structure II, in the I/O cells under different temperatures.

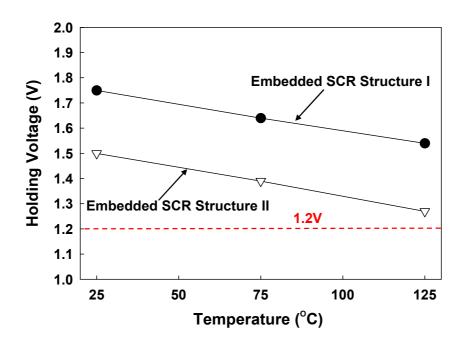

- **Fig. 5.6** The relation between the holding voltage of the embedded SCR structures and the operating temperature.

- Fig. 5.7 The measured dc I-V characteristics of the (a) embedded SCR structure I, and (b) embedded SCR structure II, in the I/O cells under different substrate-triggered currents (Itrig).

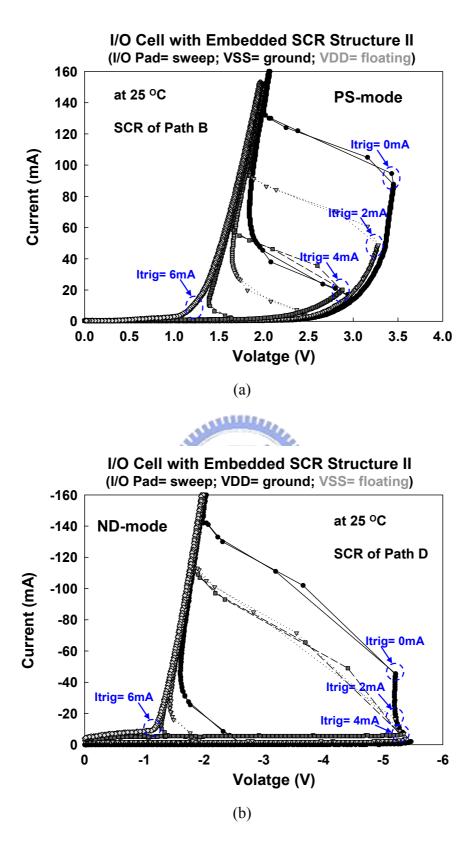

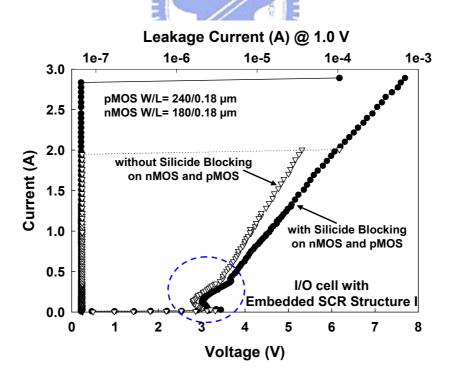

- Fig. 5.8 The measured dc I-V characteristics of (a) the parasitic SCR structure (path B) between I/O pad and VSS power line, and (b) the parasitic SCR structure (path D) between I/O pad and VDD power line, in the I/O cell with embedded SCR structure II under different substrate-triggered currents (Itrig).

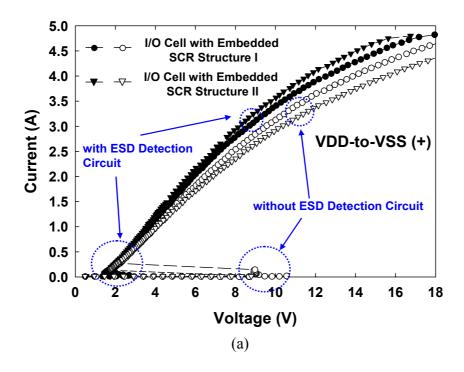

- **Fig. 5.9** (a) The TLP-measured I-V curves of the I/O cells with embedded SCR structures I and II under positive VDD-to-VSS ESD stress with or without ESD detection circuit. (b) The enlarged view around the switching point of the measured curves for I/O cells with ESD detection circuit.

- **Fig. 5.10** The TLP-measured I-V curves of the input pad under positive-to-VSS ESD stress with or without embedded SCR structure, where the I/O nMOS and pMOS are silicide-blocking but the embedded SCR structures are fully silicided.

- **Fig. 5.11** The TLP-measured I-V curves of the input pad under positive-to-VSS ESD stress with or without silicide blocking on the input pMOS and nMOS devices, whereas the embedded SCR structures are fully silicided.

- Fig. 5.12 The TLP-measured I-V curves of the I/O cells with embedded SCR structures I

- and II under negative-to-VSS ESD stress.

- **Fig. 5.13** The testchip to verify ESD robustness of the I/O cells with embedded SCR structures. The output buffer of pMOS (Mp\_out) and nMOS (Mn\_out) in output cell are individually controlled by the input cells.

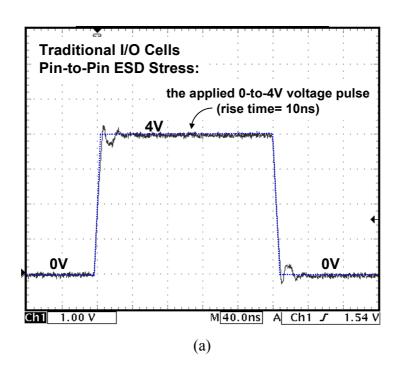

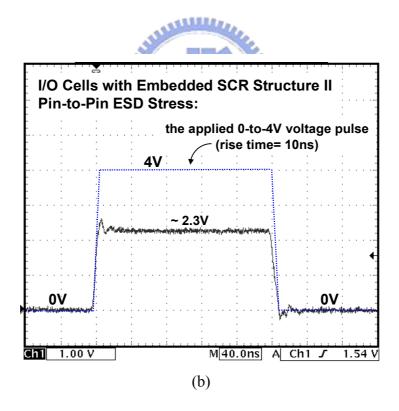

- **Fig. 5.15** Measured voltage waveforms on the I/O pads triggered by a 0-to-4V voltage pulse with a rise time of 10ns for the (a) traditional I/O cells, and (b) new proposed I/O cells with embedded SCR structure II, under pin-to-pin ESD stress condition. (*Y* axis: 1 V/div., *X* axis: 40 ns/div.)

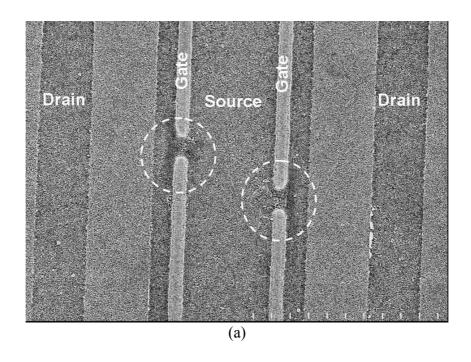

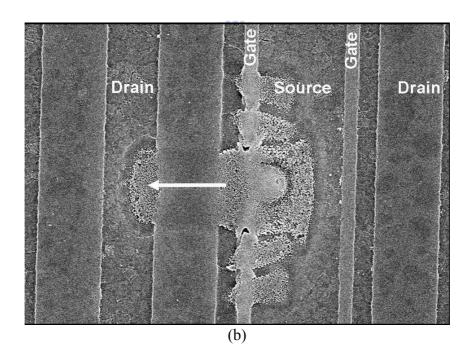

- **Fig. 5.14** (a) The failure location at the input nMOS device for the I/O cells with embedded SCR structure I under positive-to-VSS ESD stress. (b) The failure location at the input nMOS device for the I/O cells with embedded SCR structure II under negative-to-VSS ESD stress.

- **Fig. 5.15** Measured voltage waveforms on the I/O pads triggered by a 0-to-4V voltage pulse with a rise time of 10ns for the (a) traditional I/O cells, and (b) new proposed I/O cells with embedded SCR structure II, under pin-to-pin ESD stress condition. (*Y* axis: 1 V/div., *X* axis: 40 ns/div.)

# **INTRODUCTION**

## 1.1 Background