## 國立交通大學

電子工程學系電子研究所

博士論文

低電壓互補式金氧半製程下的高電壓電路設計

# HIGH-VOLTAGE CIRCUIT DESIGN IN LOW-VOLTAGE CMOS PROCESSES

研究生:陳世倫(Shih-Lun Chen)

指導教授 :柯 明 道 (Ming-Dou Ker)

中華民國九十五年七月

## 低電壓互補式金氧半製程下的高電壓電路設計

## HIGH-VOLTAGE CIRCUIT DESIGN IN LOW-VOLTAGE CMOS PROCESSES

研究生:陳世倫 Student: Shih-Lun Chen

指導教授:柯明道 Advisor: Ming-Dou Ker

#### **A Dissertation**

Submitted to Department of Electronics Engineering and Institute of Electronics

College of Electrical and Computer Engineering National Chiao Tung University in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

in Electronic Engineering

July 2006 Hsinchu, Taiwan, Republic of China

中華民國九十五年七月

## 低電壓互補式金氧半製程下的高電壓電路設計

研究生:陳世倫 指導教授:柯明道 博士

## 國立交通大學電子工程學系電子研究所

## 摘要

本論文提出數個在低電壓互補式金氧半(CMOS)製程下所設計的高電壓電路。隨著互補式金氧半製程的進步,積體電路(Integrated Circuit)的操作速度越來越快而電晶體(Transistor)的面積越來越小。由於積體電路可靠度(Reliability)的問題,電晶體的正常操作電壓(Normal Operation Voltage)必需隨著製程進步而降低。另一方面,由於系統晶片(System-on-a-Chip,SOC)的設計趨勢,單一晶片裡將包含許多不同類形的電路。所以在一個系統晶片裡,部分電路仍然必需操作在高電壓的環境裡。如果利用低電壓製程所設計的積體電路操作在高電壓的環境,開極氧化層可靠度(Gate-Oxide Reliability)、熱載子衰退效應(Hot-Carrier Degradation)、漏電流(Leakage Current)等現象將會發生。所以本論文提出了數個低電壓互補式金氧半製程下所設計的高電壓電路,且無關極氧化層可靠度、熱載子衰退效應、漏電流等問題。本論文所提出的電路適合實現在深次微米(Deep Sub-Micron Meter),甚至是奈米(Nano Meter)互補式金氧半製程裡。本論文共包含七個章節。

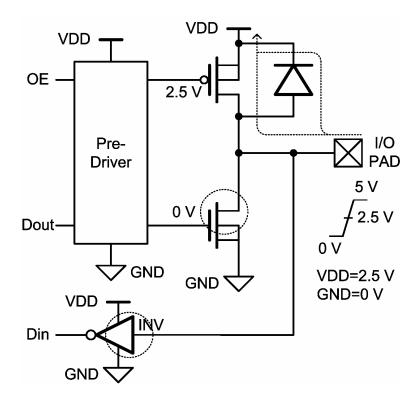

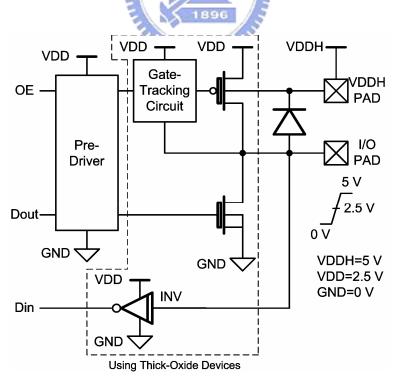

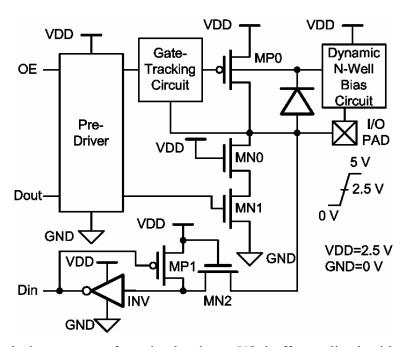

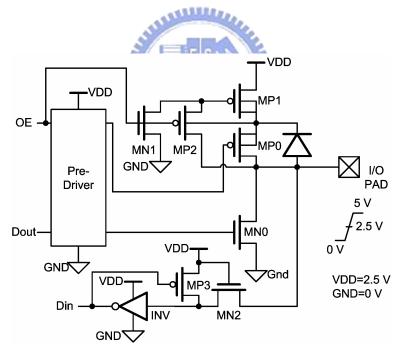

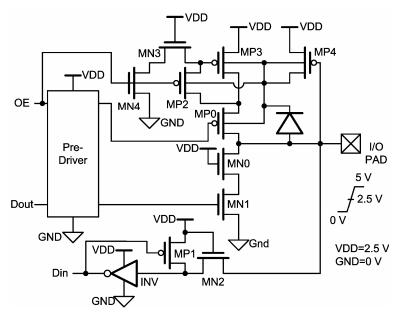

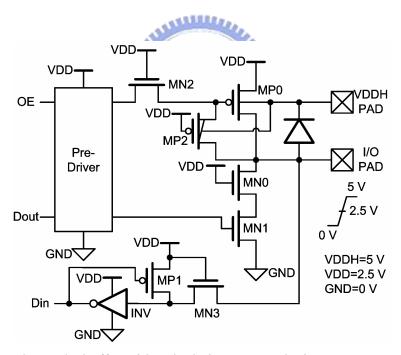

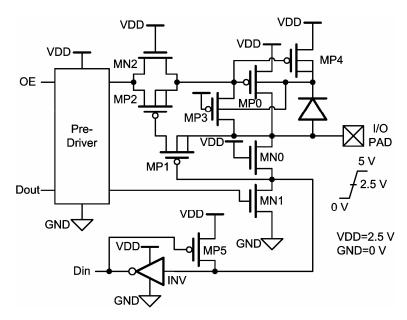

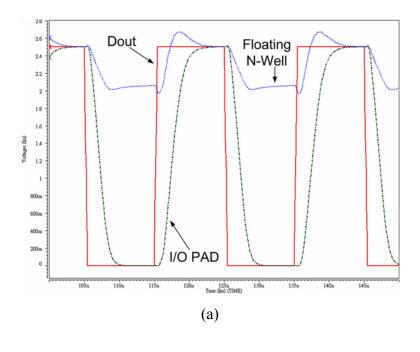

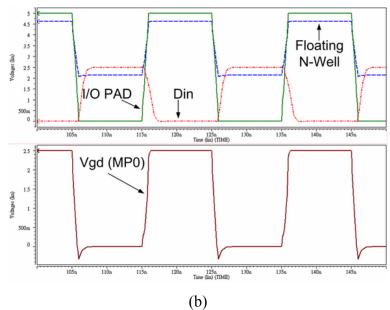

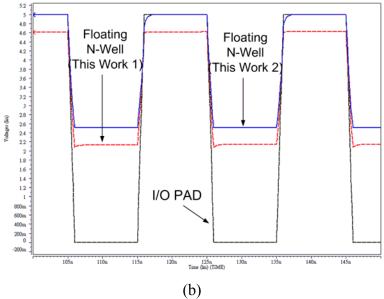

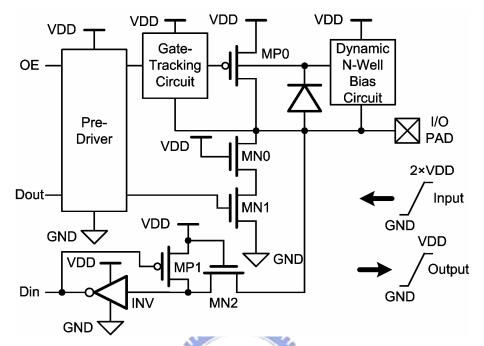

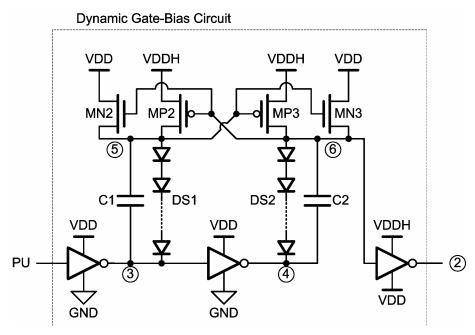

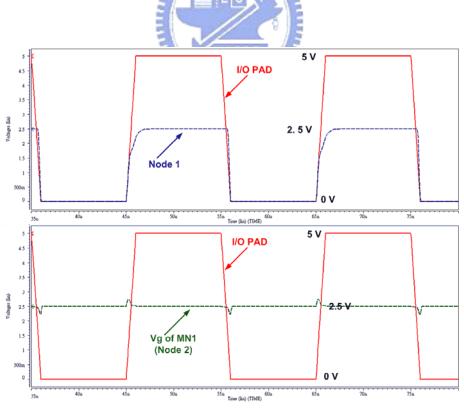

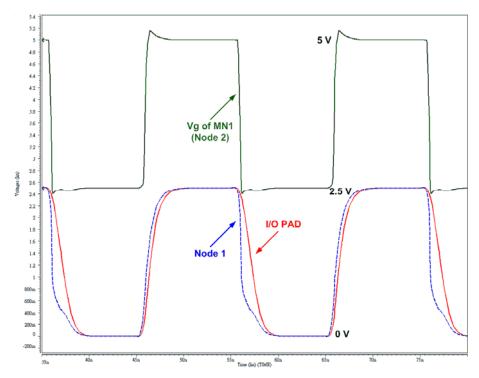

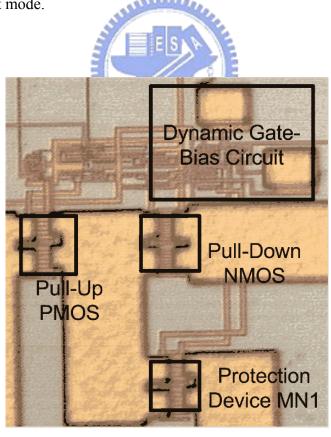

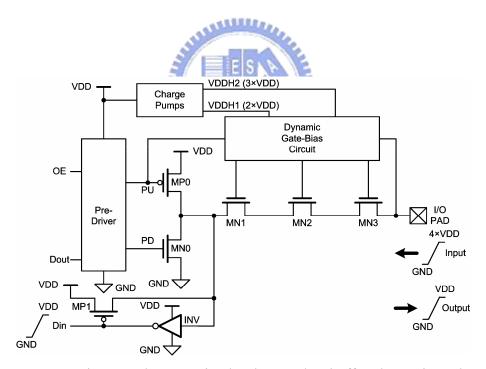

在第二章中,本論文提出了兩個利用低電壓元件所實現的混合電壓介面輸入輸出電路(Mixed-Voltage I/O Buffer)。這兩個混合電壓介面輸入輸出

電路擁有新型的動態 N 阱偏壓電路(Dynamic N-Well Bias Circuit)和閘極電壓追蹤電路(Gate-Tracking Circuit)來避免混合電壓介面(Mixed-Voltage Interface)所造成的漏電流的問題。此外,這兩個混合電壓介面輸入輸出電路也避免了閘極電壓過高所造成的閘極氧化層可靠度問題。跟先前的混合電壓介面輸入輸出電路比較,本論文所提出的兩個利用低電壓元件所實現的混合電壓介面輸入輸出電路擁有較小的面積。此外,本論文所提出的第二個混合電壓介面輸入輸出電路解決了浮接 N 阱(Floating N-Well)的現象,將可大量減少次臨介漏電流(Subthreshold Leakage Current)的問題。其更適用於先進製程下的設計。本論文所提出的兩個利用低電壓元件所實現的混合電壓介面輸入輸出電路已經在 2.5 伏 0.25 微米互補式金氧半製程裡實現並驗證。

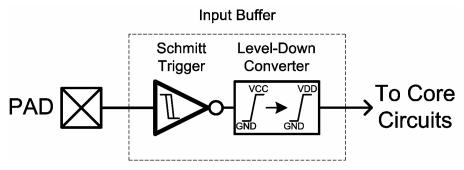

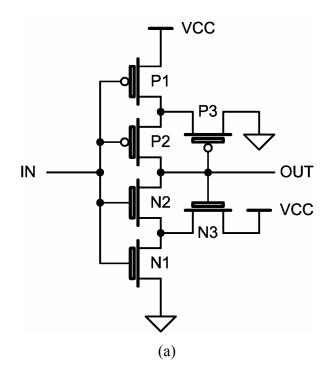

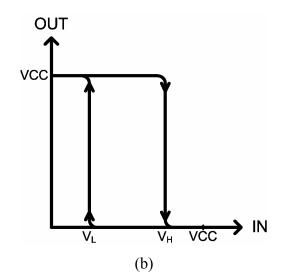

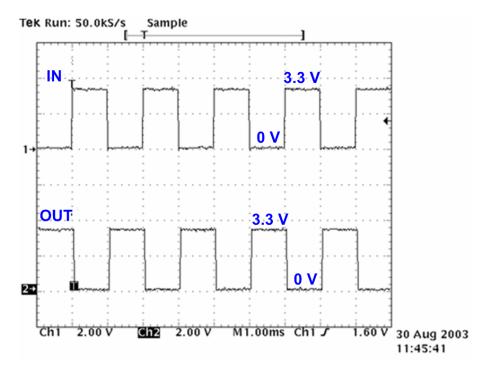

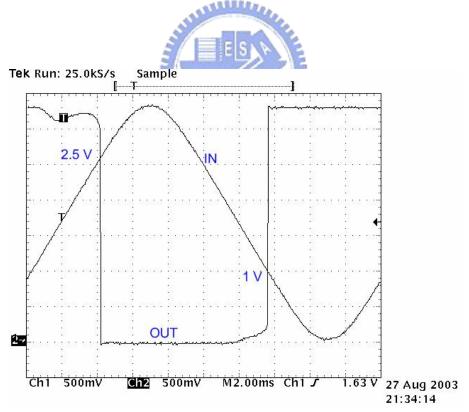

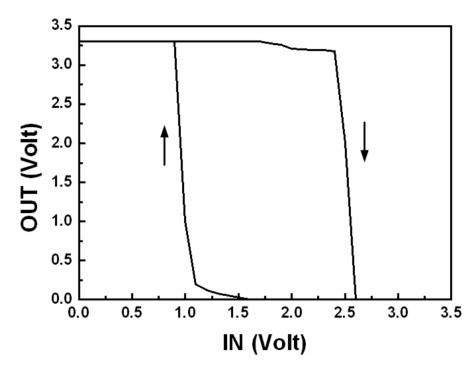

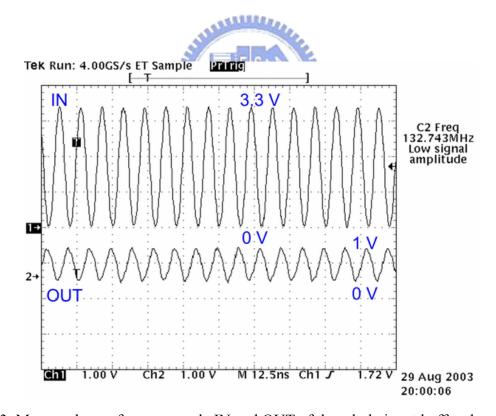

由於系統晶片的需求,單一晶片內可能包含數位電路以及類比電路。以 1/2.5 伏 0.13 微米互補式金氧半製程來說,數位電路用 1 伏元件來實現以減少功率消耗(Power Consumption)和矽面積(Silicon Area),類比電路以2.5 伏元件來實現以保持電路的效能(Performance),但此系統晶片的介面是3.3 伏,例如 PCI-X 的介面。因此,在第三章中,提出了應用在3.3 伏的環境且利用 1/2.5 伏製程所實現的輸入電路和輸出電路。此外,一個新型的史密特觸發器(Schmitt Trigger)和電壓準位轉換器(Level Converter)分別被應用在所提出的輸入電路和輸出電路。本論文所提出應用在3.3 伏環境的輸入電路和輸出電路已經在1/2.5 伏 0.13 微米互補式金氧半製程裡實現並已在3.3 伏的操作環境下驗證。

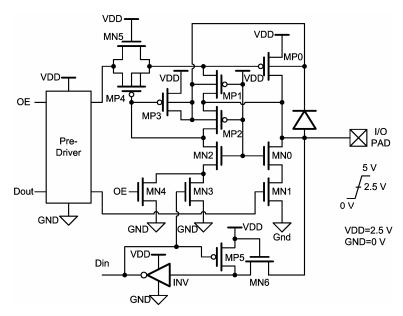

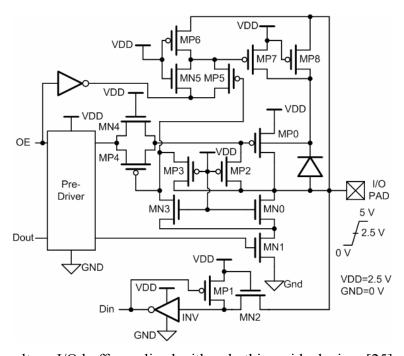

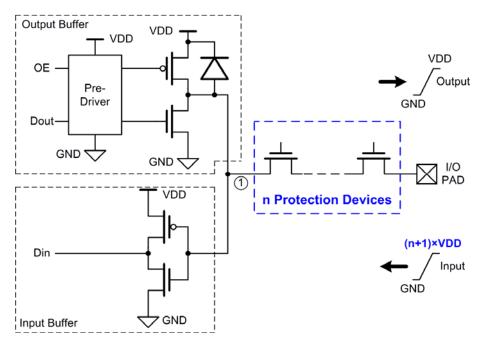

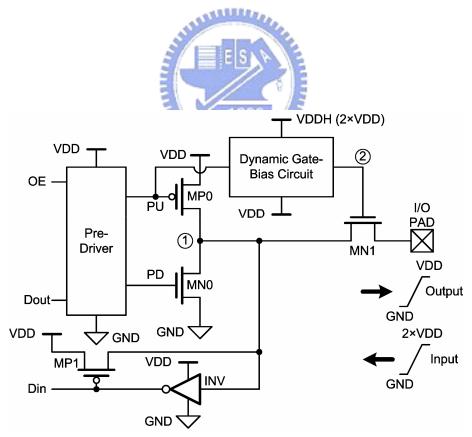

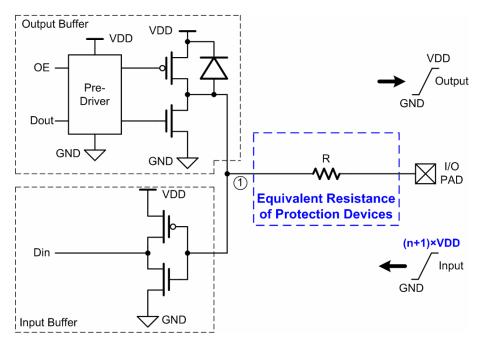

有別於傳統的混合電壓介面輸入輸出電路使用動態N阱偏壓電路和閘極電壓追蹤電路來避免漏電流以及閘極氧化層可靠度的問題。在第四章中,本論文提出了用N型金氧半場效電晶體(NMOS)阻隔的技巧來設計混合電壓介面輸入輸出電路。使用此N型金氧半場效電晶體阻隔的技巧不但

能設計出接收兩倍操作電壓輸入訊號的混合電壓介面輸入輸出電路,甚至可設計三倍、四倍、五倍操作電壓輸入訊號的混合電壓介面輸入輸出電路。 其限制在於寄生 PN 接面(PN-Junction)的崩潰電壓(Breakdown Voltage)。利用所提出的 N 型金氧半場效電晶體阻隔的技巧所設計的接收兩倍操作電壓輸入訊號的混合電壓介面輸入輸出電路已經在 2.5 伏 0.25 微米互補式金氧半製程裡實現並在 2.5/5 伏的混合電壓介面下驗證。而利用所提出的 N 型金氧半場效電晶體阻隔的技巧所設計的接收三倍操作電壓輸入訊號的混合電壓介面輸入輸出電路已經在 1 伏 0.13 微米互補式金氧半製程裡實現並在 1/3 伏的混合電壓介面下驗證。

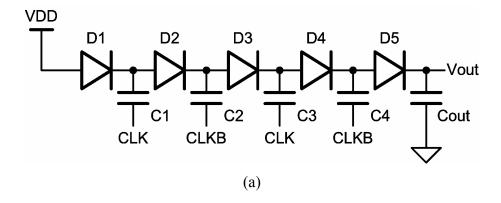

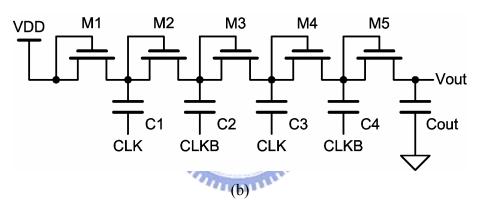

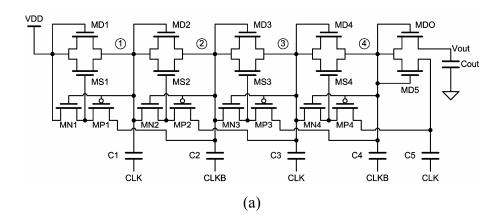

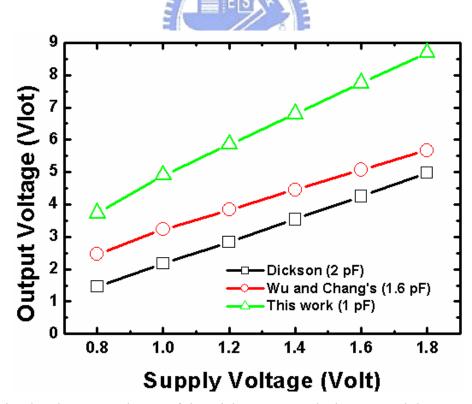

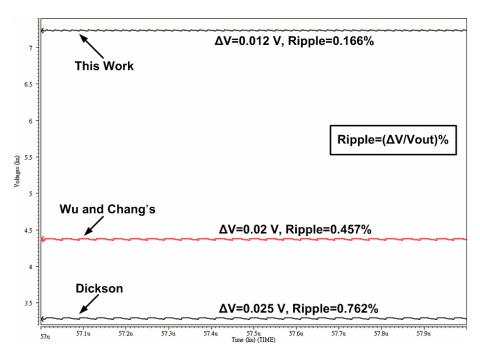

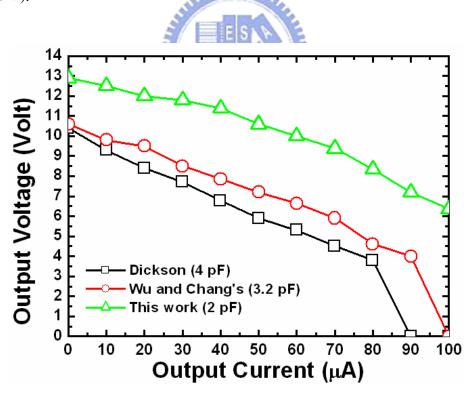

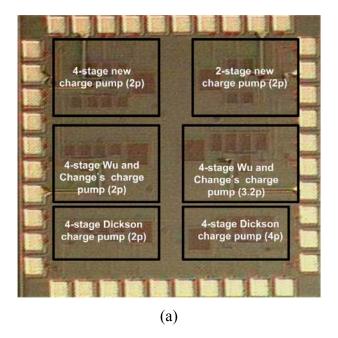

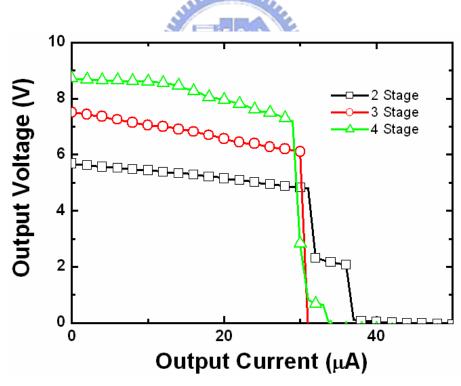

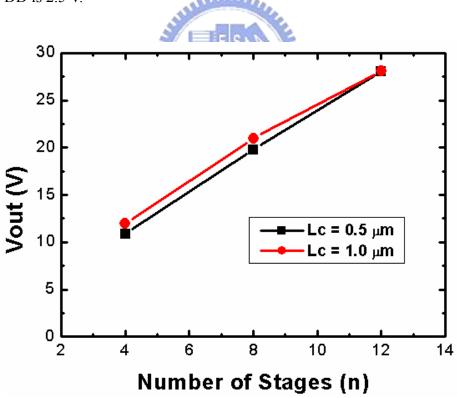

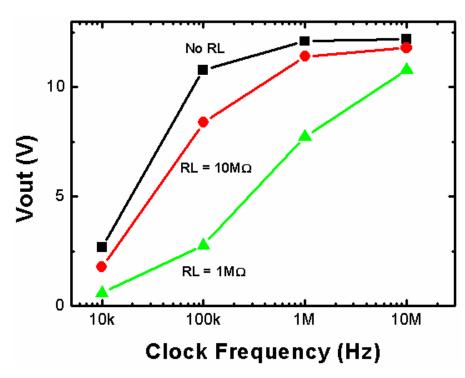

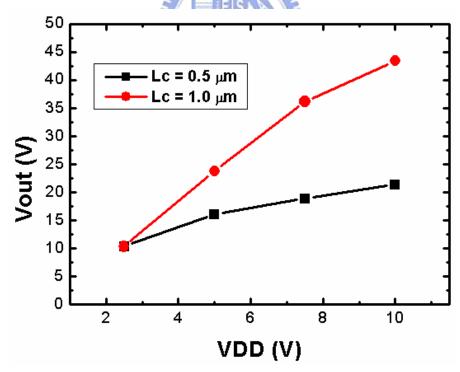

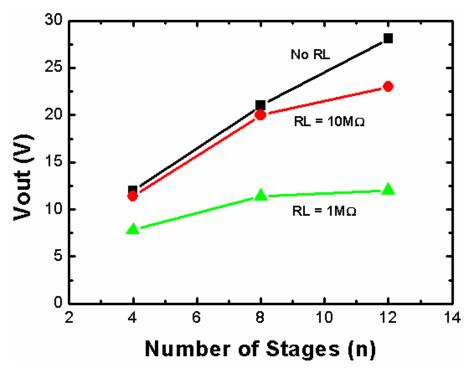

電荷幫浦電路(Charge Pump Circuit)是用來產生一個高於電源電壓 (Power Supply Voltage)的輸出電壓。當利用低電壓元件來設計傳統的電荷幫 浦電路時,將會發生嚴重的閘極氧化層可靠度問題。因此,在第五章中,本論文提出了一個新型的電荷幫浦電路,其避免了閘極電壓過高所造成的 閘極氧化層可靠度問題。此外,本論文所提出的電荷幫浦電路有較好的效能(Performance)其輸出的漣波電壓(Output Voltage Ripple)也比傳統的電荷幫浦電路小。本論文所提出的電荷幫浦電路已經在 3.3 伏 0.35 微米互補式金氧半製程裡實現並驗證。

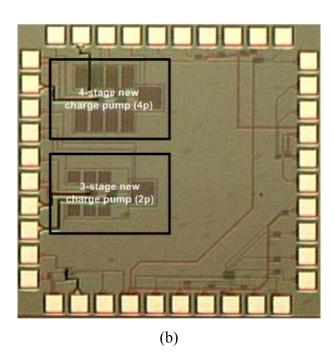

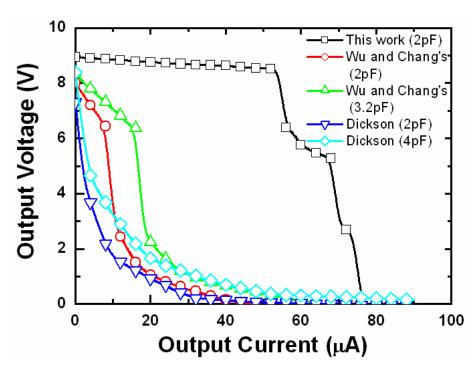

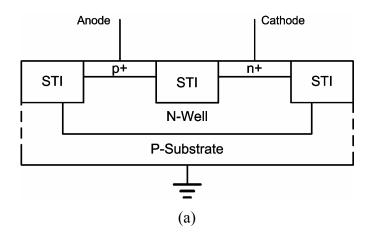

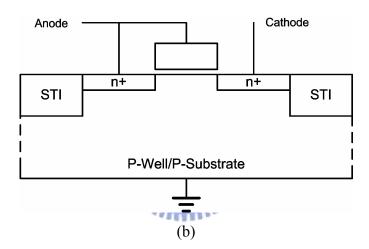

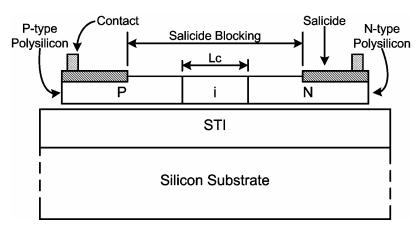

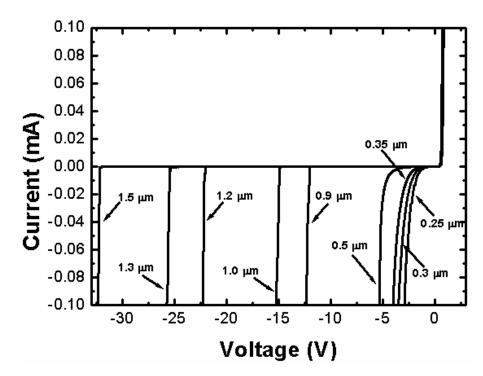

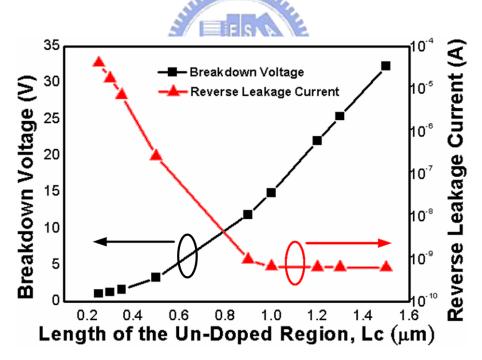

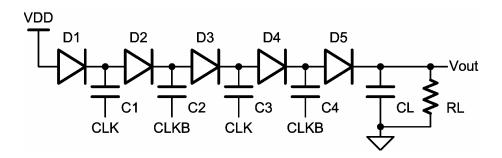

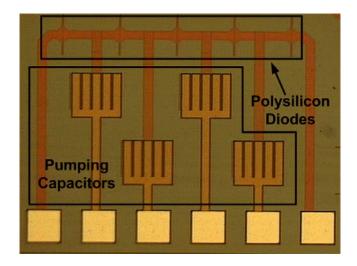

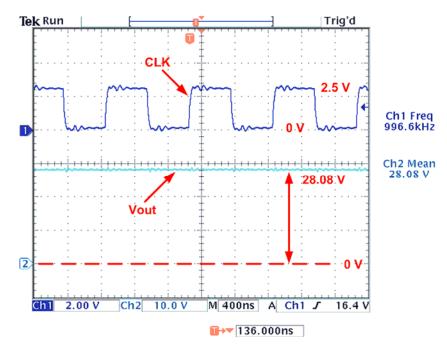

在互補式金氧半製程裡實現電荷幫浦電路,其輸出電壓將會被寄生 PN接面的崩潰電壓所限制。此外,隨著互補式金氧半製程的進步,寄生 PN接面的崩潰電壓也隨著降低。由於系統晶片的需求,在低電壓製程裡產生一個高電壓是必需的。因此,在第六章中,本論文提出了用多晶矽二極體(Polysilicon Diode)所實現的電荷幫浦電路。此多晶矽二極體利用淺溝隔絕層(Shallow Trench Isolation Layer)與基底(Substrate)相隔絕,所以流經此多晶矽二極體的電荷不會經由寄生 PN接面的崩潰流失到基底。換句話說,本論文提出用多晶矽二極體所實現的電荷幫浦電路,其輸出電壓不會被寄

生 PN 接面的崩潰電壓所限制。此外,多晶矽二極體並不會增加額外的製程步驟,其與標準的互補式金氧半製程相容(Compatible)。本論文提出用多晶矽二極體所實現的電荷幫浦電路已經在 2.5 伏 0.25 微米標準互補式金氧半製程裡實現並驗證。其輸電壓遠高於寄生 PN 接面的崩潰電壓。

在本博士論文中提出數個在低電壓互補式金氧半製程下所設計的高電 壓電路。所提出的電路已在實際晶片上成功驗証,並有相對應的國際會議 論文、國際期刊論文發表與專利申請。

## HIGH-VOLTAGE CIRCUIT DESIGN IN LOW-VOLTAGE CMOS PROCESSES

Student: Shih-Lun Chen Advisor: Dr. Ming-Dou Ker

Department of Electronics Engineering and Institute of Electronics

National Chiao Tung University

## ABSTRACT

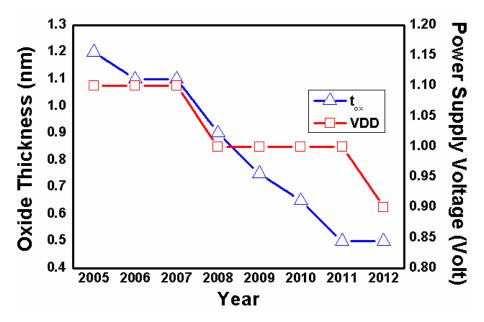

The scaling trend of the CMOS technology is toward the nanometer region to increase the speed and density of the transistors in integrated circuits. Due to the reliability issue, the power supply voltage is also decreased with the advanced technologies. However, in an electronic system, some circuits could be still operated at high voltage levels. If the circuits realized with low-voltage devices are operated at high voltage levels, the gate-oxide breakdown, hot-carrier degradation, leakage issues, and so on will occur. Therefore, designing the high-voltage circuits in low-voltage CMOS processes is an important topic in today and future VLSI (very large scale integration) design. In this dissertation, several circuits designed in low-voltage CMOS processes but operated in high-voltage environments are presented. There are seven chapters included in this dissertation.

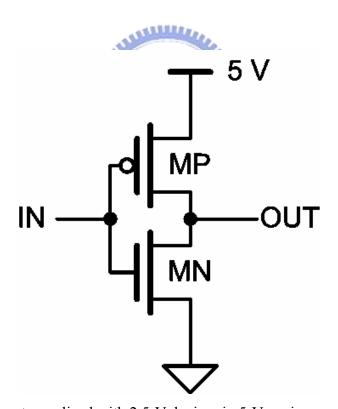

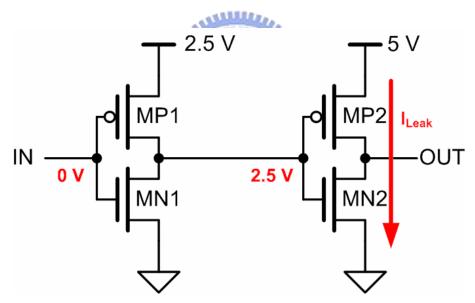

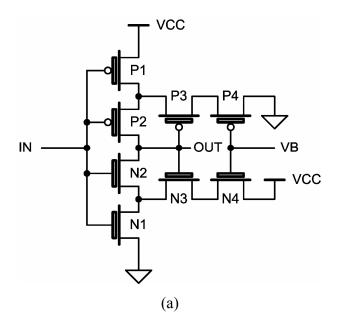

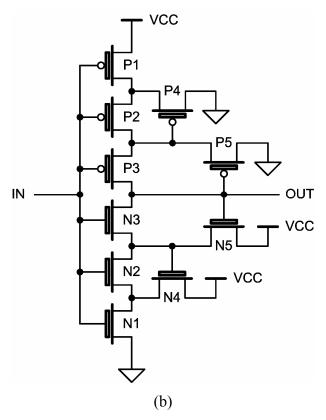

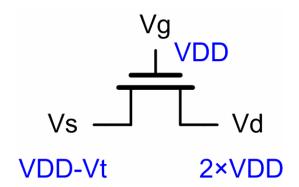

Two new mixed-voltage I/O buffers realized with low-voltage devices are presented in Chapter 2 to prevent the undesired leakage current paths and the gate-oxide reliability problem, which occur in the conventional CMOS I/O buffer. These two new mixed-voltage I/O buffer have novel gate-tracking circuits and dynamic n-well bias circuits. Compared with the prior designs of mixed-voltage I/O buffers, these two new mixed-voltage I/O buffers occupy smaller silicon area. Besides, the new proposed mixed-voltage I/O buffer 2 can be applied for high-speed applications without the gate-oxide reliability problem and the circuit leakage issue. The new proposed mixed-voltage I/O buffers realized with 1×VDD devices

can be easily applied in 1×VDD/2×VDD mixed-voltage interface.

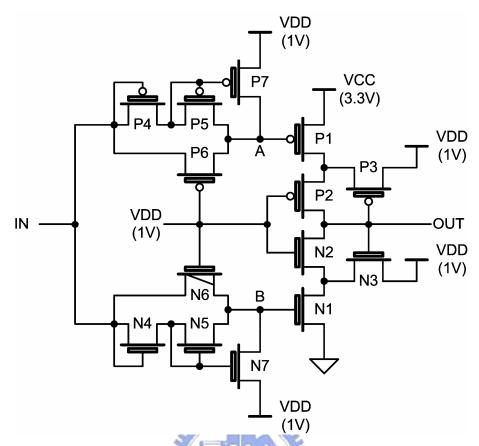

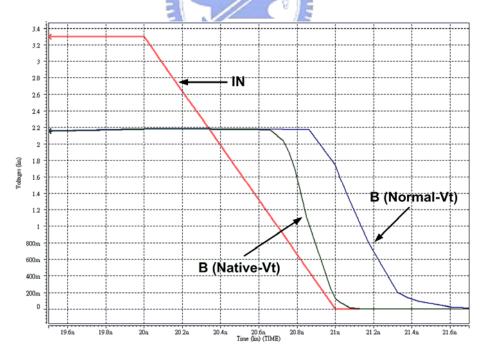

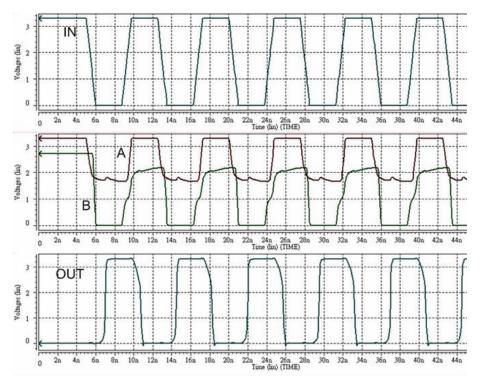

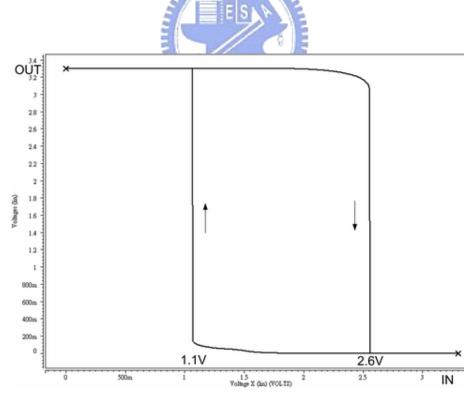

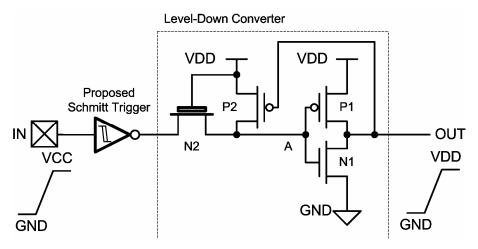

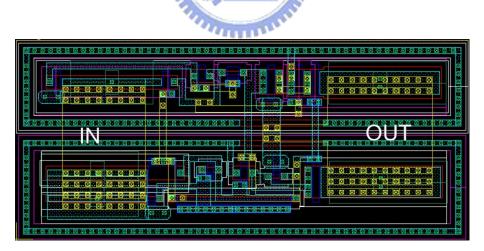

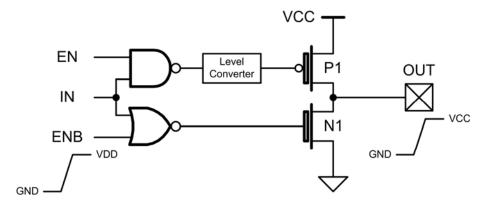

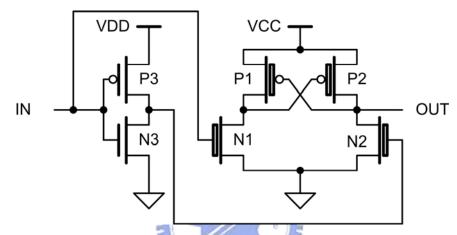

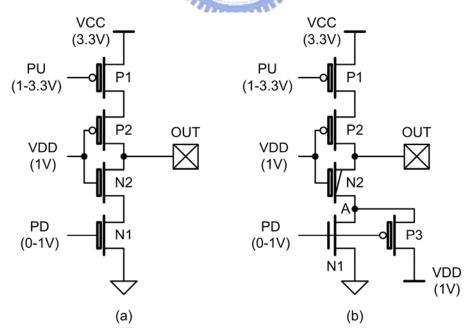

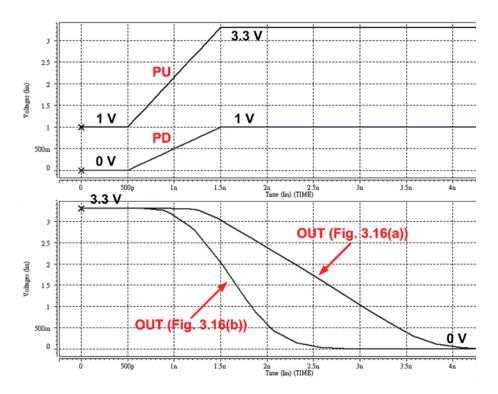

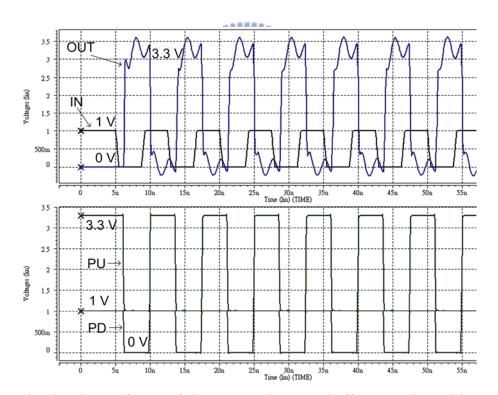

Due to the high-integration trend of SOC (system-on-a-chip), an electronic system may be integrated into a single chip. Hence, there are digital circuits and analog circuits integrated in a single chip. For example, the digital part of the SOC is designed with 1-V devices to decrease its power consumption, the analog part is designed with 2.5-V devices to improve the circuit performance, and the chip-to-chip interface is 3.3-V PCI-X in a 0.13-μm 1/2.5-V CMOS process. Thus, the traditional I/O circuits are not suitable for this application. An input buffer with the proposed Schmitt trigger circuit and an output buffer with the proposed level converter in a 0.13-μm 1/2.5-V CMOS process are presented in Chapter 3 for 3.3-V applications.

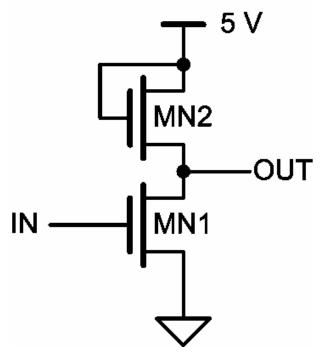

An NMOS-blocking technique for mixed-voltage I/O buffer design is presented in Chapter 4. Unlike the traditional mixed-voltage I/O buffer design, the mixed-voltage I/O buffer realized with only 1×VDD devices by using the NMOS-blocking technique can receive 2×VDD, 3×VDD, and even 4×VDD input signals without the gate-oxide reliability issue. In this dissertation, the 2×VDD input tolerant mixed-voltage I/O buffer by using the NMOS-blocking technique has been verified in a 0.25-µm 2.5-V CMOS process to serve 2.5/5-V mixed-voltage interface. The 3×VDD input tolerant mixed-voltage I/O buffer by using the NMOS-blocking technique has been verified in a 0.13-µm 1-V CMOS process to serve 1/3-V mixed-voltage interface. The NMOS-blocking technique can be extended to design the 4×VDD, 5×VDD, and even 6×VDD input tolerant mixed-voltage I/O buffers. The limitation of the NMOS-blocking technique is the breakdown voltage of the pn-junction in the given CMOS process.

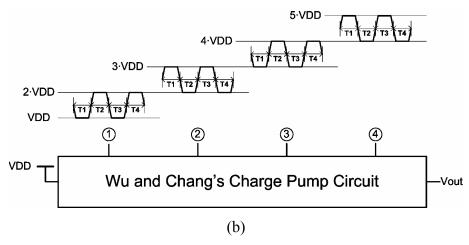

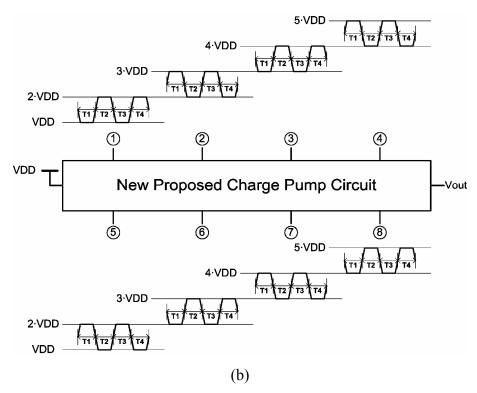

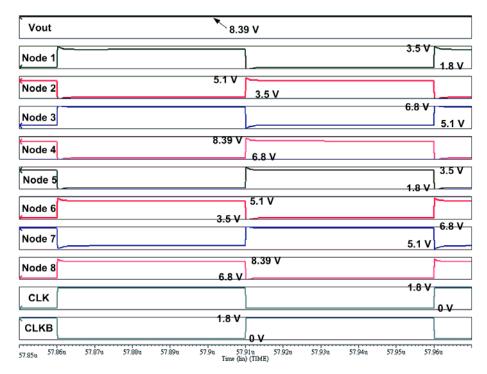

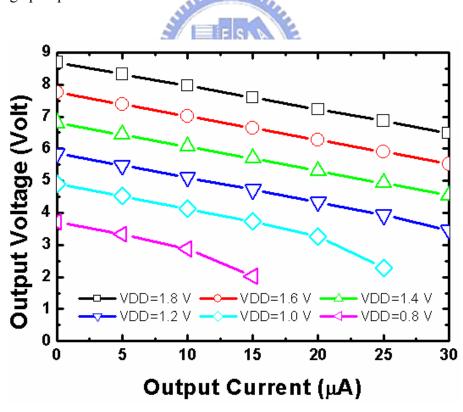

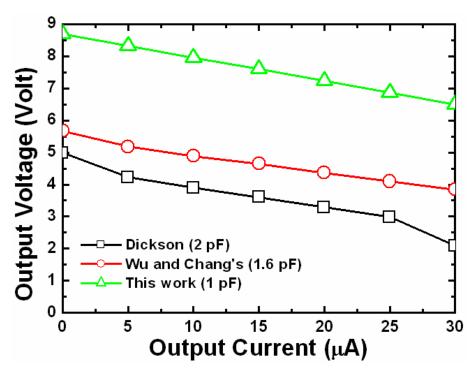

A new charge pump circuit without the gate-oxide overstress is presented in Chapter 5. Because the charge transfer switches of the new proposed charge pump circuit can be fully turned on and turned off, as well as the output stage doesn't have the threshold drop problem, its pumping efficiency is higher than that of the prior designs. The gate-drain and the gate-source voltages of all devices in the new charge pump circuit don't exceed VDD, so the new charge pump circuit doesn't suffer the gate-oxide reliability problem. Besides, the proposed charge pump circuit has two pumping branches pumping the output node alternately so the output voltage ripple is small. The proposed circuit is suitable in low-voltage CMOS processes because of its high pumping efficiency and no overstress across the gate oxide of devices.

In general, the output voltage of the charge pump circuit will be limited by the breakdown voltage of the parasitic pn-junction in the given CMOS process. Chapter 6

presents an on-chip ultra-high-voltage charge pump circuit designed with the polysilicon diodes in low-voltage standard CMOS processes. Because the polysilicon diodes are fully isolated from the silicon substrate, the output voltage of the charge pump circuit is not limited by the junction breakdown voltage of parasitic pn-junction. The polysilicon diodes can be implemented in the standard (bulk) CMOS processes without extra process steps. The proposed charge pump circuit designed with the polysilicon diodes has been fabricated and verified in a 2.5-V 0.25-µm bulk CMOS process.

In summary, several circuits designed in low-voltage CMOS processes but operated in high-voltage environments are presented in this dissertation. The proposed circuits have been implemented and verified in silicon chips. The proposed circuits are very useful and cost-efficient for the advanced SOC applications.

### **ACKNOWLEDGEMENTS**

在交通大學電子研究所的生涯中,首先要感謝我的指導教授柯明道教授在這些年來耐心的指導與鼓勵,使我能順利完成博士學業。不只在專業領域上的知識,從柯教授認真的研究態度和嚴謹的處事原則,也讓我學習到克服困難、解決問題的正確態度與方法。此外,感謝 307 實驗室另外四位師長,吳重雨教授、吳錦川教授、吳介琮教授以及陳巍仁教授給我的指導與建議。

感謝黃弘一教授帶領我進入積體電路設計的殿堂,奠定了我在電路設計上的基礎。還有感謝周世傑教授、馬金溝博士、鄭國興教授在百忙之中抽空來擔任我的口試委員,給我指導跟建議,讓整個論文更加完整。

感謝廖以義博士,在我初來到交通大學時,給我許多生活、學業上的建議與幫助。還有謝謝其他 307 實驗室的成員陳東暘博士、林子超博士、施育全博士、周忠昀博士、徐國鈞博士、林坤賢博士,林俐如、周儒明、李瑞梅、范啟威、王文傑、范振麟、翟芸、陳崇昇、許勝福、鄧至剛、徐新智、蘇烜毅、虞繼堯、張瑋仁、曾偉信、顏承正、蕭淵文、李健銘、陳世宏、陳志豪、陳煒明、王暢資、王資閔等學長姐、同學、學弟們在課業、研究、生活上的幫忙與協助,讓我順利完成我的博士論文、並學習到做人處事上的態度與方法。此外,感謝歷任 307 實驗室的助理李婷媛小姐、卓慧貞小姐在實驗室行政事務上的許多協助。

致上最深的感謝給我親愛的家人們,祖母林玉雲女士、父親陳祐榮先生、母親鄭素嬌女士、弟弟陳亞倫、妹妹陳亞雯以及其他家人們。有了您們的支持、鼓勵、陪伴和照顧,才能讓我順利完成學業。還要謝謝女友鄭立欣小姐,一路上陪伴著我。最後謝謝所有幫助我、陪著我成長的人。謝謝你們。

陳 世 倫 誌於風城交大 95 年 夏

## **CONTENTS**

| Abstract (Cl | hinese)                                                    |                                                        | i                                                 |  |

|--------------|------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------|--|

| Abstract (Er | nglish)                                                    |                                                        | v                                                 |  |

| •            | ements (Chine                                              | ese)                                                   | ix                                                |  |

| Contents     | `                                                          |                                                        | xi                                                |  |

| Table Captio | ons                                                        |                                                        | XV                                                |  |

| Figure Capti | ions                                                       |                                                        | ix xi xv xviii    2 2 2 2 2 2 2 4 4 4 4 4 Devices |  |

| Chapter 1.   | Introduction                                               | 1                                                      | 1                                                 |  |

| 1.1.         | Scaling Tren                                               | d of CMOS Technology                                   | 1                                                 |  |

|              | 1.1.1.                                                     | Gate-Oxide Breakdown                                   | 2                                                 |  |

|              | 1.1.2.                                                     | Hot-Carrier Degradation                                | 2                                                 |  |

| 1.2.         | Issues of Hig                                              | h-Voltage Circuit Design in Low-Voltage CMOS Processes | 3                                                 |  |

| 1.3.         | Organization                                               | of This Dissertation                                   | 4                                                 |  |

| Chapter 2.   | Mixed-Volta                                                | ge I/O Buffers With Only Thin Gate-Oxide Devices       | 11                                                |  |

| 2.1.         | Issues of Mix                                              | xed-Voltage I/O Interface                              | 11                                                |  |

| 2.2.         | Overview on the Prior Designs of Mixed-Voltage I/O Buffers |                                                        |                                                   |  |

|              | 2.2.1.                                                     | Deign Concepts of Mixed-Voltage I/O Buffers With       |                                                   |  |

|              |                                                            | Thin-Oxide Devices                                     | 13                                                |  |

|              | 2.2.2.                                                     | Prior Designs of Mixed-Voltage I/O Buffers             | 14                                                |  |

| 2.3.         | New Mixed-                                                 | Voltage I/O Buffer 1                                   | 16                                                |  |

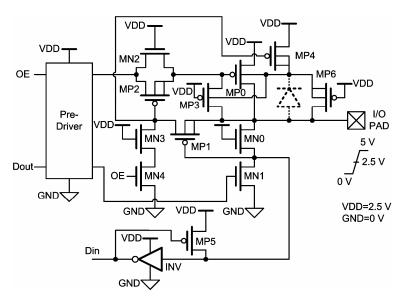

|              | 2.3.1.                                                     | Circuit Implementation                                 | 16                                                |  |

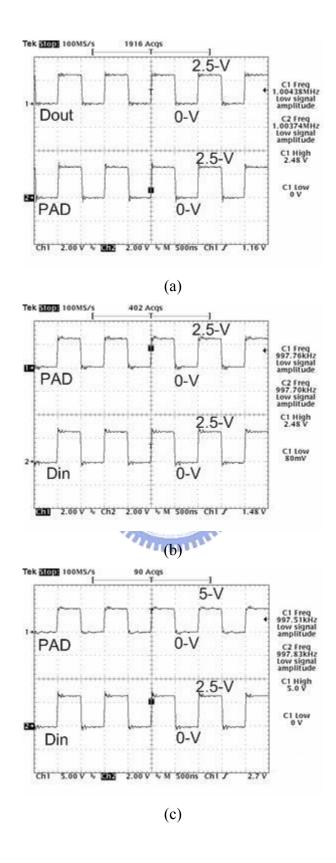

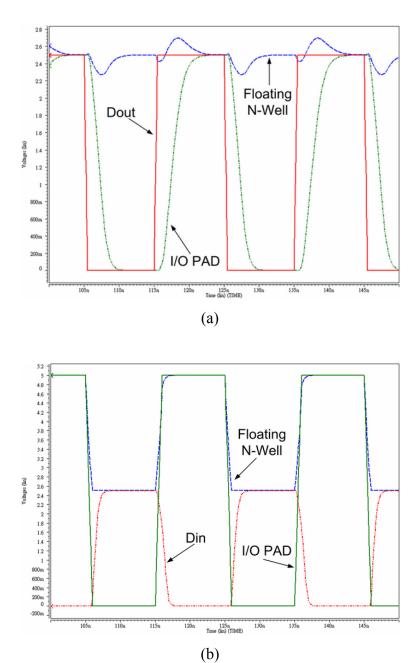

|              | 2.3.2.                                                     | Simulation and Experimental Results                    | 18                                                |  |

| 2.4.         | New Mixed-                                                 | Voltage I/O Buffer 2                                   | 19                                                |  |

|              | 2.4.1.                                                     | Circuit Implementation                                 | 19                                                |  |

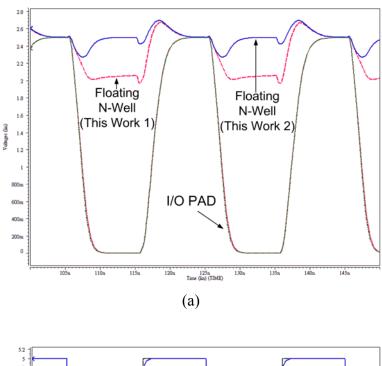

|              | 2.4.2.                                                     | Simulation Results                                     | 19                                                |  |

| 2.5.         | Discussions                                                | and Comparisons                                        | 20                                                |  |

|              | 2.5.1.                                                     | Speed                                                  | 20                                                |  |

|              | 2.5.2.                                                     | Power Consumption                                      | 20                                                |  |

|              | 2.5.3.                                                     | Area                                                   | 21                                                |  |

|              | 2.5.4.                                                     | Noise, Latch-Up, and Subthreshold Leakage Issues       | 22                                                |  |

|              | 2.5.5.                                                     | Transient Stress                                       | 22                                                |  |

|         |      | 2.5.6.                                                       | Comparisons                                       | 22 |  |  |

|---------|------|--------------------------------------------------------------|---------------------------------------------------|----|--|--|

|         | 2.6. | Summary                                                      |                                                   | 23 |  |  |

| Chapter | 3.   | 3.3-V Input Buffer and Output Buffer in 0.13-µm 1/2.5-V CMOS |                                                   |    |  |  |

|         |      | Process                                                      |                                                   | 39 |  |  |

|         | 3.1. | Input Buffer                                                 |                                                   | 39 |  |  |

|         |      | 3.1.1.                                                       | Background                                        | 39 |  |  |

|         |      | 3.1.2.                                                       | Schmitt Trigger Design                            | 41 |  |  |

|         |      | 3.1.3.                                                       | Whole Input Buffer Design                         | 43 |  |  |

|         |      | 3.1.4.                                                       | Experimental Results                              | 43 |  |  |

|         |      | 3.1.5.                                                       | Summary                                           | 44 |  |  |

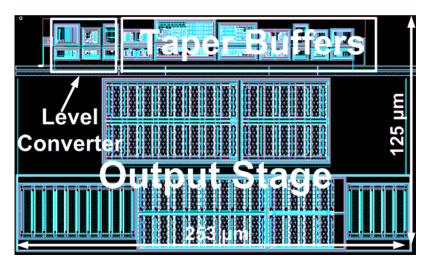

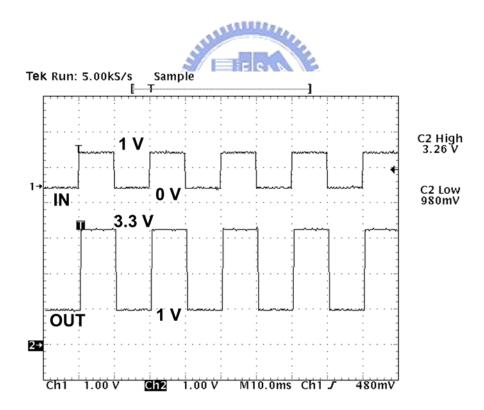

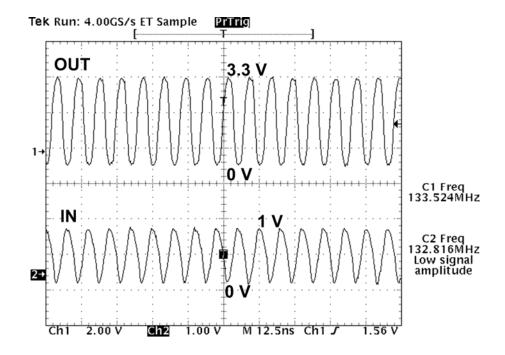

|         | 3.2. | Output Buffe                                                 | r                                                 | 44 |  |  |

|         |      | 3.2.1.                                                       | Background                                        | 44 |  |  |

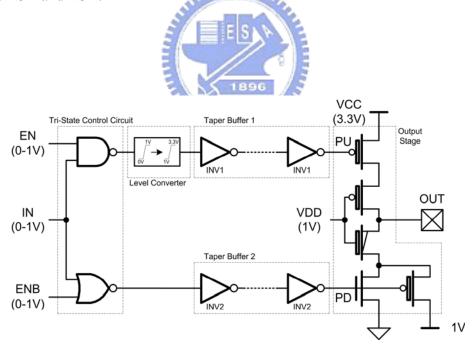

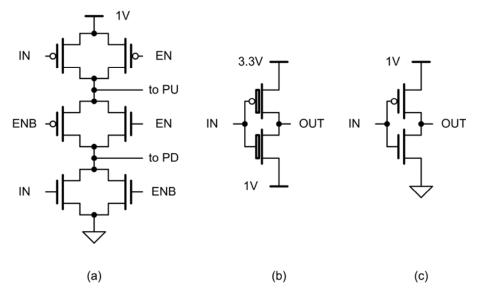

|         |      | 3.2.2.                                                       | Output Stage Design                               | 46 |  |  |

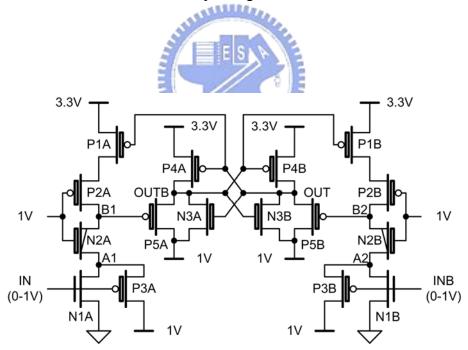

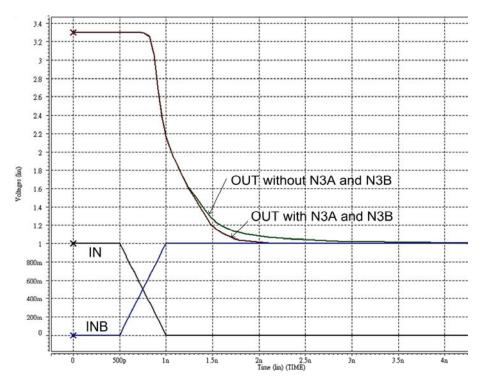

|         |      | 3.2.3.                                                       | Level Converter Design                            | 47 |  |  |

|         |      | 3.2.4.                                                       | Whole Output Buffer Design                        | 48 |  |  |

|         |      | 3.2.5.                                                       | Experimental Results                              | 49 |  |  |

|         |      | 3.2.6.                                                       | Discussions                                       | 49 |  |  |

|         |      | 3.2.7.                                                       | Summary                                           | 50 |  |  |

|         | 3.3. | Conclusion                                                   | 1896                                              | 50 |  |  |

| Chapter | 4.   | NMOS-Block                                                   | ing Technique for Mixed-Voltage I/O Buffer Design | 65 |  |  |

|         | 4.1. | NMOS-Block                                                   | ing Technique                                     | 65 |  |  |

|         |      | 4.1.1.                                                       | Background                                        | 65 |  |  |

|         |      | 4.1.2.                                                       | NMOS-Blocking Technique                           | 67 |  |  |

|         | 4.2. | 2×VDD Input                                                  | Tolerant Mixed-Voltage I/O Buffer                 | 67 |  |  |

|         |      | 4.2.1.                                                       | Circuit Implementation                            | 67 |  |  |

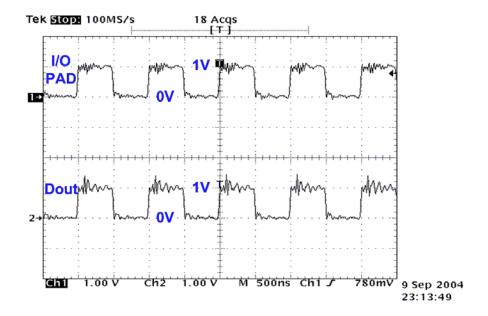

|         |      | 4.2.2.                                                       | Simulation and Experimental Results               | 69 |  |  |

|         | 4.3. | 3×VDD Input                                                  | Tolerant Mixed-Voltage I/O Buffer                 | 70 |  |  |

|         |      | 4.3.1.                                                       | Circuit Implementation                            | 70 |  |  |

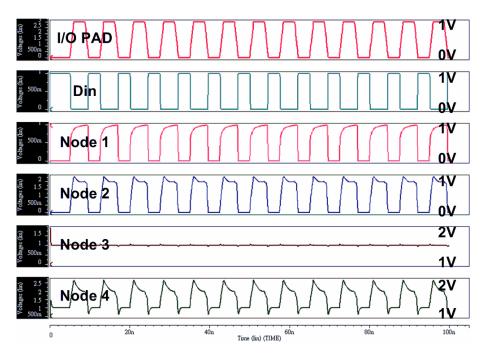

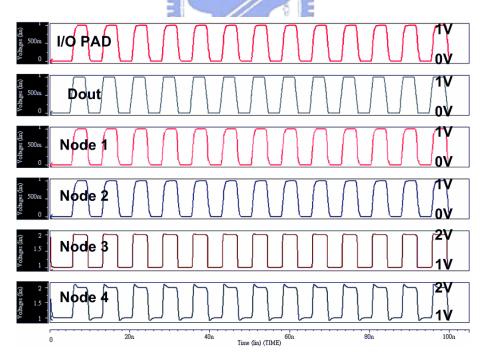

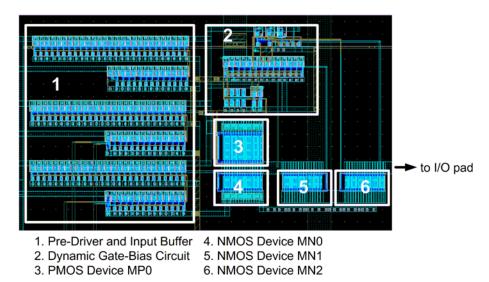

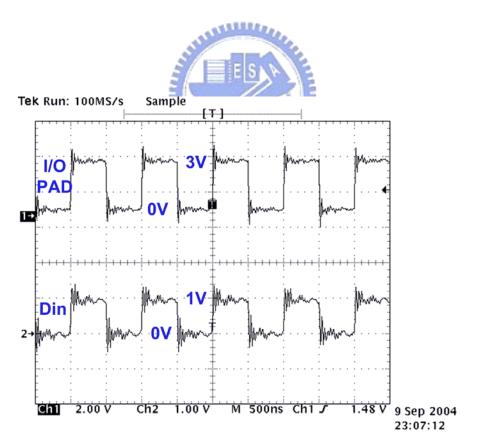

|         |      | 4.3.2.                                                       | Simulation and Experimental Results               | 71 |  |  |

|         | 4.4. | Discussions                                                  |                                                   | 72 |  |  |

|         |      | 4.4.1.                                                       | Limitation of the NMOS-Blocking Technique         | 72 |  |  |

|         |      | 4.4.2.                                                       | Gate-Oxide Overstress                             | 73 |  |  |

|         |      | 4.4.3.                                                       | Hot-Carrier Degradation                           | 73 |  |  |

|           |                                         | 4.4.4.        | Speed Degradation of the NMOS-Blocking Technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 74  |

|-----------|-----------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|           |                                         | 4.4.5.        | Advantages of the NMOS-Blocking Technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 74  |

|           |                                         | 4.4.6.        | Duty Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 74  |

|           | 4.5.                                    | Summary       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 75  |

| Chapter   | 5.                                      | Charge Pum    | p Circuit Without Gate-Oxide Reliability Issue in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|           |                                         | Low-Voltage   | Processes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 87  |

|           | 5.1.                                    | Background    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 87  |

|           | 5.2.                                    | New Charge    | Pump Circuit Without Gate-Oxide Reliability Issue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 90  |

|           | 5.3.                                    | Verifications | and Comparisons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 91  |

|           |                                         | 5.3.1.        | Simulation Results and Comparisons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 91  |

|           |                                         | 5.3.2.        | Silicon Verifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 93  |

|           |                                         | 5.3.3.        | Discussions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 94  |

|           | 5.4.                                    | Summary       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 95  |

| Chapter   | 6.                                      | Ultra-High-V  | Voltage Charge Pump Circuit With Polysilicon Diodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|           |                                         | in Low-Volta  | age Standard CMOS Processes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 105 |

|           | 6.1.                                    | Background    | A PROPERTY OF THE PROPERTY OF | 105 |

|           | 6.2.                                    | Polysilicon D | riodes E E E E E E E E E E E E E E E E E E E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 107 |

|           |                                         | 6.2.1.        | Device Structure of the Polysilicon Diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 107 |

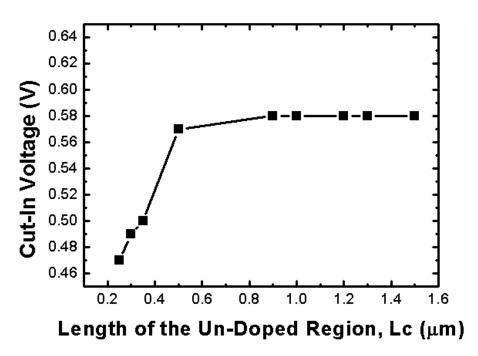

|           |                                         | 6.2.2.        | Characteristics of the Polysilicon Diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 107 |

|           | 6.3.                                    | Ultra-High-V  | oltage Charge Pump Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 108 |

|           |                                         | 6.3.1.        | Circuit Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 108 |

|           |                                         | 6.3.2.        | Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 109 |

|           |                                         | 6.3.3.        | Discussions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 111 |

|           | 6.4.                                    | Summary       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 111 |

| Chapter   | Chapter 7. Conclusions and Future Works |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|           | 7.1.                                    | Main Results  | of This Dissertation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 121 |

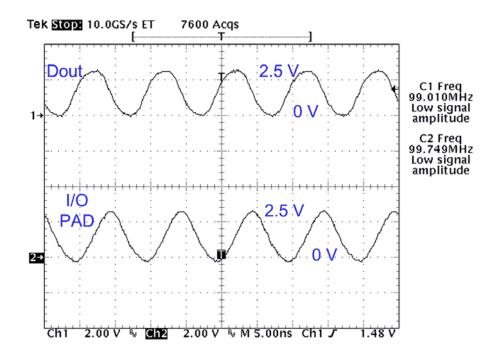

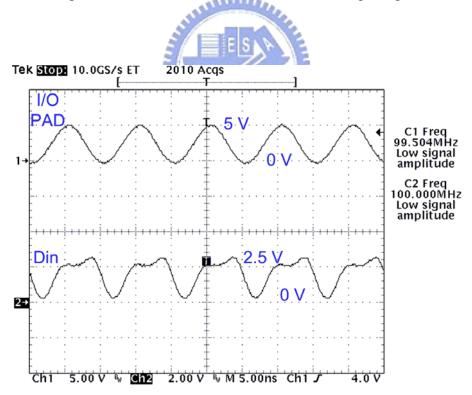

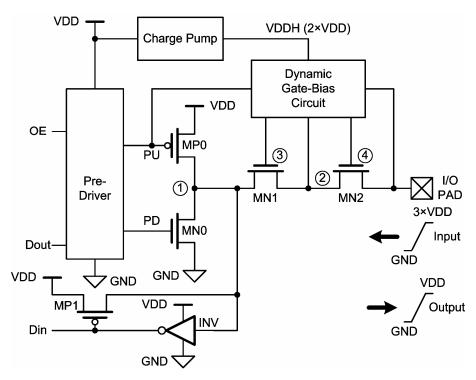

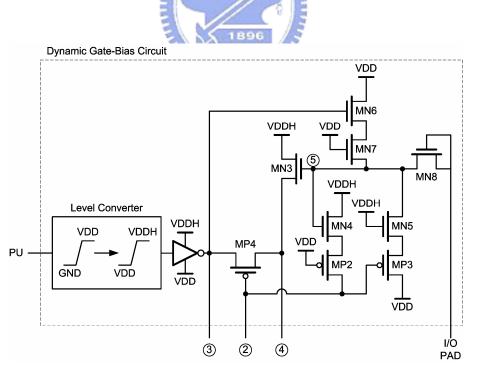

|           | 7.2.                                    | Future Works  | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 123 |