# 國立交通大學

電子工程學系電子研究所

博士論文

低電壓互補式金氧半製程下可相容高工作電壓之 靜電放電防護設計

# HIGH-VOLTAGE-TOLERANT ESD PROTECTION DESIGN IN LOW-VOLTAGE CMOS PROCESSES

研究生:張瑋仁(Wei-Jen Chang)

指導教授 :柯 明 道 (Ming-Dou Ker)

中華民國九十六年九月

# 低電壓互補式金氧半製程下可相容高工作電壓之 静電放電防護設計

# HIGH-VOLTAGE-TOLERANT ESD PROTECTION DESIGN IN LOW-VOLTAGE CMOS PROCESSES

研究生:張瑋仁 Student: Wei-Jen Chang

指導教授:柯明道 Advisor: Ming-Dou Ker

國立交通大學電子工程學系電子研究所

**将士論义**

### **A Dissertation**

Submitted to Department of Electronics Engineering and Institute of Electronics

College of Electrical and Computer Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of Doctor of Philosophy

in **Electronic Engineering**

September 2007 Hsinchu, Taiwan, Republic of China

中華民國九十六年九月

# 低電壓互補式金氧半製程下可相容高工作電壓 之靜電放電防護設計

研究生:張瑋仁 指導教授: 柯明道 博士

# 國立交通大學電子工程學系電子研究所

# 摘要

隨著半導體製程的進步與發展,積體電路產品已經成為民生用品般地大量製造與使用,許多整合多功能的系統晶片(SoC)已經成為各電子公司的產品研發主力,電子產業也在這個領域有長足的進步與發展。但由於半導體製造技術的日新月異,使得積體電路對靜電放電防護的能力下降很多,同時由於操作電壓一直在下降,但是週邊電路的電壓卻未隨半導體製程的進步而降低,所以在扮演晶片輸入輸出媒介的混合電壓界面(Mixed-Voltage I/O Interface)上將會產生許多問題,尤其在電子系統訊號整合上。因此要在此混合電壓電路加上其靜電放電保護電路,需要考量界面電壓轉換、混合電壓界面間的漏電流(Leakage Current)、混合電壓界面電路的可靠度(Reliability)等問題。因此,在混合電壓界面上,如何仔細評估這些問題進而設計出具有高的靜電放電防護能力的電路將是當今以及未來積體電路設計上的重要課題,這個主題隨著半導體製程進入 0.13 微米 以及 90 奈米之後,對積體電路設計產業更加重要。另外,隨著高壓金氧半製程在面版驅動電路(LCD Driver ICs)、電源供應器(Power Supplies)、電源管理(Power Management),以及汽車電子(Automotive Electronics)等使用的普及化,對

於使用在這些應用的輸出端以及當作靜電放電保護元件的高壓電晶體來說,靜電放電的可靠度問題將比在一般低壓製程的元件來得嚴重,因此如何有效改善靜電放電耐壓能力,將是這些高壓積體電路設計上很重要的課題,這個主題也隨著這些產業應用上的多元化而更趨重要。所以本論文分別針對了混合電壓界面電路以及高壓金氧半製程應用上的限制與困難作討論,並進一步設計出有效的靜電放電防護電路以適用在各相關應用之積體電路晶片。

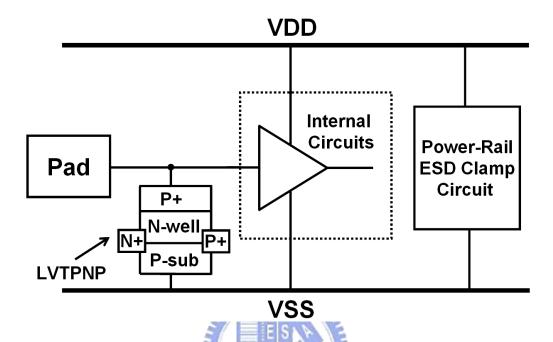

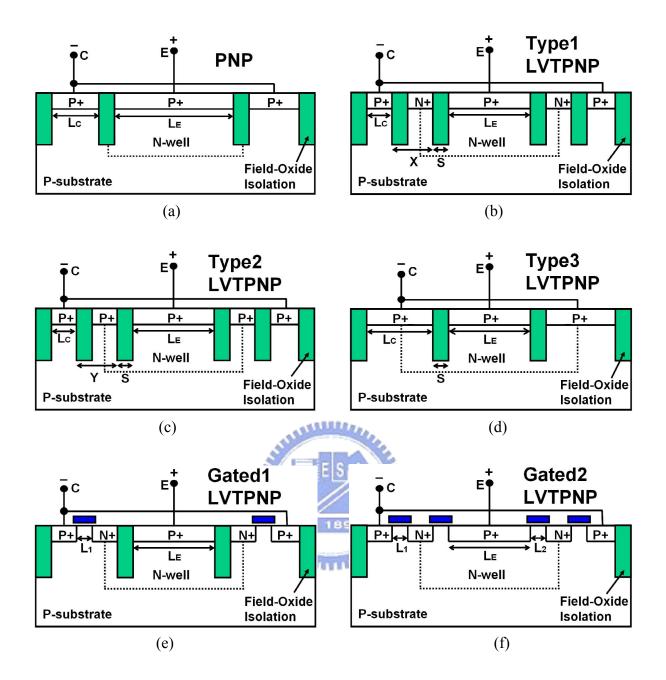

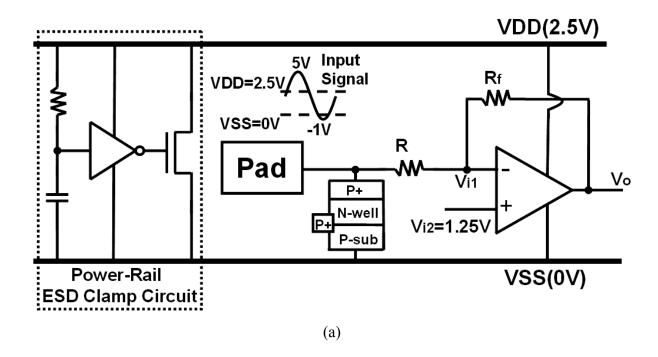

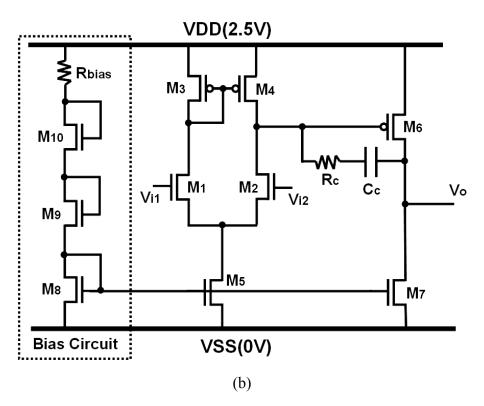

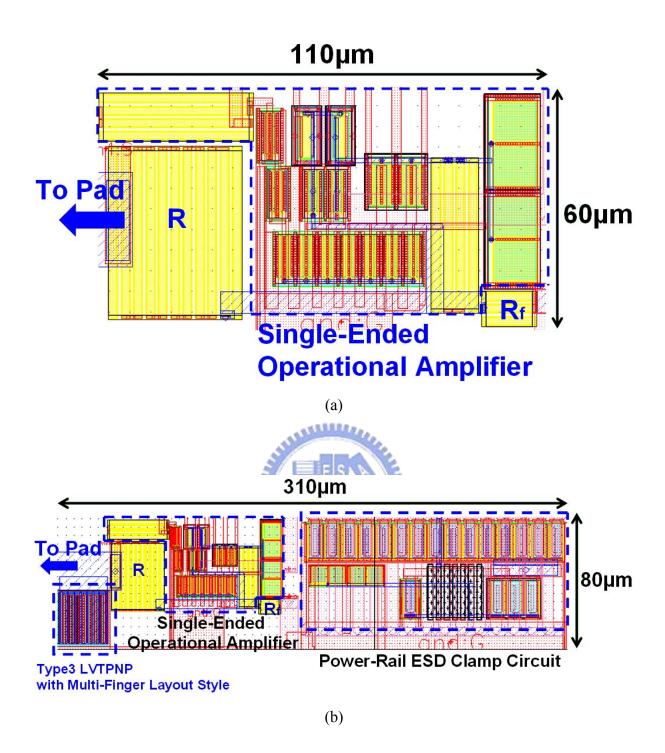

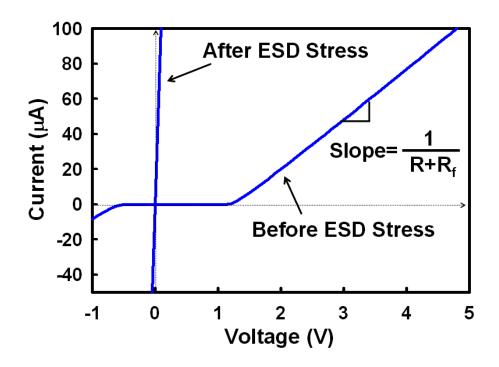

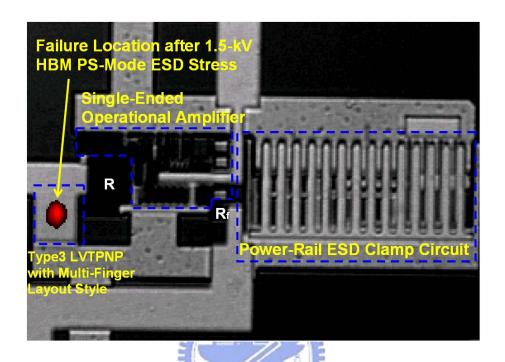

首先,本論文提出了一種新型的低電壓驅動雙載子接面電晶體 (Low-Voltage-Triggered PNP, LVTPNP)來當作混合電壓輸入輸出界面 (Mixed-Voltage I/O Interfaces) 之靜電放電保護元件。此新型靜電放電保 護元件是在 CMOS 製程中寄生的雙載子接面電晶體的 N 型井 (N-Well) 以 及 P 型基板 (P-Substrate) 接面上,額外植入 N 型或是 P 型的擴散離子所 構成,以降低 N 型井以及 P 型基板接面的崩潰電壓,當輸入電壓比 VDD 高(Over-VDD)或比 VSS 低(Under-VSS)時,不會有漏電以及閘極氧化 層的可靠度問題。在 0.35 微米互補式金氧半製程,已經驗證了此低電壓驅 動雙載子接面電晶體會比傳統寄生的雙載子接面電晶體的靜電放電耐受程 度來得高,而該元件的最佳化佈局方式 (Layout Style) 也在 0.35 微米以及 0.25 微米互補式金氧半製程中驗證來提升元件本身的靜電放電耐受程度, 經由實驗證明,具有多指狀(Multi-Finger)佈局方式的元件靜電放電耐受 程度會比單指狀 (Single Finger) 的要來得高。除此之外,在 0.25 微米製程 的晶片驗證下,具有多指狀佈局方式的低電壓驅動雙載子接面電晶體搭配 電源間的靜電放電箝制電路(Power-Rail ESD Clamp Circuit)成功地提升了 非同步數位用戶專線 (Asymmetric Digital Subscriber Line, ADSL) 輸入級的 靜電放電耐受程度,此輸入級的訊號界於 5V 到-1V 之間,此電壓同時超過 了該 IC 之 VDD (2.5V) 和低過了該 IC 之 VSS (0V)。

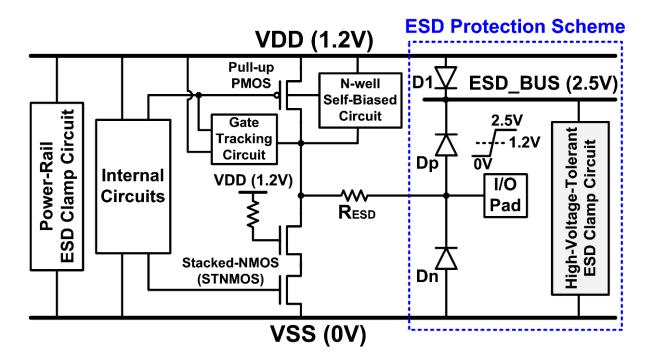

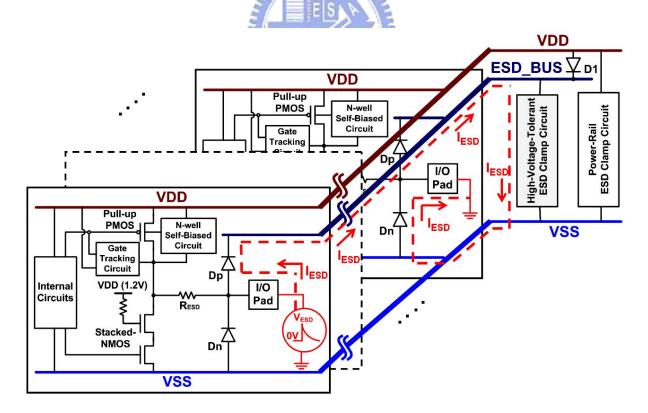

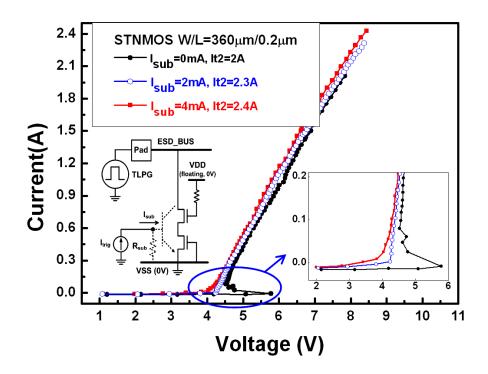

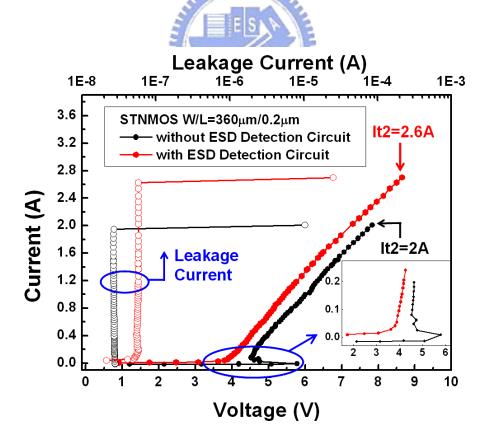

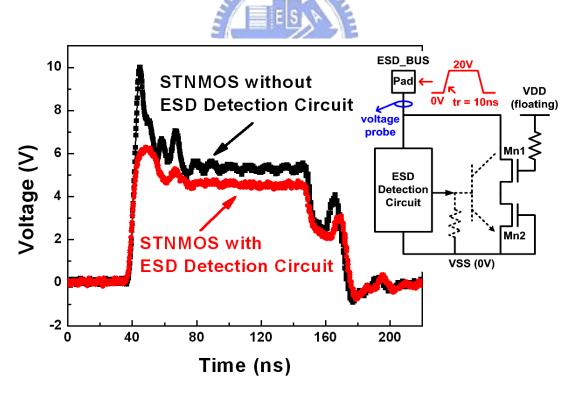

本論文研究的第二部分,為了提供有效的靜電放電防護於 1.2/2.5V 混 合電壓輸入輸出界面,本論文提出了新型的靜電放電保護架構並在 0.13 微 米製程中成功驗證,此架構同時利用了靜電放電匯流排(ESD BUS)以及 可耐高工作電壓之靜電放電箝制電路 (High-Voltage-Tolerant ESD Clamp Circuit)來實現。當混合電壓輸入輸出界面的銲墊(Pad)對 VDD(或 VSS) 之間遭受靜電轟擊或是輸入輸出腳對腳(Pin-to-Pin)之間遭受靜電轟擊時, 此靜電放電保護架構都可以提供相對應的放電路徑來避免內部電路遭受靜 電損壞。在此靜電放電防護電路中,可耐高工作電壓之靜電放電箝制電路 都是利用 1.2V 低壓元件來實現,並可安全地在 2.5V 的電壓偏壓下工作而 不會有閘極氧化層的可靠度問題。由實驗可知,比起一般的堆疊式電晶體 (Stacked-NMOS)而言,基板觸發(Substrate Triggered)技術可以有效提 升該可耐高工作電壓之靜電放電箝制電路的導通速度以及靜電放電耐受程 度。在堆疊式電晶體的元件尺寸為 480μm/0.2μm 的大小之下, 1.2/2.5V 的 混合電壓輸入輸出界面之人體放電模式靜電放電耐壓能力(HBM ESD levels)可以從原本的 5kV 增加到 6.5kV;同時,機械放電模式靜電放電耐壓 能力(MM ESD levels)可以從原本的 275V 增加到 400V。

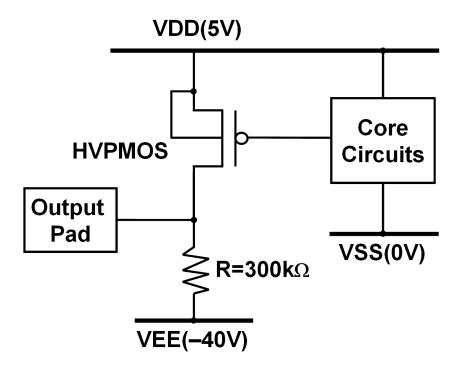

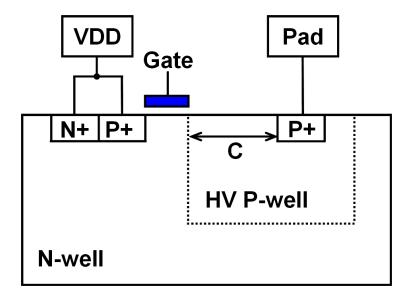

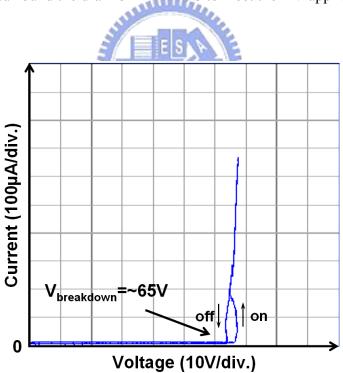

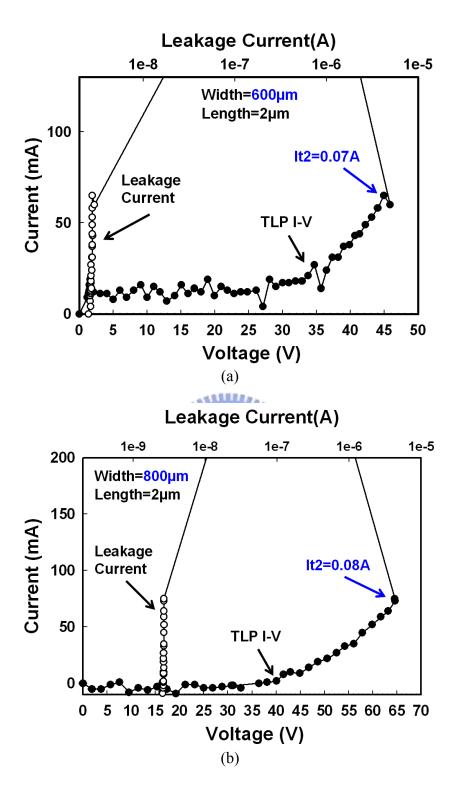

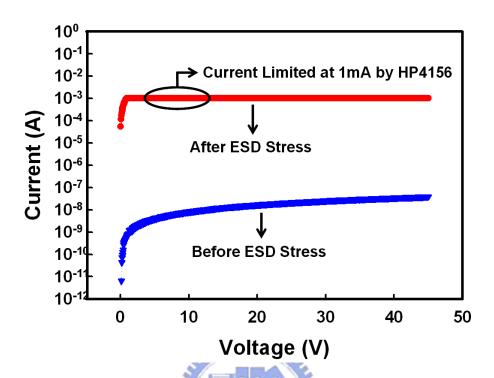

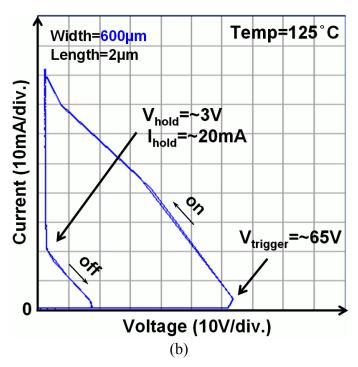

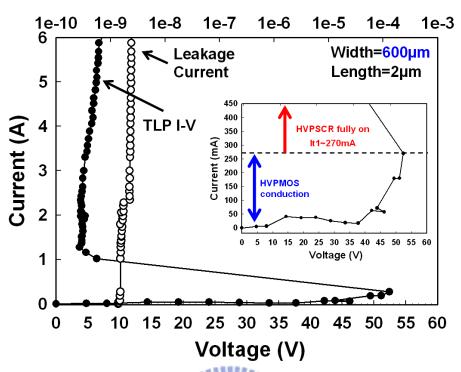

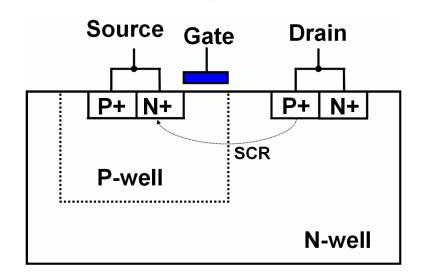

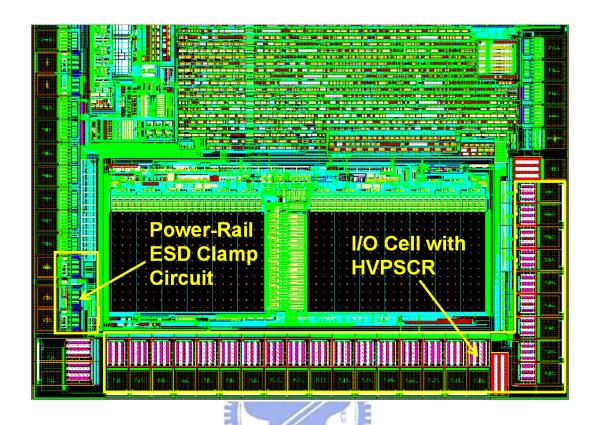

本論文研究的第三部份,為了提升應用在車用電子(Automotive Electronics)中的真空螢光顯示器(Vacuum-Fluorescent-Display,VFD)驅動 IC 的靜電放電耐受程度,本論文提出一種新型的靜電放電保護的元件結構。此元件結構是在高壓 P 型的金氧半電晶體(HVPMOS)的汲極當中植入一個 N 型離子佈植來形成一個嵌入式高壓 P 型矽控整流器(High-Voltage P-Type Silicon Controlled Rectifier, HVPSCR)路徑,此結構只需要加入額外的 N 型離子局部佈局面積即可實現。在 0.5 微米的互補式金氧半製程中,成功驗證了具有此嵌入式高壓 P 型矽控整流器的真空螢光顯示器驅動積體電路的人體放電模式靜電放電耐壓能力可以從不到 500V 增加到 8kV;同

時,當元件尺寸為 500μm/2μm、600μm/2μm 以及 800μm/2μm 時,機械放電模式之靜電放電耐壓能力可以通過 1100V、1300V 以及 1900V 的靜電測試。此外,此嵌入式高壓 P 型矽控整流器的真空螢光顯示器驅動積體電路可成功通過 ±200mA 的閂鎖 (Latchup) 測試。

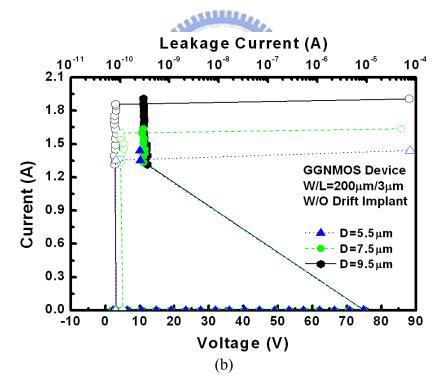

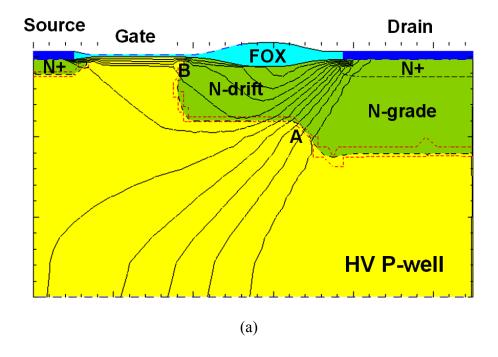

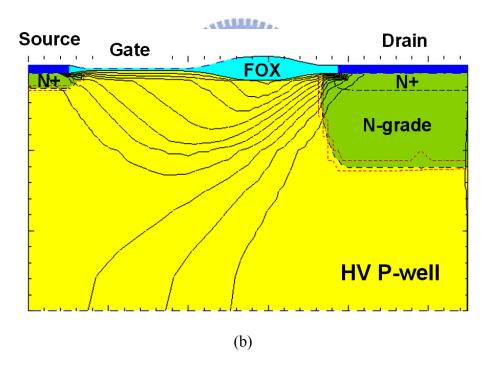

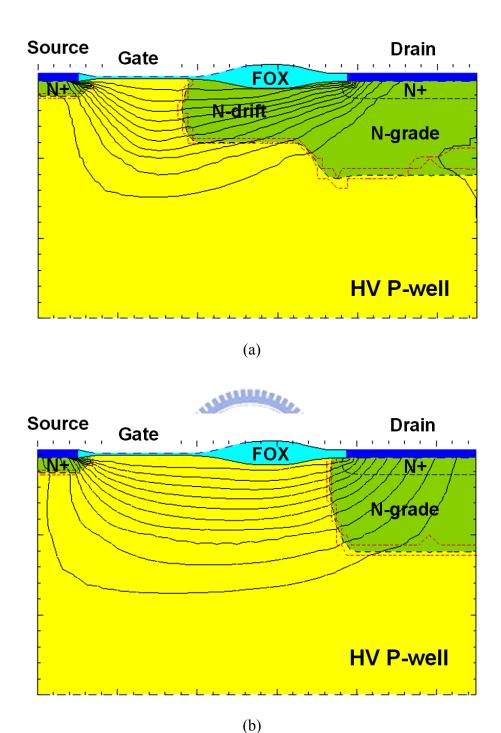

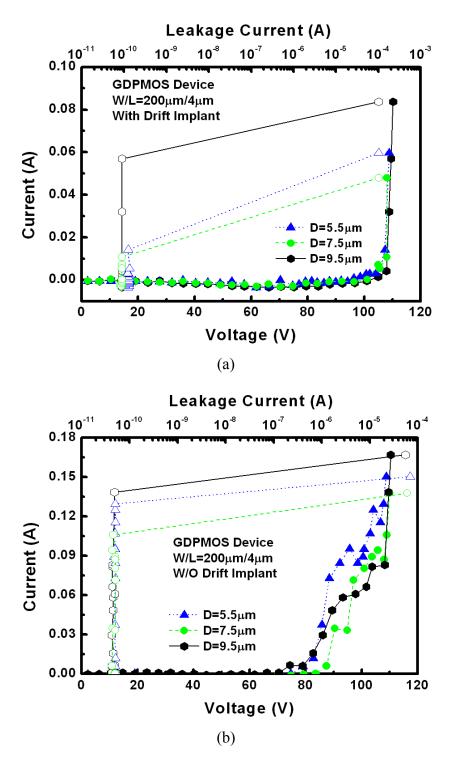

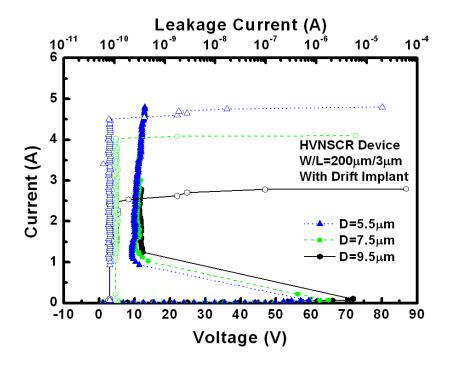

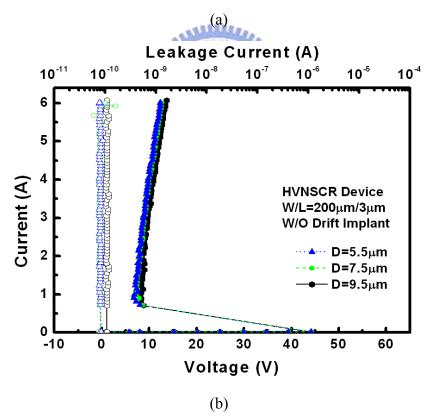

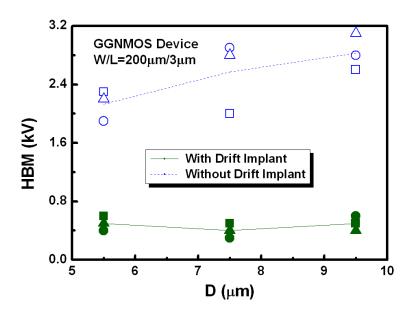

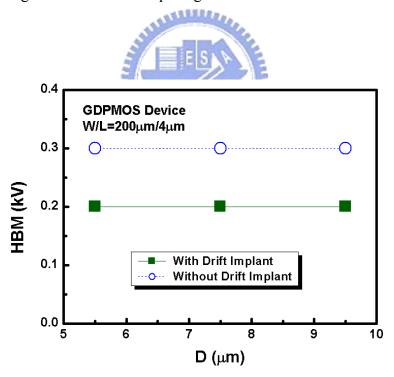

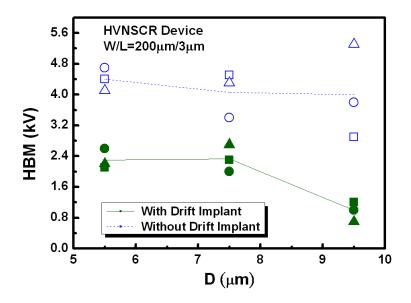

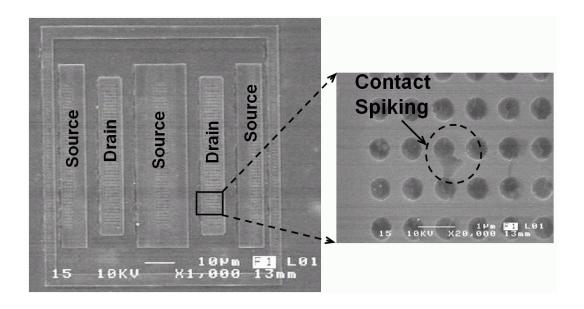

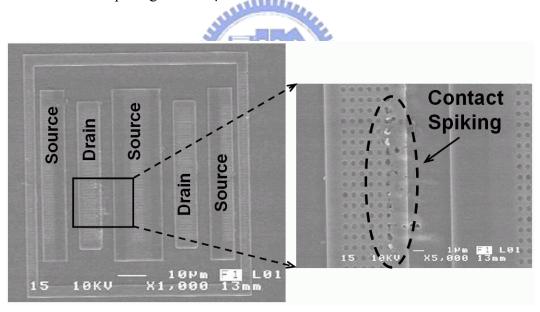

本論文研究的第四部分,觀察到使用在輸出端以及當作靜電放電保護 元件的高壓電晶體,靜電放電的可靠度問題比在一般製程的元件來得嚴 重,因此本論文利用 40-V 金氧半製程對於不同元件結構以及汲極到閘極的 距離(Layout Spacing from Drain to Polygate)做一深入探討。實驗結果成 功驗證了汲極下端沒有植入的飄移摻雜(Drift Implant)佈局的高壓金氧半 電晶體比起汲極下端沒有植入的飄移摻雜(Drift Implant)佈局的高壓金氧半 電晶體比起汲極下端有加入移摻雜的高壓金氧半電晶體有較高的二次崩潰 電流(Secondary Breakdown Current, It2)以及較好的靜電放電防護能力。 在所有元件結構當中,嵌入在高壓 N 型的金氧半電晶體中的高壓 N 型矽控 整流器(HVNSCR)並在汲極下端移除了飄移摻雜的結構,具有最高的二 次崩潰電流以及靜電放電耐受度。此外,元件模擬技巧也成功地分析了有 無飄移摻雜對於元件內電流分佈的影響。

本論文分別針對了混合電壓界面電路以及高壓金氧半製程應用上的限 制與困難作討論,並進一步設計出有效的靜電放電防護電路應用在各相關 之積體電路晶片。本博士論文所提出電路已經有相對應的國際期刊與會議 論文發表以及專利申請。

# HIGH-VOLTAGE-TOLERANT ESD PROTECTION DESIGN IN LOW-VOLTAGE CMOS PROCESSES

Student: Wei-Jen Chang Advisor: Dr. Ming-Dou Ker

Department of Electronics Engineering and Institute of Electronics

National Chiao Tung University

#### **ABSTRACT**

The scaling trend of the CMOS technology is toward the nanometer region to increase the speed and density of the transistors in integrated circuits. Due to the reliability issue, the power supply voltage is also decreased with the advanced technologies. However, in an electronic system, some circuits could be still operated at high voltage levels. If the circuits realized with low-voltage devices are operated at high voltage levels, the gate-oxide breakdown and leakage issues will occur. Therefore, for the CMOS integrated circuits (ICs) with the mixed-voltage I/O interfaces, the on-chip electrostatic discharge (ESD) protection circuits will meet more design constraints and difficulties. The on-chip ESD protection circuit for mixed-voltage I/O interfaces should meet the gate-oxide reliability constraints and prevent the undesired leakage current paths during normal circuit operating operation. During ESD stress condition, the on-chip ESD protection circuit should provide effective ESD protection for the internal circuits. In high-voltage CMOS technology, high-voltage transistors have been widely used for display driver ICs, power supplies, power management, and automotive electronics. The high-voltage MOSFET was often used as the ESD protection device in the high-voltage CMOS ICs, because it can work as both of output driver and ESD protection device simultaneously. With an ultra-high operating voltage, the ESD robustness of high-voltage MOSFET is quite weaker than that of low-voltage MOSFET. Hence, how to improve the ESD robustness of HV NMOS with a reasonable silicon area is indeed an important reliability issue in HV CMOS technology. In this thesis, some new ESD protection structures are proposed to improve ESD robustness of the high-voltage IC products fabricated in CMOS technology.

To protect the mixed-voltage I/O interfaces for signals with voltage levels higher than VDD (over-VDD) and lower than VSS (under-VSS), ESD protection design with the low-voltage-triggered PNP (LVTPNP) device in CMOS technology is proposed. The LVTPNP is realized by inserting N+ or P+ diffusion across the junction between N-well and P-substrate of the PNP device. The LVTPNP devices with different structures have been investigated and compared in CMOS processes. The experimental results in a 0.35-μm CMOS process have proven that the ESD level of the proposed LVTPNP is higher than that of the traditional PNP device. Furthermore, layout on LVTPNP device for ESD protection in mixed-voltage I/O interfaces is also optimized in this work. The experimental results verified in both 0.35-μm and 0.25-μm CMOS processes have proven that the ESD levels of the LVTPNP drawn in the multi-finger layout style are higher than that drawn in the single finger layout style. Moreover, one of the LVTPNP devices drawn with the multi-finger layout style has been used to successfully protect the input stage of an ADSL IC in a 0.25-μm salicided CMOS process.

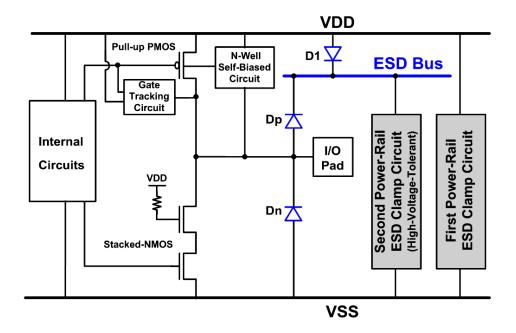

To increase the system-on-chip ESD immunity of micro-electronic products against system-level ESD stress, the chip-level ESD/EMC protection design should be enhanced. Considering gate-oxide reliability, a new ESD protection scheme with ESD\_BUS and high-voltage-tolerant ESD clamp circuit for 1.2/2.5 V mixed-voltage I/O interfaces is proposed in this chapter. The devices used in the high-voltage-tolerant ESD clamp circuit are all 1.2 V low-voltage NMOS/PMOS devices which can be safely operated under the 2.5 V bias conditions without suffering from the gate-oxide reliability issue. The four-mode (PS, NS, PD, and ND) ESD stresses on the mixed-voltage I/O pad and pin-to-pin ESD stresses can be effectively discharged by the proposed ESD protection scheme. The experimental results verified in a 0.13 µm CMOS process have confirmed that the proposed new ESD protection scheme has high human-body-model (HBM) and machine-model (MM) ESD robustness with a fast turn-on speed. The proposed new ESD protection scheme, which is designed with only low-voltage devices, is an excellent and cost-efficient solution to protect mixed-voltage I/O interfaces.

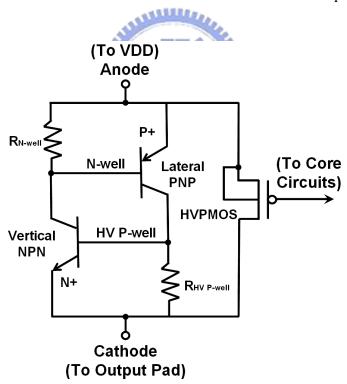

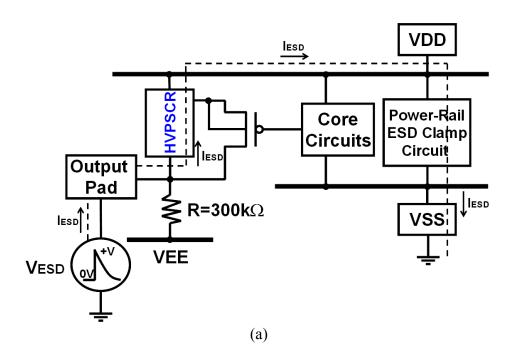

To greatly improve ESD robustness of the vacuum-fluorescent-display (VFD) driver IC for automotive electronics applications, a new electrostatic discharge protection structure of

high-voltage P-type silicon controlled rectifier (HVPSCR) embedded into the high-voltage PMOS device is proposed. By only adding the additional N+ diffusion into the drain region of high-voltage PMOS, the TLP-measured secondary breakdown current (It2) of output driver has been greatly improved greater than 6A in a 0.5-μm high-voltage CMOS process. Such ESD-enhanced VFD driver IC, which can sustain HBM ESD stress of up to 8kV, has been in mass production for automotive applications in car without latchup problem. Moreover, with device widths of 500μm, 600μm, and 800μm, the MM ESD levels of the HVPSCR are as high as 1100V, 1300V, and 1900V, respectively.

The dependences of drift implant and layout parameters on ESD robustness in a 40-V CMOS process have been investigated in silicon chips. From the experimental results, the HV MOSFETs without drift implant in the drain region have better TLP-measured It2 and ESD robustness than those with drift implant in the drain region. Furthermore, the It2 and ESD level of HV MOSFETs can be increased as the layout spacing from the drain diffusion to polygate is increased. It was also demonstrated that a specific test structure of HV n-type silicon controlled rectifier (HVNSCR) embedded into HV NMOS without N-drift implant in the drain region has the excellent TLP-measured It2 and ESD robustness. Moreover, due to the different current distributions in HV NMOS and HVNSCR, the dependences of the TLP-measured It2 and HBM ESD levels on the spacing from the drain diffusion to polygate are different.

In this thesis, the novel ESD protection circuits have been developed for mixed-voltage I/O interfaces and high-voltage CMOS process with high ESD robustness. Each of the ESD protection circuits has been successfully verified in the testchips.

### **ACKNOWLEDGEMENTS**

在交通大學電子研究所的生涯中,首先要感謝我的指導教授柯明道教授在碩士班和博士班這幾年當中提供我最好的研究環境和資源,並耐心的指導與鼓勵,使我能順利完成博士學業。在指導教授循序漸進的教誨下,讓我得以在積體電路靜電放電設計領域中,由入門到能夠解決問題,同時,也不厭其煩地教導我做研究的方法與論文寫作的技巧。此外,不只在專業領域上的知識,從柯教授認真的研究態度和嚴謹的處事原則,也讓我學習到克服困難、解決問題的正確態度與方法,以及如何團隊合作把一件事情有效率地處理好。雖然過程艱辛,也經歷不少挫折,卻讓我獲益良多,也讓我這幾年成長許多。

此外,很感謝 307 實驗室另外四位師長,吳重雨校長、吳錦川教授、吳介琮教授以及陳巍仁教授給我的指導與建議。其中,在我遭遇瓶頸的時候,由於吳校長在公開場合給學生一席話的啟發,讓我瞭解一個新的 idea,是需要長時間的努力累積之下,在突發奇想中產生的。還有感謝周世傑教授、方偉騏教授、謝詠芬博士、姜信欽博士在百忙之中抽空來擔任我的口試委員,給我指導跟建議,讓整個論文更加完整。

再來非常感謝財團法人聯發科技教育基金會提供優渥的獎學金,在這麼 多優秀的申請者當中獲得這項殊榮,真的感到萬分榮幸,讓我可以無後顧之 憂的情形下專心從事研究,同時也減輕了家中的經濟負擔。

感謝 307 實驗室的羅文裕學長以及徐國鈞博士,在我初來到柯教授研究群時,給我許多研究和學業上的建議與幫助。感謝碩士班期間,一起在 527 奮鬥的成員郭秉捷、莊凱嵐、黃如琳、陳正瑞、李權哲、周政賢、林棋樺,有了你們再苦的日子也笑得出來。還有謝謝其他 307 實驗室的成員林昆賢博士、陳世倫博士、許勝福博士、陳榮昇博士、施育全博士、李瑞梅博士,王文傑、徐新智、顏承正、蕭淵文、李健銘、陳世宏、陳志豪、陳穩義、吳偉琳、陳煒明、賴泰翔、王暢資、王資閔、林群佑、陳世範、黃曄仁等學長姐、同學、學弟們在課業、研究、生活上的幫忙與協助,讓我順利完成我的博士論文、並學習到做人處事上的態度與方法。此外,感謝 307 實驗室的助理卓慧貞小姐在實驗室行政事務上的許多協助。

致上最深的感謝給我親愛的家人們,祖父張孟源先生、父親張智鐸先生、母親莊月梅女士、大妹張育菁、小妹張育慈以及其他家人們。有了您們的支持、鼓勵、陪伴和照顧,才能讓我順利完成學業。最後謝謝所有幫助我、陪著我成長的人。謝謝你們。

張 瑋 仁 謹誌於竹塹交大 96 年 秋

# **CONTENTS**

| ABSTR  | ACT (CHINESE)                            | i         |

|--------|------------------------------------------|-----------|

| ABSTRA | ACT (ENGLISH)                            | V         |

| ACKNO  | OWLEDGEMENTS                             | vii       |

| CONTE  | NTS                                      | ix        |

| TABLE  | CAPTIONS                                 | xii       |

| FIGURE | E CAPTIONS                               | xiv       |

| СНАРТ  | ER 1 INTRODUCTION                        | 1         |

| 1.1    | Background                               | 1         |

| 1.2    | Issue of Mixed-Voltage I/O Interfaces    | 1         |

| 1.3    | Issue of High-Voltage CMOS ICs           | 4         |

| 1.4    | Thesis Organization ES                   | 5         |

| Figur  | res 1896                                 | 7         |

| CHAPT  | ER 2 OVERVIEW ON ESD PROTECTION DE       | ESIGN FOR |

|        | MIXED-VOLTAGE I/O CIRCUITS               | 11        |

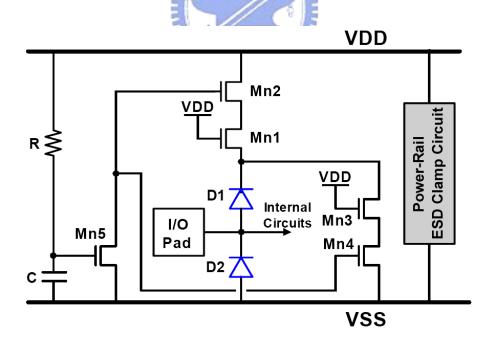

| 2.1    | Substrate-Triggered Stacked-NMOS Device  | 11        |

| 2.2    | Extra ESD Device between I/O Pad and VSS | 13        |

| 2.3    | Extra ESD Device between I/O Pad and VDD | 15        |

| 2.4    | ESD Protection Design with ESD Bus       | 16        |

| 2.5    | Special Applications                     | 17        |

| 2.6    | Summary                                  | 18        |

| Figur  | res                                      | 19        |

# CHAPTER 3 ESD PROTECTION DESIGN WITH LOW-VOLTAGE-TRIGGERED PNP (LVTPNP) DEVICES FOR MIXED-VOLTAGE I/O INTERFACE

|     |           |       |                                                           | 25 |

|-----|-----------|-------|-----------------------------------------------------------|----|

|     | 3.1       | ESI   | Protection Design with LVTPNP Device                      | 25 |

|     |           | 3.1.1 | Device Structures and TLP-Measured I-V Characteristics    | 26 |

|     |           | 3.1.2 | Layout Parameters of LVTPNP Devices on HBM ESD Levels     | 27 |

|     |           | 3.1.3 | Multi-Finger Layout Style for LVTPNP                      | 29 |

|     | 3.2       | App   | plication in ADSL Interface                               | 31 |

|     |           | 3.2.1 | ESD Protection Design with LVTPNP for Input Stage of ADSL | 31 |

|     |           | 3.2.2 | HBM ESD Levels of ADSL with the Type3 LVTPNP              | 33 |

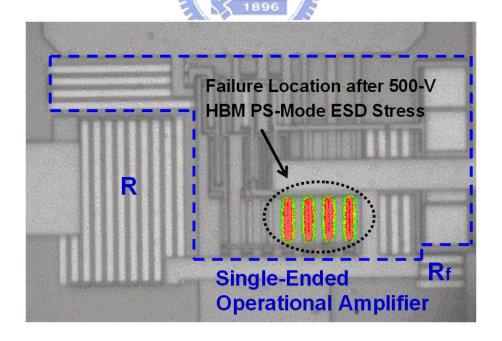

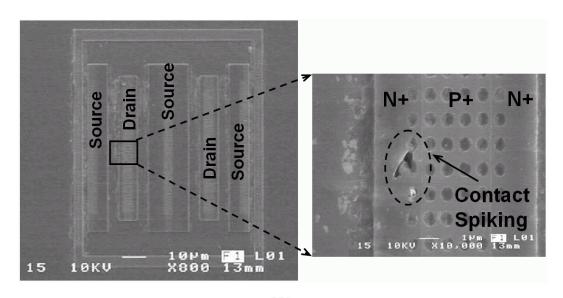

|     |           | 3.2.3 | Failure Analysis                                          | 34 |

|     | 3.3       | Sun   | nmary                                                     | 34 |

| ,   | Tab       | les   |                                                           | 36 |

|     | Figu      | ıres  |                                                           | 40 |

|     |           |       |                                                           |    |

| CHA | <b>AP</b> | ΓER 4 | HIGH-VOLTAGE-TOLERANT ESD CLAMP                           |    |

|     |           |       | CIRCUIT IN LOW-VOLTAGE THIN-OXIDE                         |    |

|     |           |       | TECHNOLOGY                                                | 55 |

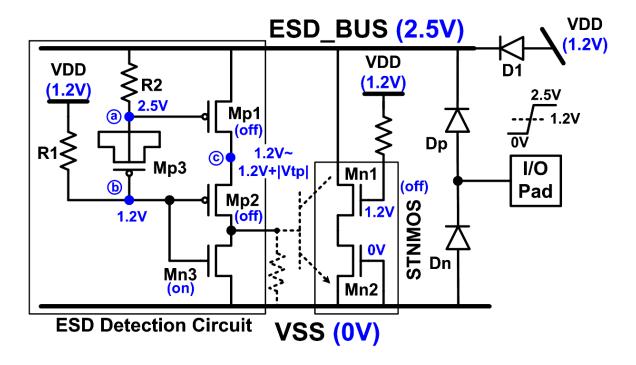

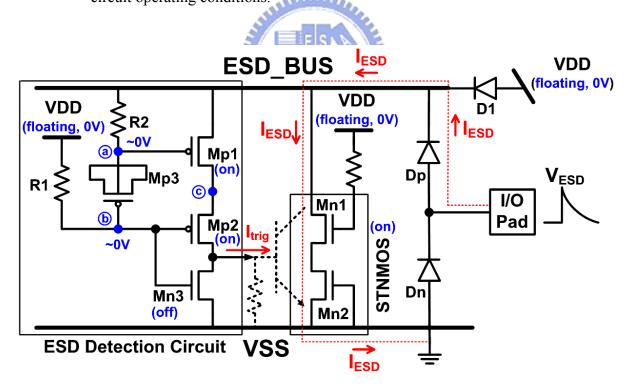

|     | 4.1       | ESI   | O Protection Scheme for Mixed-Voltage I/O Interface       | 55 |

|     | 4.2       | Hig   | h-Voltage-Tolerant ESD Clamp Circuit                      | 57 |

|     |           | 4.2.1 | Substrate-Triggered STNMOS                                | 57 |

|     |           | 4.2.2 | Operation Principle                                       | 58 |

|     |           | 4.2.3 | H-Spice Simulated Results                                 | 59 |

|     | 4.3       | Exp   | periment Results                                          | 60 |

|     |           | 4.3.1 | Characteristics of Substrate-Triggered STNMOS             | 60 |

|     |           | 4.3.2 | Turn-on Speed                                             | 61 |

|     |           | 4.3.3 | ESD Robustness of STNMOS Devices                          | 62 |

|     | 4.4       | Sun   | nmary                                                     | 62 |

| 1   | Tab       | les   |                                                           | 63 |

|     | Figu      | ıres  |                                                           | 64 |

| CHAPTER 5 ESD PROTECTION DESIGN FOR AUTOMOTIVE |       |                                                       | $\mathbf{E}$ |

|------------------------------------------------|-------|-------------------------------------------------------|--------------|

|                                                |       | VACUUM-FLUORESCENT-DISPLAY (VFD)                      |              |

|                                                |       | DRIVER IC                                             | 72           |

| 5.1                                            | Orig  | ginal Design for VFD I/O                              | 72           |

|                                                | 5.1.1 | Device Structure and I-V Characteristic of the HVPMOS | 73           |

|                                                | 5.1.2 | ESD robustness and Failure Analysis                   | 73           |

| 5.2                                            | Nev   | v ESD Design for VFD I/O                              | 74           |

|                                                | 5.2.1 | Device Structure and Turn-on Mechanism of the HVPSCR  | 74           |

|                                                | 5.2.2 | ESD Protection Design for VFD I/O with Both HVPSC     | R and        |

|                                                |       | Power-Rail ESD Clamp Circuit                          | 76           |

| 5.3                                            | Exp   | erimental Results                                     | 77           |

|                                                | 5.3.1 | I-V Characteristic of the HVPSCR                      | 77           |

|                                                | 5.3.2 | ESD robustness of the VFD Driver IC                   | 79           |

| 5.4                                            | Sun   | nmary                                                 | 79           |

| Tab                                            | oles  | E ESAN 3                                              | 81           |

| Fig                                            | ures  | 1896                                                  | 82           |

| CHAP                                           | TER 6 | ESD ROBUSTNESS OF ON-CHIP ESD                         |              |

|                                                |       | PROTECTION DEVICES IN 40-V CMOS                       |              |

|                                                |       | TECHNOLOGY                                            | 96           |

| 6.1                                            | Dev   | rice Structures in 40-V CMOS Process                  | 96           |

|                                                | 6.1.1 | HV NMOS With or Without N-Drift Implant               | 97           |

|                                                | 6.1.2 | HV PMOS With or Without P-Drift Implant               | 97           |

|                                                | 6.1.3 | HVNSCR With or Without N-Drift Implant                | 98           |

| 6.2                                            | Exp   | perimental Results and Discussion                     | 99           |

|                                                | 6.2.1 | TLP-Measured I-V Characteristics                      | 99           |

|                                                | 6.2.2 | HBM ESD Robustness                                    | 103          |

|                                                | 6.2.3 | Failure Analysis                                      | 105          |

| 6.3                                            | Sun   | nmary                                                 | 105          |

| Tables                                         |       |                                                       | 106          |

| Figures          |                                  | 107            |

|------------------|----------------------------------|----------------|

| СНАРТ            | TER 7 CONCLUSIONS AND FUTURE WOR | 2 <b>K</b> 120 |

| 7.1              | Main Results of This Thesis      | 120            |

| 7.2              | Future Works                     | 122            |

| REFER            | NCES                             | 123            |

| VITA             |                                  | 131            |

| PURLICATION LIST |                                  |                |

#### **TABLE CAPTIONS**

#### **CHAPTER 3**

| Table 3.1 | Breakdown voltage and breakdown current of the LVTPNP devices under | r both |

|-----------|---------------------------------------------------------------------|--------|

|           | positive-to-VSS and negative-to-VSS ESD-stress conditions.          | 36     |

| Table 3.2 | HBM ESD Levels of the LVTPNP devices with different layout styles   | under  |

|           | positive-to-VSS ESD-stress condition.                               | 37     |

| T 11 22   | HDM ECD I 1 C 4 I MEDND 1 : 41 I CC 4 1 4 4 1                       | 1      |

**Table 3.3** HBM ESD Levels of the LVTPNP devices with different layout styles under negative-to-VSS ESD-stress condition.

**Table 3.4** HBM ESD Levels of ADSL input stage with different ESD protection designs under PS-mode, NS-mode, PD-mode, and ND-mode ESD-stress conditions. 39

#### **CHAPTER 4**

**Table 4.1** HBM and MM ESD levels of STNMOS with or without ESD detection circuit.

63

#### **CHAPTER 5**

- **Table 5.1** TLP\_It2 and HBM ESD levels under negative-to-VDD ESD stresses of the HVPMOS.

- **Table 5.2** TLP\_It2, HBM and MM ESD levels under negative-to-VDD ESD stresses of the HVPSCR.

#### **CHAPTER 6**

- **Table 6.1** TLP-measured It2 of HV GGNMOS and HV GDPMOS with or without drift implant under different spacings D. 106

- **Table 6.2** TLP-measured It2 of HV GGNMOS and HVNSCR with or without drift implant under different spacings D.

# FIGURE CAPTIONS

### **CHAPTER 1**

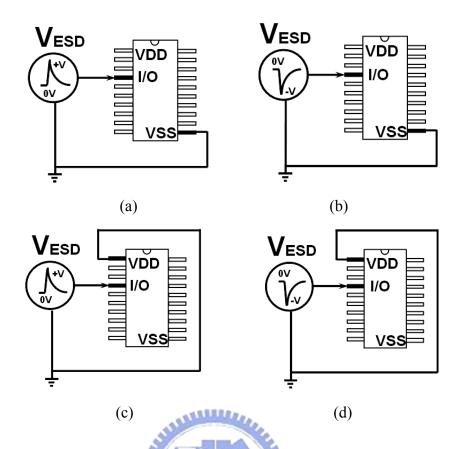

| Fig. 1.1        | The four pin-combination modes for ESD test on an IC product: (a) positive-to-VSS (PS-mode), (b) negative-to-VSS (NS-mode), (c) positive-to-VDD (PD-mode), and (d) negative-to-VDD (ND-mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

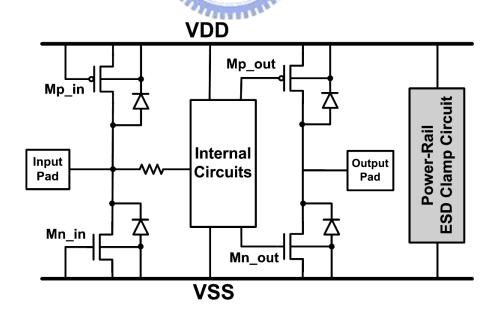

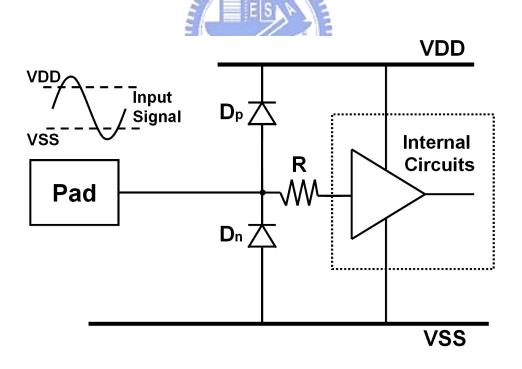

| Fig. 1.2        | Typical on-chip ESD protection circuits in a CMOS IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

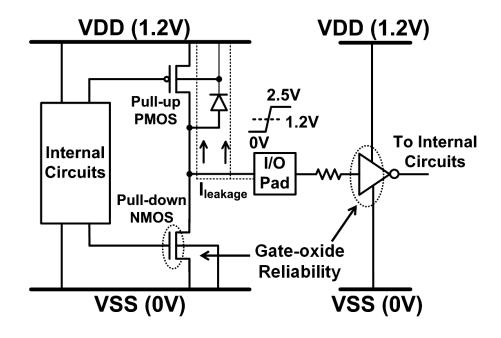

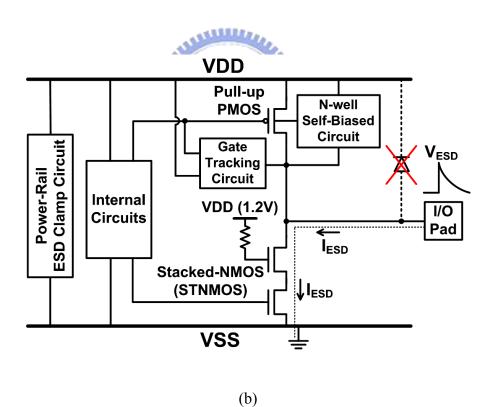

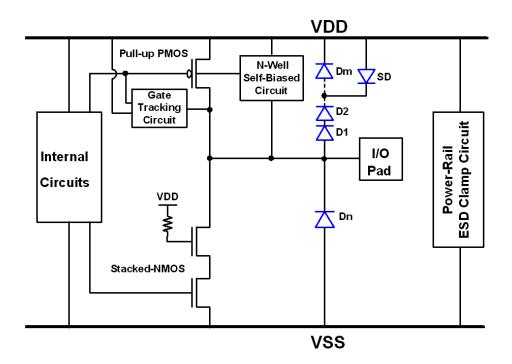

| Fig. 1.3        | Typical circuit diagrams for (a) the traditional CMOS I/O buffer, and (b) the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 116.110         | mixed-voltage I/O circuits with the stacked-NMOS and the N-well self-biased                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 | PMOS. 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

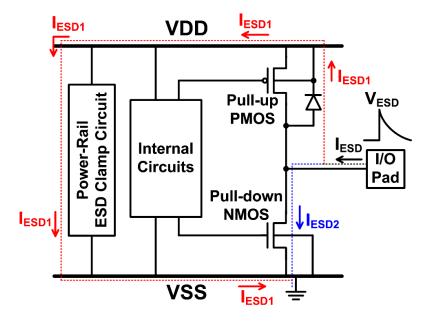

| Fig. 1.4        | The ESD current paths of (a) the traditional I/O pad with power-rail ESD clamp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.8.1           | circuit, and (b) the mixed-voltage I/O pad with power-rail ESD clamp circuit,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 | under the positive-to-VSS (PS-mode) ESD stress. The ESD current paths are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 | indicated by the dashed lines.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

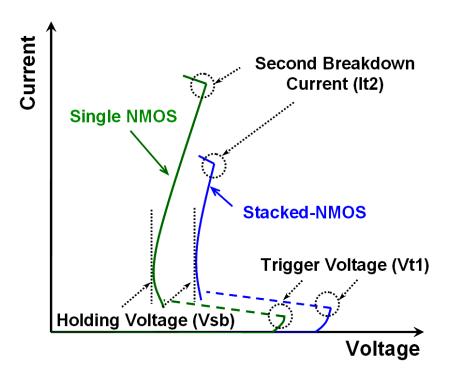

| Fig. 1.5        | The I-V curves in high-current region of single NMOS and stacked-NMOS. 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Fig. 1.6        | The input signals with voltage levels higher than VDD and lower than VSS in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8               | some mixed-voltage I/O interfaces.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | The state of the s |

| CHAPTI          | ER 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

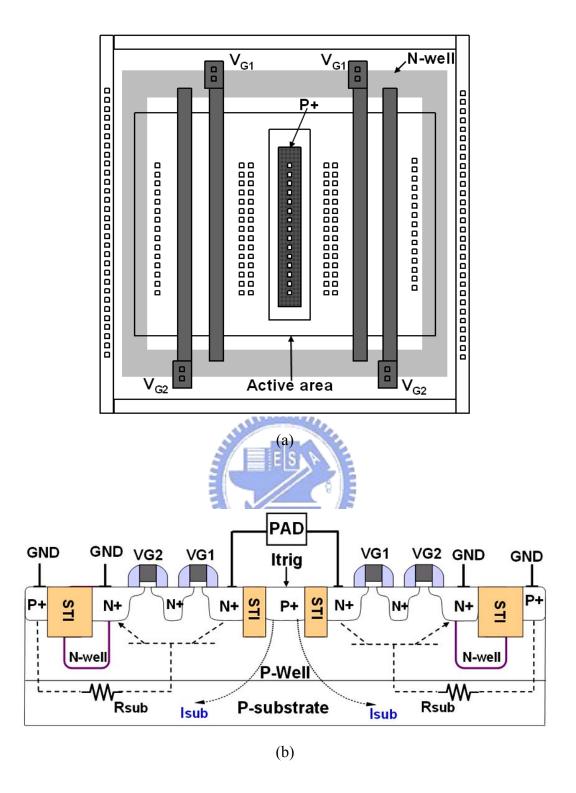

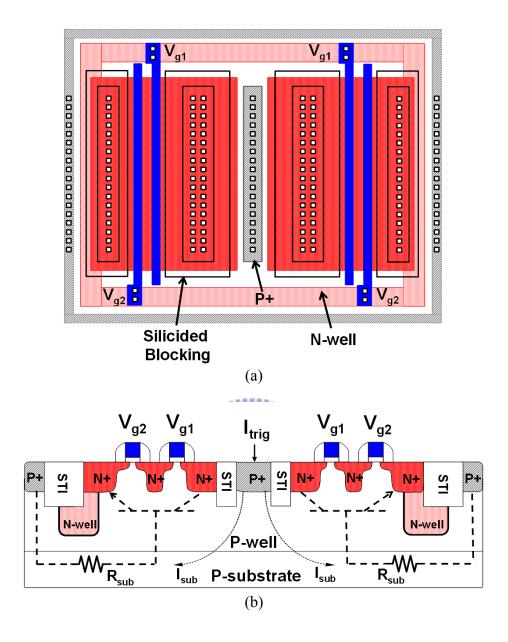

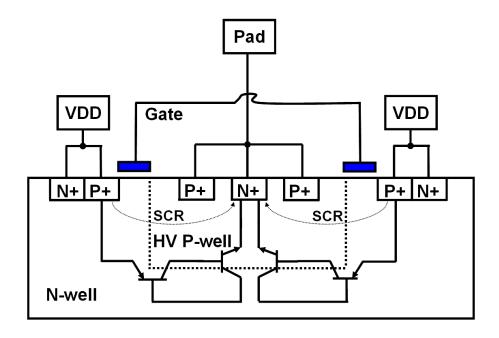

| Fig. 2.1        | (a) Finger-type layout pattern, and (b) the corresponding cross-sectional view, of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | the substrate-triggered stacked-NMOS device for mixed-voltage I/O circuits. 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

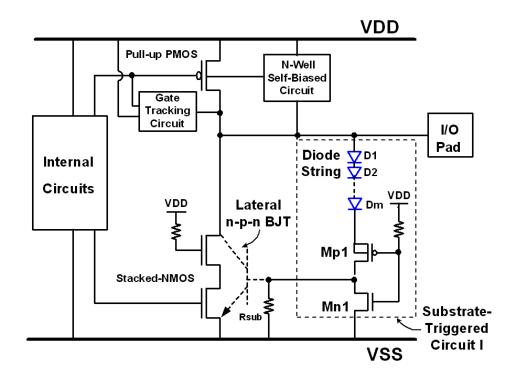

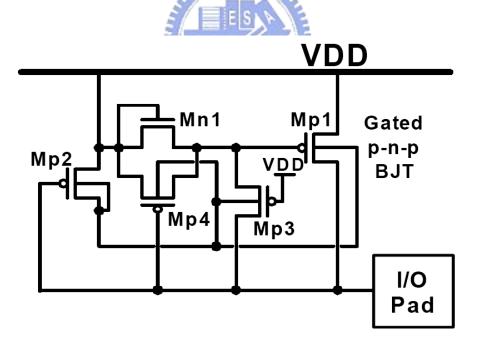

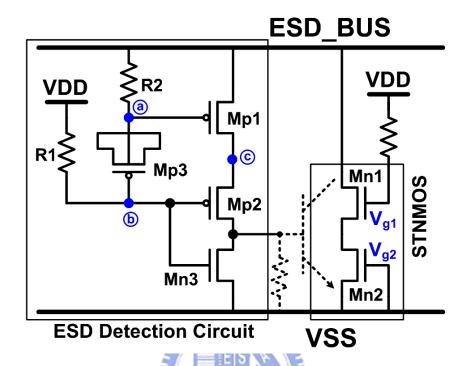

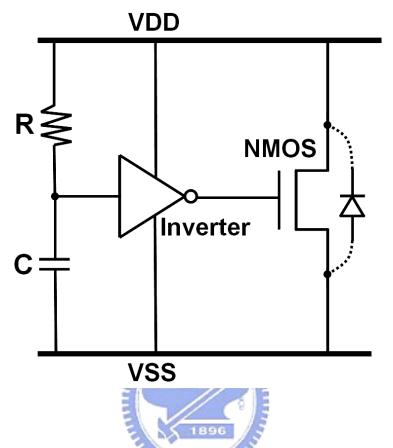

| Fig. 2.2        | Schematic circuit diagram of the substrate-triggered stacked-NMOS device with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 | substrate-triggered circuit I for the mixed-voltage I/O circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

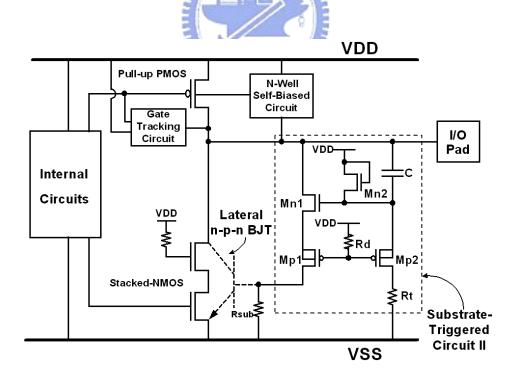

| Fig. 2.3        | Schematic circuit diagram of the substrate-triggered stacked-NMOS device with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 | substrate-triggered circuit II for the mixed-voltage I/O circuits. 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

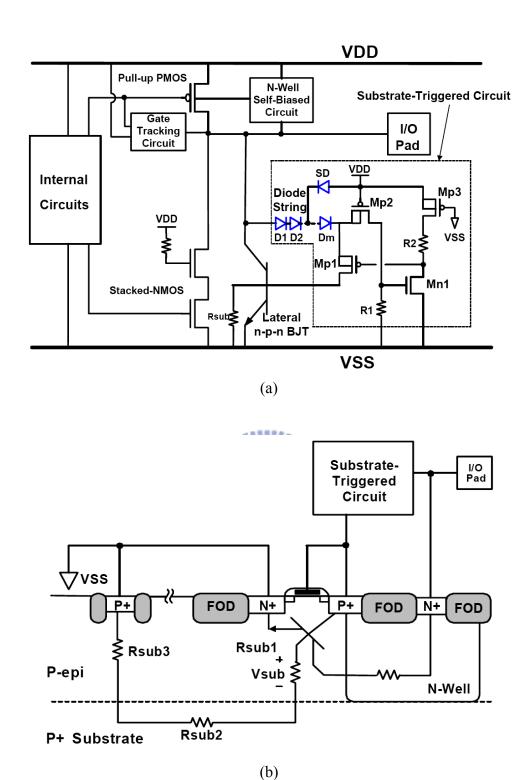

| Fig. 2.4        | (a) ESD protection design with substrate-triggered lateral n-p-n BJT device to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | protect the mixed-voltage I/O circuits. (b) Cross-sectional view of the lateral                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 | n-p-n BJT device in a thin-epi CMOS process.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

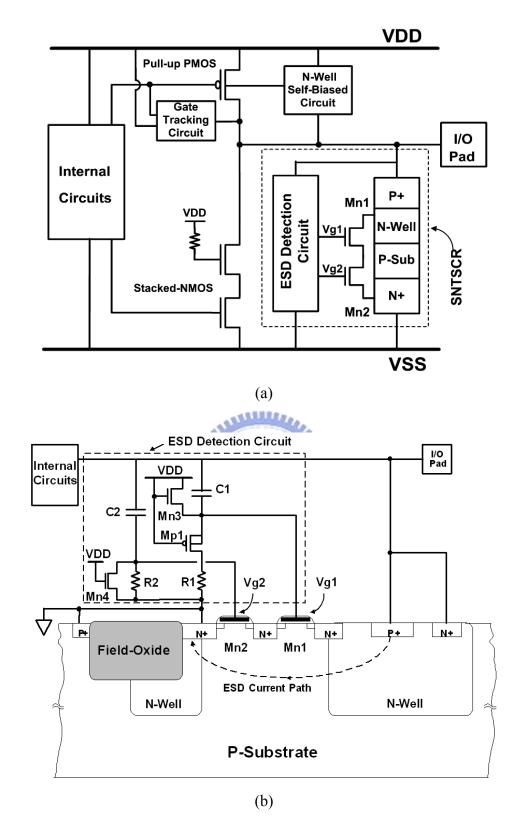

| Fig. 2.5        | (a) ESD protection circuit with the SNTSCR device to protect the mixed-voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | I/O circuits. (b) Realizations of the SNTSCR device and the ESD detection circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                 | with the gate-coupling technique to trigger on the SNTSCR device. 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

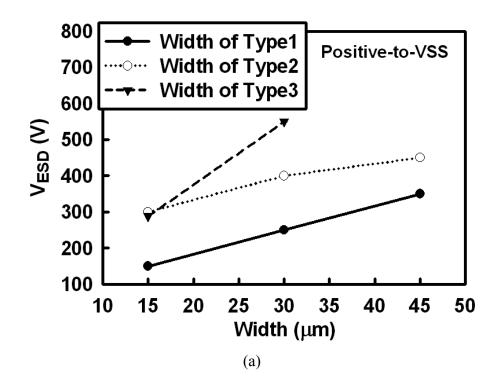

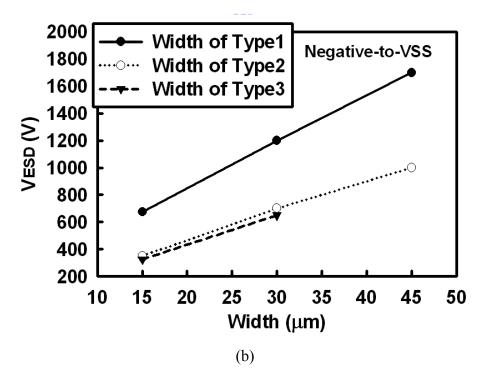

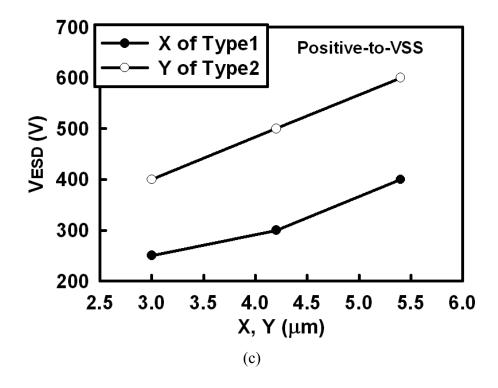

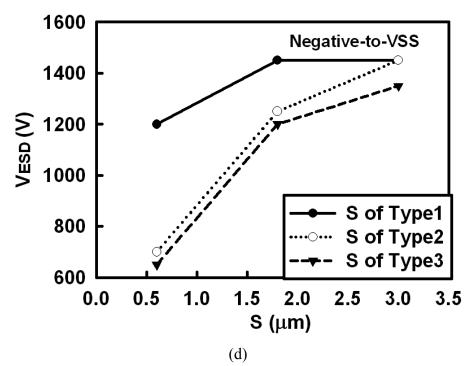

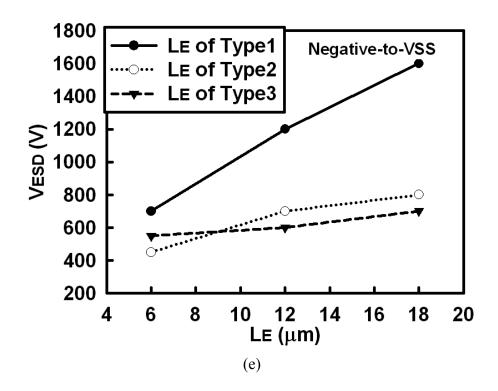

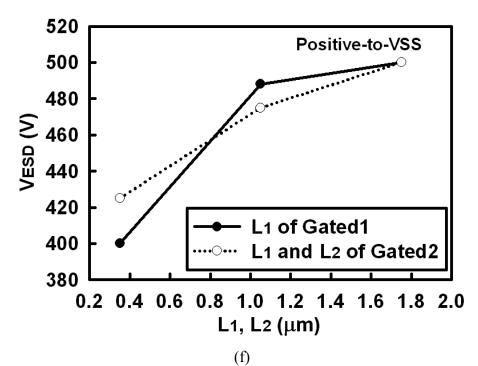

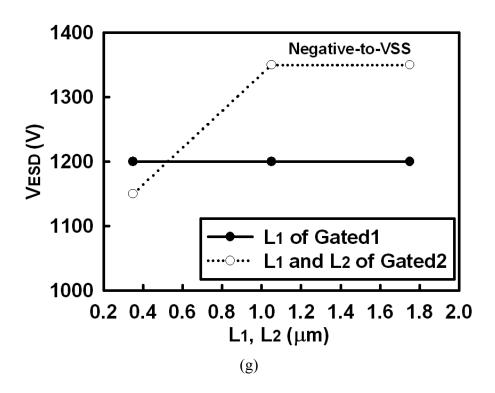

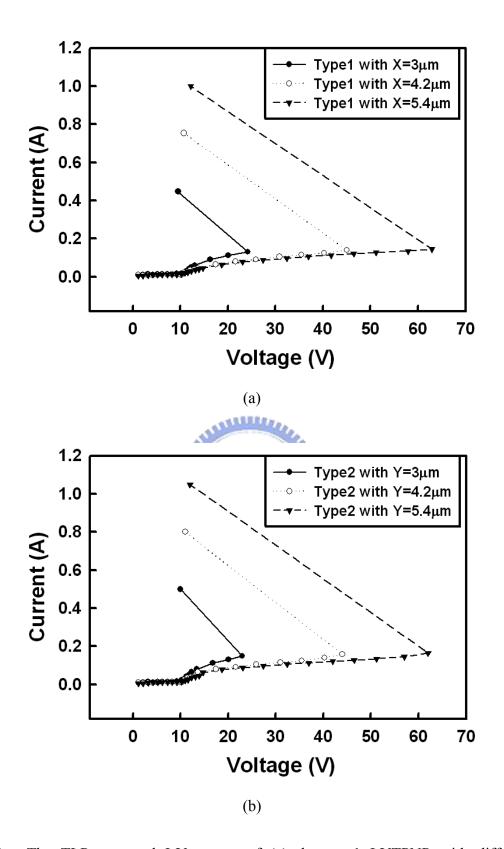

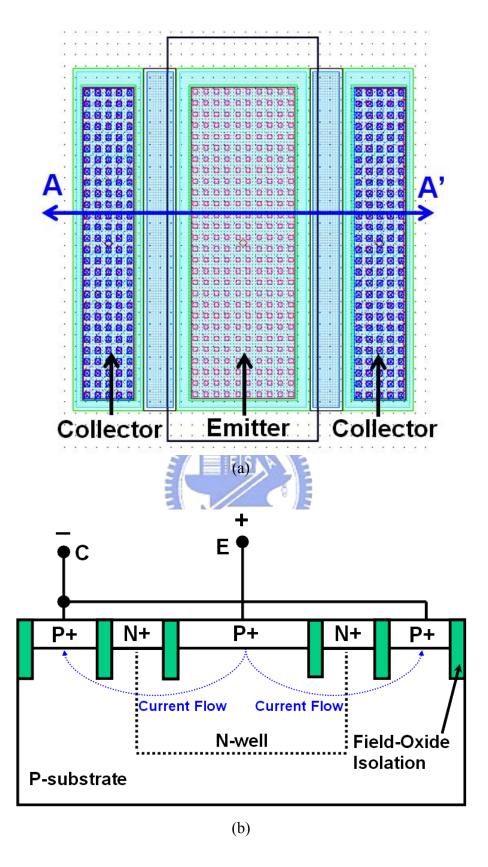

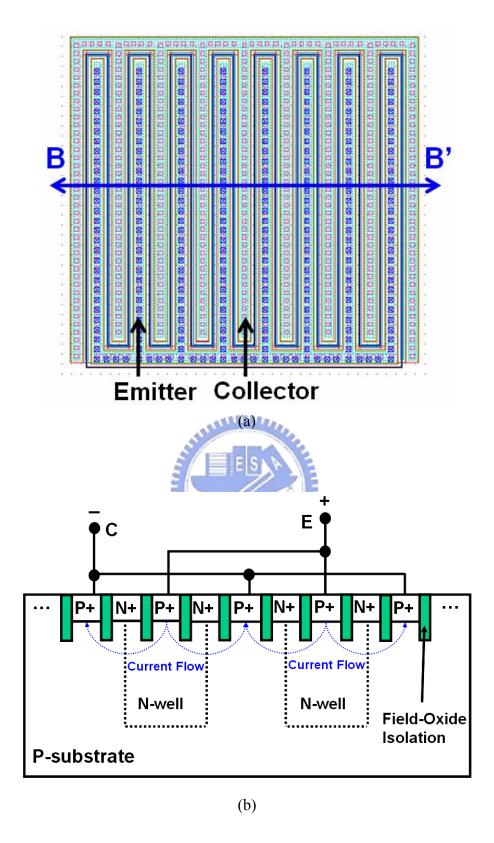

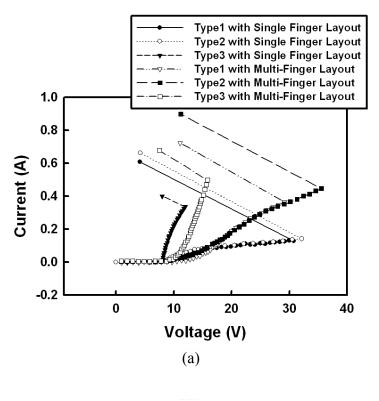

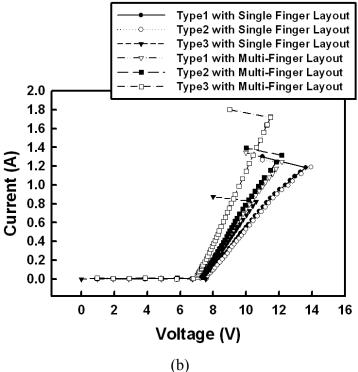

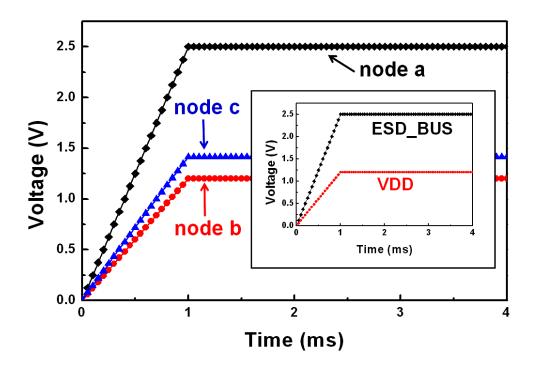

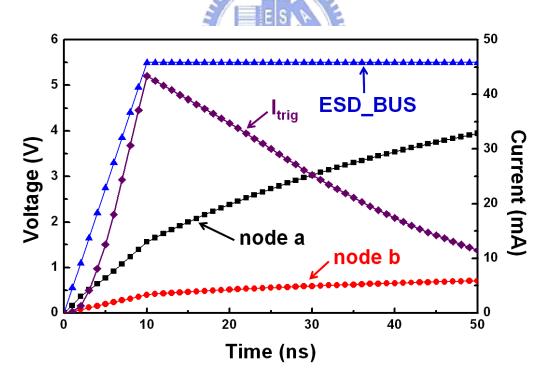

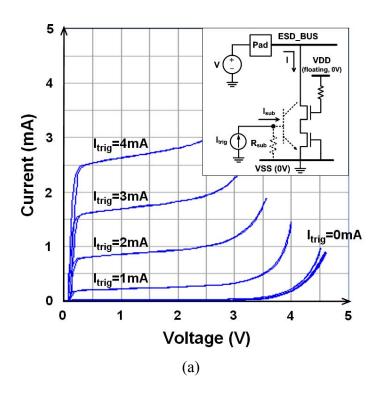

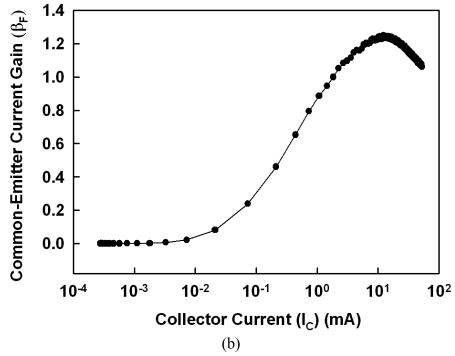

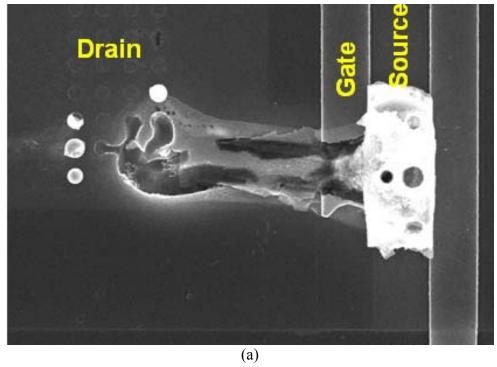

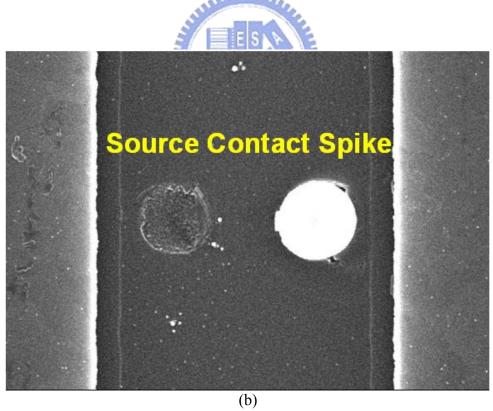

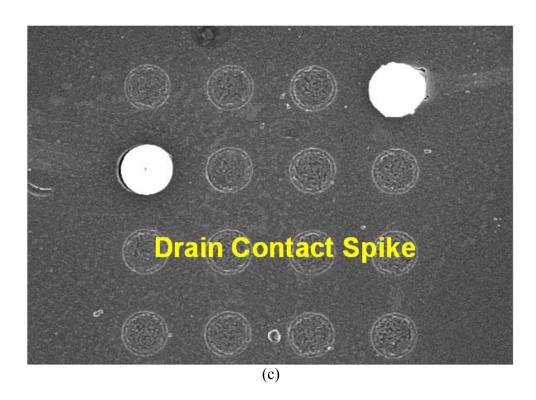

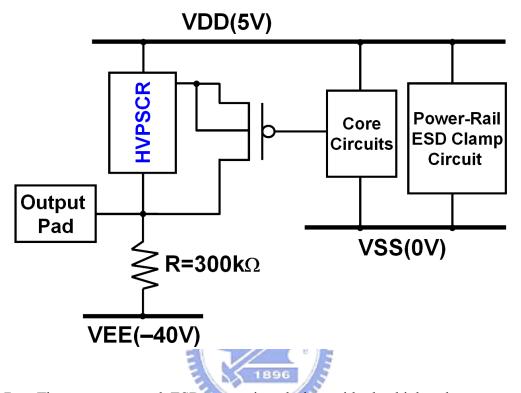

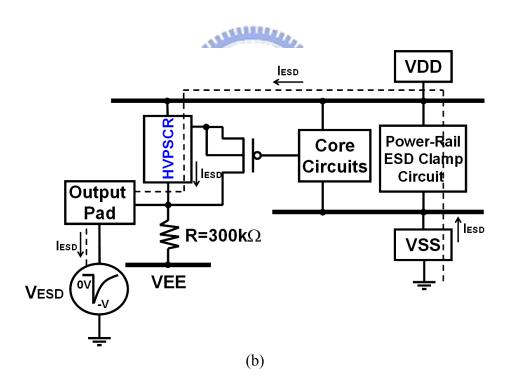

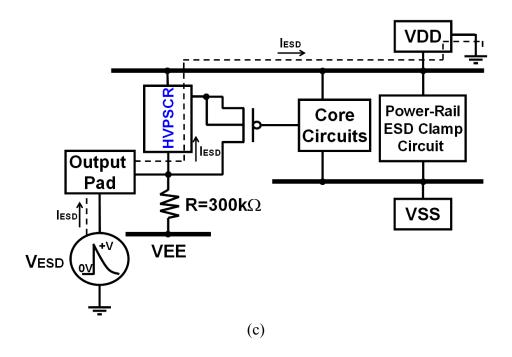

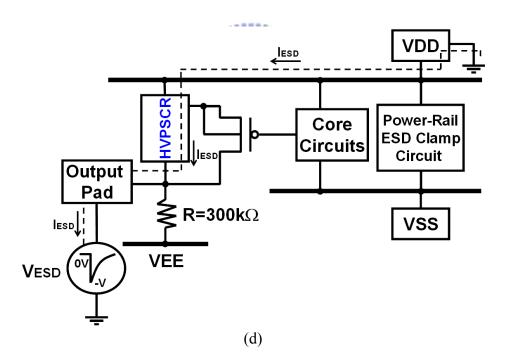

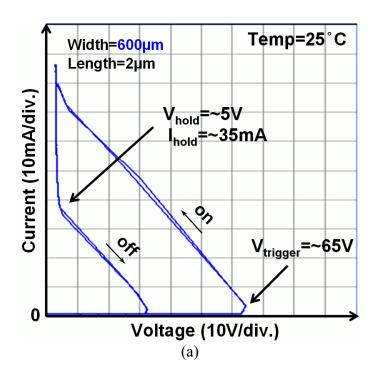

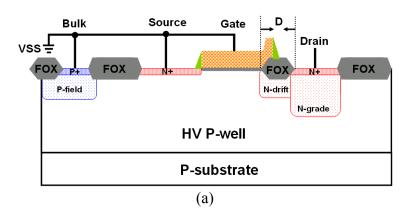

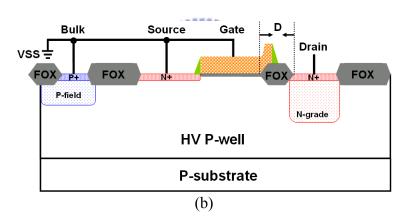

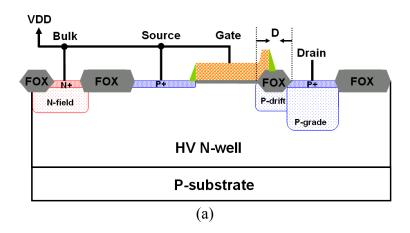

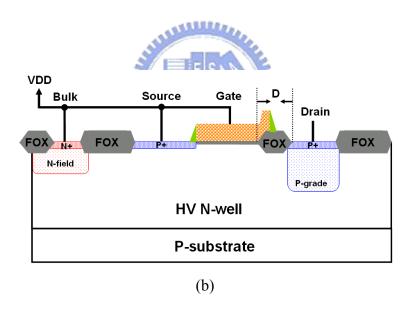

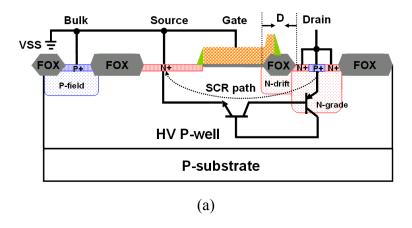

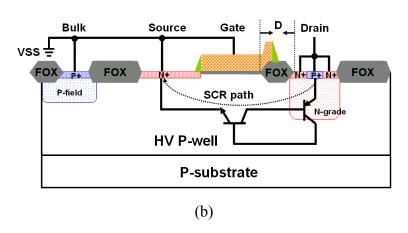

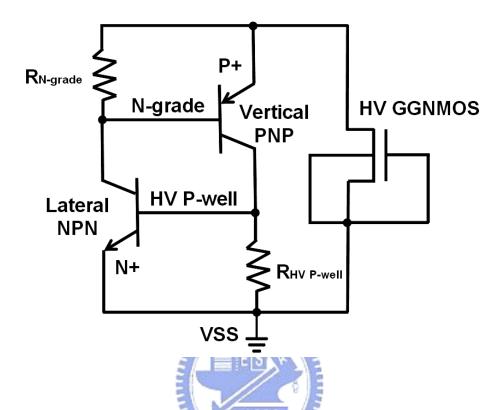

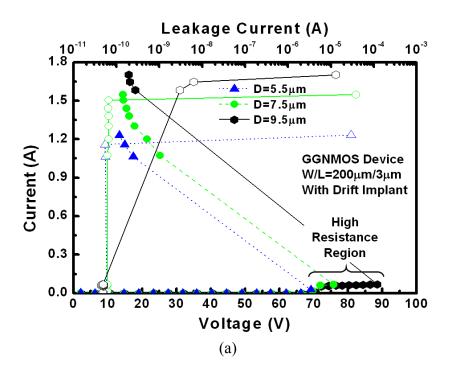

| <b>Fig. 2.6</b> | ESD protection design with the diode string connected between the I/O pad and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |