# 國立交通大學

電子工程學系 電子研究所碩士班

碩士論文

90 奈米互補式金氧半製程下 之多功能輸入/輸出元件庫設計

# Design of Configurable I/O Cell Library in 90-nm CMOS Process

研究生: 陳世範 (Shih-Fan Chen)

指導教授: 柯明道教授 (Prof. Ming-Dou Ker)

中華民國九十七年九月

# 90 奈米互補式金氧半製程下 之多功能輸入/輸出元件庫設計

# Design of Configurable I/O Cell Library in 90-nm CMOS Process

研究生: 陳世範 Student: Shih-Fan Chen

指導教授:柯明道教授 Advisor: Prof. Ming-Dou Ker

國立交通大學 電子工程學系 電子研究所 碩士論文

#### A Thesis

Submitted to Department of Electronics Engineering and Institute of Electronics

College of Electrical and Computer Engineering

National Chiao-Tung University in Partial Fulfillment of the Requirements for the Degree of

Master

in

Electronics Engineering September 2008 Hsin-Chu, Taiwan, Republic of China

中華民國九十七年九月

# 90 奈米互補式金氧半製程下 之多功能輸入/輸出元件庫設計

學生: 陳世範 指導教授: 柯明道教授

#### 國立交通大學 電子工程學系電子研究所碩士班

#### ABSTRACT (CHINESE)

在積體電路(Integrated Circuits)設計中,元件庫(Cell Library)是不可或缺的一個重要部分,因為元件庫包含了組成積體電路的所有最基本單元。其中,輸入/輸出單元 (Input/Output Cell, I/O Cell)連接積體電路與外界,並提供輸出驅動電流或接收輸入訊號的功能,亦保護積體電路免於遭受靜電放電(electrostatic discharge, ESD)損壞。然而,隨著互補式金氧半導體(Complementary Metal-Oxide-Semiconductor, CMOS)積體電路製程技術的演進,積體電路中的電晶體尺寸逐漸縮小,電路功能越來越多,操作速度也越來越快,元件庫勢必要提供更多不同功能的輸出入單元,以因應各種電路需求。此外,電晶體閘極氧化層的崩潰電壓隨著製程演進日益降低,造成積體電路產品的靜電放電耐受度下降。因此元件庫的設計在先進互補式金氧半製程中,存在更多的困難與挑戰。

本論文在 90 奈米互補式金氧半製程中,設計並驗證一套輸入/輸出元件庫,此多功能輸入/輸出元件庫包含多功能輸入/輸出單元(Configurable I/O Cell)、電源單元(Power Cell)、類比輸入/輸出單元(Analog I/O Cell)和電源切斷單元(Power Break Cell)。輸出單元內可以控制電流驅動能力,並可在三態(Tri-State)時選擇是否具有拉高(Pull Up)至高邏輯

#### ABSTRACT (CHINESE)

準位(Logic High)或拉低(Pull Down)至低邏輯準位(Logic Low)之功能。在輸入單元部分,可以選擇是否具有史密特觸發(Schmitt-Trigger)功能,以提升對輸入訊號的雜訊抵抗能力,這些功能皆由單一輸出入單元完成。此外,隨著瞬間輸出電流增加,接地電位彈跳現象(Ground Bounce)將越來越嚴重,使得電路可能發生功能錯誤的現象。本輸入/輸出單元亦提供一個具有電壓迴轉率控制(Slew-Rate Control)的多功能輸出入單元以抑制接地電位彈跳現象。靜電放電防護方面,本輸入/輸出元件庫提供了多組高效能靜電放電防護電路,以建構完整的全晶片(Whole-Chip)靜電放電防護。本論文以 90 奈米互補式金氧半製程設計並製作此輸入/輸出元件庫,實驗晶片的量測結果已成功驗證此輸入/輸出元件庫之所有功能,包含接收輸入訊號、傳送輸出訊號、電壓迴轉率控制與全晶片靜電放電防護。

**Design of Configurable I/O Cell Library**

in 90-nm CMOS Process

Student: Shih-Fan Chen

Advisor: Prof. Ming-Dou Ker

Department of Electronics Engineering and Institute of Electronics

National Chiao-Tung University

ABSTRACT (ENGLISH)

The cell library plays an important role in integrated circuits (ICs), because it includes all

of fundamental cells to construct the ICs. In the cell library, the input/output (I/O) cells

provide the link between the ICs and outward. Thus, the I/O cells are used to provide the

driving currents, to receive the input signals, and to protect the ICs against electrostatic

discharge (ESD) damages. As the feature size of MOS transistors shrinks with the advance of

complementary metal-oxide-semiconductor (CMOS) technology, the circuit functions become

more complex and the operating frequency becomes higher. However, thinner gate-oxide

decreases the ESD robustness of MOS transistors. Hence, there are more challenges and limits

for the I/O cell library design in nanoscale CMOS technology.

In this thesis, an I/O cell library is designed in 90-nm CMOS technology. The I/O cell

library includes the configurable I/O cells, analog I/O cells, power cells, and power break cell.

In the configurable I/O cell, the output stage is used to provide driving current. Besides, it can

- iii -

#### ABSTRACT (ENGLISH)

pull the I/O pad up to logic high or pull the I/O pad down to logic low under the tri-state. In input stage, a schmitt-trigger is realized and can be turned on to increase the noise margin of input signal. All of the aforementioned functions have been integrated in a single configurable I/O cell proposed in this thesis. Moreover, the ground bounce issue becomes more critical as the instantaneous driving current becomes larger. In the proposed I/O cell library, the slew-rate-control unit is realized in another configurable I/O cell to mitigate the ground bounce issue. In addition, several effective ESD protection circuits are designed in this I/O cell library to provide whole-chip ESD protection. The proposed I/O cell library has been fabricated in 90-nm CMOS process. Experimental results have successfully verified all of the functions provided in the I/O cell library, including receiving input signals, transmitting output signals, slew-rate control, and whole-chip ESD protection.

## 致謝

在短暫且充實的碩士研究生活中,我要感謝指導教授<u>柯明道</u>博士。艱苦的研究過程中,老師不畏辛苦地反覆指導,選擇不直接告訴我答案,而是細心地指引研究方向。因此我要向<u>柯明道</u>教授致上我最高的謝意,使我在靜電放電防護領域從零到擁有晶片下線驗證及解決問題的能力。同時也學習到老師正確的處事態度及做事方法,畢業後我一定會記住老師教導的一切,好好在工作領域上發揮。

其次,我要感謝『工研院系統晶片技術發展中心-產品與靜電防護技術部』提供許多研究資源及寶貴意見,在剛進入學校時可以快速進步。特別感謝<u>吳文慶</u>組長、<u>簡丞星</u>副組長、<u>柏獅、世宏</u>學長,給予數不清的 layout 及量測建議。還有校長、<u>小繆、清吉、伯瑋、項彬</u>等諸位學長,感謝你們給予許多生涯規劃的想法。最後是<u>哲維、信源</u>學長,謝謝你們陪我在工研院裡一起嘻笑做研究。

另外,感謝『UMC-RT&A/ESD』的天浩經理,給予我研究中無限的支持、<u>新言</u>學長提供一堆設計 ESD 防護的技巧及觀念、文祺學長的游泳初體驗、<u>書玄</u>學姐的 call call 樂、<u>萌慧</u>姐的借機器、<u>季陽</u>學長的機車話教學、大正學長的高壓扣殺、<u>Ruth</u>的 TOTO 打折、<u>泰翔</u>老大溫柔關愛的眼神還有無可挑剔的擁抱、大嫂的閃光攻勢、<u>桂枝</u>姐有名又好吃的下午茶、<u>暢資</u>學長震撼的報告、<u>Grace</u> 姐的英文教學、<u>Alice</u> 姐很給面子的笑聲和無私的關心,最後還有<u>堂龍</u>學弟的量測陪伴,謝謝你們。

當然,還要感謝『奈米電子與晶片系統實驗室』的陳榮昇、許勝福、顏承正、陳穩義、王資閱、林群祐、張瑋仁等諸位學長們,給我相當多的指導與幫助。感謝宗諭學長、豪哥、介堯學長、鯉魚學長、俊哥、順哥、國忠學長,在課業或研究給予許多建議。特別感謝芳綾、佳惠學姐、宏泰學長,在我最無知的時候教導我電路設計及觀念。還有蕭淵文學長,不辭辛苦地幫我改論文及投影片,真是太感謝太感謝了。感謝詹豪傑學長給我一個學習的好榜樣。還有所有碩士班的同學們,帥到掉渣的阿邦、每個禮拜都要一起健身的期聖跟阿喵、陸享享的所有白痴行徑、常常告訴我哪裡有好笑的紹岐、有暴力傾向的老大仔、跟我是麻吉的威宇、黑 x 幫的阿宅、老人歐陽、剛剛交女友的宗恩、強大區文、無恥的科科、直球國維、英文超厲害的塔哥、很有錢的建名、蒙神、曄仁,以及學弟彥良、順天、小勻、該儒、哲倫、韋霖、白襪的佐達、小熊萬歲的思翰和學妹佳琪、怡歆、筱任、惠雯,因為有你們的陪伴,使這碩士生涯充滿歡笑及溫暖。

最後,謝謝我最愛的家人。偉大的父親<u>陳明和</u>和母親<u>方月娥</u>,您們這一生對我無私的付出,讓我全心全意地完成學業,沒有您們傾力的栽培,無法完成這論文,您們是此論文最大的推手,謝謝您們。大姊<u>陳惠真</u>、二姐<u>陳婉真</u>,感謝你們願意在背後給予這個對家裡沒什麼貢獻的弟弟最大的支持。還有親愛的<u>小宛儒</u>,每每在我耳朵旁邊一直喊加油到都快讓我耳聾的妳,是我努力向前的最大動力。也謝謝所有幫助過我的人,謝謝!

陳 世 範 僅誌於竹塹交大 民國九十七年九月

# **CONTENTS**

| <b>ABST</b>  | RACT (CHINESE)                                        | i     |

|--------------|-------------------------------------------------------|-------|

| ABST         | RACT (ENGLISH)                                        | iii   |

| ACKN         | OWLEDGEMENT                                           | v     |

| TABL         | CAPTIONS                                              | viii  |

| <b>FIGUI</b> | E CAPTIONS                                            | X     |

| Chapte       | r 1 Introduction                                      | 1     |

| 1.3          | MOTIVATION                                            | 1     |

|              | 1.1.1 Issue of I/O Interface                          | 1     |

|              | 1.1.2 Issue of ESD                                    | 3     |

| 1.2          | INTRODUTION OF CONFIGURABLE I/O CELL LIBRARY          | 3     |

| 1.3          | THESIS ORGANIZATION                                   | 4     |

| Chapte       | r 2 Design and Simulation Results of Configurable I/O | Cell8 |

| 2.1          | INTRODUCTION OF CONFIGURABLE I/O CELL                 |       |

| 2.2          |                                                       |       |

| 2.3          |                                                       |       |

|              | 2.3.1 Driving Capability                              | 10    |

|              | 2.3.2 Short-circuit Current Reduction                 |       |

| 2.4          | Pre-driverLevel Shifter                               | 13    |

| 2.5          | LEVEL SHIFTER                                         | 14    |

| 2.0          | INPUT STAGE                                           | 15    |

| 2.7          | PULL-UP/PULL-DOWN NETWORK                             | 16    |

| 2.8          | SLEW-RATE CONTROL                                     | 17    |

|              | 2.8.1 Introduction                                    | 17    |

|              | 2.8.2 Concept of Slew-rate Control                    | 19    |

|              | 2.8.3 Design of Slew-rate Control                     | 19    |

| Chapte       | r 3 Design of ESD Protection Circuits                 | 57    |

| 3.1          | INTRODUCTION                                          | 57    |

| 3.2          | POWER/GROUND CELLS                                    | 58    |

| 3.3          | ANALOG I/O CELLS                                      | 60    |

| 3.4          | POWER BREAK CELL                                      | 60    |

| Chapte       | r 4 Physical Layout of Configurable I/O Cell Library  | 67    |

| 4.1          | CONFIGURABLE I/O CELL WITH SLEW-RATE CONTROL          | 67    |

| 4.2          | POWER/GROUND CELLS AND ANALOG I/O CELLS               | 67    |

| 4.3          | POWER BREAK CELL                                      | 68    |

| 4 4          | FILLER AND CONRNER CELLS                              | 68    |

#### **CONTENTS**

| Chap | ter      | 5 Test   | Chip Arrangement of Configurable I/O Cell Library        | 77  |

|------|----------|----------|----------------------------------------------------------|-----|

| 5    | 5.1      | VERIVIC  | ATION ON CONFIGURABLE I/O CELL                           | 77  |

|      |          | 5.1.1    | Pull-Up/Pull-Down Resistance                             | 77  |

|      |          | 5.1.2    | Schmitt-trigger Threshold Points                         | 78  |

|      |          | 5.1.3    | Driving Capability                                       | 79  |

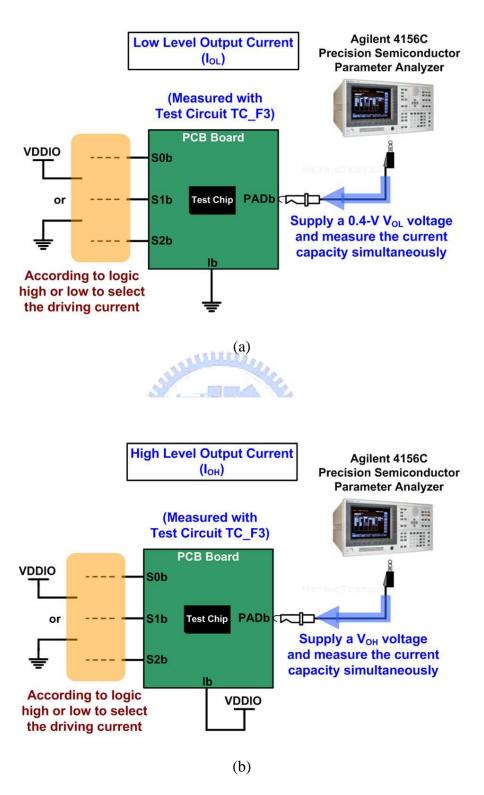

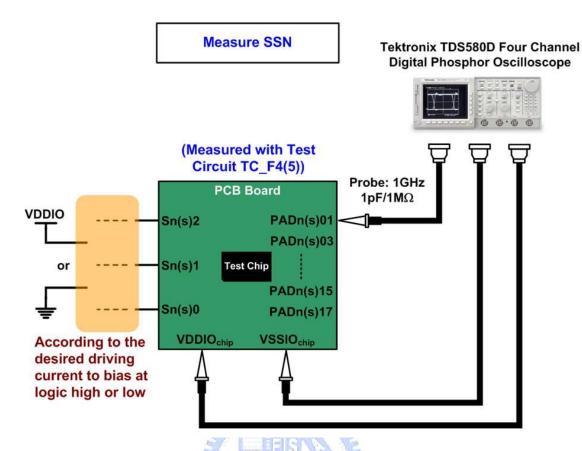

|      |          | 5.1.4    | Simultaneous Switching Noise (SSN) and Propagation Delay | 80  |

| 5    | 5.2      | VERIFICA | TION ON THE ESD ROBUSTNESS OF EACH CELL                  | 83  |

| 5    | 5.3      | VERIFICA | TION ON WHOLE-CHIP ESD PROTECTION                        | 83  |

| Chap | ter      | 6 Expe   | erimental Results                                        | 101 |

| 6    | 6.1      | FUNCTION | VERIFICATION                                             | 101 |

|      |          | 6.1.1    | Pull-up/Pull-down Resistance                             | 101 |

|      |          | 6.1.2    | Schmitt-trigger Threshold Point                          | 102 |

|      |          | 6.1.3    | Driving Capability                                       | 102 |

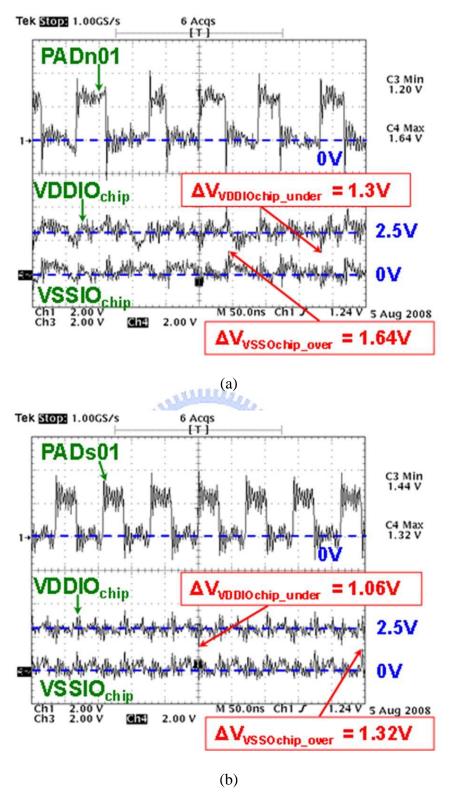

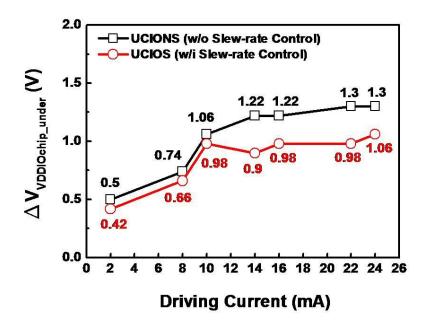

|      |          | 6.1.4    | Simultaneous Switching Noise (SSN)                       | 103 |

|      |          | 6.1.5    | Propagation Delay                                        | 103 |

|      |          | 6.1.6    | Operating Frequency                                      |     |

| 6    | 6.2      | ESD ROB  | USTNESS                                                  |     |

|      |          | 6.2.1    | Each Power Cell                                          | 105 |

|      |          | 6.2.2    | Whole-Chip ESD Protection Structure                      | 106 |

| 6    | 6.3      | SUMMARY  | 7 E E                                                    | 107 |

| Chap | ter      | 7 Cond   | clusions and Future Works                                | 134 |

| 7    | 7.1      | CONCLUS  | VORKS                                                    | 134 |

| 7    | 7.2      | FUTURE W | VORKS                                                    | 135 |

| REFI | ERI      | ENCES    |                                                          | 136 |

| VITA | <b>\</b> |          | ••••••                                                   | 139 |

# TABLE CAPTIONS

| Tabel 1.1  | Configurable I/O cell library.                                                                | 5   |

|------------|-----------------------------------------------------------------------------------------------|-----|

| Tabel 2.1  | Pin description.                                                                              | .21 |

| Tabel 2.2  | Configurable I/O cell with different output driving.                                          | .21 |

| Tabel 2.3  | State of I/O PAD in configurable I/O cell with different input signal                         | .22 |

| Tabel 2.4  | DC specification of configurable I/O cell in 2.5-V VDDIO supply voltage                       | .23 |

| Tabel 2.5  | DC specification of configurable I/O cell in 1.8-V VDDIO supply voltage                       | .24 |

| Tabel 2.6  | DC specification of configurable I/O cell in 3.3-V VDDIO supply voltage                       | .25 |

| Tabel 2.7  | Simulation Environment                                                                        | .26 |

| Tabel 2.8  | Simulation results of pull low driving current (I <sub>OL</sub> ) of output NMOS in different | ent |

|            | simulation conditions.                                                                        | .26 |

| Tabel 2.9  | I <sub>OH</sub> and duty cycle comparison between two methods of MP0 design                   | .27 |

| Tabel 2.10 | Simulation results of high level output current (I <sub>OH</sub> ) of output PMOS designed    | ł   |

|            | with the second method in different simulation environments                                   | .27 |

| Tabel 2.11 | Duty cycle in different simulation environment.                                               | .28 |

| Tabel 2.12 | Simulation results of duty cycle in different output MOS fingers and operati                  | ng  |

|            | frequencies with 2.5-V VDDIO voltage supply.                                                  | .28 |

| Tabel 2.13 | Simulation results of duty cycle in different output MOS fingers and operati                  | ng  |

|            | frequencies with 1.8-V VDDIO voltage supply.                                                  | .29 |

| Tabel 2.14 | Simulation results for duty cycle in different output MOS fingers and operat                  | ing |

|            | frequencies with 3.3-V VDDIO voltage supply.                                                  | .29 |

| Tabel 2.15 | Truth table of pre-driver.                                                                    | .30 |

| Tabel 2.16 | Duty cycle simulations under different VDDIO voltage supply with input sign                   | ıal |

|            | $V_{in} = 0 \sim VDDIO$ , $T_r = T_f = 0.1ns$ , pulse width=1.875ns, period = 3.75ns,         |     |

|            | $frequency = 266MHz, and C_{load} = 20fF.$                                                    | .31 |

| Tabel 2.17 | Threshold voltages of schmitt-trigger under different simulation conditions                   | .31 |

| Tabel 2.18 | Tabel 2.18 Duty Cycle of schmitt-trigger input stage under different simulation conditions    |     |

|            | with input signal $V_{PAD} = 0 \sim VDDIO$ , $T_r = T_f = 0.1ns$ , pulse width=1.875ns,       |     |

|            | period = $3.75$ ns, frequency = $266$ MHz, and $C_{load} = 0.1$ pF                            | .32 |

| Tabel 2.19 | Duty Cycle of normal input stage under different simulation conditions with                   |     |

|            | input signal $V_{PAD} = 0 \sim VDDIO$ , $T_r = T_f = 0.1 ns$ , pulse width=1.875ns, period    | =   |

|            | $3.75$ ns, frequency = $266$ MHz, and $C_{load} = 0.1$ pF                                     | .32 |

| Tabel 2.20 | Equivalent pull-up resistance (R <sub>PU</sub> ) in simulated circuit under different         |     |

|            | simulation conditions.                                                                        | .33 |

| Tabel 2.21 | Equivalent pull-down resistance $(R_{PD})$ in simulated circuit under different               |     |

|            | simulation conditions.                                                                        | .33 |

| Tabel 2.22 | Variation of pull-up/pull-down resistance                                                     | .34 |

| Tabel 2.23 | Reduction of the maximum switching current on VDDIO power line under           |    |  |

|------------|--------------------------------------------------------------------------------|----|--|

|            | different simulation conditions                                                | 34 |  |

| Tabel 2.24 | Reduction of the maximum switching current on VSSIO ground line under          |    |  |

|            | different simulation conditions                                                | 35 |  |

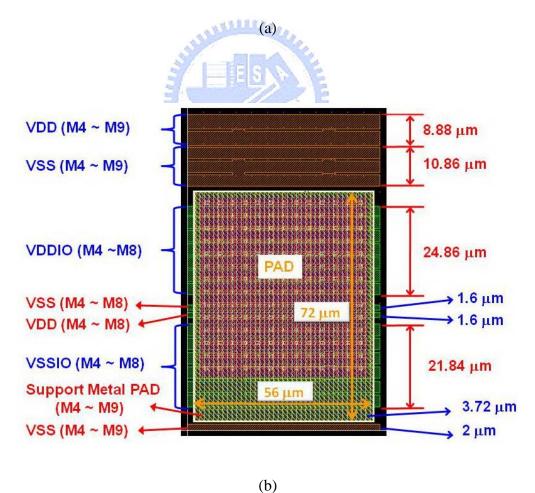

| Tabel 4.1  | Layer name definition of bond pad.                                             | 69 |  |

| Tabel 5.1  | Definition of function test circuit.                                           | 84 |  |

| Tabel 5.2  | Threshold voltages of input stage under different simulation conditions        | 85 |  |

| Tabel 5.3  | Driving capability of configurable I/O cell in 1.8-V VDDIO supply voltage      | 85 |  |

| Tabel 5.4  | Driving capability of configurable I/O cell in 2.5-V VDDIO supply voltage      | 86 |  |

| Tabel 5.5  | Driving capability of configurable I/O cell in 3.3-V VDDIO supply voltage      | 87 |  |

| Tabel 5.6  | Comparisons of propagation delays.                                             | 87 |  |

| Tabel 6.1  | The simulation and measurement results of pull-up/pull-down network1           | 08 |  |

| Tabel 6.2  | The simulation and measurement results of input stage threshold points1        | 08 |  |

| Tabel 6.3  | Measurement results of the driving capability under 2.5-V VDDIO supply         |    |  |

|            | voltage1                                                                       | 09 |  |

| Tabel 6.4  | Measurement results of the driving capability under 1.8-V VDDIO supply         |    |  |

|            | voltage1                                                                       | 09 |  |

| Tabel 6.5  | Measurement results of the driving capability under 3.3-V VDDIO supply         |    |  |

|            | voltage. 1                                                                     | 10 |  |

| Tabel 6.6  | The operating frequency of the configurable I/O cell operating in transmitting |    |  |

|            | mode with different driving current and VDDIO supply voltage                   | 10 |  |

| Tabel 6.7  | HBM and MM ESD robustness of the UVDD25 and UVDD10 cells                       | 11 |  |

| Tabel 6.8  | HBM and MM ESD robustness of the UVSS25 cell1                                  | 11 |  |

| Tabel 6.9  | HBM and MM ESD robustness of the UVSS10 cell                                   | 11 |  |

| Tabel 6.10 | HBM and MM ESD robustness of the 2.5-V analog I/O cells                        | 12 |  |

| Tabel 6.11 | HBM and MM ESD robustness of the 1.0-V analog I/O cells1                       | 12 |  |

| Tabel 6.12 | HBM and MM ESD robustness of the power break cell1                             | 12 |  |

| Tabel 6.13 | HBM and MM ESD robustness of whole-chip protection with power break cell       | l  |  |

|            | 1                                                                              | 13 |  |

| Tabel 6.14 | HBM and MM ESD robustness of configurable I/O cell with whole-chip             |    |  |

|            | protection1                                                                    | 14 |  |

| Fig. 1.1  | The four pin-combination modes for ESD test on an IC product: (a)                                 |   |

|-----------|---------------------------------------------------------------------------------------------------|---|

|           | positive-to-VSS (PS-mode), (b) negative-to-VSS (NS-mode), (c) positive-to-VDI                     | ) |

|           | (PD mode), and (d) negative-to-VDD (ND-mode)                                                      | 6 |

| Fig. 1.2  | Typical on-chip ESD protection circuits in a CMOS IC.                                             | 6 |

| Fig. 1.3  | The ESD current paths of the I/O pad with power-rail ESD clamp circuit under                      |   |

|           | positive-to-VSS (PS-mode) ESD stress. The ESD current paths are indicated by                      |   |

|           | the dashed lines                                                                                  | 7 |

| Fig. 2.1  | Block diagram of 90-nm 1.0-V/2.5-V configurable I/O cell                                          | 6 |

| Fig. 2.2  | Illustration of pull low driving current (I <sub>OL</sub> ) with (a) terminal condition and (b)   |   |

|           | I-V curve of output NMOS                                                                          | 6 |

| Fig. 2.3  | Illustration of Pull high driving current (I <sub>OH</sub> ) with (a) terminal condition, (b) I-V |   |

|           | curve of output PMOS and (c) corresponding V <sub>OH</sub> in different VDDIO voltage             |   |

|           | supply3                                                                                           | 7 |

| Fig. 2.4  | Simulated result of single-finger output NMOS                                                     | 7 |

| Fig. 2.5  | The first method for designing single-finger output PMOS MP03                                     | 8 |

| Fig. 2.6  | Simulated results for single-finger output PMOS MP0 with the channel width of                     |   |

|           | 45.4□ m3                                                                                          | 8 |

| Fig. 2.7  | The second method for designing single-finger output PMOS                                         | 8 |

| Fig. 2.8  | Relation between PMOS Size and Duty Cycle                                                         | 9 |

| Fig. 2.9  | Simulated waveform for determining size of single-finger output PMOS MP03                         | 9 |

| Fig. 2.10 | The inverter with short-circuit reduction for (a) output NMOS and (b) output                      |   |

|           | PMOS4                                                                                             | 0 |

| Fig. 2.11 | Simulation setup of short-circuit current reduction4                                              | 0 |

| Fig. 2.12 | Simulation results of short-circuit current reduction with the pseudo worst                       |   |

|           | simulation case (85°C, TT corner), $V_{in} = 0 \sim VDDIO$ , $T_r = T_f = 0.1$ ns, Frequency      | = |

|           | 266MHz, and $C_{load} = 12pF$ , (a) 1.8-V VDDIO, (b) 2.5-V VDDIO, and (c) 3.3-V                   |   |

|           | VDDIO4                                                                                            | 1 |

| Fig. 2.13 | Logic diagram of pre-driver4                                                                      | 2 |

| Fig. 2.14 | Circuit implementation of pre-driver4                                                             | 2 |

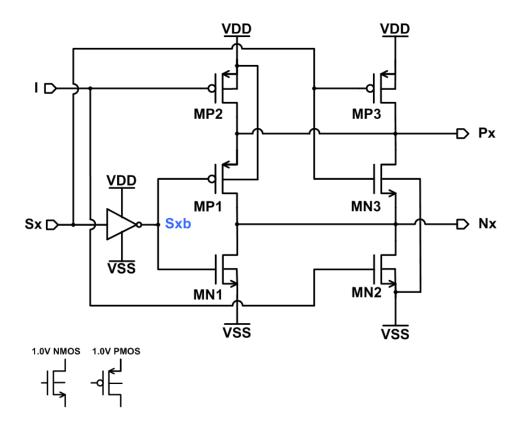

| Fig. 2.15 | Simulation waveforms of pre-driver with the pseudo worst case (85°C, TT corner)                   |   |

|           | $C_{load} = 0.9 fF$ , (a) 266-MHz input signal $V_I$ , 133-MHz input signal $V_{Sx}$ , (b)        |   |

|           | 133-MHz input signal $V_{\rm I}$ , 266-MHz input signal $V_{\rm Sx}$ , and (c) 266-MHz input      |   |

|           | signals $V_I$ and $V_{Sx}$                                                                        | 3 |

| Fig. 2.16 | Circuit diagram of level shifter                                                                  | 4 |

| Fig. 2.17 | 17 Simulation waveforms of level shifter circuit with the pseudo worst case (85°C,                |   |

|           | TT), 1.0-V VDD, 2.5-V VDDIO, and C <sub>load</sub> = 20fF4                                        | 4 |

| Fig. 2.18 | 18 Simulation waveforms of level shifter circuit operating in different VDDIO                      |  |

|-----------|----------------------------------------------------------------------------------------------------|--|

|           | voltage supply with the pseudo worst case (85°C/TT), 1.0-V VDD, and $C_{load}$ =                   |  |

|           | 20fF                                                                                               |  |

| Fig. 2.19 | Circuit diagram of schmitt-trigger with an enable signal (SCH)45                                   |  |

| Fig. 2.20 | Circuit diagram of input stage                                                                     |  |

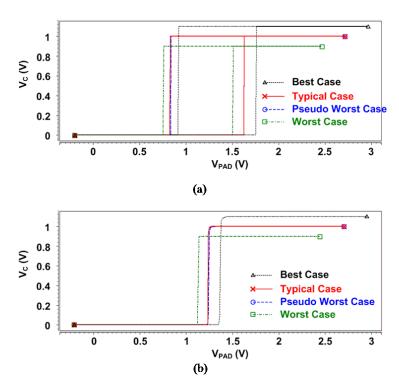

| Fig. 2.21 | Voltage transform curve (VTC) of input stage with (a) $SCH = 1$ and (b) $SCH = 0$ .                |  |

|           | 46                                                                                                 |  |

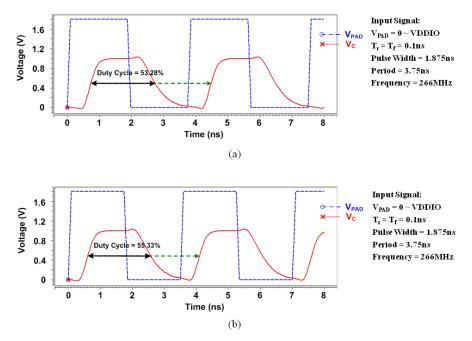

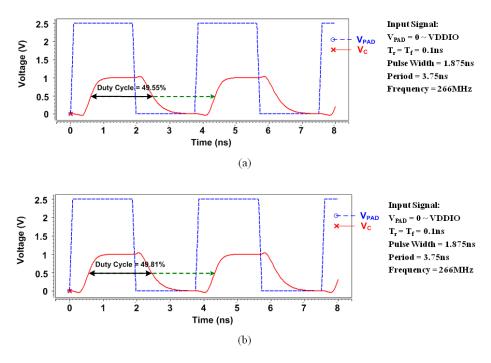

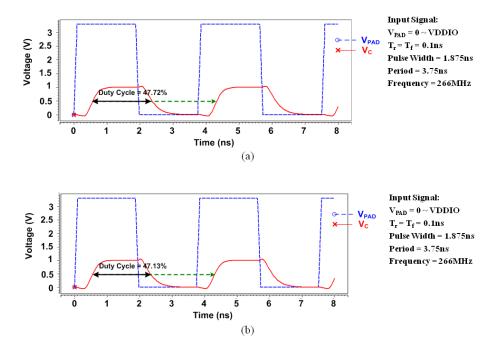

| Fig. 2.22 | Simulation waveforms of (a) schmitt-trigger input stage (SCH = 1) and (b) normal                   |  |

|           | input stage (SCH = 0) with the pseudo worst case, $C_{load} = 0.1 pF$ , 1.0-V VDD, and             |  |

|           | 1.8-V VDDIO                                                                                        |  |

| Fig. 2.23 | Simulation waveforms of (a) schmitt-trigger input stage (SCH = 1) and (b) normal                   |  |

|           | input stage (SCH = $0$ ) with the pseudo worst case ( $85^{\circ}$ C/TT), Cload = $0.1$ pF,        |  |

|           | 1.0-V VDD, and 2.5-V VDDIO                                                                         |  |

| Fig. 2.24 | Simulation waveforms of (a) schmitt-trigger input stage (SCH = 1) and (b) normal                   |  |

|           | input stage (SCH = 0) with the pseudo worst case (85 $^{\circ}$ C/TT), $C_{load} = 0.1 pF$ , 1.0-V |  |

|           | VDD, and 3.3-V VDDIO.                                                                              |  |

| Fig. 2.25 | Circuit implementation of pull-up and pull-down network                                            |  |

| Fig. 2.26 | Determination of pull-up MOS (MP1) size; (a) simulated method, and (b)                             |  |

|           | simulated result                                                                                   |  |

| Fig. 2.27 | Determination of pull-down MOS (MN1) size; (a) simulated method, and (b)                           |  |

|           | simulated result50                                                                                 |  |

| Fig. 2.28 | Simulation setup of equivalent (a) pull-up resistance and (b) pull-down resistance                 |  |

|           | in pull-up/pull-down network51                                                                     |  |

| Fig. 2.29 | The model for ground bounce effect                                                                 |  |

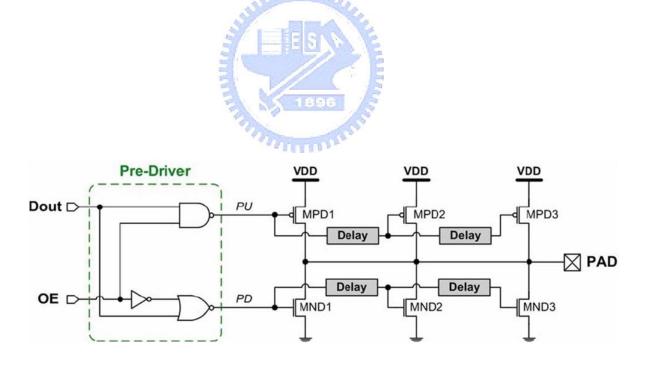

| Fig. 2.30 | Output buffer with slew-rate control                                                               |  |

| Fig. 2.31 | Design for output driver of configurable I/O cell with slew-rate control53                         |  |

| Fig. 2.32 | Gate-controlled signals of (a) output NMOS and (b) output PMOS with slew-rate                      |  |

|           | control under the pseudo worst case (85°C/TT),1.0-V VDD, 2.5-V VDDIO, and                          |  |

|           | $C_{load} = 12pF.$                                                                                 |  |

| Fig. 2.33 | Switching current on (a) VDDIO power line and (b) VSSIO ground line55                              |  |

| Fig. 2.34 | Output waveforms of configurable I/O cell with the pseudo worst case (85°C/TT),                    |  |

|           | 1.0-V VDD, C <sub>load</sub> = 12pF, (a) 1.8-V VDDIO, (b) 2.5-V VDDIO, and (c) 3.3-V               |  |

|           | VDDIO56                                                                                            |  |

| Fig. 3.1  | Typical on-chip ESD protection circuits in a CMOS IC62                                             |  |

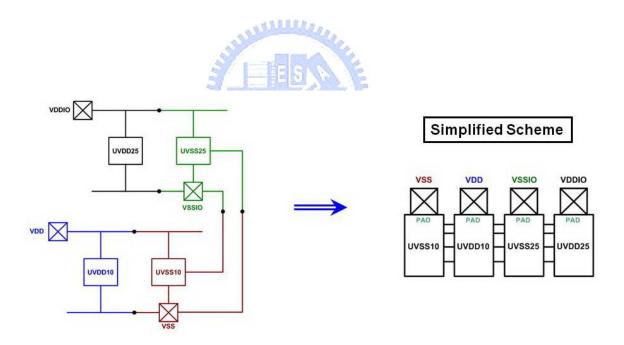

| Fig. 3.2  | Whole-chip ESD protection scheme62                                                                 |  |

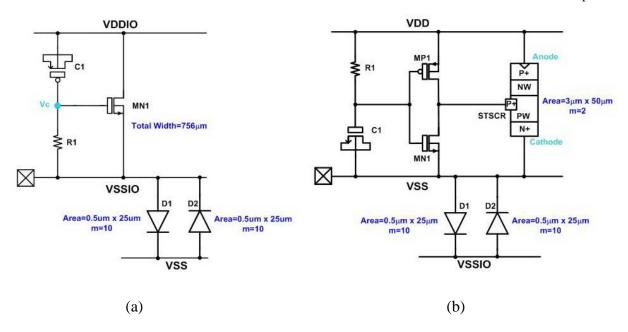

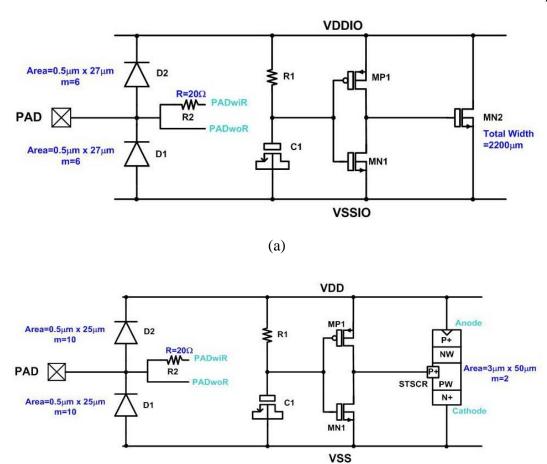

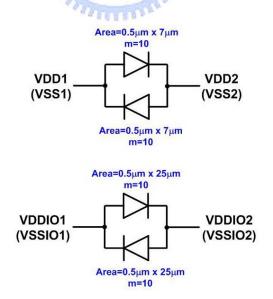

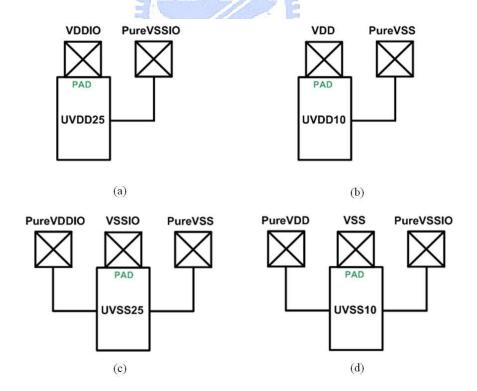

| Fig. 3.3  | Circuit diagram of (a) UVDD25, (b) UVDD10 cells63                                                  |  |

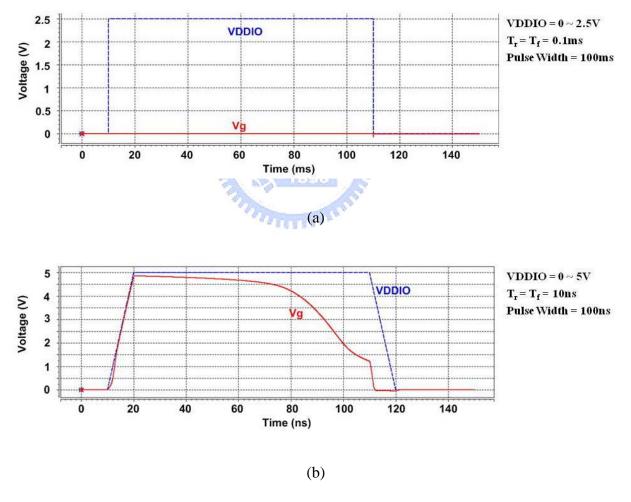

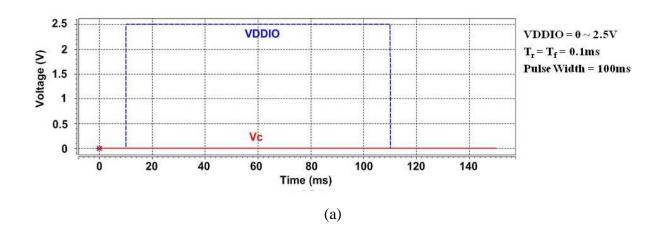

| Fig. 3.4  | Simulated results of UVDD25 and UVSS25 cells under (a) power-on condition                          |  |

| Č         | and (b) ESD stress condition.                                                                      |  |

| Fig 35    | • •                                                                                                |  |

| Fig. 3.6  | Simulated results of UVSS25 cell under (a) power-on condition and (b) ESD           |

|-----------|-------------------------------------------------------------------------------------|

|           | stress condition. 64                                                                |

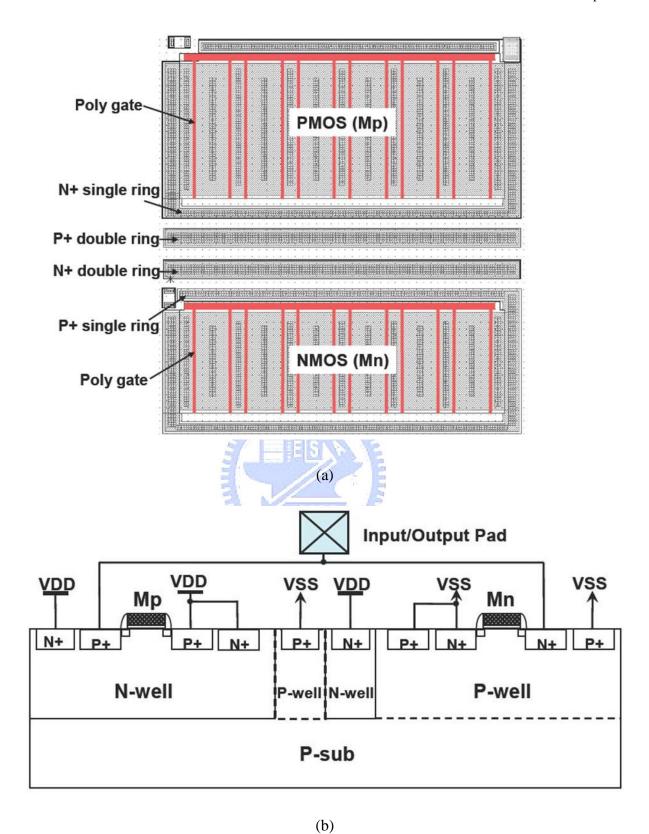

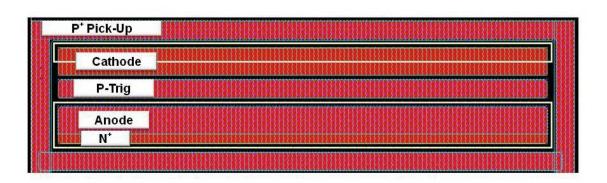

| Fig. 3.7  | (a) Layout view and (b) device structures of the I/O cell with double guard rings   |

|           | inserted between input (or output) PMOS and NMOS devices                            |

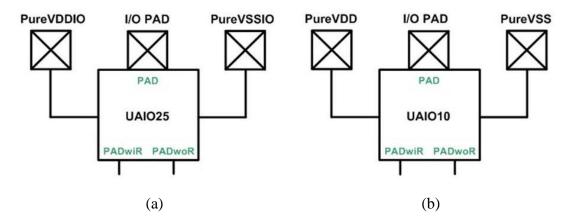

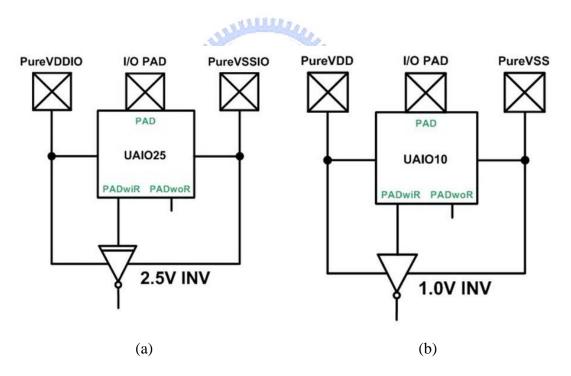

| Fig. 3.8  | Circuit diagram of (a) UAIO25 and (b) UAIO10 cells66                                |

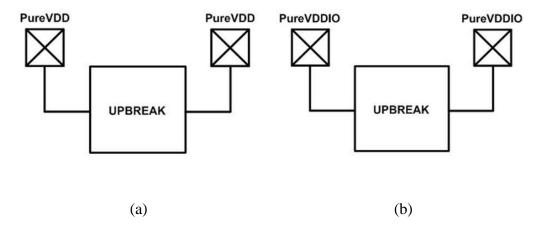

| Fig. 3.9  | Circuit diagram of power break cell                                                 |

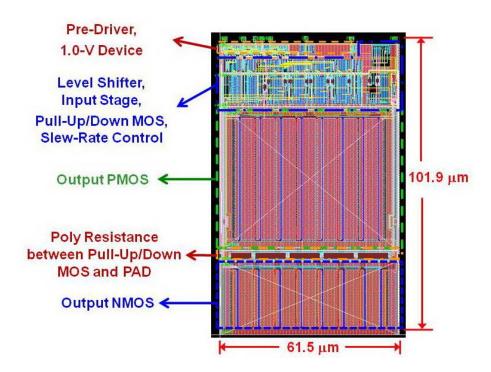

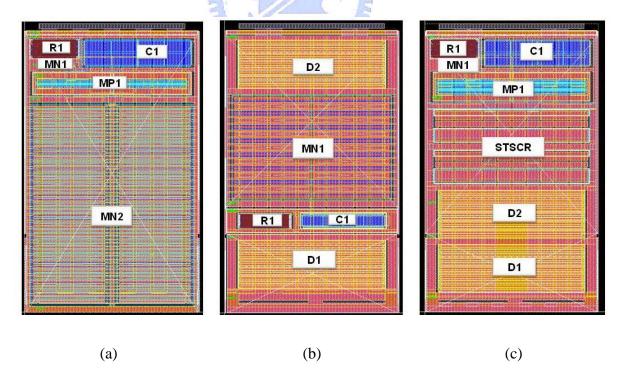

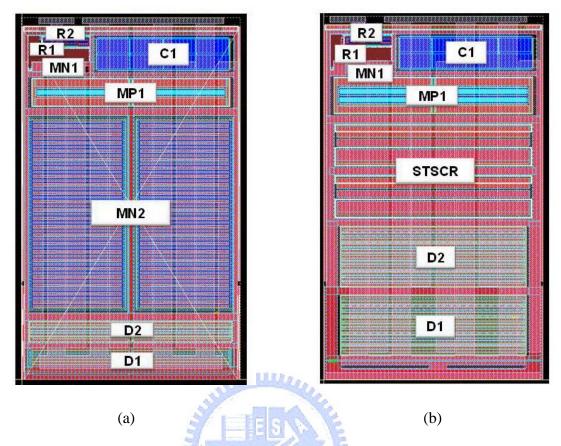

| Fig. 4.1  | (a) Layout implementations of configurable I/O with slew-rate control cell          |

|           | (UCIOS) and power line. (a) Configurable I/O cell, (b) power line and (c)           |

|           | complete layout implementation71                                                    |

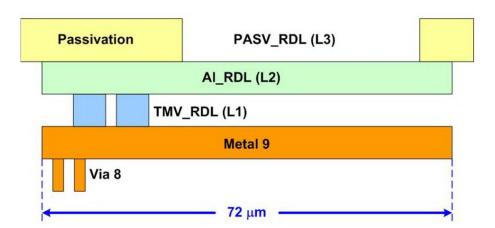

| Fig. 4.2  | Cross section view of bond pad                                                      |

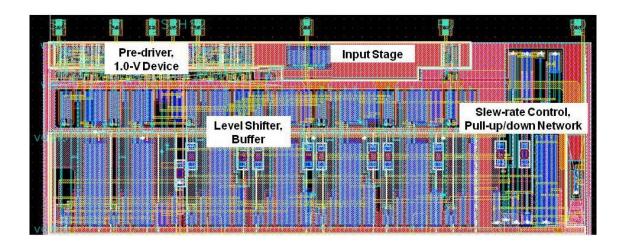

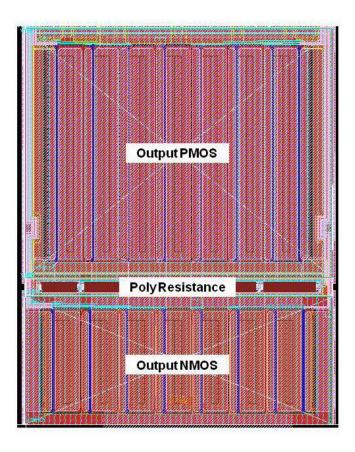

| Fig. 4.3  | Block layout views of configurable I/O with slew-rate control cell (UCIOS). (a)     |

|           | Pre-driver, level shifter, input stage, pull-up/pull-down network and slew-rate     |

|           | control; (b) Output driver and poly resistance between pull-up/pull-down MOS        |

|           | and I/O PAD72                                                                       |

| Fig. 4.4  | Slew-rate control circuit layout of configurable I/O without slew-rate control cell |

|           | (UCIONS)                                                                            |

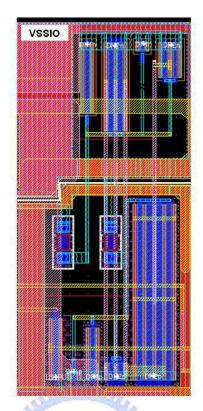

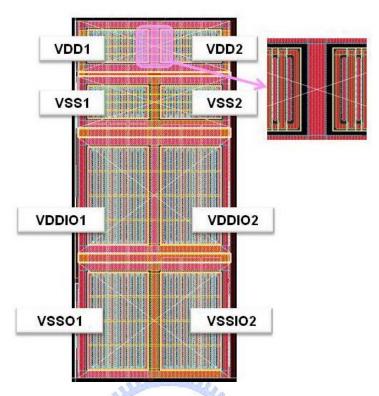

| Fig. 4.5  | Layout-top-view of (a) UVDD25, (b) UVSS25, and (c) UVSS10 cells73                   |

| Fig. 4.6  | Layout-top-view of (a) UAIO25 and (c) UAIO10 cells74                                |

| Fig. 4.7  | Layout-top-view of STSCR drawn in UVDD10 and UAIO10 cells74                         |

| Fig. 4.8  | Layout-top-view of UPBREAK cell75                                                   |

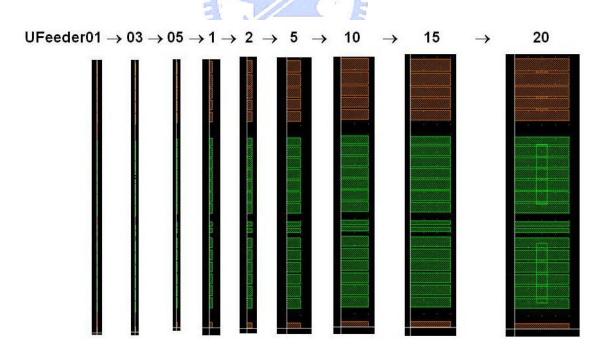

| Fig. 4.9  | Layout-top-view of UFeeder01, UFeeder03, UFeeder05, UFeeder1, UFeeder2,             |

|           | UFeeder5, UFeeder10, UFeeder15, and UFeeder20 cells                                 |

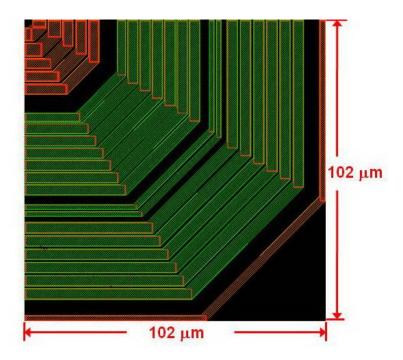

| Fig. 4.10 | Layout-top-view of corner cell (UCorner)                                            |

| Fig. 5.1  | Test circuit for measuring pull-up/pull-down resistance and Schmitt-trigger         |

|           | threshold points                                                                    |

| Fig. 5.2  | The implementation of the input cell by making from configurable I/O with           |

|           | slew-rate control cell                                                              |

| Fig. 5.3  | Simulated results of (a) pull-up and (b) pull-down resistance                       |

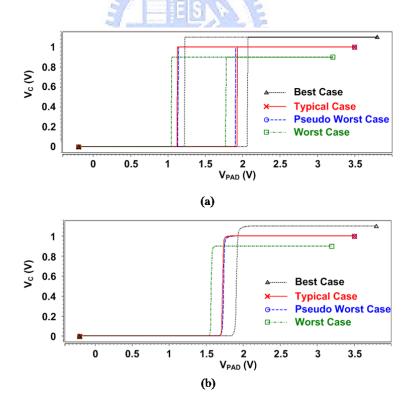

| Fig. 5.4  | Voltage-transfer curve of configurable I/O with (a) SCHa receiving a 1.8-V          |

|           | voltage and (b) SCHa receiving a 0-V voltage in 1.8-V VDDIO supply voltage. 89      |

| Fig. 5.5  | Voltage-transfer curve of configurable I/O with (a) SCHa receiving a 2.5-V          |

|           | voltage and (b) SCHa receiving a 0-V voltage in 2.5-V VDDIO supply voltage. 90      |

| Fig. 5.6  | Voltage-transfer curve of configurable I/O with (a) SCHa receiving a 3.3-V          |

|           | voltage and (b) SCHa receiving a 0-V voltage in 3.3-V VDDIO supply voltage. 90      |

| Fig. 5.7  | Test circuit of configurable I/O driving capability91                               |

| Fig. 5.8  | Method for measuring SSN (simultaneous switching noise) of UCIOS and                |

|           | UCIONS91                                                                            |

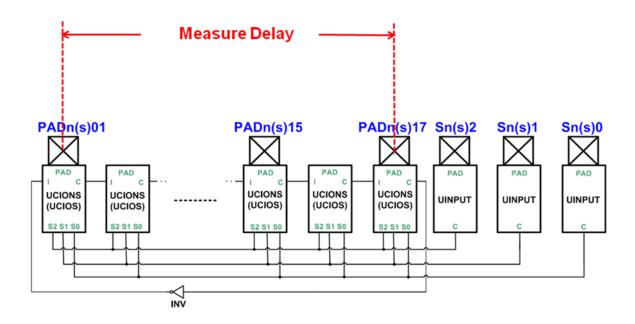

| Fig. 5.9  | Test circuit for measuring SSN and propagation delay of configurable I/O cells. 92  |

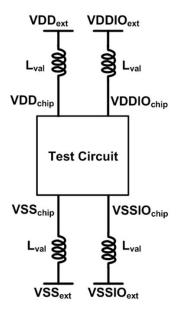

| Fig. 5.10 | Simulated model of ground bounce. 92                                                |

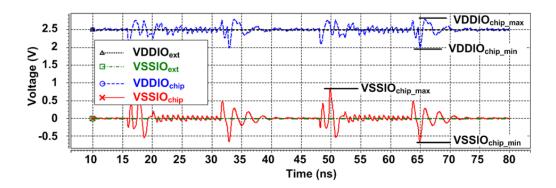

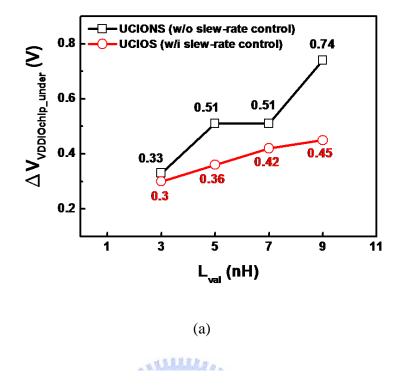

| Fig. 5.11 | Simulation waveforms of ground bounce effects on power lines93                                         |

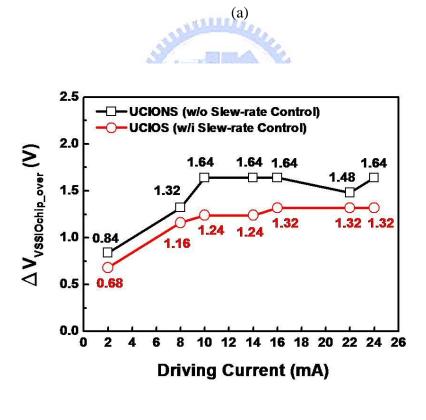

|-----------|--------------------------------------------------------------------------------------------------------|

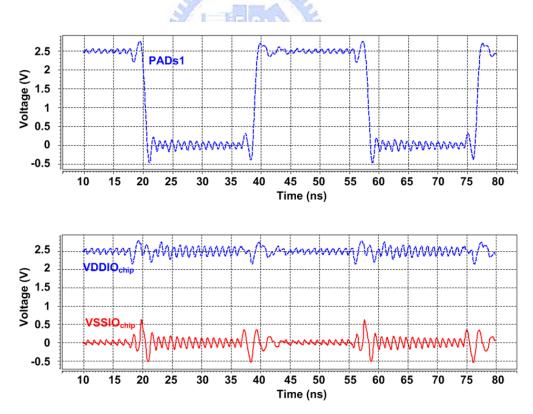

| Fig. 5.12 | Simulation waveforms of the UCIOS (configurable I/O cell with slew-rate control)                       |

|           | with ground bounce effect in transmitting mode93                                                       |

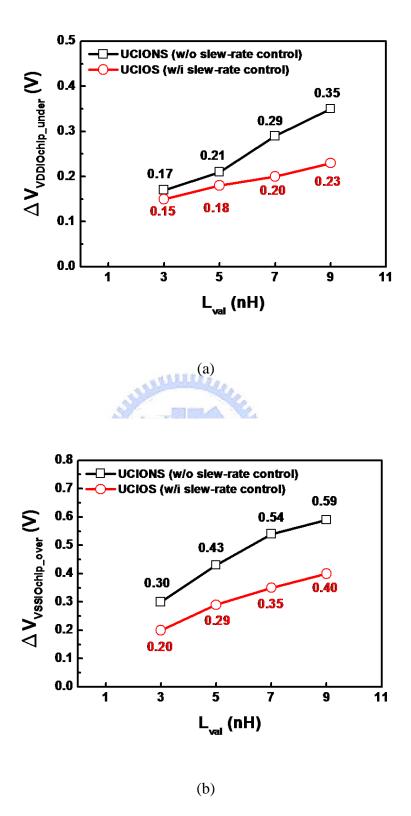

| Fig. 5.13 | The relation between ground bounce on VDDIO <sub>chip</sub> /VSSIO <sub>chip</sub> power line and wire |

|           | bond inductance on the UCIONS and UCIOS with 1.8-V VDDIO <sub>ext</sub> voltage                        |

|           | supply. (a) The undershoot on VDDIO <sub>chip</sub> power line and (b) the overshoot on                |

|           | VSSIO <sub>chip</sub> power line94                                                                     |

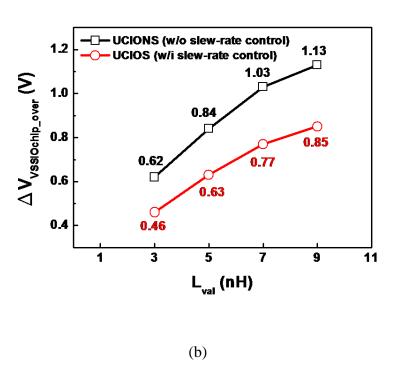

| Fig. 5.14 | The relation between ground bounce on VDDIO <sub>chip</sub> /VSSIO <sub>chip</sub> power line and wire |

|           | bond inductance on the UCIONS and UCIOS with 2.5-V VDDIO <sub>ext</sub> voltage                        |

|           | supply. (a) The undershoot on VDDIO <sub>chip</sub> power line and (b) the overshoot on                |

|           | VSSIO <sub>chip</sub> power line95                                                                     |

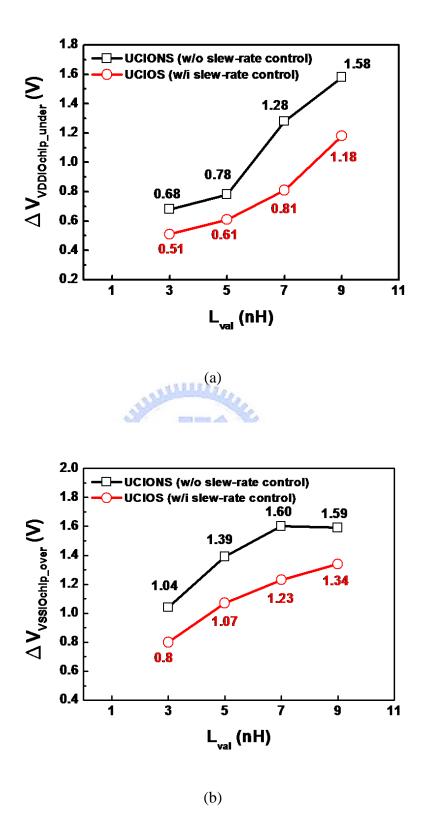

| Fig. 5.15 | The relation between ground bounce on VDDIO <sub>chip</sub> /VSSIO <sub>chip</sub> power line and wire |

|           | bond inductance on the UCIONS and UCIOS with 3.3-V VDDIO <sub>ext</sub> voltage                        |

|           | supply. (a) The undershoot on VDDIO <sub>chip</sub> power line and (b) the overshoot on                |

|           | VSSIO <sub>chip</sub> power line96                                                                     |

| Fig. 5.16 | Simulation waveforms for propagation delay of I/O cell with operating in                               |

|           | transmitting mode                                                                                      |

| Fig. 5.17 | Testkeys of power/ground cells, (a) UVDD25, (b) UVDD10, (c) UVSS25, and (d)                            |

|           | UVSS1097                                                                                               |

| Fig. 5.18 | Testkeys of analog I/O cells, (a) UAIO25 and (b) UAIO1098                                              |

| Fig. 5.19 | Testkeys of analog I/O cells, (a) UAIO25 and (b) UAIO10 with inverter stage98                          |

| Fig. 5.20 | Testkeys of power break cell for (a) 1.0-V power domain and (b) 2.5-V power                            |

|           | domain. 99                                                                                             |

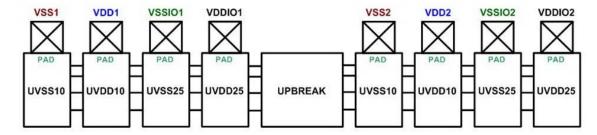

| Fig. 5.21 | Simplified scheme of whole-chip protection circuit99                                                   |

| Fig. 5.22 | Whole-chip protection scheme with power break cell                                                     |

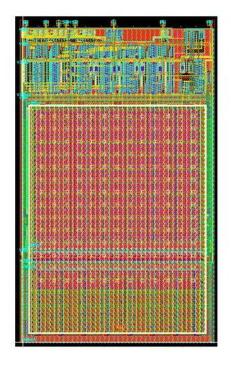

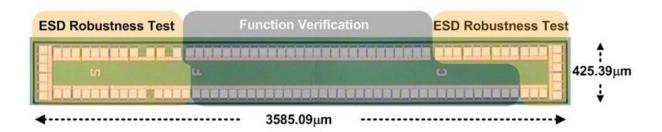

| Fig. 5.23 | Layout-top-view of test chip in UMC 90-nm CMOS process                                                 |

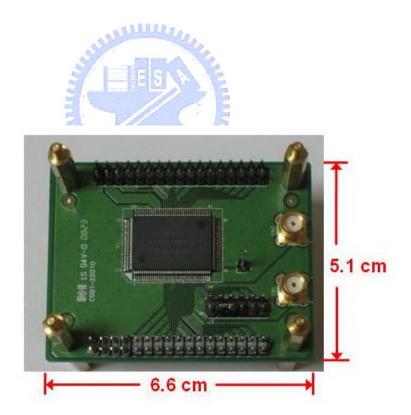

| Fig. 6.1  | The test chip photograph of the configurable I/O cell library in UMC 90-nm                             |

|           | CMOS process. 115                                                                                      |

| Fig. 6.2  | The PCB view of tested chip                                                                            |

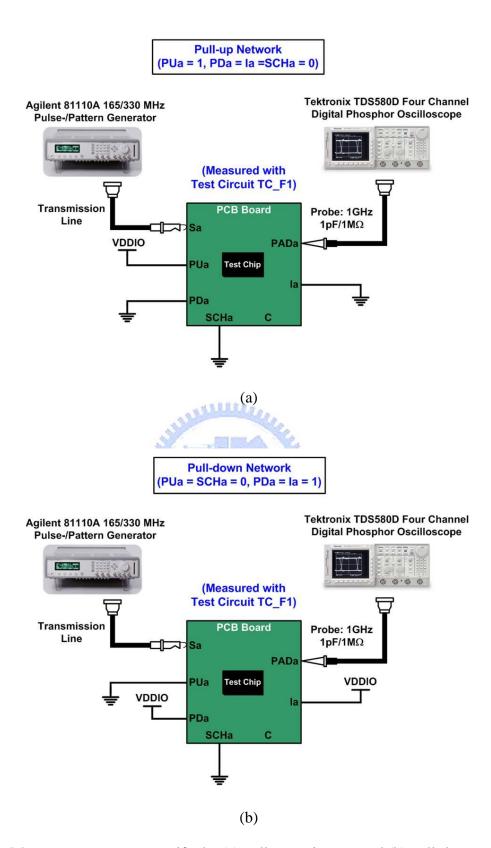

| Fig. 6.3  | Measurement setup to verify the (a) pull-up resistance and (b) pull-down                               |

|           | resistance. 116                                                                                        |

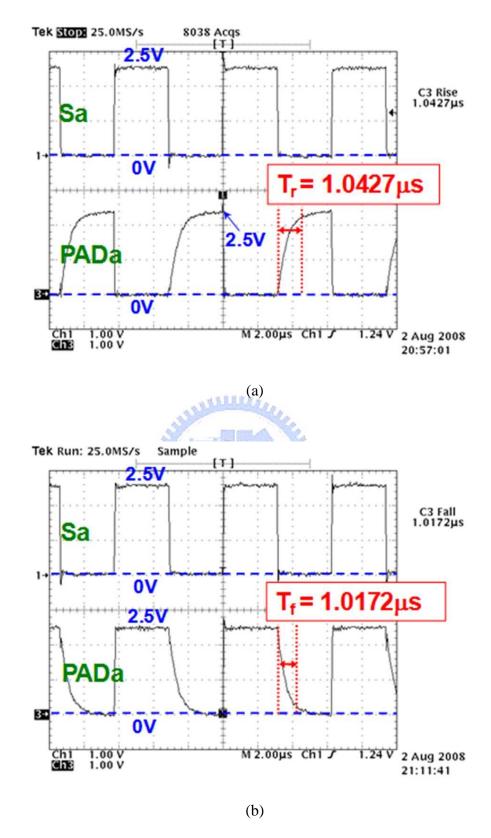

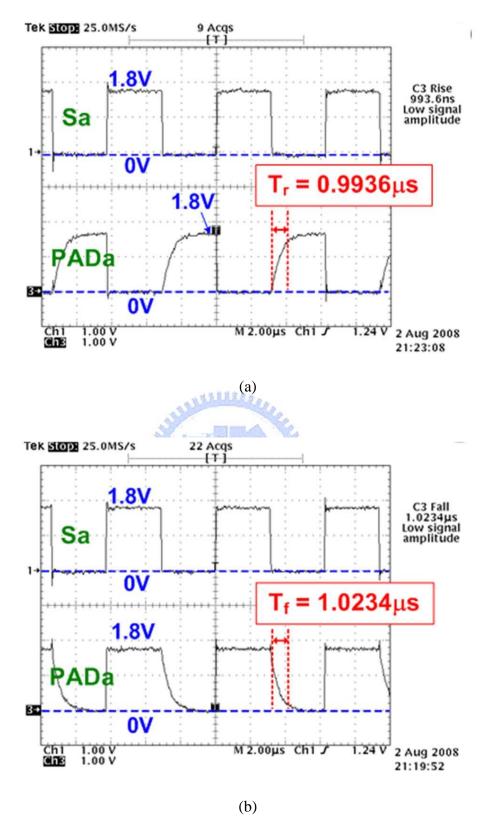

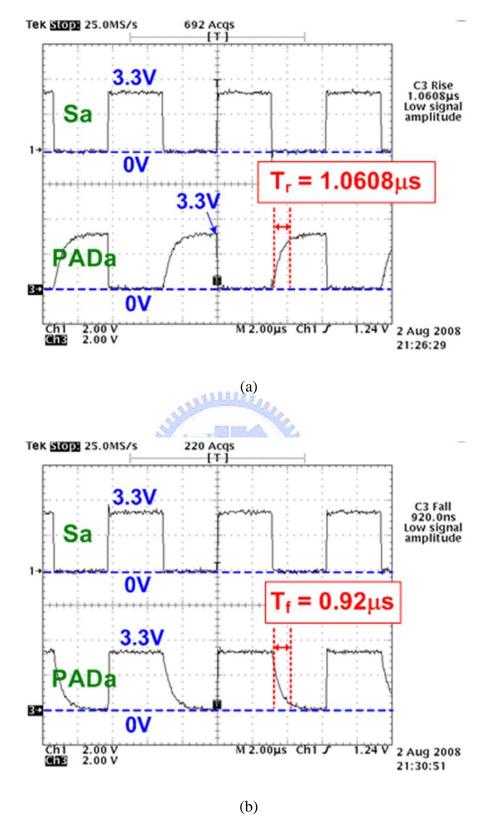

| Fig. 6.4  | Measured waveforms of the (a) pull-up network and (b) pull-down network with                           |

|           | 2.5-V VDDIO voltage supply                                                                             |

| Fig. 6.5  | Measured waveforms of the (a) pull-up network and (b) pull-down network with                           |

|           | 1.8-V VDDIO voltage supply                                                                             |

| Fig. 6.6  | Measured waveforms of the (a) pull-up network and (b) pull-down network with                           |

|           | 3.3-V VDDIO voltage supply                                                                             |

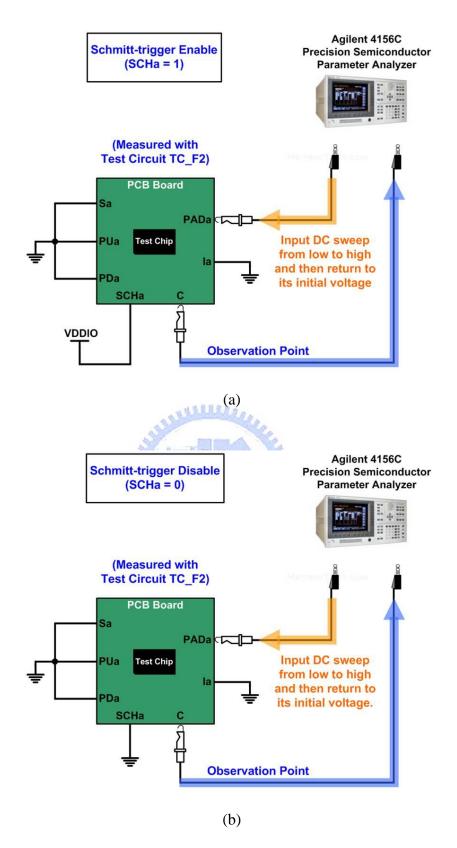

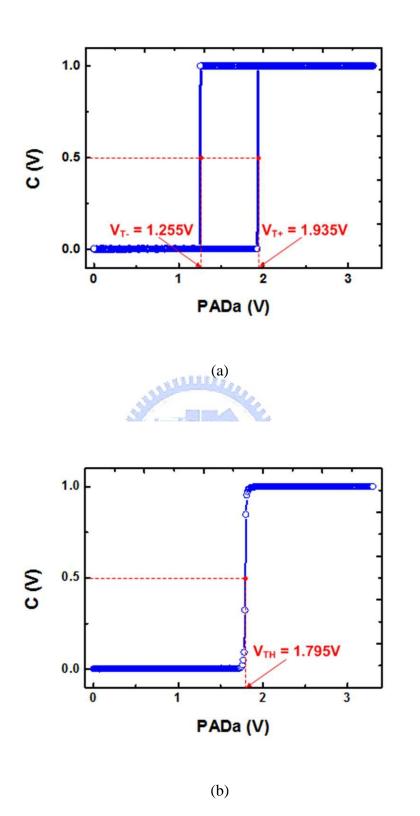

| Fig. 6.7  | Measurement setup to verify input stage threshold points with (a) schmitt-trigger                      |

|           | enable (SCHa = 1) and (b) schmitt-trigger disable (SCHa =0)                                            |

| Fig. 6.8  | Measured result of input stage with (a) schmitt-trigger enable (SCHa = 1) and (b)              |

|-----------|------------------------------------------------------------------------------------------------|

|           | schmitt-trigger disable (SCHa =0) under 2.5-V VDDIO121                                         |

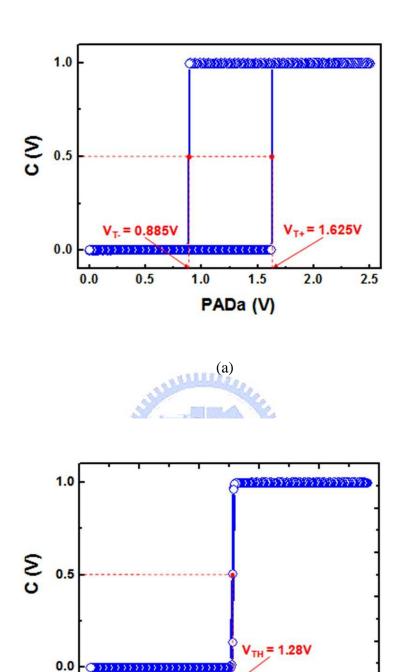

| Fig. 6.9  | Measured result of input stage with (a) schmitt-trigger enable (SCHa = 1) and (b)              |

|           | schmitt-trigger disable (SCHa =0) under 1.8-V VDDIO122                                         |

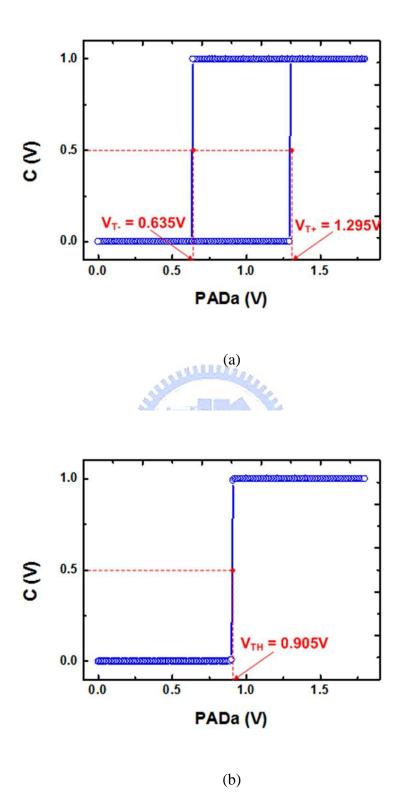

| Fig. 6.10 | Measured result of input stage with (a) schmitt-trigger enable (SCHa = 1) and (b)              |

|           | schmitt-trigger disable (SCHa =0) under 3.3-V VDDIO123                                         |

| Fig. 6.11 | Measurement setup to verify (a) low level output current (I <sub>OL</sub> ) and (b) high level |

|           | output current (I <sub>OH</sub> )124                                                           |

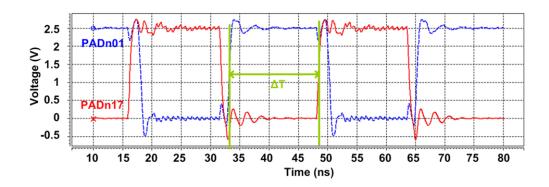

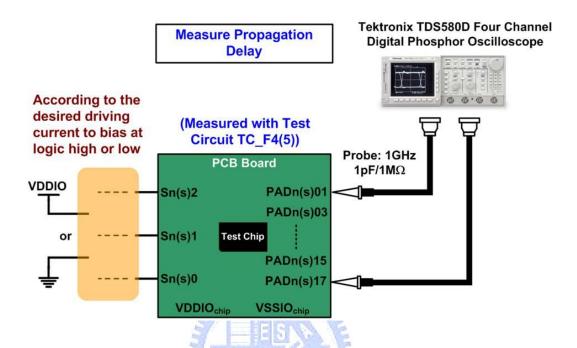

| Fig. 6.12 | Measurement setup to verify simultaneous switching noise (SSN)                                 |

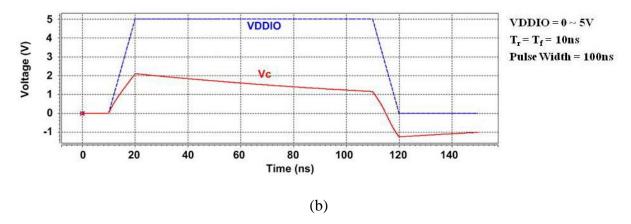

| Fig. 6.13 | Measured waveforms of simultaneous switching noise (SSN) issue when the                        |

|           | configurable I/O cell operating (a) without slew-rate control (UCIONS) and (b)                 |

|           | with slew-rate control (UCIOS)                                                                 |

| Fig. 6.14 | The relation between ground bounce on the power/ground line and driving current                |

|           | with the UCIONS and UCIOS. (a) The undershoot on VDDIO <sub>chip</sub> power line and          |

|           | (b) the overshoot on VSSIO <sub>chip</sub> ground line                                         |

| Fig. 6.15 | Measurement setup to test the propagation delay of the UCIONS (UCIOS) cell                     |

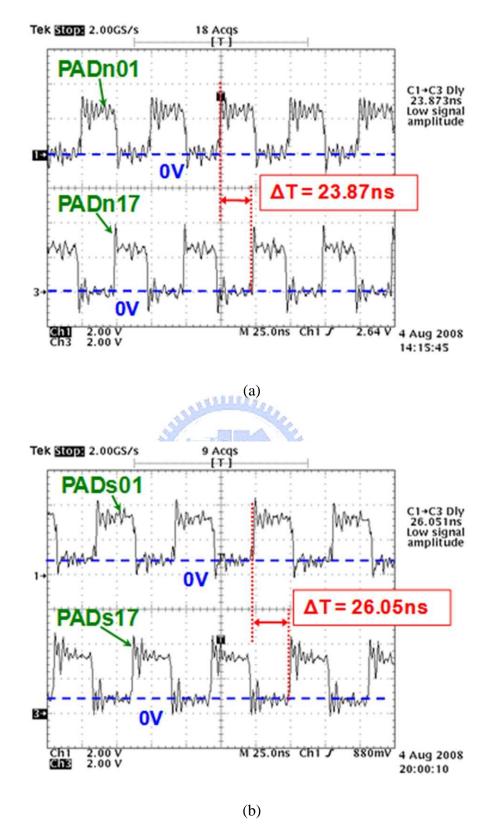

|           |                                                                                                |

| Fig. 6.16 | Measured waveforms to test the propagation delay when the configurable I/O cell                |

|           | operating (a) without slew-rate control (UCIONS) and (b) with slew-rate control                |

|           | (UCIOS) under 2.5-V VDDIO supply voltage                                                       |

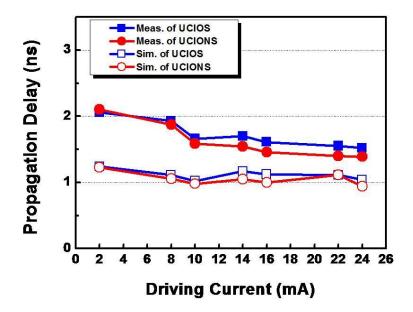

| Fig. 6.17 | Propagation delay comparison between measurement and simulation results of the                 |

|           | propagation delay with 2.5-V VDDIO and different driving current130                            |

| Fig. 6.18 | Propagation delay comparison between measurement and simulation results in                     |

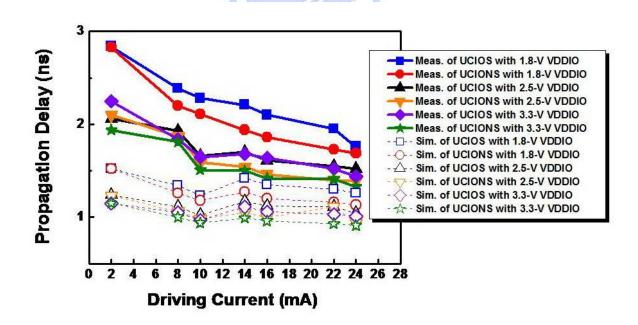

|           | different driving current and VDDIO supply voltage                                             |

| Fig. 6.19 | Measurement setup to test the maximum operating frequency at the output stage                  |

|           | of the configurable I/O131                                                                     |

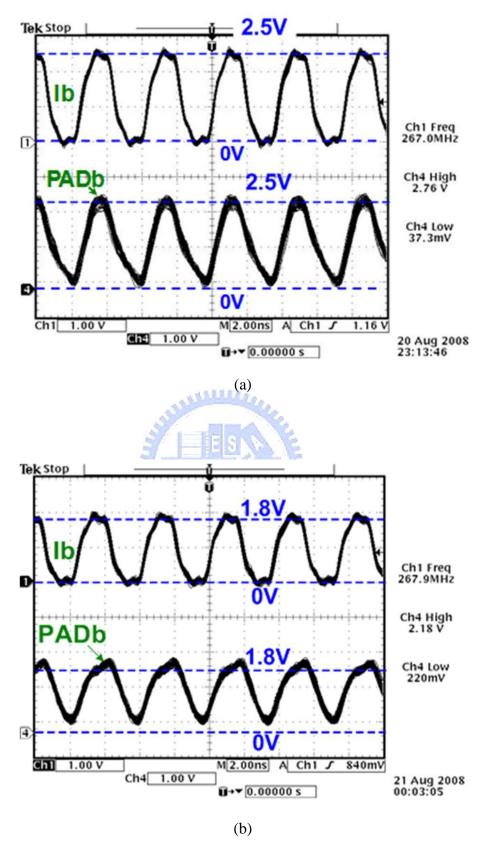

| Fig. 6.20 | Measured waveforms of the configurable I/O cell operating at 266M-Hz operating                 |

|           | frequency and 24-mA driving current when receiving 0V-to-VDDIO input signals                   |

|           | at pin Ib with (a) 2.5-V, (b) 1.8-V, and (c) 3.3-V VDDIO supply voltage133                     |

| Fig. 6.21 | Testkey of configurable I/O cell with whole-chip protection circuit133                         |

| Fig. 6.22 | Protective extend test of whole-chip protection circuit                                        |

# **Chapter 1**

## Introduction

#### 1.1 MOTIVATION

In the digital integrated circuits (ICs) or mixed-signal ICs designs of the system-on-a-chip (SoC) and VLSI system, the cell libraries are often used to accelerate the design process to achieve the time-to-market requirement. The I/O (input/output) cell is an essential element in the IC products, which can provide enough output driving currents or receive the external signals. In the meanwhile, the I/O cell also can provide a sufficient electrostatic discharge (ESD) protection to protect the internal circuits and I/O circuits inside the ICs.

#### 1.1.1 Issue of I/O Interface

With new generations of CMOS technologies, the dimensions of transistors have been scaled down to reduce the silicon cost, and to increase circuit performance (ex., operating speed). However, since the thickness of gate-oxide becomes much thinner, several problems such as gate-oxide reliability [1] and hot-carrier degradation [2] will be faced. Thus, the core power supply voltage (VDD) must be correspondingly decreased to ensure the ICs lifetime. Since the power supply voltage has been reduced, it will decrease lower power consumption to achieve the purpose of low power. In order to increase the circuit performance and decrease the power consumption, generally the internal or core circuit is designed with thin-oxide

devices and lower power supply. But the I/O cell may receive or transmit a higher voltage level signal at the I/O interface. Therefore, in this thesis, the thick-oxide devices have been used to prevent the reliability issue. When such I/O cell receives a high voltage level signal, the signal will be transformed into a low voltage level signal and then it will be transmitted to the internal circuit. As a result, there is no need to concern the reliability issues while the internal circuit will be designed with the thin-oxide devices and operated with low voltage supply.

In high-speed interface, the output buffer is a major contributor to the pin-to-pin delays because of output loading as well as package and aboard parasitic. The channel widths of output buffer are always increased to achieve high driving capability and high speed, which results in large power/ground noise due to output drivers switching simultaneously. Since the input pads are connected to the same power/ground buses, power/ground noise must be well controlled to avoid any false switching. Even though the internal power/ground buses are separated from the external (I/O buffers) power/ground buses, they are connected through a VDD/VSS package plane in multilayer package. Therefore, the output buffer must be designed with considerations of power/ground noise to achieve high performance.

In this thesis, two configurable I/O cells are designed to provide different driving capacities, turn on/off the pull-up or pull-down mechanism, and switch on/off the function of schmitt-trigger when the I/O circuit operates in transmitting mode, tri-state, and receiving mode, respectively. Instead of providing different cells as general I/O cells, the configurable I/O cells combine most functions to meet different specification requirement. Beside, the difference between these two configurable I/O cells is the output buffer without or with slew-rate control mechanism. The configurable I/O cell with slew-rate control is designed with considerations of power/ground noise.

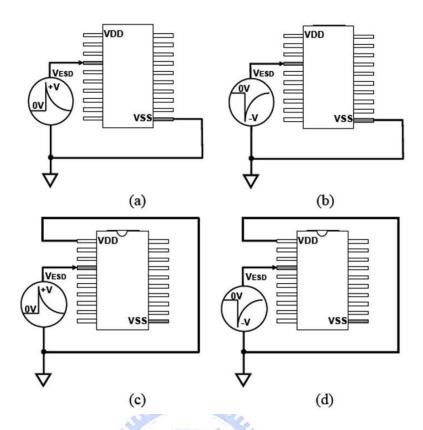

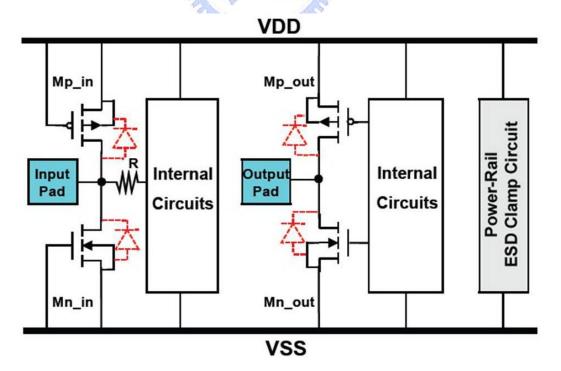

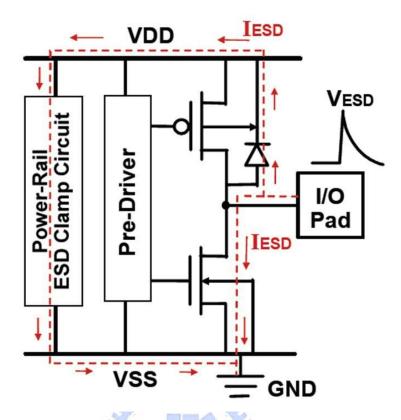

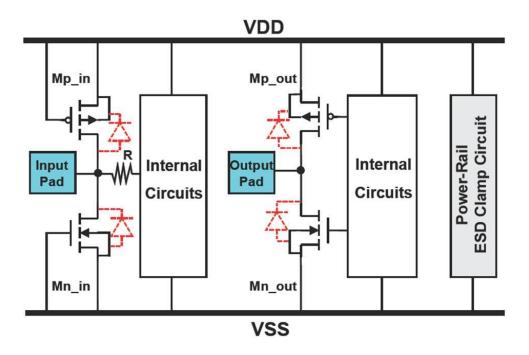

#### 1.1.2 Issue of ESD

ESD has become the main reliability concern on semiconductor products, especially for the SoC implementation in nanoscale CMOS processes. The ESD specifications of commercial IC products are generally required to be higher than 2kV in human-body-model (HBM) and 200V in machine-model (MM) [3] ESD stress. Therefore, on-chip ESD protection circuits have to be added between the input/output pad and VDD/VSS to provide the desired ESD robustness in CMOS ICs [4]-[6]. ESD stresses on an I/O pad have four pin-combination modes: positive-to-VSS (PS-mode), negative-to-VSS (NS-mode), positive-to-VDD (PD-mode), and negative-to-VDD (ND-mode), as shown in Fig. 1.1(a) ~ 1.1(d), respectively. The typical design of on-chip ESD protection circuits in a CMOS IC is illustrated in Fig. 1.2. To avoid the unexpected ESD damage in the internal circuits of CMOS ICs [7]-[9], the turn-on-efficient power-rail ESD clamp circuit is placed between VDD and VSS power lines [10]. ESD current at the I/O pad under the PS-mode ESD stress can be discharged through the parasitic diode of PMOS from I/O pad to VDD, and then through the VDD-to-VSS ESD clamp circuit to ground as shown in Fig. 1.3. Consequently, the I/O circuits cooperating with the VDD-to-VSS ESD clamp circuit can achieve a much higher ESD level [10].

In this thesis, a new set I/O cell library is proposed to assist the digital or mixed-signal IC design with effective ESD protection circuits to enhance the ESD level in SoC implementations. The configurable I/O cell library has been fabricated and verified in UMC 90-nm salicide CMOS process.

#### 1.2 Introdution of Configurable I/O Cell Library

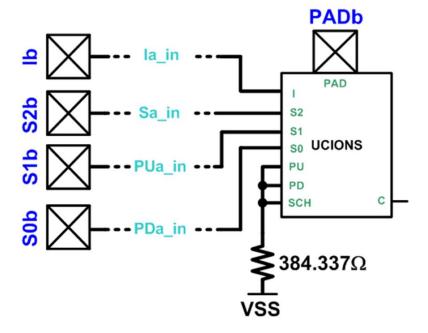

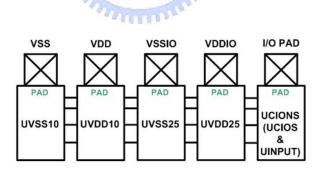

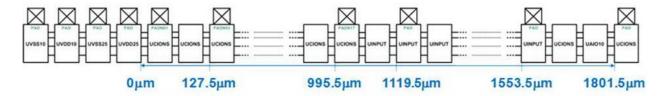

Table 1.1 lists the cell categories and functions of the configurable I/O cell library. This

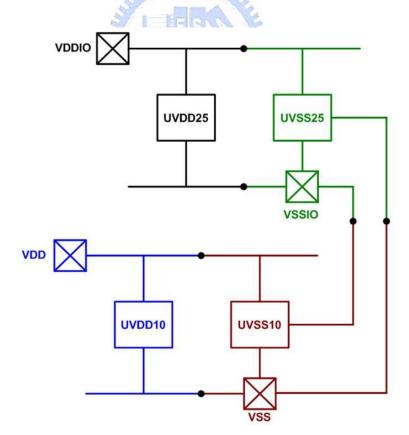

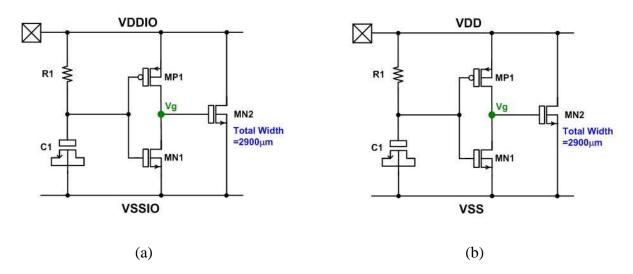

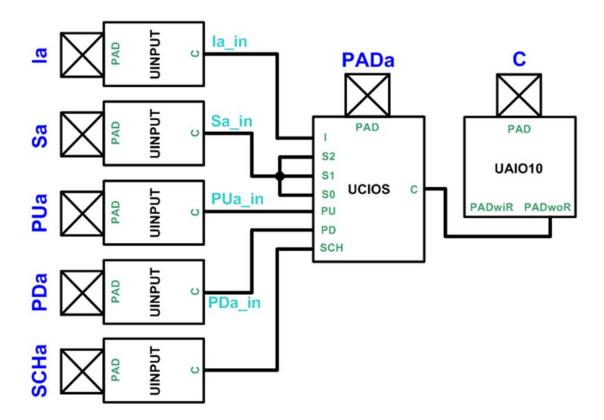

I/O cell provides two configurable I/O cells named UCIONS (without slew-rate control mechanism) and UCIOS (with slew-rate control mechanism). While the configurable I/O cell operates in transmitting mode, 7 different output driving currents can be selected in the I/O cell. When the I/O cell operates in receiving mode, the I/O cell becomes an input cell and can be selected with or without the function of schmitt-trigger. When the configurable I/O cell operates in tri-state mode, the functions of pull-up and pull-down can be turned on or off separately. Thus, in this situation, the voltage level at the I/O PAD can be biased at high or low or floating. The analog signals can be transmitted by the analog I/O cell (UAIO25 or UAIO10) which is composed of ESD protection circuit only. The I/O cell library provides four power cells (UVDD25, UVSS25, UVDD10, and UVSS10). The UVDD25 and UVSS25 cells are used to provide the supply voltages for I/O ring, and the UVDD10 and UVSS10 are used to provide the supply voltages for pre-driver and internal circuits.

### 1.3 THESIS ORGANIZATION

In chapter 2, the DC specification of this configurable I/O cell will be listed, and the circuit design and the simulation results of the configurable I/O cell will be specified. The design of ESD protection circuits will be introduced in chapter 3. The whole layout implementation of the I/O cell library will be shown in chapter 4. Besides, in chapter 5, the test chip arrangement for function verification and ESD robustness tests will be illustrated. The experimental results will be shown in chapter 6. Finally, the last chapter ends with a few concluding statements pertaining to the research as well as recommendations for future work in the area.

TORRESS.

Tabel 1.1

Configurable I/O cell library.

| I/O Cells                              |                                                     |                     |  |

|----------------------------------------|-----------------------------------------------------|---------------------|--|

| Cell Name                              | Function                                            | Pins                |  |

| HCIOC                                  |                                                     | PAD, I, S0, S1, S2, |  |

| UCIOS                                  | Configurable I/O Cell with Slew-Rate Control        | PD, PU, SCH, C      |  |

| LICIONS                                | Configuration I/O Collegists and Class Page Control | PAD, I, S0, S1, S2, |  |

| UCIONS                                 | Configurable I/O Cell without Slew-Rate Control     | PD, PU, SCH, C      |  |

| UINPUT                                 | Input Cell                                          | PAD, C              |  |

| UAIO25                                 | Analog I/O for 2.5 V                                | PADwiR, PADwoR      |  |

| UAIO10                                 | Analog I/O for 1.0 V                                | PADwiR, PADwoR      |  |

|                                        | Power Cells                                         |                     |  |

| Cell Name                              | Function                                            | Pins                |  |

| UVDD25                                 | Positive Power Source for I/O Ring                  | VDDIO               |  |

| UVSS25                                 | Ground Supply for I/O Ring                          | VSSIO               |  |

| UVDD10                                 | Positive Power Source for Pre-Driver and Core       | VDD                 |  |

| O V DD10                               | — Circuit                                           | VDD                 |  |

| UVSS10                                 | Ground Supply for Pre-Driver and Core Circuit       | VSS                 |  |

| UPBREAK                                | Power Bus Break Cell                                |                     |  |

|                                        | Other Cells                                         |                     |  |

| Cell Name                              | Cell Name Function                                  |                     |  |

| HEadarVV                               | 0.1, 0.3, 0.5, 1, 2, 5, 10, 15 and 20μm-Width       | of Filler Cells     |  |

| UFeederXX for Interconnection          |                                                     |                     |  |

| UCorner                                | UCorner Cell                                        |                     |  |

|                                        | Physical Dimension of Cells                         |                     |  |

| Cell Pitch                             | Pitch 61.5μm per cell                               |                     |  |

| Cell Hight 101.9μm                     |                                                     |                     |  |

| Metal Layers Suitable for 4 ~ 9 layers |                                                     |                     |  |

Fig. 1.1 The four pin-combination modes for ESD test on an IC product: (a) positive-to-VSS (PS-mode), (b) negative-to-VSS (NS-mode), (c) positive-to-VDD (PD mode), and (d) negative-to-VDD (ND-mode).

Fig. 1.2 Typical on-chip ESD protection circuits in a CMOS IC.

Fig. 1.3 The ESD current paths of the I/O pad with power-rail ESD clamp circuit under the positive-to-VSS (PS-mode) ESD stress. The ESD current paths are indicated by the dashed lines.

# Chapter 2

## Design and Simulation Results of Configurable I/O Cell

#### 2.1 INTRODUCTION OF CONFIGURABLE I/O CELL

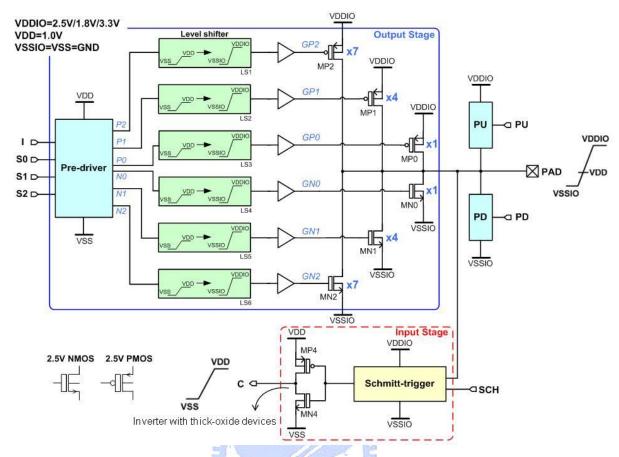

- Fig. 2.1 shows the circuit block diagram of the configurable I/O cell and the function of each block circuit is defined as follows:

- Pre-driver: The driving select signals, S0, S1, and S2, are used to control the configurable I/O cell operating in transmitting mode or in receiving mode (tri-state input mode). When the configurable I/O cell operates in transmitting mode, the pre-driver generates pull up signals, P0, P1, and P2, and pull down signals, N0, N1, and N2. Therefore, the output transistors NMOS and PMOS can be turned on (off) separately to change the output driving capability.

- Level shifter: The voltage level of operation signal is shifted from low (VSS-to-VDD) to high (VSSIO-to-VDDIO).

- Output stage: When the configurable I/O cell operates in transmitting mode, the low voltage level (VSS-to-VDD) at the data input signal, I, will be transformed into the high voltage level (VSSIO-to-VDDIO) at the I/O PAD. Consequently, different amount of output transistors NMOS/PMOS turned on will result in different output driving capability.

- Input stage: When the configurable I/O cell operates in receiving mode, the

schmitt-trigger control signal, SCH, controls input stage to become normal input stage or schmitt-trigger input stage. Moreover, the configurable I/O cell in receiving mode receives VSSIO-to-VDDIO input signal at the I/O PAD and then transmits VSS-to-VDD output signal to core circuit through the input stage.

- Pull-up/Pull-down network: When the driving select signals S0, S1, and S2 are biased at 0V and the I/O PAD is floating, the configurable I/O cell operates in tri-state. In this situation, the mechanism of pull-up and pull-down can be turned on or off by the pull up signal PU and the pull down signal PD.

- Slew-rate control: When the output stage operates with slew-rate control circuit, the simultaneous switching noise (SSN) can be reduced significantly.

Table 2.1, Table 2.2, and Table 2.3 list the pins usage and functions of configurable I/O cell. Besides, the design flow, specific circuit, operation principle, and simulation results of configurable I/O cell are discussed in following sections.

Marining

#### 2.2 BASIC SPECIFICATION

In this configurable I/O cell library, the typical core power supply voltage (VDD) and I/O output driver power supply voltage (VDDIO) are 1.0V and 2.5V. However, the library is also compatible with 1.8-V ~ 3.3-V design window of VDDIO. Therefore, the information of this library will be provided not only with 2.5-V VDDIO, but also with 1.8-V and 3.3-V VDDIO supply voltage in following introduction. Table 2.4, Table 2.5, and Table 2.6 list the DC specification of configurable I/O cell under 2.5-V, 1.8-V, and 3.3-V VDDIO supply voltage, respectively.

#### 2.3 OUTPUT STAGE

#### 2.3.1 Driving Capability

In order to design an output cell with variable driving capability, the transistors of output driver are distributed into three groups, MP0/MN0, MP1/MN1, and MP2/MN2 as shown in Fig. 2.1. The specification on dc driving currents of the configurable I/O cell are defined as 2mA, 8mA, 10mA, 14mA, 16mA, 22mA, and 24mA with different output MOS fingers. When the output driving current is 2mA, the finger number of the output driver is one. Similarly, when the output driving current is 24mA, the finger numbers of the output driver are 12 fingers.

The driving select signals, S2, S1, and S0, are used not only to control the operating mode, but also to choose the output driving capability in transmitting mode. In order to distribute the output driving current equally, 12 fingers of output drive are divided into three groups in parallel. The transistor MP0/MN0 is designed with only one finger, and MP1/MN1 and MP2/MN2 are composed of 4 fingers and 7 fingers, respectively. The relation between the driving capability and the driving select signals (S0, S1, and S2) has been mentioned in Table 2.2. Moreover, the design flow of output driver will be introduced in next paragraph. However, several parameters should be defined firstly in this section as follows:

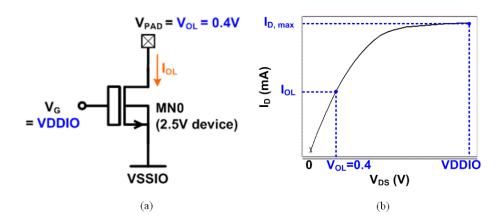

- $I_{OL}$ : The sink current at I/O PAD of configurable I/O cell when the voltage at I/O PAD of configurable I/O cell is biased at  $V_{OL}$  (= 0.4V), as shown in Fig. 2.2.

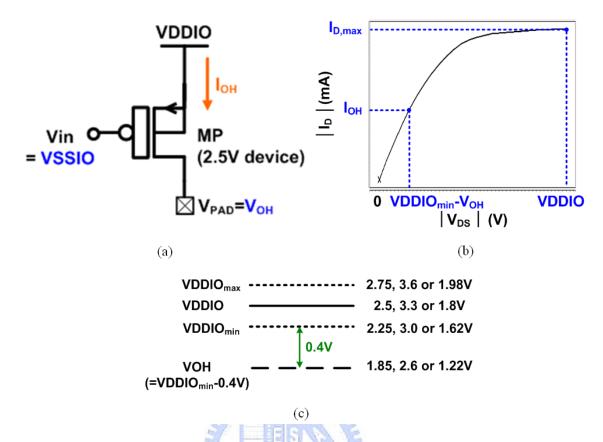

- $I_{OH}$ : The source current at I/O PAD of configurable I/O cell when the voltage at I/O PAD of configurable I/O cell is biased at  $V_{OH}$  (= VDDIO<sub>min</sub> 0.4V = 0.9 x VDDIO 0.4V), as shown in Fig. 2.3.

• Duty cycle: The fraction time that the system in an active state can be expressed as following equation:

$$Duty \ Cycle = \frac{\tau}{T} \tag{1}$$

where  $\tau$  is the duration that the function is non-zero; T is the period of the function.

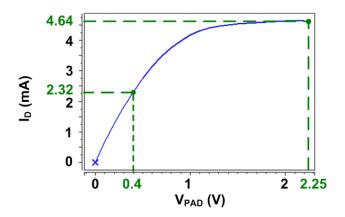

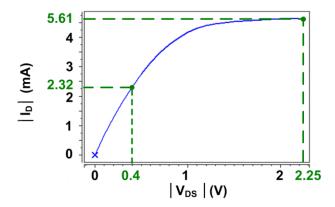

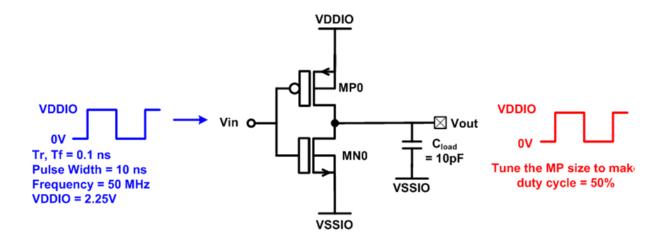

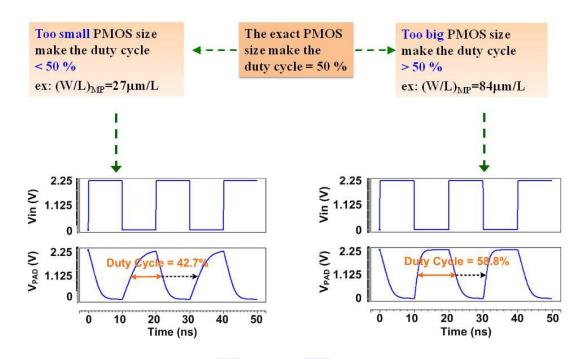

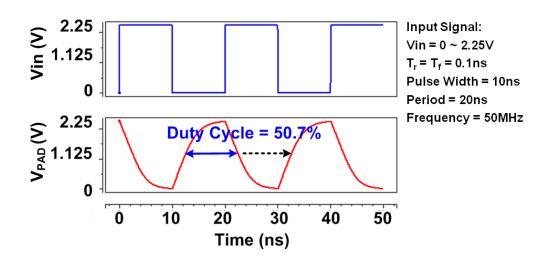

First of all, the size of output NMOS with single finger (MN0) in Fig. 2.1 has to be determined in output driver design. The simulation setup for measuring size of MN0 is shown as Fig. 2.2(a). It has been simulated by SPICE in a 90-nm CMOS process with a simulated environment of 2.25-V (0.9 x 2.5V) VDDIO and the worst case (temperature of 125 °C and SS corner) which can result in the experience results to meet the design specification certainly. Table 2.7 lists the definition of simulated environment. As shown in Fig. 2.4, the MN0 size can be determined with the low level output current I<sub>OL</sub> equaled to 2.32mA. While the simulated and measured values of I<sub>OH</sub>/I<sub>OL</sub> are larger than the definition value (2mA, 8mA, 10mA... 24mA), it can be described as design specification conformability in driving capability. Table 2.8 depicts the simulation results of the level output current I<sub>OL</sub> in different simulation environments. The dimension of the NMOS is determined with 2.25-V VDDIO and the worst case simulation environment. After determining the size of MNO, a single-finger output PMOS, MPO, is combined with this output NMOS as an inverter to design output PMOS. In this thesis, there are two methods to design the output PMOS. The first method determines the size of output PMOS MP0 by the high level output current  $I_{OH} \approx I_{OL}$  where  $I_{OL}$ was the simulated driving current under the worst case and 2.25-V VDDIO for output NMOS, as shown in Fig. 2.5. Fig. 2.6 shows the simulated result of output PMOS MP0 with the channel width of 45.4µm and the simulation environment is set in the worst case and 2.25-V VDDIO. As shown in Fig. 2.7, the second method to determine the size of output PMOS MPO is to make that duty cycle of output signal near to 50% when a square wave with duty cycle of 50% is inputted. A loading capacitance of 10pF is added at I/O PAD in the second method for simulating actual condition and setting the same simulation environment as the first method. The duty cycle of output signal could be more (less) than 50% due to too big (small) PMOS size, as shown in Fig. 2.8. Thus, the channel width of MP0 by second method is determined on 42μm and the simulated duty cycle is 50.7% as shown in Fig. 2.9. According to these two PMOS sizes from these two methods, the corresponding I<sub>OH</sub> and duty cycle are compared in Table 2.9 with the same simulation environment. Since the output PMOS size in the second method is smaller than the first method, the output PMOS size is decided on 42μm.

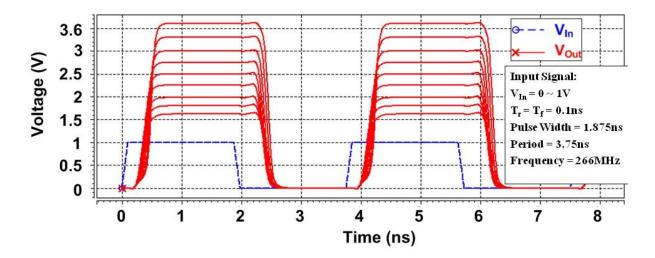

The simulation results of pull high driving current ( $I_{OH}$ ) and duty cycle with different simulation environments are listed in Table 2.10 and Table 2.11, respectively. In Table 2.11, the input signal  $V_{in}$  is set in 0 ~ VDDIO,  $T_r = T_f = 0.1$ ns, pulse width = 1.875ns, period = 3.75ns, frequency = 266MHz and the additional loading capacitance ( $C_{load}$ ) is 10pF. Furthermore, Table 2.12, Table 2.13, and Table 2.14 list the simulation results of duty cycle with different output MOS fingers and operating frequencies under 2.5-V, 1.8-V, and 3.3-V VDDIO voltage supplies. Similarly, the input signal  $V_{in}$  is set in 0 ~ VDDIO,  $T_r = T_f = 0.1$ ns, pulse width = 1.875ns, period = 3.75ns, frequency = 266MHz, and  $C_{load}$  is 10pF but the simulation environment is set with pseudo worst case for close to actual condition.

#### 2.3.2 Short-circuit Current Reduction

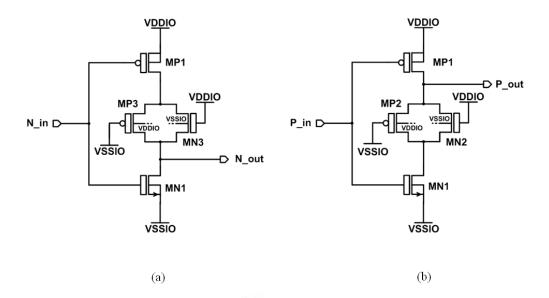

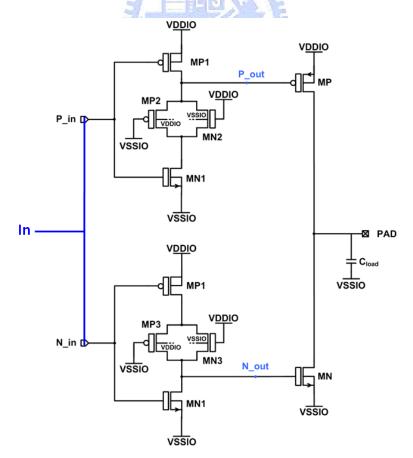

The circuit consumes unnecessary power due to short-circuit current. In order to reduce the short-circuit current at the output stage, the output NMOS/PMOS should be turned on slowly and turned off quickly to avoid DC paths flowed from VDDIO to VSSIO. Thus, the gate-controlled signals of output PMOS (NMOS) should be designed with a short (long) rise time and long (short) fall time. Fig. 2.10 shows the implementation of inverter with short-circuit current reduction. MP2/MN2 and MP3/MN3 are transmission gates as resistive elements to slow down the turn-on signal of output driver. In order to verify the effect of

transmission gates, the inverters with short-circuit current reduction are placed in front of the output driver as shown in Fig. 2.11. Fig. 2.12 shows the simulation results under different VDDIO supply voltage. When the gate-controlled signals (P\_out and N\_out) are pulled up to VDDIO, the signal of N\_out is transmitted more slowly than P\_out. On the contrary, the signal of P\_out is transmitted more slowly than N\_out when P\_out/ N\_out are pulled down to VSSIO. The inverter with short-circuit current reduction can be used to produce a delay of signal.

The inverters with short-circuit current reduction shown in Fig. 2.10 are added to the inverter chains to form the tapper buffers in front of the output driver (MN1~2/MP1~2) as shown in Fig. 2.1. Besides, since single-finger output drivers (MN0/MP0) have small amount of driving currents, the tapper buffers in front of it (MN0/MP0) can be composed of general inverters (without short-circuit reduction) to save layout area. In addition, each gate terminal of MP2-MP3 and MN2-MN3 shown in Fig. 2.10 has to be connected to power line (VDDIO or VSSIO) through a resistance individually to avoid the gate-oxide breakdown under ESD stress condition. However, in order to show the circuit clearly, the resistances are all omitted in this figure.

#### 2.4 PRE-DRIVER

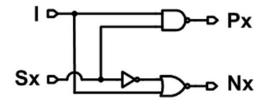

The pre-driver circuit uses thin-oxide (1.0-V) devices since the input data comes from internal core circuit with VSS-to-VDD (0V-to-1.0V) voltage level. Furthermore, the pre-driver circuit generates control signals of output drivers. Table 2.15 lists the truth table of pre-driver circuit, where the control signals (S2-S0), input signal (I), and gate-controlled signals (P2-P0 and N2-N0) correspond to that in Fig. 2.1. According to the table, the relation between the gate-controlled signals (P2P0 and N2-N0) and control/input signals (S2-S0 and I)

can be defined as the equation as follows:

$$Px = \overline{Sx \cdot I} \qquad x = 0, 1, 2$$

$$Nx = (\overline{Sx} + I) \qquad x = 0, 1, 2$$

(2)

Therefore, the logic diagram of pre-driver composed of a NAND gate and NOR gate is shown in Fig. 2.13. However, since parts of transistors can be used commonly to save layout area, the circuit is implemented as shown in Fig. 2.14. Fig. 2.15 shows the simulation waveforms under different frequencies of input signals. It depicts the pre-driver can be operated correctly under different input frequency.

#### 2.5 LEVEL SHIFTER

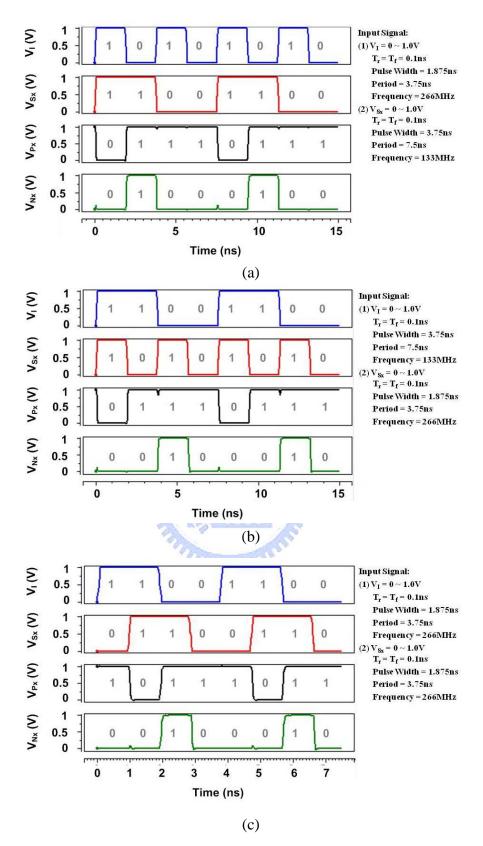

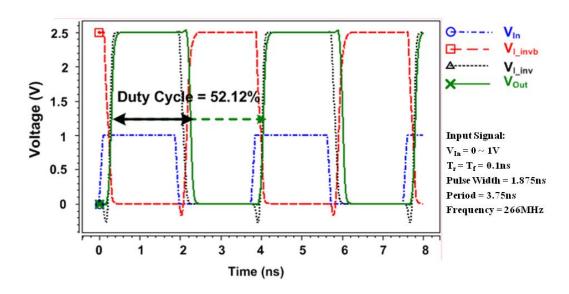

Since the output stage receives VSS-to-VDD (low voltage level) input signals at control/input signal pin (I, S0, S1, and S2) and transmits VSS-to-VDDIO (high voltage level) output signals at I/O PAD, the I/O cell needs a level shifter circuit to shift the voltage level from VDD to VDDIO. Fig. 2.16 shows circuit implementation of level shifter. Two inverters connected to gate terminals of transistors MN1 and MN2 separately are comprised of 1.0-V devices, other transistors are 2.5-V devices. When the input (In) receives a DC signal of VDD (1.0V), the node Inb and node In\_buff are biased at VSS and VDD. Thus, the transistor MN2 (2.5V device) is turned on weakly due to the  $V_{GS, MN2} = 1.0V$  and MN1 is turned off. However, when the node I\_invb is pulled down to logic low, the node I\_inv will start to be pulled up to logic high through the transistor MP1. Therefore, the transistor MP2 will be switched off, and then the output (Out) will be biased at VDDIO due to the node I\_invb is biased at 0V. On the contrary, when the input (In) receives a DC signal of VSS (0V), the level shifter will transmit a logic high output signal to output (Out). Fig. 2.17 and Fig. 2.18 show the simulation

waveforms of level shifter circuit. The duty cycles are simulated under different simulation conditions as listed in Table 2.16. A small amount of load capacitance ( $C_{load}$ ) is added to simulate the parasitic capacitance while the output is connected to the input of inverter chain.

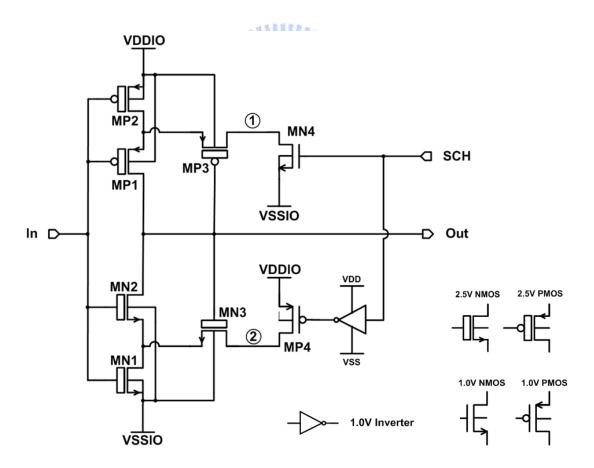

#### 2.6 INPUT STAGE

The circuit diagram of schmit-trigger with an enable signal, SCH, is shown in Fig. 2.19, where the transistors MN4/ MP4 are 1.0-V devices, and the others are 2.5-V devices. While SCH receives logic high (1.0V) to trigger the function of schmitt-trigger, the node 1 and 2 are biased at VSS (0V) and VDD (1.0V) and then the noise margin will be enhanced. On the contrary, while SCH receives logic low to turn off the function of schmitt-trigger, the node 1 and 2 are floating points and then the circuit will become a inverter to form normal input stage.

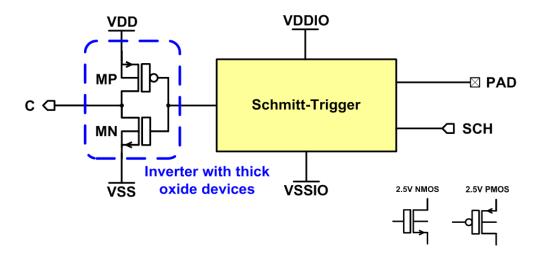

In this configurable I/O cell, the I/O cell receives VSSIO-to-VDDIO (0V ~ 2.5V/1.8V/3.3V) input signal at I/O PAD and transmits VSS-to-VDD (0V ~ 1.0V) output signal at pin to internal circuit (C) as shown in Fig. 2.1. An inverter has been added to shemitt-trigger circuit as shown in Fig. 2.20. The supply voltage VDD (1.0V) is used to transform the voltage level from VSSIO-to-VDDIO (high voltage level) to VSS-to-VDD (low voltage level). In order to overcome gate-oxide reliability [1] and hot-carrier degradation [2], this inverter is composed of thick-oxide devices. However, the inverter with thick-oxide devices causes a small |Vgs| of the transistor MP when MP is turned on. Thus, in order to make a close 50-persentage duty cycle of output signal, MP has been designed in a big size to enhance the driving capability.

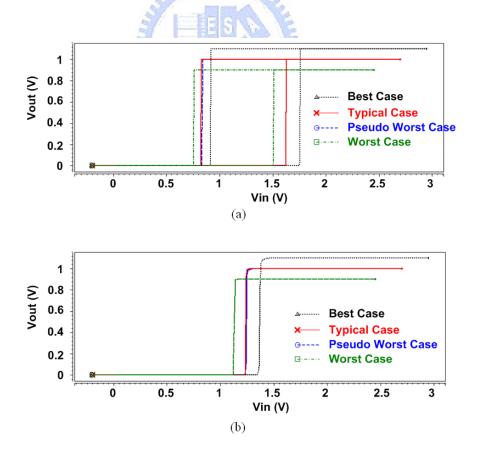

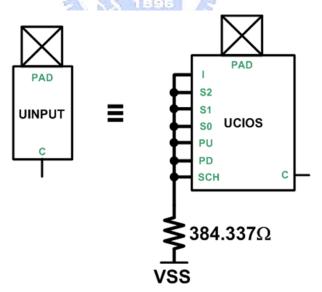

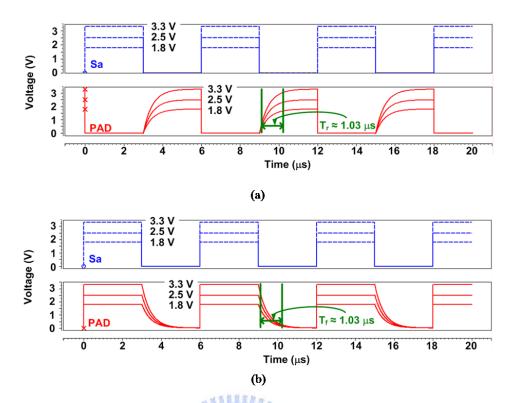

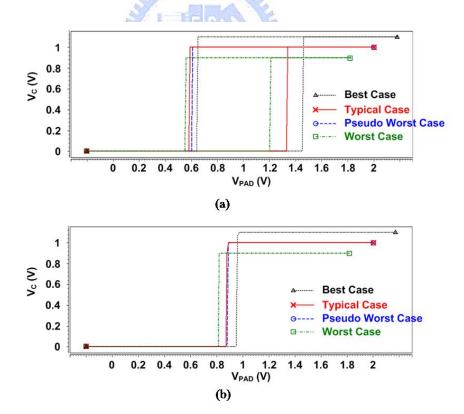

Fig. 2.21 shows the simulated voltage transform curve (VTC) of schmitt-trigger under

different simulation conditions, and Table 2.17 lists the corresponding threshold voltages ( $V_{T+}$ ,  $V_{T-}$ , and  $V_{TH}$ ). The waveforms of output signal, C, is simulated while the I/O PAD is swept from logic low to high and then return to its initial voltage level. The  $V_{T+/-}$  is defined as the voltage level of I/O PAD while the voltage level of C is VDD/2 with the function of schmitt-trigger (SCH = 1). The  $V_{T+}$  is I/O PAD transmitted from low to high, and the  $V_{T-}$  is that from high to low. The  $V_{TH}$  is defined as the voltage level of I/O PAD while the voltage level of C is VDD/2 without the function of schmitt-trigger (SCHa = 0). Fig. 2.22-24 show the simulation waveforms of input stage when the I/O PAD is inputted a signal with 266-MHz frequency under different VDDIO supply voltage, and Table 2.18-19 list the duty cycle under different simulation conditions. Since the  $|V_{T+}|$  of the transistor MN shown in Fig. 2.20 vary from 1.62V to 3.6V, the range of duty cycle in Table 2.18 and 3.19 are 45.72% ~ 56.65% and 44.85% ~ 61.79%, respectively.

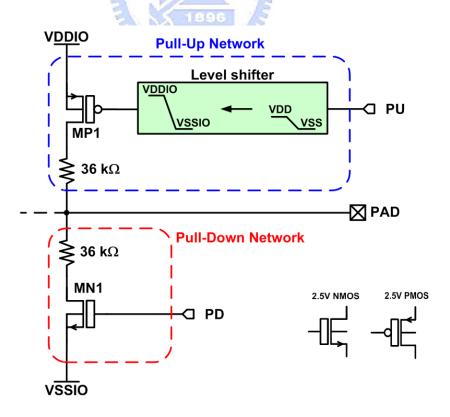

## 2.7 PULL-UP/PULL-DOWN NETWORK

In this thesis, the pull-up and pull-down resistances are formed with a PMOS and NMOS operating in linear region, respectively. Besides, in order to prevent ESD stress, two 36k-Ω resistances are placed individually between the I/O PAD and the drain terminal of PMOS/NMOS as shown in Fig. 2.25. To avoid an undesired leakage current, the control signal PU (VSS-to-VDD) is shifted to high voltage level (VSSIO-toVDDIO) by level shifter mentioned in section 2.4 to turn the PMOS (MP1) off completely.

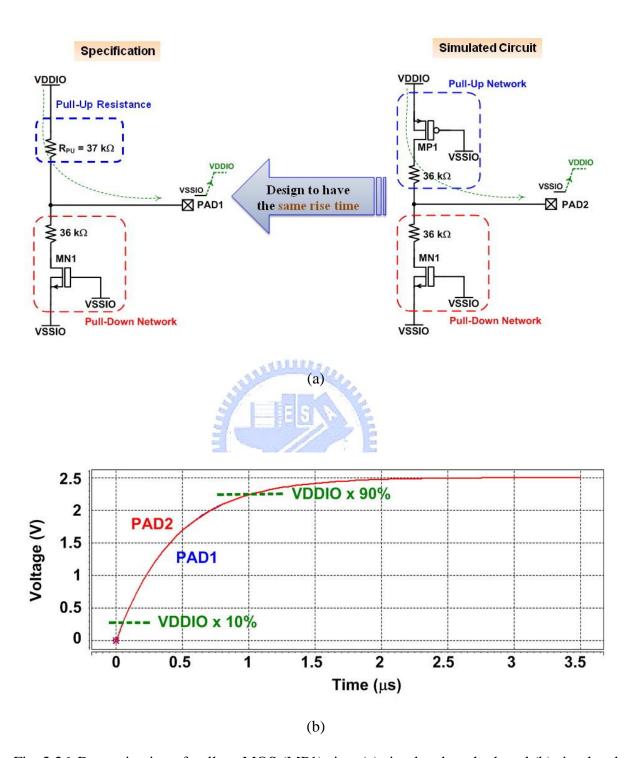

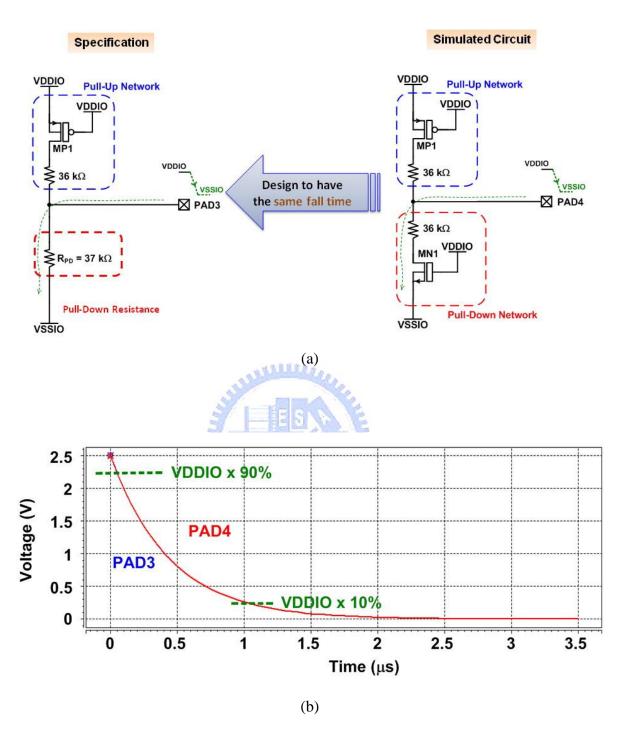

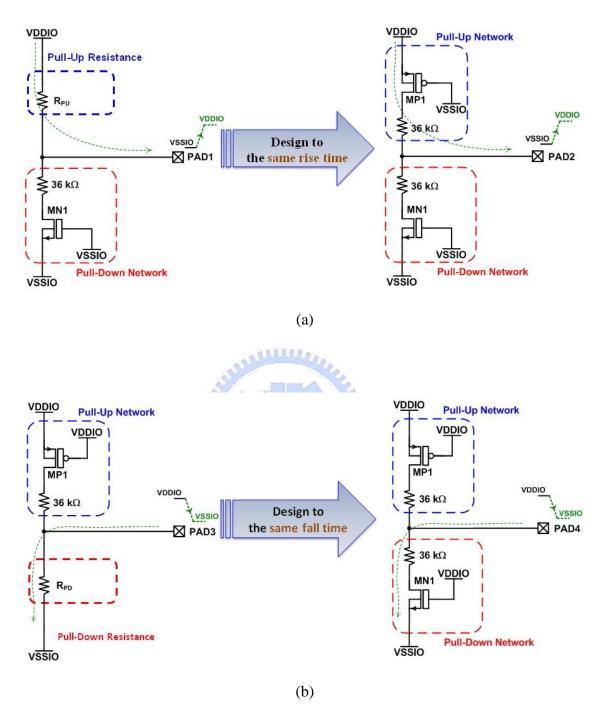

Since the equivalent resistance of the PMOS/NMOS (MP1/MN1) operating in linear region is nonlinear resistance, the rise/fall time of pull-up/pull-down network is near to that with the pull-up/pull-down resistances of design specification to determine the MP1/MN1

sizes. As shown in Fig. 2.26, to determine the size of the pull-up MOS (MP1), the gate terminals of MP1 and MN1 are biased at 0V to turn on the MP1 and turn off the MN1, respectively. Under the same additional load capacitance ( $C_{load}$ ) of 12pF, MP1 and the 36k- $\Omega$  series resistance are replaced by an ideal resistance ( $R_{PU}$ ) of 37k $\Omega$ . In order to make that these two simulated circuit have similar rise time, the device size of MP1 can be optimized with the typical simulation case and 2.5-V VDDIO. Therefore, the device size of MP1 can be determined and the corresponding ideal resistance can be defined as the equivalent pull-up resistance ( $R_{PU}$ ) in simulated circuit, simultaneously. Similarly, the dimension of pull-down MOS (MN1) is determined as shown in Fig. 2.27. Hence, the size of MN1 can be determined and the corresponding ideal resistance is defined as the equivalent pull-down resistance ( $R_{PD}$ ) in simulated circuit, simultaneously.

After determination of the MP1/MN1 size, Fig. 2.28 shows the simulation setup of the equivalent pull-up/pull-down resistances ( $R_{PU}/R_{PD}$ ) in simulated circuits with different simulated conditions and load capacitance of 12pF. The  $R_{PU}/R_{PD}$  is modified to obtain the same rise/fall time of the pull-up/pull-down network. The simulation results are listed in Table 2.23 and Table 2.24. The variation of pull-up/pull-down resistance is listed in Table 2.25.

#### 2.8 SLEW-RATE CONTROL

#### 2.8.1 Introduction

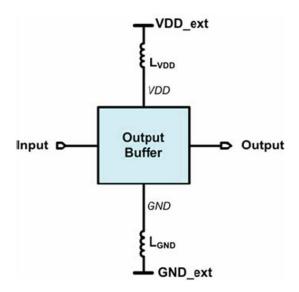

Signal and power integrity are crucial issues in VLSI systems. Modern trends in deep sub-micron circuit designs, such as high operating frequencies, short rise/fall times, and lower supply voltage, exacerbate this problem. Output buffers provide an interface for driving mainly capacitive and inductive external loads. The capacitive load typically consists of the

bonding wire, the pin, the conductors on the PCB and the input capacitances of connected gates. The inductive load usually comprises the package parasitic series inductances of the power and ground lines supplying the output buffer, connected to the external power and ground rails on the PCB. A major component of the circuit noise is the inductive noise. Ground bounce, also known as simultaneous switching noise (SSN) or delta-I noise, is a voltage glitch induced at power/ground (P/G) distribution connections due to switching currents passing through either wire/substrate inductance or package lead inductance associated with power or ground rails. When the current flows through the inductance L, the voltage drop can be expressed as

$$V = L \frac{di}{dt} \tag{3}$$

In the output buffer design, the transistors sizing is imposed by DC interfacing constraints. This leads to several problems [11]:

- Unacceptable high current peaks which occur with the simultaneous switching of many output buffers;

- Inductive power supply noise which results in large voltage drops;

- Electromagnetic interference (EMI) due to high output edge switching rates.

The results noise voltage can potentially cause spurious transitions at inputs of devices sharing the same power and ground rails. Therefore, controlling the output voltage variations is generally required to limit the crosstalk and reduce the inductive power supply noise to an acceptable value. Besides, the effect of ground bounce in output buffer can be simply modeled as an inductor shown in Fig. 2.29 [12].

#### 2.8.2 Concept of Slew-rate Control

To solve these problems, a reduction of the slew rate in the output edges is preferred as far as the speed specification is satisfied [13]. A simple approach is to slow down the turn-on time of the output switching transistor through an access resistor to the transistor gate. Furthermore, the output driver can be divided into several parallel output drivers for ground bounce reduction and slew-rate control. An output buffer with slew-rate control, which is a three-step slew-rate control circuit, is shown in Fig. 2.30 [14]. The parallel output transistors of slew-rate controlled output buffer turn on progressive through delay elements implemented by resistors or transmission gates. This helps reduce the slew rate of output buffer and the ground/power bounce. However, the output transistors turn off step by step as output transistors turn on.

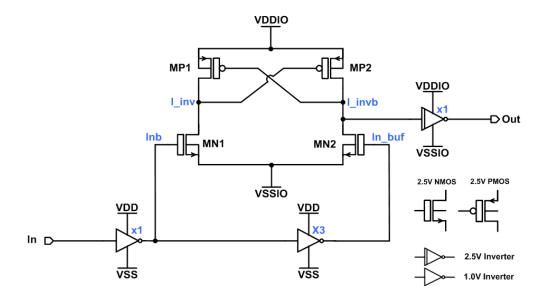

#### 2.8.3 Design of Slew-rate Control

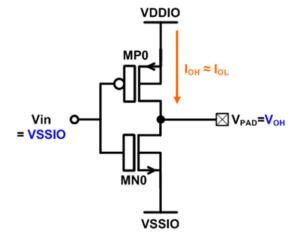

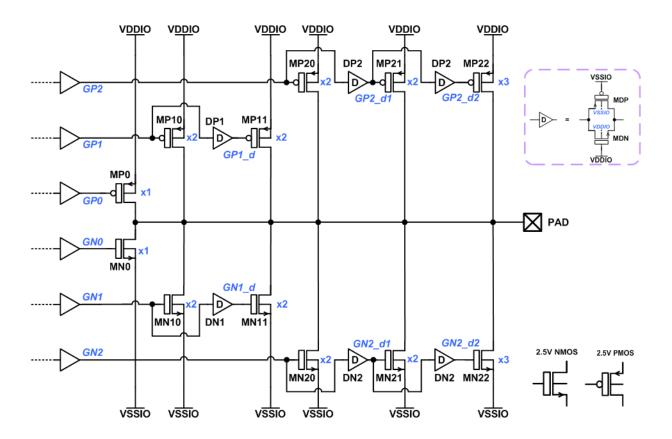

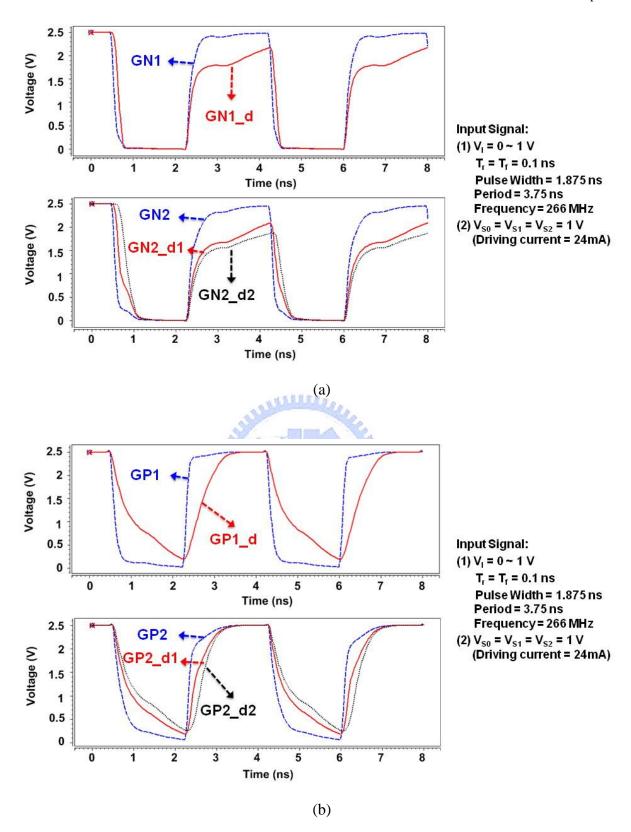

Fig. 2.31 shows the output driver of configurable I/O cell with slew-rate control to reduce ground/power bounce. The delay elements are implemented by transmission gate (MDN/MDP). The original MN1/MP1 (multiple=4) shown in Fig. 2.1 are divided into MN10/MP10 (m=2) and MN11/MP11 (m=2). The original MN2/MP2 (m=7) are divided into MN20/MP20 (m=2), MN21/MP21 (m=2), and MN22/MP22 (m=3). In order to reduce short-circuit current simultaneously, the gate-controlled signals of output NMOS have to be designed with longer rise times and shorter fall times. Thus, larger NMOS width and smaller PMOS width of transmission gates DN1 and DN2 are needed. On the contrary, larger PMOS width and smaller NMOS width of transmission gates DP1 and DP2 are needed.

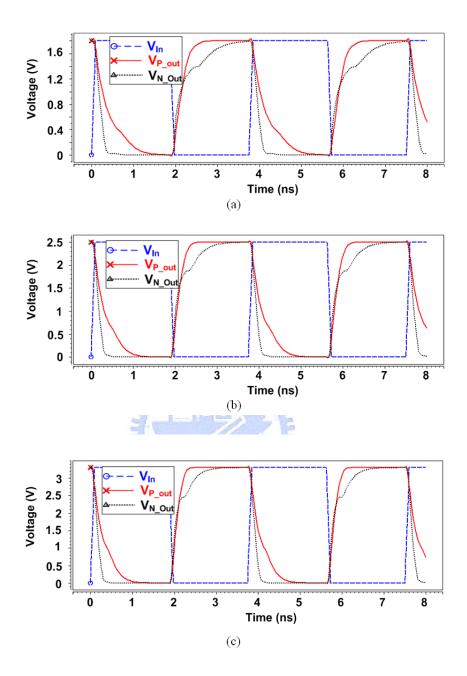

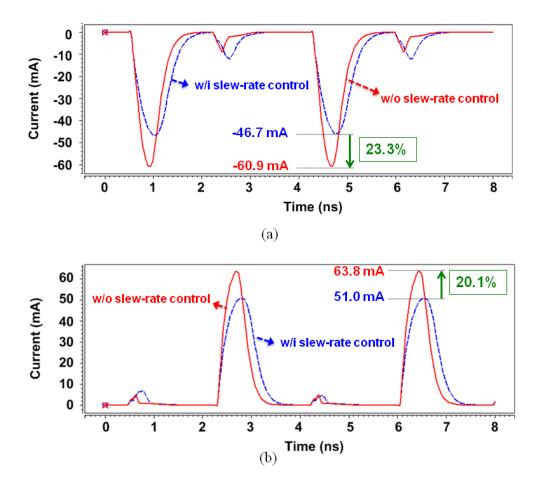

The gate-controlled signals of output driver with slew-rate control are simulated as shown in Fig. 2.32, and the corresponding switching current on power and ground lines are

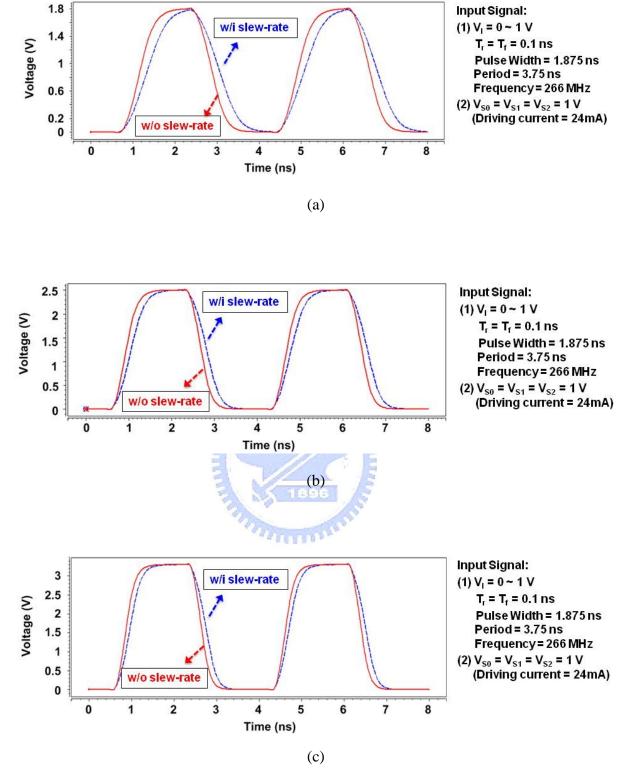

shown in Fig. 2.33. As a result, the ground bounce effects of output driver with slew-rate control were improved obviously. Fig. 2.34 shows the output waveforms of the configurable I/O cell with different VDDIO supply voltages. The rise times and fall times of output driver with slew-rate control are longer than those of output driver without slew-rate control. Table 2.23 and Table 2.24 list the simulation results of maximum switching current reduction on VDDIO and VSSIO power lines, respectively.

Tabel 2.1

Pin description.

| Input Control Pins | Description             |

|--------------------|-------------------------|

| SCH                | Schmitt-trigger enable  |

| PU                 | Pull up enable          |

| PD                 | Pull down enable        |

| S0, S1, S2         | Driving select          |

| I                  | Data input              |

| PAD                | Bidirectional pin       |

| С                  | Pin to internal circuit |

Tabel 2.2

Configurable I/O cell with different output driving.

| Operating Mode        | Control Pins |            |    | ins | Output Driving | Input Function        |  |

|-----------------------|--------------|------------|----|-----|----------------|-----------------------|--|

| Operating Mode        | S2           | <b>S</b> 1 | S0 | SCH | Output Driving | Input Function        |  |

| Receive               | 0            | 0          | 0  | 1   | 3              | Schmitt-trigger input |  |

| $(PAD \rightarrow C)$ | 0            | 0          | 0  | 0   |                | Normal input          |  |

|                       | 0            | 0          | 1  | X   | 2mA            |                       |  |

|                       | 0            | 1          | 0  | X   | 8mA            |                       |  |

| Tuo n ann :4          | 0            | 1          | 1  | X   | 10mA           |                       |  |

| Transmit              | 1            | 0          | 0  | X   | 14mA           |                       |  |

| $(I \rightarrow PAD)$ | 1            | 0          | 1  | X   | 16mA           |                       |  |

|                       | 1            | 1          | 0  | X   | 22mA           |                       |  |

|                       | 1            | 1          | 1  | X   | 24mA           |                       |  |

Tabel 2.3

State of I/O PAD in configurable I/O cell with different input signal.

|    |            | Output |   |    |    |          |           |   |

|----|------------|--------|---|----|----|----------|-----------|---|

| S2 | <b>S</b> 1 | S0     | Ι | PU | PD | PAD      | PAD       |   |

| 0  | 0          | 0      | X | 0  | 0  |          | High-Z    |   |

| 0  | 0          | 0      | X | 1  | 0  |          | Pull-up   |   |

| 0  | 0          | 0      | X | 0  | 1  | No input | Pull-down |   |

|    | Else       |        |   |    | X  | X        |           | 1 |

|    |            |        | 0 | X  | X  |          | 0         |   |

Tabel 2.4 DC specification of configurable I/O cell in 2.5-V VDDIO supply voltage.