# 國立交通大學

電子研究所

博士論文

具製程電壓溫度補償之非晶體震盪器電路設計 與實現

DESIGN AND IMPLEMENTATION OF CRYSTAL-LESS CLOCK GENERATOR WITH PROCESS VOLTAGE TEMPERATURE COMPENSATION

研 究 生: 陸亭州(Ting-Chou Lu)

指導教授: 柯明道(Ming-Dou Ker)

冉曉雯(Hsiao-Wen Zan)

中華民國一〇六年 六 月

# 具製程電壓溫度補償之無晶體震盪器電路設計 與實現

# DESIGN AND IMPLEMENTATION OF CRYSTAL-LESS CLOCK GENERATOR WITH PROCESS VOLTAGE TEMPERATURE COMPENSATION

研究生: 陸亭州

指導教授:柯明道

冉晓雯

**Student: Ting-Chou Lu**

**Advisor: Ming-Dou Ker**

Hsiao-Wen Zan

國立交通大學

電子研究所

博士論文

A Dissertation

Submitted to Institute of Electronics

College of Electrical and Computer Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

in

Electronics Engineering

June 2017 Hsinchu, Taiwan, Republic of China

中華民國一〇六年 六 月

# 具製程電壓溫度補償之無晶體震盪器電路設計 與實現

研究生:陸亭州 指導教授:柯明道 博士

冉曉雯 博士

國立交通大學電子研究所

摘要

隨著半導體製程進步,低操作電壓電路之應用逐漸隨半導體進步而日趨盛行,而其中最無法降低電壓部分為晶體振盪器。其有穩地性極佳但必須操作在高操作電壓之工作環境之特性。因此,無晶體振盪器之可行性日趨重要,但低操作電壓伴隨著電路操作頻率增快、處理資料量增加,引發劇烈系統晶片溫度變化,降低電路穩定性、造成資料錯誤等缺點。為了避免上述問題產生以及搭配低電壓電路設計,系統晶片整合時需規劃於電路中一溫度製程補償電路,作為監測並管理晶片溫度於安全範圍內。因此低成本、高精準度之無晶體頻率產生器已成為近年積體電路相當熱門之研究議題。

傳統類比式無晶體振盪器利用疊接方式做操作電壓之補償,並利用BJT 作為穩定溫度之能帶除參考電壓電路。然而此些方式並無法利用在低電壓 之溫度補償架構上主要為BJT之可驅動電壓遠大於低電壓之操作電壓。此 種溫度補償電路為具有高解析且高精準度之溫度補償電路。但由於電路功 率消耗大、晶片面積大、轉換率低、製成與電壓限彈性度低等缺點。使得 傳統式溫度補償電路於低電壓應用時,有許多限制與成本過高的問題。 為改善上述類比式溫度感測器缺點,本篇提出低電壓操作電路,利用基極操作電壓,次臨界區MOSFET操作元件,以及-gm增益放大技術來使得操作於低電壓趨為可行。實現具有功率消耗低、晶片面積小、設計複雜度低與系統相容度高之溫度補償電路,改善了傳統式溫度補償電路之缺點。但是電路特性與應用規格之不同,目前尚未有人達到低電壓頻率飄移精準之無晶體頻率產生器。

本篇論文主要提出共兩顆不同的具溫度電壓頻率補償之無晶體震盪器,一為具八個相位輸出,本電路實現於TSMC 18um混合訊號製程,供應電壓為1.8伏特並以環型震盪器為基底,採用兩點校正的方式,並找出所在之製程及溫度飄移後,使用簡易類比方式進行線性度修正增加量測精準度,提供具溫度製程補償之準確輸出。並在於面積極小的情況,達到相位間誤差小於5.5%以及duty Cycle 誤差小於4.3%,經修正後溫度係數為小於70ppm/°C,八相位頻率為192MHz之輸出頻率。

另一顆為超低壓具溫度補償之無晶體頻率產生器,本電路實現於TSMC 65nm混合訊號製程,供應電壓為0.5伏特,並提供一不具頻率電壓溫度影響且其輸出頻率為2.4GHz 之時脈,前端以環型振盪器及LC壓控震盪器以及數位電路構成製程選擇電路,校正頻率產生器因製程變異引起的偏移誤差。經選擇製程後由查看設計好的比較表後再經溫度補償。以低電壓的能帶隙電壓產生電路以及低電壓之溫度控制器產生一部隨溫度以及製程影響之電路;功率消耗為2.5mW/sample,操作溫度0°C~100°C,經查表修正後頻率誤差為33.47 ppm/°C。

本研究將以類比式無晶體頻率產生器之方法為主,保留原有之優點並朝高精準度補償為設計目標,以達到頻率飄移為50 ppm/°C 之規格。此外傳統文獻中為了提高精準度於量測時採用兩點校正(two point calibration)之測試方法,增加了許多測試成本,此問題亦為本研究探討要點之一。

此外。為了維持論文的完整性,附錄A並收錄了利用了TCAD軟體模擬 討論背電極對非晶體氧化銦鎵鋅(amorphous IGZO)之空乏層的影響,因為 電子空乏效應,在高的功函數的背金屬下,電子都被金屬移走,而此行為 導致了臨界電壓的增加,而利用了TCAD軟體的模擬,可發現增加通道長度 以及減少厚度可以有效地增進此效應。而附錄B收錄了作者於博士班期間 發表的另一篇有關玻璃基板的參考電壓電路。

### DESIGN AND IMPLEMENTATION OF CRYSTAL-LESS CLOCK GENERATOR WITH PROCESS VOLTAGE TEMPERATURE COMPENSATION

Student: Ting-Chou Lu Advisor: Dr. Ming-Dou Ker

Dr. Hsiao-Wen Zan

#### Abstract

Process and temperature variations have become a serious concern for ultra-low voltage (ULV) technology. The clock generator is the essential component for the ULV very-large-scale integration (VLSI). MOSFETs is operated in the sub-threshold region are widely applied for ULV technology. However, MOSFETs at subthreshold region have relatively high variations with process and temperature. In this paper, process and temperature variations on the clock generators has been studied.

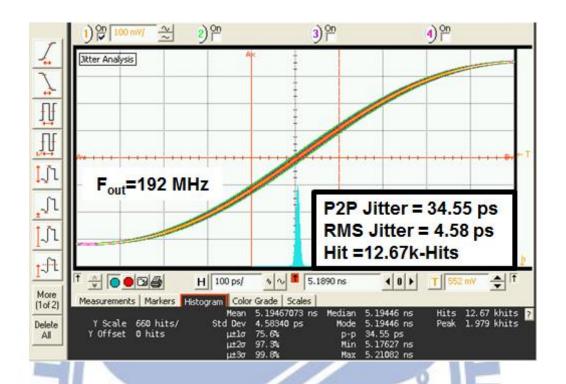

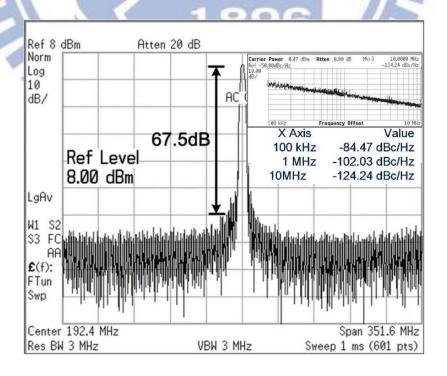

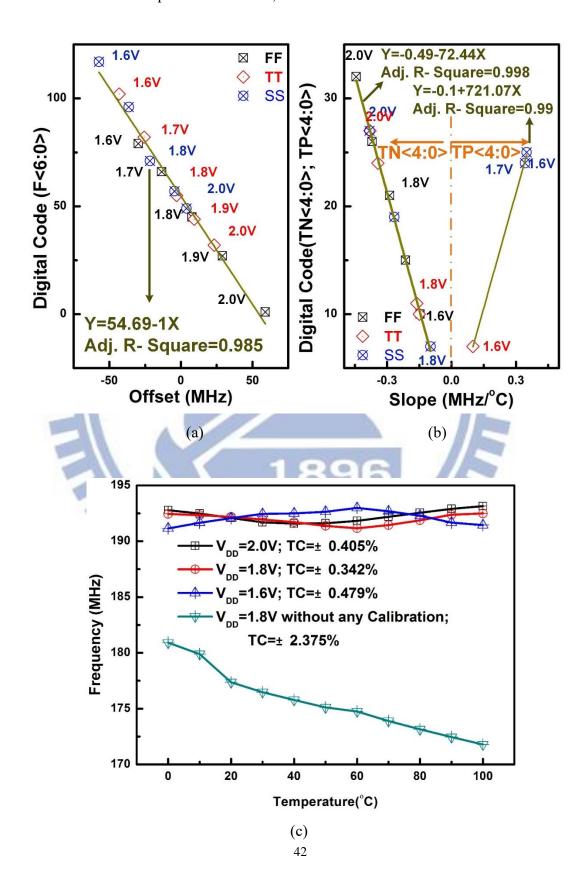

A multi-phase crystal-less clock generator (MPCLCG) with a process-voltage-temperature (PVT) calibration circuit is proposed in Chapter 3. It operates at 192 MHz with 8 phases outputs, and is implemented as a 0.18 μm CMOS process for digital power management systems. A temperature-calibrated circuit is proposed to align operational frequency under process and supply voltage variations. It occupies an area of 65μm ×75μm and consumes 1.1 mW with the power supply of 1.8 V. Temperature coefficient (TC) is 69.5 ppm/°C from 0 to 100°C, and 2-point calibration is applied to calibrate PVT variation. The measured period jitter is a 4.58-ps RMS jitter and a 34.55-

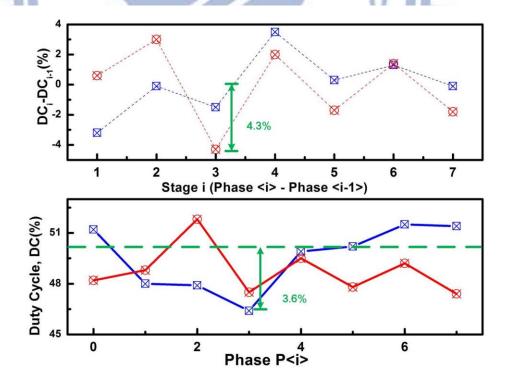

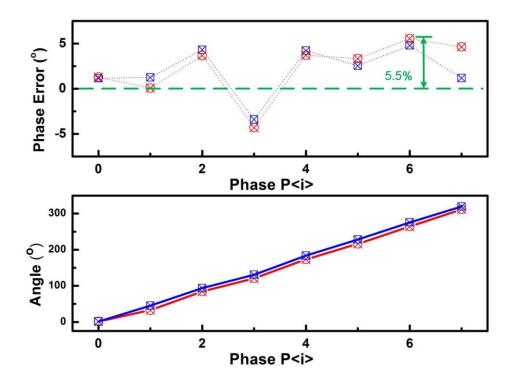

ps peak-to-peak jitter (P2P jitter) at 192 MHz within 12.67k-hits. At 192 MHz, it shows a 1-MHz-offset phase noise of -102dBc/Hz. Phase to phase errors and duty cycle errors are less than 5.5% and 4.3%, respectively.

Being operated with 0.5V supply voltage in a standard 65nm CMOS process, a new CMOS temperature compensated crystal-less clock generator. The bias current provided by the bandgap reference circuit and low-dropout operate amplifier are nearly independent of temperature due to the existence of mutual compensation of mobility and threshold voltage variation. The new proposed temperature compensated crystal-less clock generator functions well by the analog linear compensation mechanism. Chapter 4 presents an ultra-low voltage 2.4GHz CMOS voltage controlled oscillator with temperature and process compensation. A new all-digital auto compensated mechanism to reduce process and temperature variation without any laser trimming is proposed. With the compensated circuit, the VCO frequency-drift is 16.6 times the improvements of the uncompensated one as temperature changes. Furthermore, it also provides low jitter performance. We also discuss the time to digital converter system for time measurement unit in chapter 5.

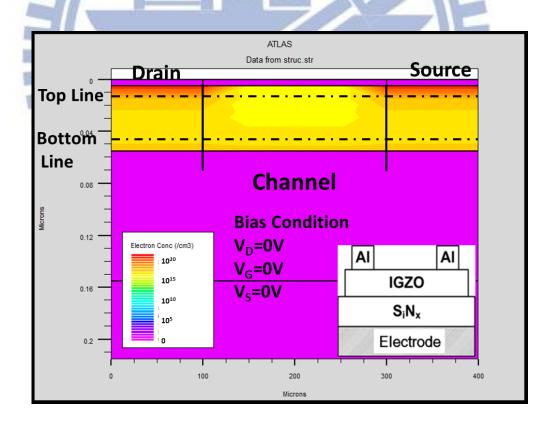

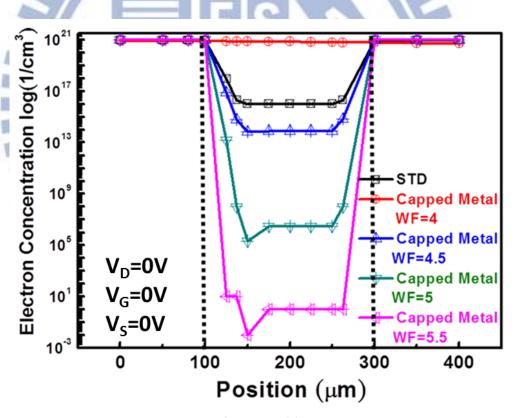

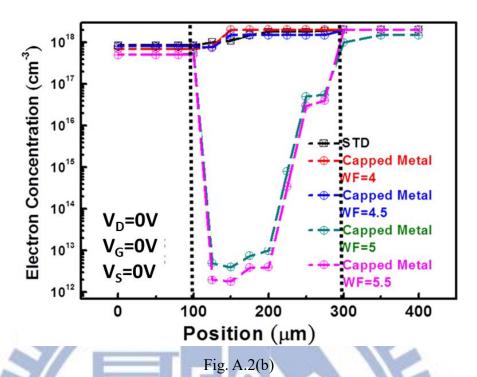

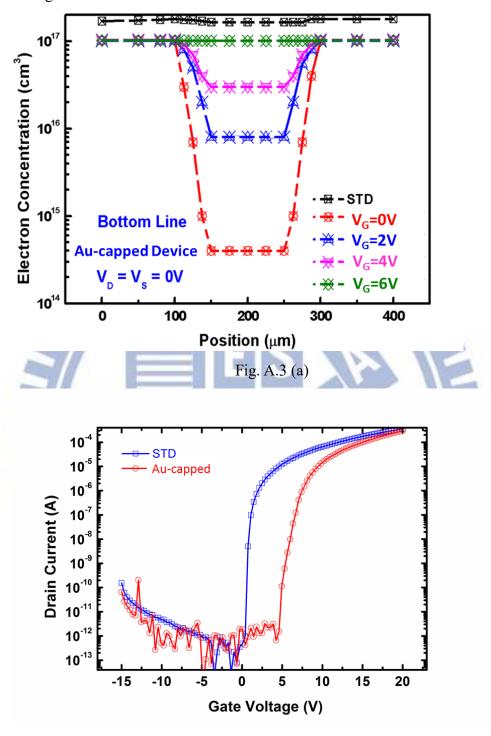

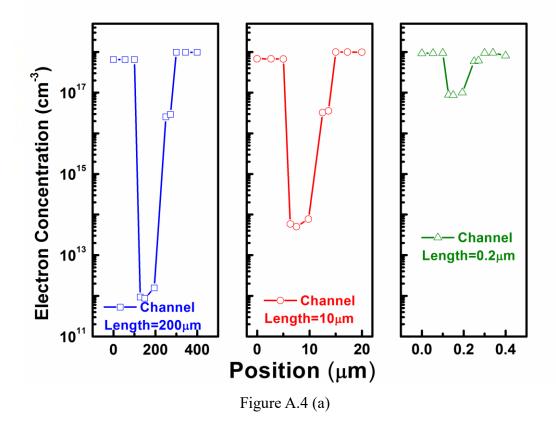

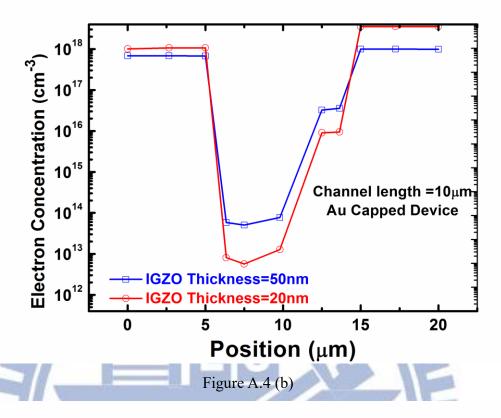

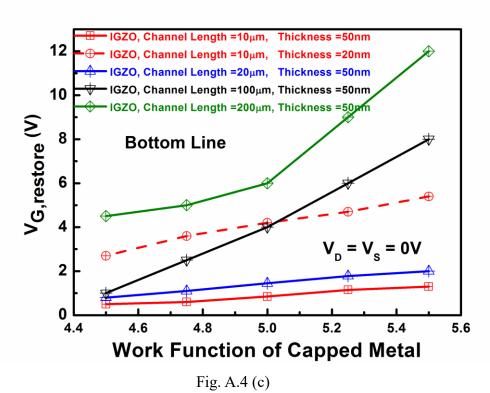

The Appendix A shows the electron distribution in an amorphous indium—gallium—zinc-oxide (a-IGZO) thin-film transistor (TFT) with a floating metal—semiconductor (MS) back interface is analyzed using a technology computer-aided design (TCAD) model. The channel geometry (i.e., length and thickness) effect is carefully investigated. At a high work function (i.e., 5 eV) of the capping metal, the capping metal (electron depletion effect) mostly removes electrons inside a-IGZO. The depletion of the IGZO film leads to an increase in threshold voltage in a-IGZO TFT. TCAD simulation reveals that increasing channel length and decreasing IGZO thickness significantly enhance such an electron depletion effect. Finally, the electron depletion effect is applied to a-IGZO TFT with a high-conductivity IGZO film to greatly suppress the leakage current by over 5 orders.

The Appendix B shows a voltage reference circuits on poly-Silicon TFT. Because this paper is based on author's master thesis, detailed contents could refer the author's master thesis.

### 致謝

日子過得越久,要感謝的人也就越多,能看清的事實也就越多。同時打破兩個教授團隊博士最高就讀年限真是有愧關心我的大家,讓各位擔心了。終於,算 是結束了一段旅程。

感謝指導教授柯明道教授的不厭其煩的指證論文上的缺失,雖然當下會覺得 痛苦,但是回想起來當注重到各種小細節才能真正確保到一件事情的穩定成功性。 感謝冉曉雯教授的指導與關心,在帶領學生從幾乎門外漢的情況到期刊論文產出 的各種教導,並於合作期間提供眾多資源讓學生放心研究。

非常謝謝各位口試委員,吳重雨校長、鄭國興教授、黃錫瑜教授、謝志成教授、洪崇智教授以及陳柏宏教授,各位教授能很準確地針對論文不足之處,提供 確實的建議。感謝陳龍英教授,在學生當助教時,提供各個方面的協助。

工研院的各位同事,劉仁傑博士在帶領我學習各種電路技術到指導人生上的 建議,李瑜副理,實際上技術電路教導以及針對個人時間緊急與否做工作上調整, 感謝黃立仁組長、朱元華組長、鄭乃禎、蔡昆儒、胡華珊學姊、梁詠智學長、洪 淑萍、邱煥科學長以及各位同事在工作上的幫忙。

謝謝 307 實驗室的學長姐以及學弟妹們的幫忙,蕭淵文博士、顏承正學長、 林群佑學長、豪哥、歐陽有儀、廖期聖、竹立瑋、林宛彦、陳思翰、戴嘉岑、李 易儒、楊逸弘、林曉平、謝佳琪、陳俊成.... 等等族繁不及備載,也謝謝冉老師 實驗室的各位學長、學弟妹,高士欽、陳蔚宗.... 等人的幫忙。也感謝重訓的夥 伴吳智祥、陳英仁讓我在這漫長的博士人生能夠健康地度過,也感謝大學同學邱 程翔在我投稿時的各種英文修改以及哈拉,及其他同學朋友的協助。

謝謝林宥婕在我最低潮時的消愁解悶,並願意陪我走過這一段人生,也感謝我家人父親陸海林、母親劉文玉以及弟弟陸亭佑在背後的支持,以及其他親屬的關心以及協助。

Even the darkest night will end and the sun will rise. Victor Hugo, Les Misérables

## 謹以此篇論文獻給我摯愛的家人

陸亭州 於 2017/06/28

# **Contents**

| Chapter 1. | Ir       | ntroduction1                                                   |

|------------|----------|----------------------------------------------------------------|

| 1.1.       | Mot      | ivation1                                                       |

| 1.2.       | Ana      | lysis of PVT Variations of VLSI system                         |

| 1.3.       | Ana      | lysis and Design of PVT Compensation for Clock System5         |

| 1.4.       | Thes     | sis Oranization                                                |

| Chapter 2. | Basi     | ics of CLCGs and Their Corresponding PVT Compensated           |

| Circ       | cuit     | 9                                                              |

| 2.1.       | Ope      | ration Principle of Crystal-less Clock Generators and the      |

| Accompa    | anied No | oise9                                                          |

| 3          | 2.1.1.   | Operational Principle of Crystal-less Clock Generators9        |

|            | 2.1.2.   | Noise Analysis of Crystal-less Clock Generator10               |

| 2.2.       | Ove      | rview of CLCG with PVT Compensation15                          |

|            | 2.2.1.   | CMOS-based Oscillators and Related PVT Compensation15          |

|            | 2.2.2.   | Relaxation Oscillators and Related PVT Compensation19          |

|            | 2.2.3.   | LC Oscillators and Related PVT Compensation22                  |

|            | 2.2.4.   | Micro Electro Mechanical Systems and their PVT                 |

| Con        | npensati | on25                                                           |

| Chapter 3. | A        | n 8 phases 192 MHz Crystal-less Clock Generator with PVT       |

| Cal        | ibratio  | n28                                                            |

| 3.1.       | Arcl     | nitecture of CLCG with PVT compensation Circuit28              |

|            | 3.1.1.   | Crystal-less Clock Generator and Phase Error Corrector Circuit |

|            |          | 29                                                             |

|            | 3.1.2.   | PVT Calibrated Circuit31                                       |

|            | 3.1.3.   | Level Shifter                                                  |

| 3.2.       | Stab     | ility of Temperature Compensation Circuit37                    |

| 3.3.       | Exp      | eriment Results                                                |

|            | 3.3.1.   | Concept                                                        |

|            | 3.3.2.   | Environment Setup                                              |

|            | 3.3.3.   | Jitter and Phase Noise Performance                             |

|           | 3.3.4       | 4. Measurement of Temperature Compensation             | 41          |

|-----------|-------------|--------------------------------------------------------|-------------|

|           | 3.3.5       | 5. Duty cycle Error and Phase to Phase Error           | 43          |

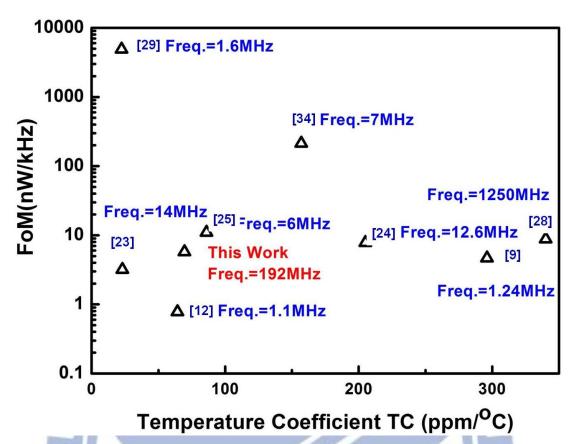

| 3.        | .4. C       | Comparison and FOM                                     | 44          |

| 3.        | .5. C       | Conclusion                                             | 47          |

| Chapter 4 | 4.          | The Ultra-Low Voltage CMOS Voltage Controlled Osc      | illator     |

| W         | vith Vol    | tage, Process and Temperature Compensation             | 48          |

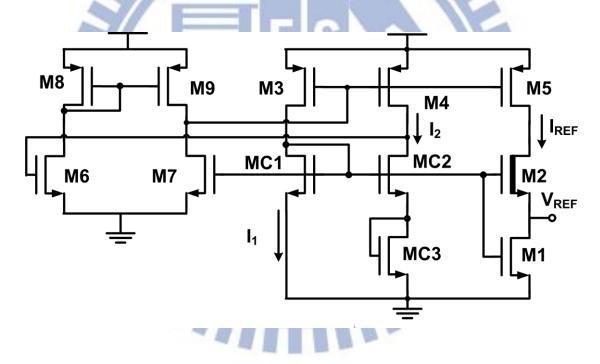

| 4.        | .1. C       | Concept of VCO with PVT Compensation                   | 49          |

| 4.        | .2. A       | rchitecture and Circuit Implementation                 | 50          |

|           | 4.2.        | 1. Auto-Calibrated Process and Temperature Circuit and | nd Its      |

| O         | perating    | g Principle                                            | 50          |

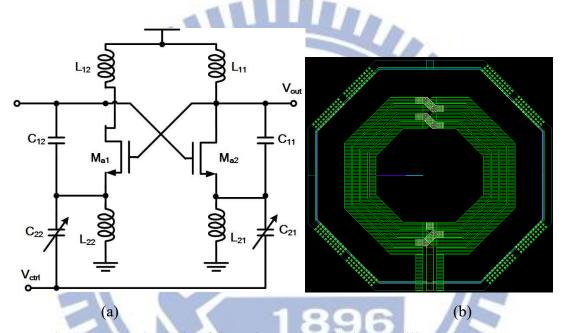

|           | 4.2.2       | 2. Process LC Oscillator                               | 55          |

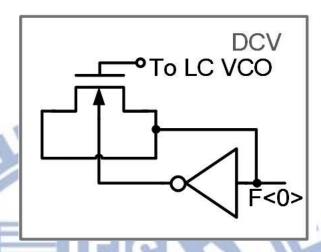

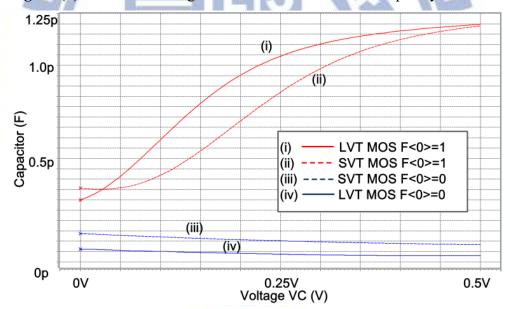

|           | 4.2.3       | 3. Digital Controlled Varactors                        | 56          |

| 4         | 4.2.4       | 4. Temperature Compensated Voltage Reference Con-      | sisting     |

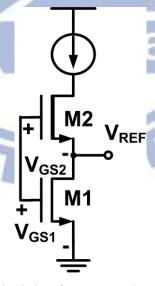

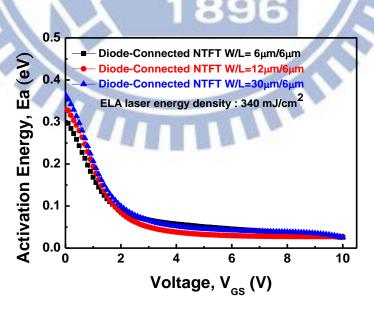

| S         | ubthresl    | hold MOSFETs                                           | 58          |

| 4.        | .3. E       | xperiment Results                                      | 62          |

|           | 4.3.        |                                                        |             |

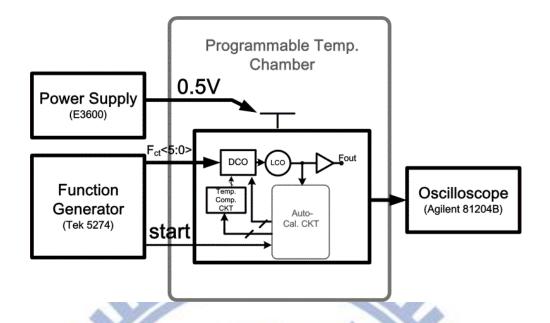

|           | 4.3.2       | 2. Environment Setup                                   |             |

|           | 4.3.3       |                                                        |             |

|           | 4.3.4       | 8                                                      |             |

| 100       | 4.3.5       | 5. Measurement under PVT Variation                     | 69          |

| 4.        | -           | OM and Comparison                                      |             |

| 4.        | .5. C       | onclusion                                              | 76          |

| Chapter 5 |             | Conclusion and Future Works                            |             |

| 5.        | $.1.$ $S_1$ | pecific New Results of This Dissertation               |             |

| 5.        | .2. Fu      | uture Works                                            | 79          |

|           |             |                                                        |             |

| Append    | dix A. I    | nvesting Electron Depletion Effect in Amorphous IGZO T | ſ <b>FT</b> |

|           | ,           | with a Floating Capping Metal by TCAD                  | 81          |

| A         | 1. Iı       | ntroduction                                            | 81          |

| A         | .2. S       | Simulation Setting and Experimental                    | 82          |

| A         | .3. S       | Simulation Results                                     | 84          |

| A         | .4. C       | Conclusion                                             | 91          |

| Appendix B. | . TC of Poly-Silicon TFT and its Application on | Voltage |

|-------------|-------------------------------------------------|---------|

|             | Reference Circuit                               | 92      |

| B.1.        | Introduction                                    | 92      |

| B.2.        | Traditional Voltage Reference Circuit           | 94      |

| B.3.        | TFT Fabrication.                                | 96      |

| B.4.        | Measured Results and Temperature Model          | 97      |

| B.5.        | Application on Voltage Reference Circuit        | 105     |

| B.6.        | Conclusion.                                     | 108     |

| Reference   |                                                 | 109     |

# **Figure Captions**

| Figure 1.1 C  | Comparison between XO and CLCGs [14]2                                          |

|---------------|--------------------------------------------------------------------------------|

| Figure 1.2 E  | Block Diagram of XO systems5                                                   |

| Figure 1.3 E  | Block Diagram of Temperature [29]6                                             |

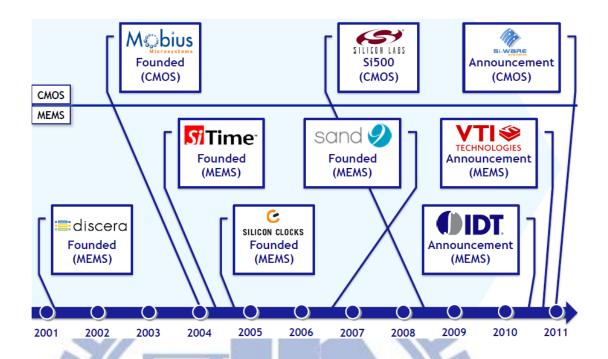

| Figure 1.4    | Main IC Supplies of CLCGs [28]7                                                |

| Figure 2.1    | The block diagram of linear model for oscillator9                              |

| Figure 2.2    | The block diagram of linear model for oscillator10                             |

| Figure 2.3    | (a) The schematic diagram of CLCG. []                                          |

| Figure 2.4    | The noise and impedance schematic diagram of CLCG13                            |

| Figure 2.5 (a | a)Time domain of DJ and (b) related jitter histogram14                         |

| Figure 2.6T   | he noise and impedance schematic diagram of CLCG15                             |

| Figure 3.1    | Block diagram of the proposed CLCG                                             |

| Figure 3.2    | Schematic of the 8 phases differential ring oscillator29                       |

| Figure 3.3    | (a) Block diagram of the VCO, LS, and PEC, and (b) simulated                   |

| result b      | between output phase and phase error30                                         |

| Figure 3.4    | Block diagram of the PVT calibrated circuit31                                  |

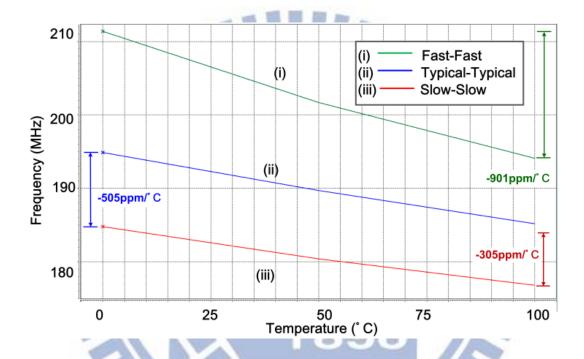

| Figure 3.5    | Simulated frequency versus temperature for the proposed DCO                    |

| withou        | t temperature calibration                                                      |

| Figure 3.6    | Simulated drain current I <sub>D</sub> and drain voltage V <sub>D</sub> versus |

| temper        | ature for the temperature calibration part                                     |

| Figure 3.7    | Simulated frequency versus temperature for the proposed VCO                    |

| under(a       | a)typical-typical and (b)slow-slow corner with supply voltage                  |

| variatio      | on35                                                                           |

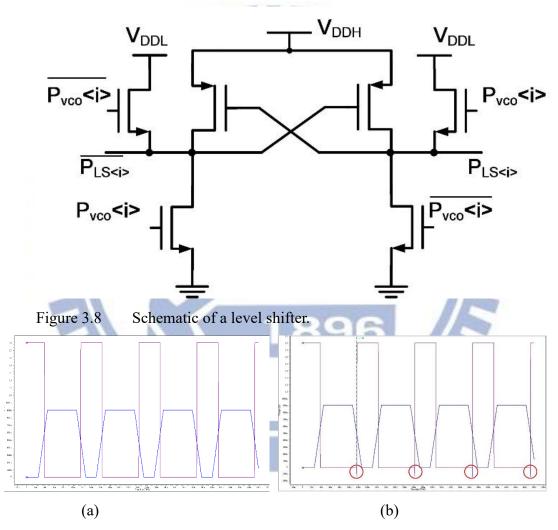

| Figure 3.8    | Schematic of a level shifter                                                   |

| Figure 3.9    | Simulation result of level shifter (a) without (b) with two NMOS               |

| devices       | 36                                                                             |

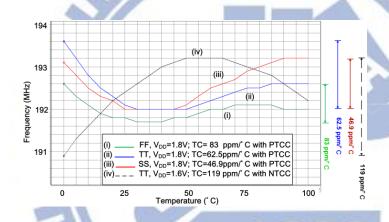

| Figure 3.10   | Simulation results of frequency versus temperature for the                     |

| propos        | ed CLCG after calibration37                                                    |

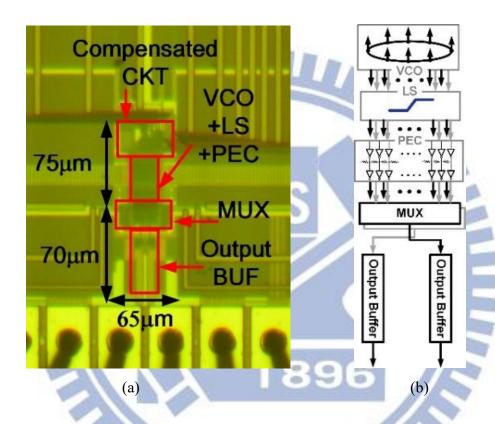

| Figure 3.11   | (a) Die photograph of the proposed circuit, and (b) block of                   |

| output        | stage                                                                          |

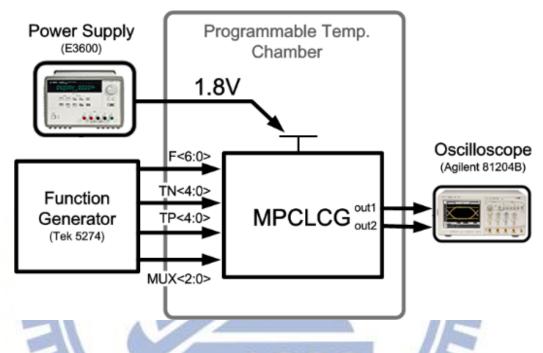

| Figure 3.12   | Measurement setup                                                              |

| Figure 3.13   | Jitter performance where RMS=4.58ps and P2P=34.55ps of 192                     |

| MHz output at 1.8V40                                                          |

|-------------------------------------------------------------------------------|

| Figure 3.14 Measured output spectrum and phase noise of 192MHz output         |

| of the VCO with a supply voltage of 1.8 V                                     |

| Figure 3.1 (a) Relationship between digital code and (a)offset, (b)slope, and |

| (c) Measurement result after temperature calibration with VDI                 |

| variation                                                                     |

| Figure 3.16 Measurement result of duty cycle error and phase to phase         |

| duty cycle error                                                              |

| Figure 3.17 Measurement result of output phase and phase to phase error       |

| 44                                                                            |

| Figure 3.18 FOM versus Temperature coefficients                               |

| Figure 4.1 Block diagram of the proposed CLCG                                 |

| Figure 4.2 The block diagram of auto-calibrated compensated circuit           |

| 5                                                                             |

| Figure 4.3(b) Simulated result of frequency versus temperature for the        |

| ring oscillator without any calibration.                                      |

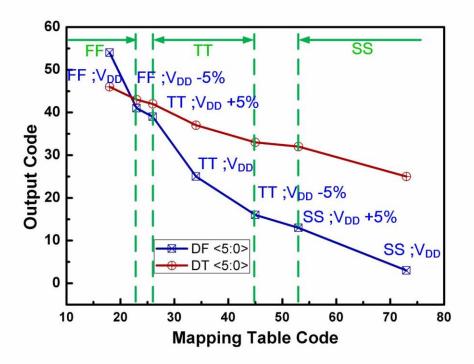

| Figure 4.4 (b). Relationship between mapping table code and output code       |

| 54                                                                            |

| Figure 4.5 Schematic of the voltage-controlled LC oscillator56                |

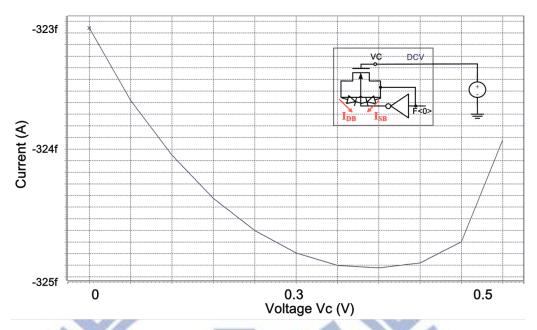

| Figure 4.6(c) The forward biasing current of the D-B and S-B diodes versu     |

| tuning voltage58                                                              |

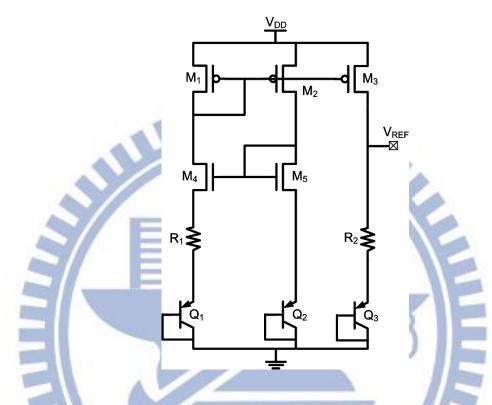

| Figure 4.7. Scheme of principle of a proposed voltage reference58             |

| Figure 4.8 Scheme of proposed temperature compensated voltage                 |

| reference 60                                                                  |

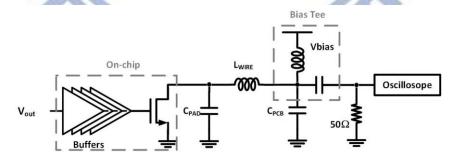

| Figure 4.9 Measurement setup                                                  |

| Figure 4.10 The output stage and equivalent impedance of measuremen           |

| environment                                                                   |

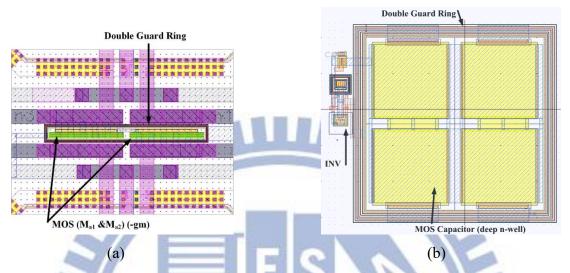

| Figure 4.11 Layout view of (a) MOS Capacitor and (b) –gm64                    |

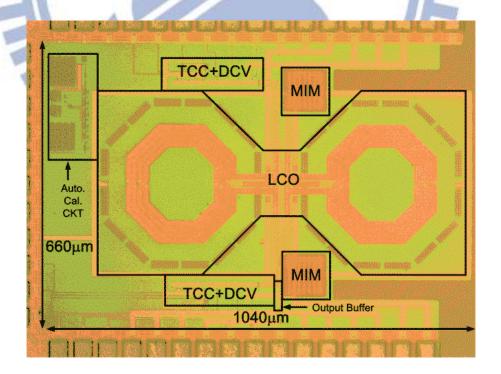

| Figure 4.12 Die photograph of the proposed circuit fabricated in a 65-nn      |

| CMOS process. 62                                                              |

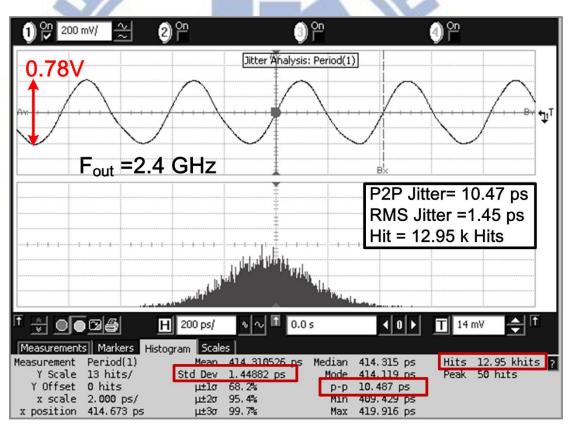

| Figure 4.13 Jitter performances where RMS=1.45ps and P2P=10.47ps o            |

| 2.4GHz output at $V_{DD}$ =0.5V65                                             |

| Figure 4.14. Measured output spectrum and phase noise of 2.4 GHz output       |

| of the VCO with a supply voltage of 0.5V66                                                      |

|-------------------------------------------------------------------------------------------------|

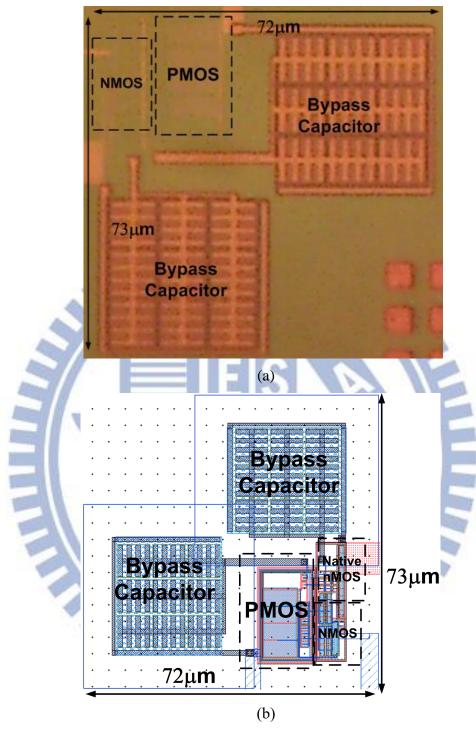

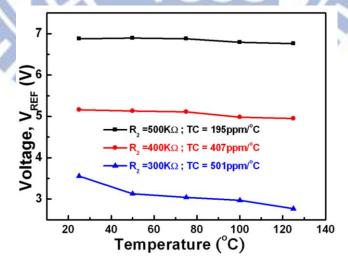

| Figure 4.15. (a)Die photo and (b) layout of the proposed CMOS voltage                           |

| reference circuit                                                                               |

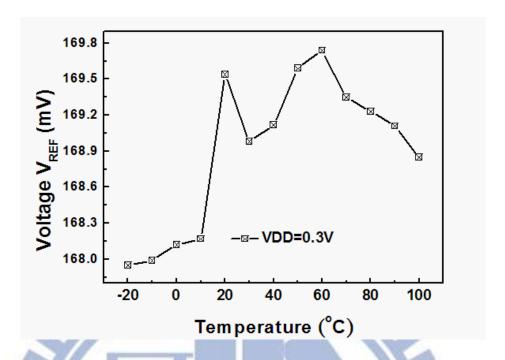

| Figure 4.16 Measured output voltage as a function of temperature. Supply                        |

| voltage sets to 0.3 V. Temperature coefficients 105 ppm/°C were                                 |

| observed68                                                                                      |

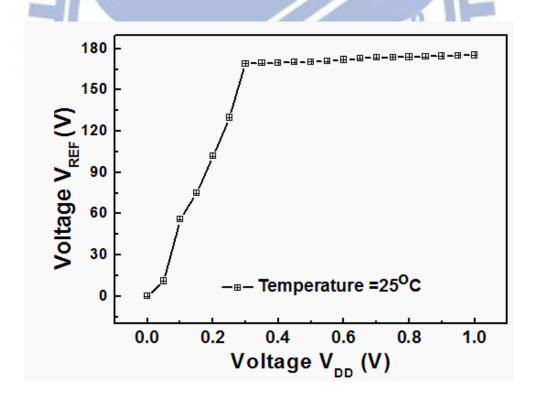

| Figure 4.17 Measured output voltage VREF at room temperature (T=25°C)                           |

| as a function of power supply. Line regulation was 4.8% for supply                              |

| voltages 0.3-1.0V                                                                               |

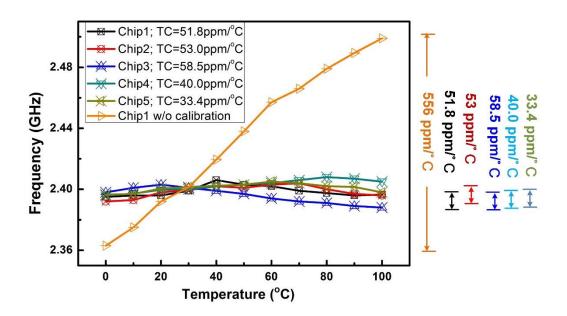

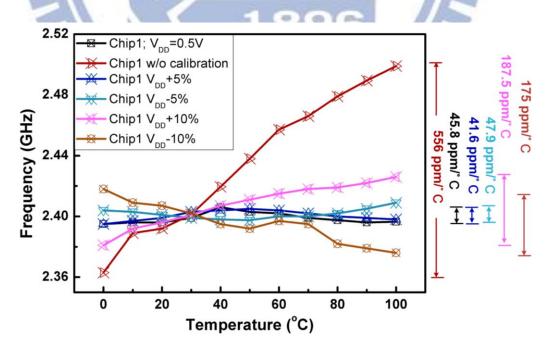

| Figure 4.18 (b). Measured results of frequency versus temperature with the                      |

| supply voltage variation70                                                                      |

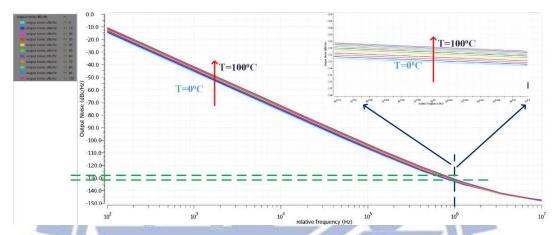

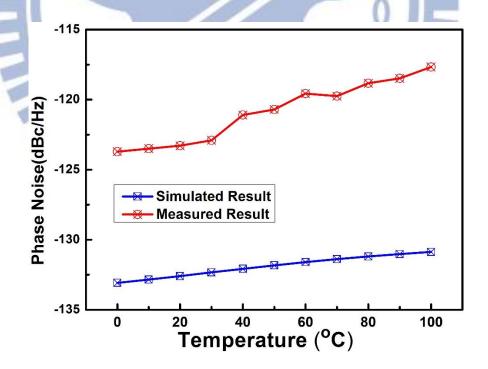

| Figure 4.19 Measured and simulated results of the relationship between                          |

| phase noise and temperature71                                                                   |

| Figure 4.20 Measured Results of output power at (a)T= $0^{\circ}$ C, (b) T= $20^{\circ}$ C, (c) |

| $T=50^{\circ}\text{C}$ , and (d) $T=100^{\circ}\text{C}$                                        |

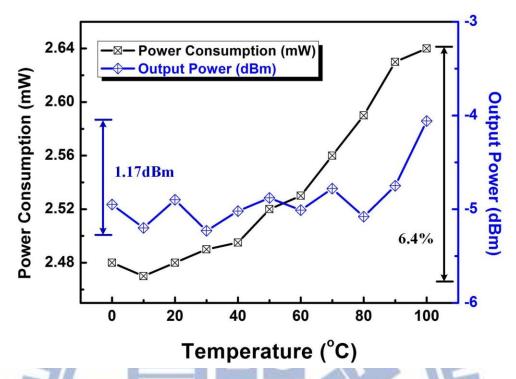

| Figure 4.21 Measured results of power consumption and output power 73                           |

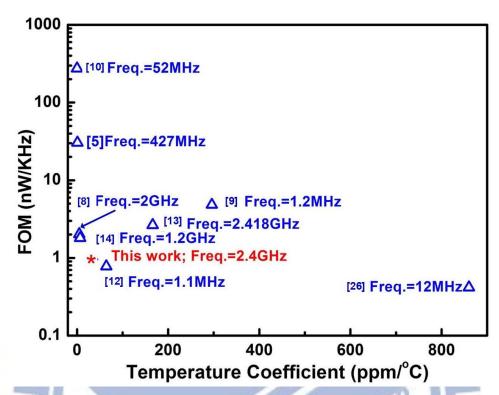

| Figure 4.22. FoM versus Temperature Coefficients                                                |

| Figure A.1 The electron concentration along (a) Top Line and (b) Bottom                         |

| Line in STD and FMC IGZO TFTs with different work functions of the                              |

| floating metal85                                                                                |

| Figure A.2 (a) The electron concentration of STD and FMC a-IGZO TFT                             |

| with different gate bias. Drain and source are grounded (VD=VS=0). (b)                          |

| The experimental transfer characteristic of STD and Au-capped a-IGZO                            |

| TFTs86                                                                                          |

| Figure A.3 Bottom-Line electron concentrations of Au-capped IGZO                                |

| TFT with (a) different channel length and (b) different IGZO thickness.                         |

| (c) V <sub>G,restore</sub> plotted as the work function of the floating capping metal           |

| with different channel length and IGZO thickness88                                              |

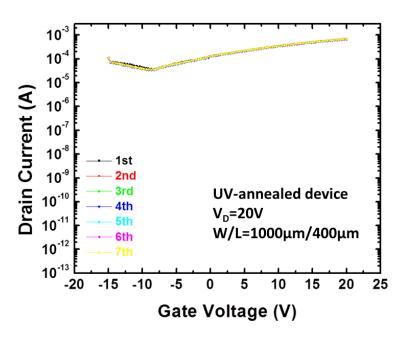

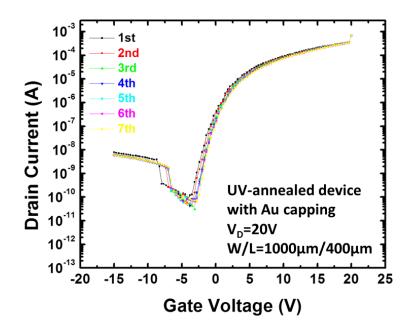

| Figure A.4. Experimental transfer characteristics of (a) UV-annealed a-IGZO                     |

| TFT and (b) UV-annealed a-IGZO TFT after Au capping. Continuous 7-                              |

| times measurements were shown90                                                                 |

# **Table Captions**

| Table 1.1 | Order of magnitude variability time domains and estima | ted |

|-----------|--------------------------------------------------------|-----|

|           | delay impact                                           | 3   |

| Table 1.2 | Categorization of device variations                    | 4   |

| Table 3.1 | Performance comparisons of clock generators            | .46 |

| Table 4.1 | Performance comparisons of clock generators            | .77 |

# **Chapter 1. Introduction**

This chapter deals with the background and the organization of this dissertation are discussed. First, the motivation of this thesis has been mentioned. Secondly, we discuss the delay variation of process, voltage, and temperature on VLSI system. And then the compensation methods for different clock references are introduced. Finally, the organization of this dissertation is well described.

#### 1.1. Motivation

With the explosive growth of portable devices and biotechnology, wireless has become one of the most important design criteria in digital, analogy, and radio frequency (RF) circuits [1]. The clock generator is an essential component for such applications. However, power consumption and frequency drifts are the key factors to be overcome in the clock generator. The crystal oscillators (XOs) had been widely applied for most condition

XOs provide precise reference clock to PLLs or DLLs for high-speed applications. However, the crystal (XTAL) is an off-chip component with high power consumption [4]. Nowadays, crystal-less clock generators have been attracted by portable devices manufactories because their low cost, small size, and on-chip characteristics.

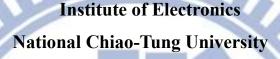

Figure 1.1 shows the comparison of XOs and CLCGs. We can find that temperature variations and phase noise are Process, voltage and temperature (PVT) variations are the critical factors of frequency drifts for clock generators. Typically, PVT compensations include material and electronic compensations [5], [6]. Material

compensation applies a substance with a positive temperature coefficient of frequency (TCF) in the resonator such as SiO<sub>2</sub> to neutralize the effect of negative TCF of the silicon resonator [7], [8]. Electronic compensations include off-chip and on-chip calibrations. Both mostly above methods combine proportional to absolute temperature (PTAT) circuit and the complementary to absolute temperature (CTAT) circuit to compensate temperature variations. Off-chip calibrations compensate the variation by off-chip circuits or external control signals [9], [10]. On-chip compensation, also known as auto calibrations, integrate sensors and compensated circuits and could all be accomplished in the chip [11], [12]. Since the additional testing procedure and off-chip circuitry are reduced, low cost will then become another advantage in on-chip compensation. Nowadays, on-chip compensation has been widely implemented with increasing precision [13], [14].

Figure 1.1 Comparison between XO and CLCGs [14].

# 1.2. Analysis of PVT Variations of VLSI system

| Time<br>domain<br>(s) | Mechanism                               | Delay impact<br>approx. (3 sigma)<br>(%) |

|-----------------------|-----------------------------------------|------------------------------------------|

| 10 <sup>12</sup>      | Lithography node                        | 20                                       |

| 10 <sup>9</sup>       | Electromigration                        | 5                                        |

| $10^{8}$              | Hot-electron effect                     | 5                                        |

| $10^{6}$              | Negative bias temperature instability   | 15                                       |

| $10^{4}$              | Chip electrical mean variation          | 15                                       |

| $10^{-1}$             | Across-chip $L_{\text{poly}}$ variation | 15                                       |

| $10^{-4}$             | Self heating/temperature                | 12                                       |

| $10^{-8}$             | SOI history effect                      | 10                                       |

| $10^{-10}$            | Supply voltage                          | 17                                       |

| $10^{-10}$            | Line-to-line coupling                   | 10                                       |

| $10^{-11}$            | Residual source/drain charge            | 5                                        |

Table 1.1 Order of magnitude variability time domains and estimated delay impact [15].

Variability in delays of CMOS clock circuits arises from the very large-scale integrated (VLSI) circuit technologies beyond the ability to control specific performance-dependent parameters [15]

The variability is one of the most urgent problems to overcome. Delay variabilities can be temporal and spatial in nature [16]. The term spatial variation refers to lateral and vertical differences from intended polygon dimensions and films thickness. Temporally, the variability can occur across nanoseconds (such as residual source/drain charge and line-to-line couple) to years (such as electro-migration and lithography node) [17]; these are shown in Table 1 [18].

Spatial variation modes exist between devices, between circuits, between chips and across wafers, lots, and the lifetime of any particular fabrication system. There are lots of methods to describe device variability; one useful approach is shown in Table 1.2. Variations are separated into rows according to spatial and temporal variation. Temporal, irreversible device variation contributors are associated with age and device wear-out.

For instance, atomistic dopant variation, line-edge roughness and film thickness variation are belonging to spatial and device-to-device variation. These above-mentioned variations are also part of intrinsic device variability. The intrinsic variations are caused by atom-level differences between devices that occur even though the devices may have identical layout geometry and environment. Even though there is no systematic process variation between MOSFETs, there is still a fair wide Gaussian distribution of threshold voltage [19].

Mostly temporal variations such as environmental operating temperature, activity factor (how often and how long the device is on), are belonging to extrinsic variation. Comparing with intrinsic variations, it is typically not associated with fundamental atomistic problems, but rather with the operating dynamics of a modern fabricator. The reversible terms can be recovered by changing the environmental condition or compensated with circuitries. Irreversible terms couldn't be recovered after occurring, but can be prevented by serval process modified way.

Furthermore, a VLSI circuit composes of numerous devices spatially distributed over a relatively small area of silicon. There circuits are typically connected to one or more power supplies via a network of wire referred to as the on-chip power grid. Temperature and power-supply variations has emerged as important sources of design components. Local temperature variations within the die that cause It is common to have power-supply variations create a 10% variation in delivered power to different parts of design, and that same 10% variation can in turn cause a similar amount of delay variation.

| Proximity                     | Spatial                                                | Temporal                                            |                                                                      |

|-------------------------------|--------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------|

|                               |                                                        | Reversible                                          | Irreversible                                                         |

| Variation of chip mean        | Parameter means $(L_{G}, V_{T}, t_{ox})$               | Environmental operating temperature Activity factor | Hot-electron effect<br>NBTI shift                                    |

| Within-chip<br>variation      | Pattern-density/<br>layout-induced<br>transconductance | On-die hot spots                                    | Hot-spot-enhanced NBTI                                               |

| Device-to-device<br>variation | Atomistic dopant<br>variation<br>Line-edge roughness   | SOI body history<br>Self heating                    | $\sigma_{\text{VT-NBTI}}$ (NBTI-induced $V_{\text{T}}$ distribution) |

|                               | Parameter std. dev.                                    |                                                     |                                                                      |

Temporal—dynamic, time-dependent delay variation

Pattern density—variation caused by variation in density of polygons in given area

Hot spots—regions of excessive local heating caused by high power dissipation density

Hot-spot-induced NBTI—Threshold variation caused by excessive local heating Self heating—Individual device heating caused by extended periods of high device current

Table 1.2 Categorization of device variations [15].

# 1.3.Analysis and Design of PVT Compensation for Clock System

According to section 1.1, process (including most spatial terms and  $\sigma VT$ -NBTI), voltage (including activity factor), and temperature (including environmental operating temperature, on-die hot spots, and so on) variation are the important factors of delays. For the clocking system, the delay of devices directly affects output frequency. Therefore, PVT variations can be detected by sensing and cataloging above variations, and compensated by circuit design and process modification.

The amount of PVT variations for the clock systems depend on the oscillator catalog. For instance, crystal oscillator (XO) are relatively high precise and resistant as PVT variations occurs. However, there are still necessary to improve PVT variation for much more highly precise applications. The temperature coefficient (TC) of XOs with PVT compensations can be lower than 5 ppm. However, the crystal (XTAL) is an off-chip component with high power consumption. Therefore, the crystal less clock generator (CLCG) are widely applied in the digital or RF circuits.

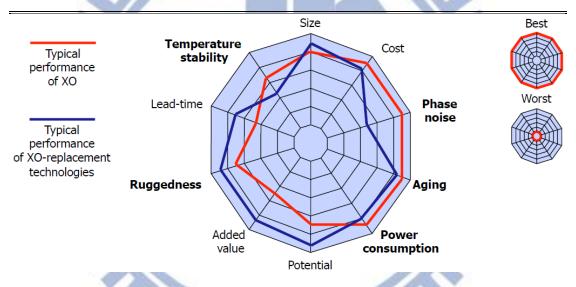

Figure 1.2 Block Diagram of XO systems.

Currently, crystal oscillators (XOs), micro electro mechanical systems (MEMS) oscillators and complementary metal-oxide-semiconductor (CMOS)-based oscillators are three main ways used to generate the reference clock signal. XOs provide highly precise and nearly temperature independent reference clock. However, the crystal

(XTAL) is an off-chip component with high power consumption. MEMS oscillators provide higher Q and better signal characteristic than CMOS-based oscillators, whereas need additional micro electro mechanical process to be integrated with traditional CMOS process [20].

MEMS oscillators provide higher Q and better signal characteristic than CMOS based oscillators, whereas need additional micro electro mechanical process to be integrated with traditional CMOS process. TC of MEMS oscillators are around 10 ppm where is between XOs and CMOS-based oscillators.

Furthermore, there are three kinds of CMOS based oscillators. The inductance-capacitor (LC) oscillators operate at high frequency [21]. The structure has high Q and low phase noise. It mostly targets at RF frequency synthesis. Relaxation oscillators repeatedly alternate between two states with a period that depend on the charging of a capacitor [22], [23]. Relaxation oscillators are also a stable LC based oscillator are with low phase noise [24]-[25]. All digital oscillator design can be integrated with digital signal processing (DSP) for portable and medical applications [26]-[28] Ring oscillators, Delay locked-loop (DLL), and phase locked-loop (PLL) are belonged to this catalog. Above these oscillators are with different circuit characteristics and PVT variations.

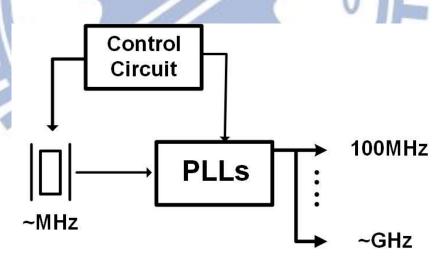

There are many PVT compensated methods for different oscillators and situations. The PVT compensated methods can be roughly divided into two parts, which are analog and digital. For example, figure 1.3 shows a traditional analog temperature compensated crystal oscillator (TCXO) structure [29]. It applies compensating circuits, such as thermistor or varactor diodes, to compensate the variations. Besides, the basic digital compensation circuits of TCXO. It applies a temperature sensor to detect the variation of temperature. Its results compare with coefficient table and compensate by logic and math function.

Figure 1.3 Block Diagram of Temperature [29].

Figure 1.4 Main IC Supplies of CLCGs [28].

## 1.4. Thesis Organization

This dissertation is composed of seven chapters. This dissertation (chapter  $2 \sim$  chapter 5) focuses on the clock generator with PVT compensation issues and the design of CLCG with auto-calibration under different situation.

This chapter provided an introduction on the challenges of the PVT variation of CMOS device and the relationship between devices and clock circuits. The catalogs of clock generators are described and the correspond PVT compensated method are also discussed in Chapter1

In Chapter 2, we discuss the operating principle of clock generators and accompanied noise. The basic noise of clock has been analyzed and their solutions. We will also discuss and analyze the characteristic of the conventional CLCGs and PVT compensated circuits. Lastly, the analysis and design issues of PVT compensated circuits for clocking circuits are presented.

In Chapter 3, One multi-phase crystal-less clock generator (MPCLCG) with a process-voltage-temperature (PVT) calibration circuit is proposed. It operates at 192 MHz with 8 phases outputs, and is implemented as a  $0.18 \, \mu m$  CMOS process for digital

power management systems. A temperature-calibrated circuit is proposed to align operational frequency under process and supply voltage variations. It occupies an area of 65µm ×75µm and consumes 1.1 mW with the power supply of 1.8 V. Temperature coefficient (TC) is 69.5 ppm/°C from 0 to 100°C, and 2-point calibration is applied to calibrate PVT variation.

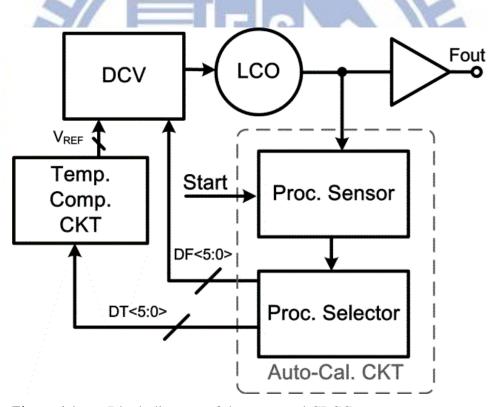

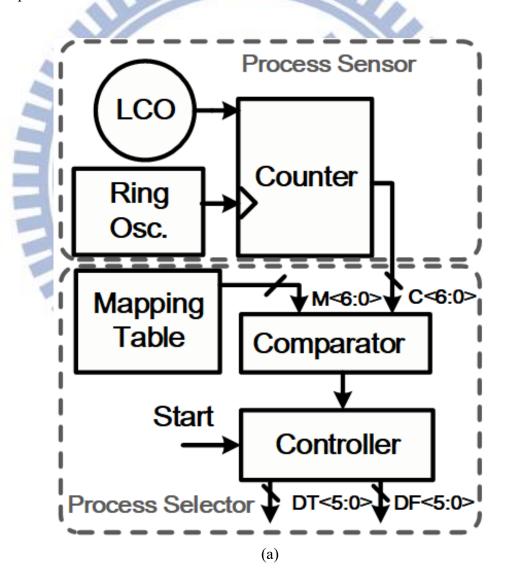

In Chapter 4, process and temperature variations on the clock generators has been studied. This paper presents an ultra-low voltage 2.4GHz CMOS voltage controlled oscillator with temperature and process compensation. A new all-digital auto compensated mechanism to reduce process and temperature variation without any laser trimming is proposed. With the compensated circuit, the VCO frequency-drift is 16.6 times the improvements of the uncompensated one as temperature changes. Furthermore, it also provides low jitter performance.

Chapter 5 summarizes the main results of this dissertation. Some suggestions for the future works are also addressed in this chapter.

Appendix A shows the electron distribution in an amorphous indium—gallium—zinc-oxide (a-IGZO) thin-film transistor (TFT) with a floating metal—semiconductor (MS) back interface is analyzed using a technology computer-aided design (TCAD) model. The channel geometry (i.e., length and thickness) effect is carefully investigated.

Appendix B shows a voltage reference circuits on poly-Silicon TFT. Because this paper is based on author's master thesis, detailed contents could refer the author's master thesis.

# Chapter 2. Basics of CLCGs and Their Corresponding PVT Compensated Circuit

The chapter introduces the fundamentals of CLCGs and their PVT compensated circuits. We will discuss and analyze the characteristic of the conventional CLCGs and PVT compensated circuits. Lastly, the analysis and design issues of PVT compensated circuits for clocking circuits are presented. The analysis results specify the research directions of the thesis.

# 2.1. Operation Principle of Crystal-less Clock Generators and the Accompanied Noise

## 2.1.1. Operational Principle of Crystal-less Clock Generators

Oscillators are fundamentally nonlinear, and oscillator's nonlinearity is the reason for their stable amplitude. However, linear models are still often used to describe oscillatory behavior. That is acceptable as oscillation start-up condition because oscillation at stat-up is a small signal. Fig. 2.1 shows the linear model of oscillator.

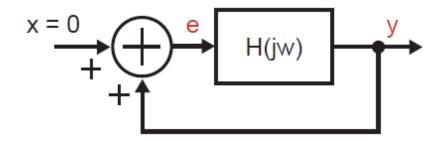

Figure 2.1 The block diagram of linear model for oscillator.

Where  $A(j\omega)$  is amplified gain and  $b(j\omega)$  is feedback network. Therefore, the closed loop gains  $G(j\omega)$  can be explained as

$$G(j\omega) = \frac{A(j\omega)}{1 - A(j\omega)\beta(j\omega)}$$

(2.1)

From the Barkhausen's stability criterion, the self-sustaining oscillation at frequency  $\omega_0$  if match the following conditions. The loop gain is equal to unity where  $|A(j\omega)\beta(j\omega)|=1$  and the phase shift around the loop is equal to  $\angle A(j\omega)\beta(j\omega)=2n\pi$ , where  $n\in 0,1,2,...$  The linear model can yield a start-up condition and provide a rough estimate frequency of oscillation. However, the periodically stable frequency could be far different from the small signal linear prediction. That is because that the output doubles as the input doubles in a linear system. In an oscillator, it leads to an amplitude that is arbitrary [30].

#### 2.1.2. Noise Analysis of Crystal-less Clock Generator

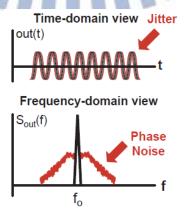

In the following section, we shortly discuss the noise from the crystal-less clock generators and analyze what kinds of noise we should handle. Fig. 2.2 shows the illustration of noise which occurs within time domain and frequency, respectively. Noticed that noise of amplitude variations suppressed by feedback in oscillator [31]. Jitter is the noise of the desired signal in time domain and phase noise is the same noise in frequency domain. The relationship between jitter at time-domain view and phase noise at frequency-domain view can be simply described. They are actually two sides of one; therefore, we discuss the jitter in theory and the main measured way of jitter are phase noise.

Figure 2.2 The block diagram of linear model for oscillator.

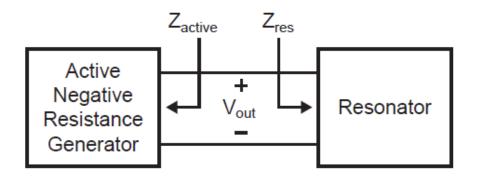

Figure 2.3 (a) The schematic diagram of CLCG. []

Fig. 2.3 (b) The noise and impedance schematic diagram of CLCG.

Fig. 2.3 (c) The noise and impedance schematic diagram of CLCG.

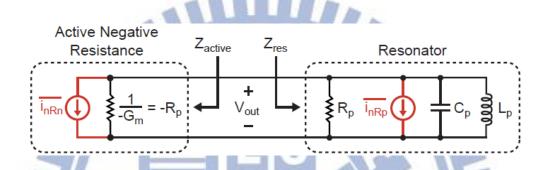

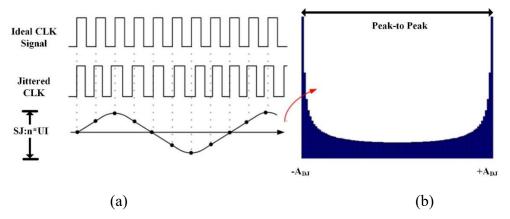

Fig. 2.3(a) shows the block diagram of a clock generator that includes an active negative resistance generator and a resonator. Fig. 2.3 (b) shows the impedance of active negative resistance and resonator. Where  $Z_{active}$  represents the active negative resistance and  $Z_{res}$  is the impendence of resonator. Then we split the noise source and ideal impedance in Fig. 2.3(c). Assume noise from active negative resistance element and tank are uncorrelated. Then, the expression represents total noise density that impacts both amplitude and phase of oscillator output are as below.

$$\frac{\overline{v_{out}^2}}{\Delta f} = \left(\frac{\overline{v_{nRp}^2}}{\Delta f} + \frac{\overline{v_{nRn}^2}}{\Delta f}\right) |Z_{tank}(\Delta f)|^2$$

$$= \frac{\overline{v_{out}^2}}{\Delta f} \left(1 + \frac{\overline{v_{nRn}^2}}{\Delta f} / \frac{\overline{v_{nRp}^2}}{\Delta f}\right) |Z_{tank}(\Delta f)|^2$$

(2.2)

Where is  $\frac{\overline{\iota_{nRp}^2}}{\Delta f}$  and  $\frac{\overline{\iota_{nRp}^2}}{\Delta f}$  are the density of white noise current for the resistance and resonator, separately.  $\frac{\overline{\iota_{nRp}^2}}{\Delta f} = 4kT\frac{1}{Rp}$  for single-sided spectrum. The tank impedance at a frequency  $\Delta f$  away from the resonance frequency ca be approximated by  $|Z_{tank}(\Delta f)|^2 \approx \left(\frac{R_p}{2Q}\frac{f_0}{\Delta f}\right)^2$  as Q is tank quality factor.  $\left(1+\frac{\overline{\iota_{nRn}^2}}{\Delta f}/\frac{\overline{\iota_{nRp}^2}}{\Delta f}\right) = F(\Delta f)$ . F( $\Delta f$ ) is called as noise factor and it is taken as a constant in this derivation process. Besides, the single side band noise to carrier ratio is been defined as the following equation.

$$L(\Delta f) = 10 \log \left( \frac{Spectral \ density \ of \ noise}{Power \ of \ carrier} \right)$$

(2.3)

Where spectral density of noise can be presented as  $S_{noise}(\Delta f) = \frac{1}{R_p} \frac{v_{out}^2}{\Delta f}$ . Therefore, eq. () can be rewritten as.

$$L(\Delta f) = 10 \log \left( \frac{S_{noise}(\Delta f)}{P_{sig}} \right) = 10 \log \left( \frac{2kTF(\Delta f)}{P_{sig}} \left( \frac{1}{2Q} \frac{f_o}{\Delta f} \right)^2 \right)$$

(2.4)

The above equation is the renowned Lesson's equation. Notice that only half of the noise is attributed to phase noise. This is due to a non-rigorous argument that the noise partitions to FM and AM noise and therefore only half of the noise contributes to the phase noise. The right hand side shows that the phase noise drops like  $1/f^2$ , an experimentally observed fact in a region of the spectrum. It's also clear that the Q factor is the key factor in determining the phase noise level.

However, the Lesson's equation is linear and time invariant. The more detailed insights into cyclostationary behavior, 1/f noise upconversion and impact of noise current modulation can be provided by Ali Hahimiri's thesis [32]. Besides, the related phase noise analysis can also refer Emad Hegazi and Jocob Rael's book [33].

Figure 2.4 The noise and impedance schematic diagram of CLCG.

The phase noise is measured by the spectrum analyzer, and the measurement are executed in the following chapter. Because the jitter noise and phase noise are two sides of one where mentioned above this section, the next paragraph we discuss the category of jitter noise and related measured method. We can be easy to distinguish which noise should be considered by analyzing the category of jitter noise.

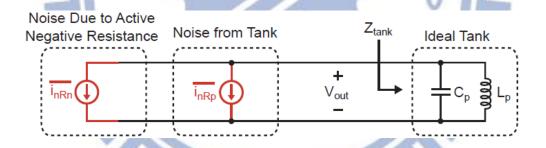

RJ is unbounded and there is a finite probability that random effects could cause a logic transition to appear anywhere, though, of course, the probability of an extremely large amount of RJ on a given transition is increasingly small. RJ usually belongs to Gaussian distribution or normal distribution. RJ is uncorrelated to the data. Besides, RJ is random in nature and does not occur with any predictable regularity.

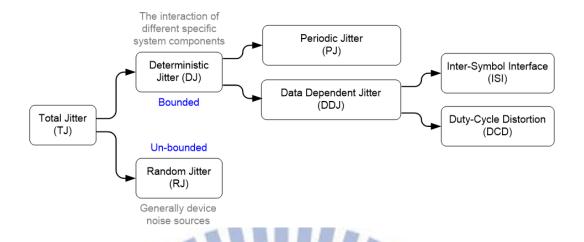

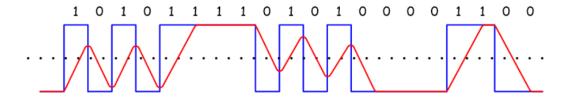

Fig. 2.4 shows the catalog of timing jitter noise. There are two major types of timing jitter, which are deterministic jitter (DJ) and random jitter (RJ). Deterministic jitter is defined as jitter that is bonded, with a well-defined minimum and maximum extent. There are a variety a deterministic data sources, mainly including periodic jitter (PJ) and data dependent jitter (DDJ). DDJ breaks down into the inter-symbol Interface (ISI) and duty-cycle distortion (DCD).

Figure 2.5 (a) Time domain of DJ and (b) related jitter histogram.

Fig. 2.4 (a) shows the jitter due to a purely periodic jitter aggressor that is a single sinsoid periodic jitter which is caused by clocks or other periodic sources. Fig. 2.4(b) is the jitter histogram of the DJ. PJ is ultimately an example of periodic phase modulation and may be the most useful category. When a PJ peak is identified it can usually be associated with a noisy circuit element operating at that same frequency. The classic example is power supply feed-through, but PJ can also be caused by crosstalk from neighboring data lines or any other type of Electromagnetic Interference (EMI).

Fig. 2.5(c) The noise and impedance schematic diagram of CLCG.

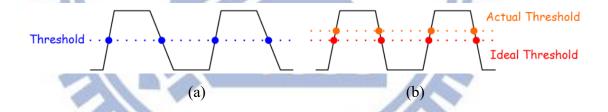

DDJ is correlated with the sequence of bits in the data stream. It most causes by the signal attenuation in the channel or non-linearity of circuitry. The typical example is inter-symbol Interface (ISI) and duty-cycle distortion (DCD). DDJ is a measure of asymmetry in the duty cycle of the transmitter. It can be classified by two main reasons. In Fig. 2.5(a), One is the mismatch between rising edge and falling edge caused by the charging rate or discharging rate which also means different slew rate (SR). Another is the drift of decision through which shown in Fig. 2.5(b). DCD most occurs in comparators or analog-to-digital converters (ADC).

Figure 2.6The noise and impedance schematic diagram of CLCG.

ISI is caused by a combination of the design of the trace and circuit geometry, the media composing both the conductor and dielectric of the circuit, and the waveform of the transmitted signal. The effects include skin effect, dielectric loss, reflect, cross talk, dispersion and limitation of system bandwidth and so on. Fig. 2.6 represents the variation of edge response in time domain.

DDJ usually adjust the quality of system transmission, especially in receiving end. The clock data recovery circuit (CDR) process data retimed in the receiving data. For the CLCG, RJ and PJ are what should be concentrated on, and the related measurement will be revealed at the following chapter. In chapter 1, we mention the PVT variations are great influence on CLCG, and we will also discuss the relationship between jitter (phase noise) and PVT variations.

## 2.2. Overview of CLCG with PVT Compensation

#### 2.2.1. CMOS-based Oscillators and Related PVT Compensation

CMOS-based oscillators are more and more attended due to the dimension and power consumption issues; although XOs and MEMS oscillators has much better stability than CMOS-based oscillators. In this section, three kinds of CMOS-based oscillators with their PVT compensation, which are mentioned in Section 1.3. would be discussed. Traditional CMOS-based oscillators have gradually been replaced by all digital for applications such as the internal control and the high-speed interfac. The low voltage, power and small area features of all digital CMOS-based oscillators bring enormous benefits. Relaxation oscillators repeatedly alternate between two states with

a period that depend on the charging of a capacitor. Inductance-capacitor (LC) oscillators operate at high frequency. The structure has high Q and low phase noise. It mostly targets at RF frequency synthesis.

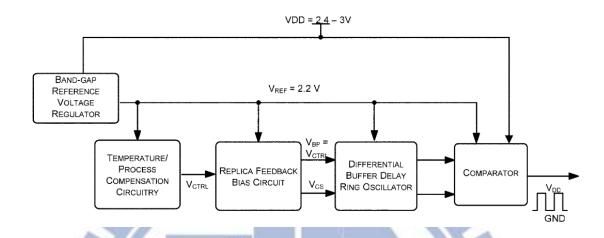

Fig. 2.7 The noise and impedance schematic diagram of CLCG [34].

Fig. 2.7 shows the block diagram of a previous traditional CMOS-based oscillator, which is based on a ring oscillator [34]. It contains a bandgap reference (BGR) voltage regulator, a temperature/process compensation circuitry, a differential buffer delay ring oscillator and a comparator. A bandgap referenced voltage regulator generates a supply and temperature independent reference voltage. It is primarily divided into two subcircuits: A bandgap reference with a stacked CMOS topology [35] and a feedback transconductance amplifier that raises the output of the bandgap circuit from 1.25 V to 2.2 V. This serves as a stable temperature independent supply voltage for the oscillator and the supporting circuits. The system uses a voltage controlled differential ring oscillator to generate a reference frequency.

In the frequency compensation circuit, a threshold voltage sensing circuit generates a process-dependent reference voltage from  $V_{REF}$ , which is supplied to the temperature compensating circuit. The output of the compensation circuit is a control voltage,  $V_{CTRL}$ , which stabilizes the frequency of oscillation by varying a reference current,  $I_{REF}$ . The output of the oscillator is converted to a full swing rail-to-rail clock signal by a process independent voltage comparator [36] to make it compatible with standard digital logic and increase noise immunity. The comparator also ensures that the clock duty cycle stays at 50%.

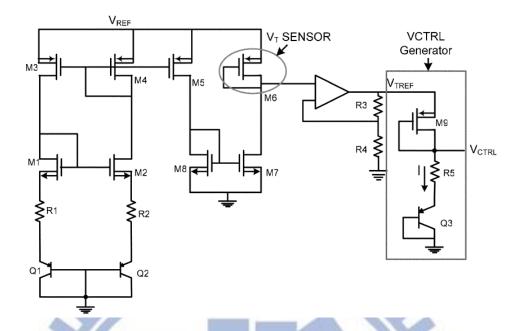

Fig. 2.8 Schematic of the basic temperature and process compensating bias generator [34].

Fig. 2.8 shows the schematic of the completely compensated circuits. The part of the circuit to the left is a self-biased reference circuit that provides a temperature independent current source, limited only by the matching of the resistors. The op-amp buffer stage boosts this reference level to (2.2 V under typical conditions) but is sensitive to the threshold voltage drift of M6.

The control voltage generator, VCTRL Generator, is implemented using a diode connected PNP transistor Q3 that provides a negative temperature coefficient. The temperature slope of can be adjusted through the ratio of M9. The temperature shift caused by the R3–R4 feedback in the amplifier is been ignored, since the effects cancel out to the first order. Therefore, the control voltage is been given by

$$V_{CTRL} = V_{TREF} - |V_{T9}| - \sqrt{\frac{2I}{\mu_p C_{ox}(W/L)_9}}$$

(2.5)

The temperature variation after compensation is down to  $\pm 0.84\%$ . The frequency stability is improved by more than 4.5 with the introduction of the compensation scheme. The average process variation within a single run at room temperature is  $\pm 1.1\%$  with compensation whereas it is almost  $\pm 8\%$  without it, a 7 X improvement.

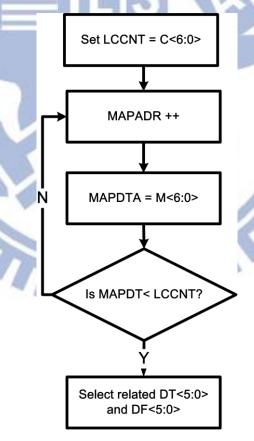

Fig. 2.9 Block diagram of all digital CLCG [26].

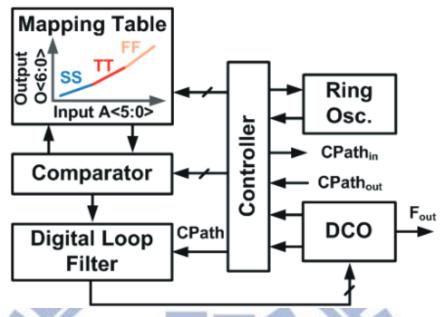

The all-digital CLCG uses frequency difference between the ring oscillator and the digital controlled oscillator (DCO) to create a mapping table under process and temperature variations [26]. The digital loop filter (DLF) adopts a successive-approximation register (SAR) algorithm for fast locking time. Fig. 2.9 shows the block diagram of the all-digital CLCG. It consists of a comparator, controller, a ring oscillator, a mapping table, a 9-bit digital loop filter (DLF), and a 9-bit digital controlled oscillator (DCO). The mapping table is based on process and temperature variations. In the mapping table detection (MTD), the frequency difference between the ring oscillator and the digital controlled oscillator (DCO).

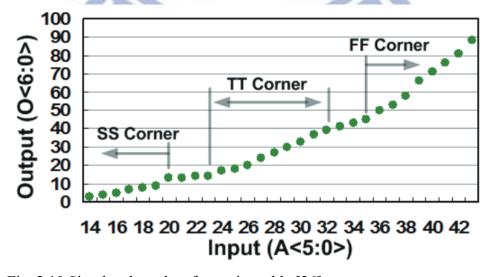

Fig. 2.10 Simulated results of mapping table [26].

The locking acquisition mechanism can be theoretically considered as a sequence of four operations:

- 1. Initialization: After Start goes high, outputs of the registers must be set or reset. The frequency difference between the ring oscillator and DCO frequency is decided.

- 2. Mapping table detection: When the initialization is completed, the frequency difference between the ring oscillator and DCO frequency can find a mapping value in the mapping table. The simulated results of mapping table is shown in Fig. 2.10. Thus, the process and temperature of this chip can be defined.

- 3. After completing mapping table detection, the DLF get the mapping value from the table and then the DLF uses the mapping value to achieve the target frequency of DCO. Therefore, the DCO output follows the DLF algorithm, which clock period is eight times as much as DCO output period.

- 4. Fine tuning track: Suppose the process and temperature variations affect the DCO operational frequency. At the fine-tuning stage, the CLCG can tune output frequency to reduce the process and temperature effects. The mechanism maintains that the function of the DSP system can work under the operational frequency of the CLCG. The CLCG was implemented in a one-poly nine-metal (1P9M) 65 nm CMOS process with power consumption smaller than 5  $\mu$ W measured at 0.3 V. The locked frequency is 12 MHz, as well as the frequency draft is less than  $\pm 4.3\%$  under the temperature from 0 to 100°C.

#### 2.2.2. Relaxation Oscillators and Related PVT Compensation

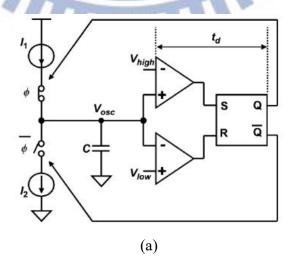

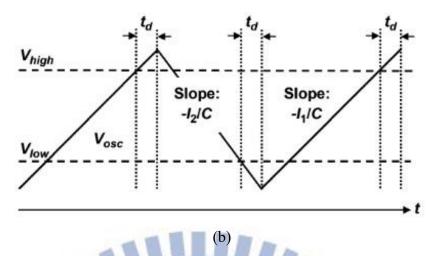

Fig. 2.11 (a) Conventtional RC oscillator (b) Waveform

Fig. 2.11 illustrates a commonly known conventional relaxation oscillator [23].

Oscillation is performed by iteration of charging and discharging the capacitor as follows:

- 1) The voltage  $V_{osc}$  rises while charging C by  $I_I$ .

- 2) If  $V_{OSC} > V_{high}$ , a comparator sets RS-FF and changes the state of oscillator into discharging phase.

- 3)  $V_{OSC}$  falls while discharging C by  $I_2$ .

- 4) If  $V_{OSC} \le V_{low}$ , another comparator resets RS-FF and the state returns to charging phase. The issues of this oscillator are as follows:

First, variation of comparator's delay  $t_d$  results in frequency variation with voltage and temperature. Second, aging of current sources  $(I_1, I_2)$  will degrade the accuracy of the slope of and varies frequency. Third, flicker noise of current sources  $(I_1, I_2)$  will degrade low offset-frequency phase noise or accumulated jitter.

A simple solution to obtain a stable and accurate oscillation is to shorten  $t_d$  to be neglected; however, this approach needs huge power to comparators so that it does not match with our motivation for low power dissipation. Therefore, the authors propose a feedback concept called voltage averaging feedback (VAF) to achieve both accuracy and low power dissipation by maintaining whole oscillation waveform

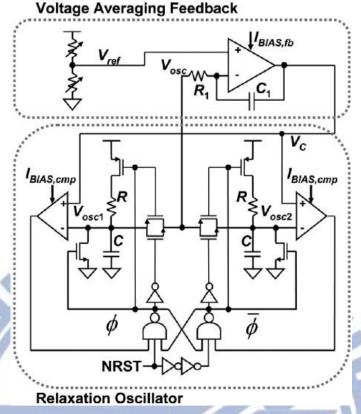

Fig.2.12 Voltage averaging feedback concept [23]

Fig. 2.12 shows the concept that comprises a complementary relaxation oscillator and an active filter for VAF, where the same complementary design is chosen for comparators and a feedback amplifier for rail-to-rail input and lass to obtain enough phase margin. The relaxation oscillator part is considered as a voltage-controlled oscillator with a control signal  $V_C$ . Oscillation waveforms  $V_{OSC1}$  and  $V_{OSC2}$  are summed up to and transferred to the active filter part.

By the measurement varying temperature at  $V_{DD} = 1.8$  V and bias for comparator  $I_{BLAS,cmp} = 1 \mu A$ , the oscillation without VAF resulted in a large variation of  $\pm 2.67\%$  because of comparators' delay. On the other hand, the oscillation with VAF achieved  $\pm 0.75\%$ . Because temperature characteristic is mainly dominated by R, not comparators. Frequency variation reduced from 0.75% to 0.19% by blending diffused and polysilicon resistors with different sensitivities to temperature.

#### 2.2.3. LC Oscillators and Related PVT Compensation

Fig. 2.13 800 MHz LC oscillator with PVT compensation [37].

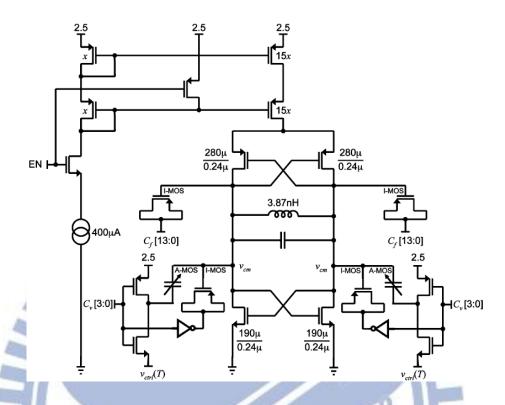

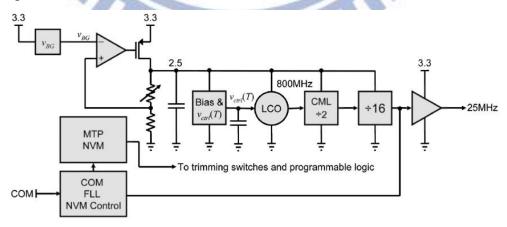

The LC oscillator is shown in Fig. 2.13, where the topology is cross-coupled and complementary [37]. The target center frequency is 800 MHz, thus enabling division by 32 to generate 25 MHz, which is a typical reference frequency for Ethernet and similar protocols.

Fig. 2.14 Chip architecture of the whole circuitry.

The chip architecture is shown in Fig. 14. A bandgap-referenced and load-compensated low drop-out (LDO) regulator steps 3.3 V to the 2.5-V core voltage.

Trimming coefficients for the LDO, bias currents and the fixed and variable capacitors are stored in an 88-b multi-time programmable (MTP) NVM. Custom logic was synthesized to support the NVM interface, a simple serial communication interface, and a digital frequency-locked loop (FLL) for automatic nominal frequency calibration.

The FLL implementation has been demonstrated in [38]. The FLL determines the trimming coefficient for the I-MOS capacitor array that centers the LCO frequency by counting deep races between the LCO and a precision off-chip oven-controlled crystal oscillator (OCXO) such that the frequency discrepancy can be resolved. Once the FLL converges (typically within 100 ms), the coefficient is stored in NVM, loaded upon power-on reset thereafter, and the reference signal is never again required. The TC for  $3.3V\pm10\%$  and -10 to  $80^{\circ}$ C is  $\pm152$  ppm.

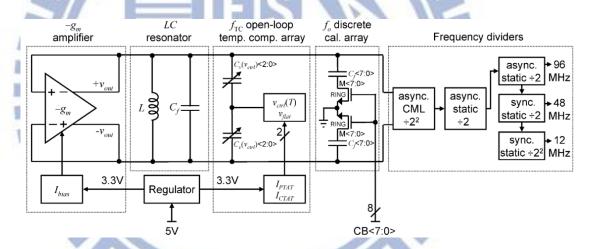

Fig. 2.15 The USB 2.0 compliant RF-TCHO clock generator architecture [23]

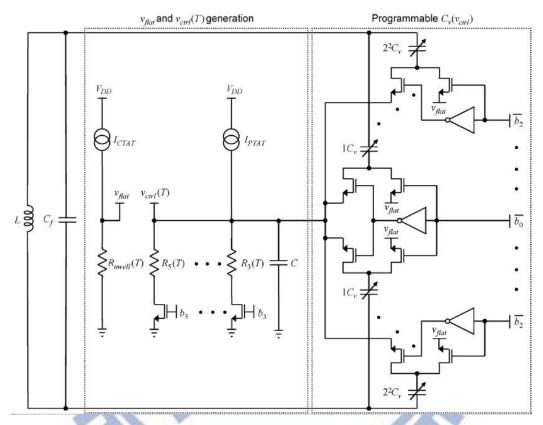

The prior art shown in Fig. 2.15 is a monolithic and self-referenced RF temperature compensated LC VCO [23], as each functional block is shown in simplified form as a module. A temperature and supply-independent current reference,  $I_{bias}$ , biases the -gm amplifier and maintains constant harmonic content in the LC network, thus minimizing bias-induced frequency drift. Temperature compensation is achieved open-loop with a reactive compensation method using a programmable array of accumulation-mode MOS (A-MOS) varactors that are biased by either a temperature-dependent voltage  $V_{ctrl}(T)$ , or by a temperature-independent voltage  $V_{flat}$ , both of which are derived from temperature-dependent current sources,  $I_{PTAT}$  and  $I_{CTAT}$ , along with resistors. The

uncompensated  $f_{TC}$  is expected to be negative due to the coil loss  $R_L$ . Consequently,  $V_{ctrl}$  (T) must increase over temperature to reduce the net tank capacitance and maintain the self-oscillation frequency. To account for process variation, programmable discrete frequency calibration was implemented as a switched-capacitor array with polyinsulator-poly (PiP) capacitors and nMOS switches.

Fig. 2.16 Programmable binary-weighted array for discrete and monotonic self-oscillation frequency calibrations.

The open-loop reactive temperature compensation circuitry is shown in Fig. 2.16. The PTAT current  $I_{PTAT}$  is driven into one of three selectable resistor banks, all of the same magnitude, but of differing TCs depending on the type of resistors in the bank. The programmable resistor bank includes n-well, n-diffusion and poly-Si resistors, which exhibit positive TCs with decreasing magnitude, respectively. The PTAT voltage  $V_{ctrl}(T)$  is filtered across a large PiP capacitor C and sets the backgate voltage on a programmable array of A-MOS varactors. Three binary-weighted programmable varactor states exist. When a bit is set, the back-gate of the corresponding varactor is connected to  $V_{ctrl}(T)$  and when it is cleared, the backgate is connected to the

temperature-independent voltage  $V_{flat}$ , which is derived by sinking  $I_{CTAT}$  into an n-well resistor with a high positive TC. The array allows the oscillation frequency to remain constant, but the ratio of the temperature-dependent to temperature-independent capacitance to be programmed, thus modifying  $f_{TC}$ . Six bits program the open-loop TC circuitry, three of which control the resistor bank and three of which select the size of the A-MOS varactor. These bits are determined post-fabrication via a one-time full temperature characterization effort, stored in NVM for all devices, and loaded thereafter upon power-on rest. TC trimming for each device is not required. Results reported subsequently utilized the state where the net resistor included 80% n-diffusion and 20% unsalicided poly-Si resistors. The TC is +8.1ppm/ $^{\circ}$ C.

# 2.2.4. Micro Electro Mechanical Systems and their PVT Compensation

Since the crystal is off- chip component with high power consumption, crystalless clock generators have become widely applied for RF or VLSI circuits. Micro electro mechanical systems (MEMS) oscillators and CMOS-based oscillators that are mentioned at 2.2.1 are widely applied ways used to generate the reference clock signal.

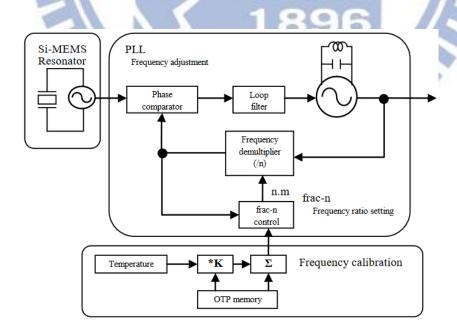

Fig. 2.17 The structure of MEM oscillator with temperature compensation [39].

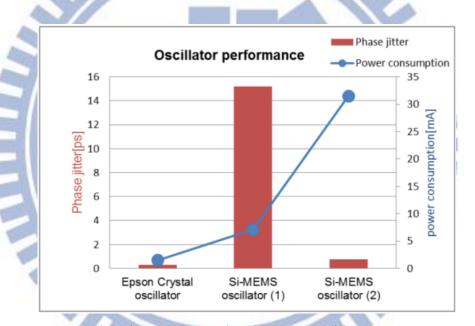

A MEMS oscillator uses a silicon resonator as the oscillating source and requires a PLL circuit to correct the frequency for manufacturing tolerances and temperature coefficient. The basic structure of these oscillators is given in Figure 2.17. Like other CMOS oscillators, MEMS oscillators have a complex structure consisting of a resonator, a fractional-n PLL, and temperature compensation and manufacturing calibration. MEMS oscillators provide higher Q and better signal characteristic than CMOS-based oscillators, whereas need additional micro electro mechanical process to be integrated with traditional CMOS process [39]. Figure 2.18 shows the comparison of MEMS oscillator and XO. We can obviously find out that MEMS has a high jitter and high power consumption. No matter improving the jitter performance or reducing the power consumption, the performance of XOs are better than MEMS oscillators [40].

Fig. 2.18 Comparison between crystal and MEMS oscillator [40].

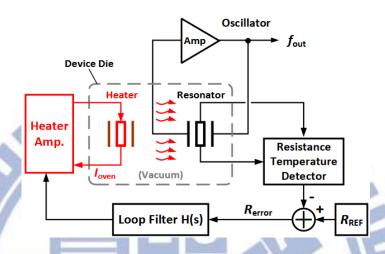

Figure 2.19 shows a novel conventional temperature compensated MEMS oscillators [41]. It consists of a main oscillator, a resistance temperature detector (RTD), a low-pass loop filter H(s), and a heater amplifier for the micro-oven. Two identical resonators are located next to each other on the same die. One is the oscillator and the other one serves as the micro-oven (with voltage applied across its body). The RTD circuit extracts the resonator temperature information – structural resistance, compare it with a reference resistor ( $R_{REF}$ ) and then generates a resistance error signal to the low-pass loop filter H(s). The main objective of loop filter is to provide a high gain so as to

suppress the resistance error and minimize the micro-oven temperature drift. The micro-oven adjacent to the main resonator is controlled by this feedback loop automatically and hence achieves an active temperature compensation. Without compensation, the overall frequency drift is about 2000 ppm. After applying proposed temperature compensation scheme, the frequency drift is greatly reduced to  $\pm 5.5$  ppm.

Fig. 2.19 Comparison between crystal and MEMS oscillator [41].

Although MEMS oscillators provide higher Q, better TC (about 10ppm through 70 degree), and better signal characteristic than CMOS-based oscillators, MEMS oscillators need additional micro electro mechanical process to be integrated with traditional CMOS process.

# Chapter 3. An 8 phases 192 MHz Crystal-less Clock Generator with PVT Calibration

This Chapter is briefly depicted an 8 phases 192 MHz crystal-less clock generator with PVT calibration in a 0.18 mm CMOS process. The proposed design architecture offers benefits. First, the PVT calibrated CLCG architecture can compensate the process, voltage, and temperature variations. Whether the clock system is positive or negative TC, the calibrated mechanism can make sure that the clock system can be compensated under various situations. Second, a voltage controlled oscillator and a phase error corrector can stabilize the 8 phases' outputs under diversified situation. Third, this design applies a level shift instead of tap buffers to amplify the output swing; therefore, it can guaranteed full swing outputs. Final, the dimension of our proposed design are so small that can be widely applied in VLSI circuitry.

## 3.1. Architecture of CLCG with PVT compensation Circuit

Figure 3.1 Block diagram of the proposed CLCG.

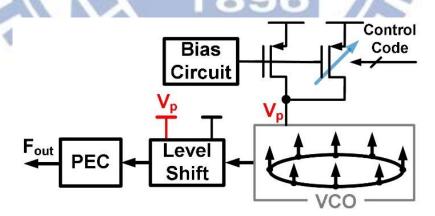

Fig. 3.1 shows the structure of the proposed multi-phase PVT calibrated CLCG. It includes a ring oscillator, a phase error corrector (PEC), a level shifter and a bias circuit.

The bias circuit consists of current source and a PVT calibrated circuit. The PVT calibrated circuit effectively improve the resistance of PVT variation. The PEC circuit reduces phase error, which mainly occurs at the mismatch of each phase. The level shifter amplifies the output swing to ensure full swing outputs.

## 3.1.1. Crystal-less Clock Generator and Phase Error Corrector Circuit

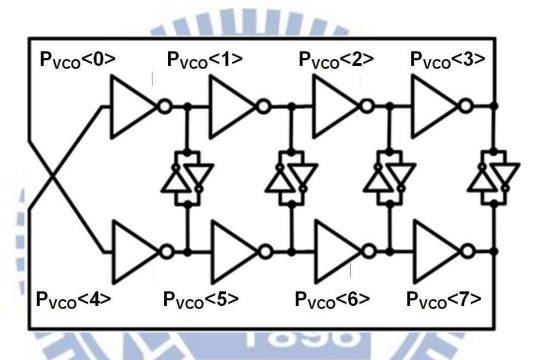

Figure 3.2 Schematic of the 8 phases differential ring oscillator.

The schematic of the applied voltage controlled oscillator (VCO) is illustrated in Fig. 3.2. This structure applies The VCO adopts 4 stages differential cell with 8 phases outputs. The delay cells are differential cell, and detailed schematic is shown as below. The latches are weak inverters, which can keep P<0> and P<4> truly inverted and reduce the mismatch from the multi-phase delay. The advantage of differential ring cell is it can provide even phase outputs symmetrically. Comparing to traditional ring oscillators, the differential ring oscillators can realize even outputs. The docking inverter pairs, which connect Pvco <1> and Pvco <5>, can effectively balance the phase-to-phase error.

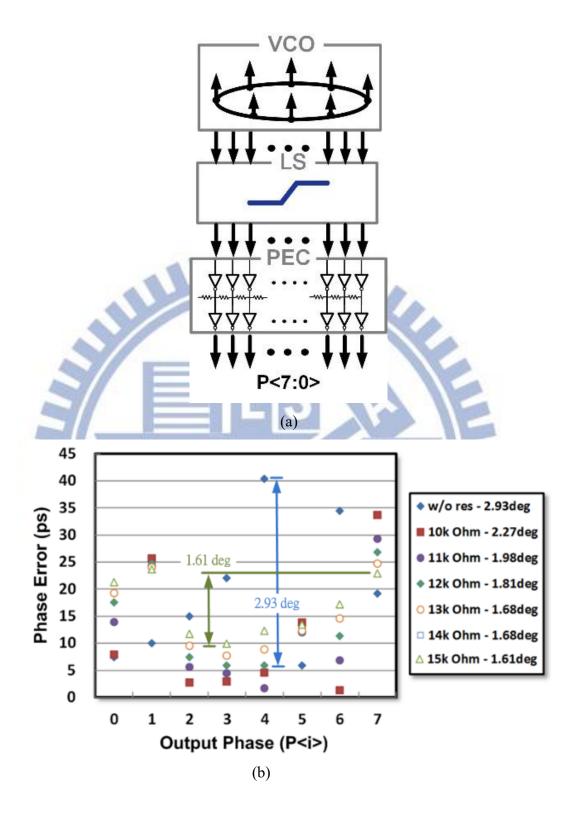

Figure 3.3 (a) Block diagram of the VCO, LS, and PEC, and (b) simulated result between output phase and phase error.

Fig. 3.3 illustrates the circuit of VCO with a phase error correct (PEC) circuit. The

phase error mainly occurs at the mismatch of each phase. The circuit routing of the ring oscillator and process variation are the major reasons. The PEC circuit applies resistors between each phase to balance the mismatch. Fig. 3.3(b) shows the relationship between output phase and phase error. The phase error without PEC circuit is 40.5 ps (2.93°) at P<4>. The PEC circuit adopts 15k Ohm to achieve the minimum phase error, which is 1.61°. Thus, the PEC can reduce the 45% phase error [42].

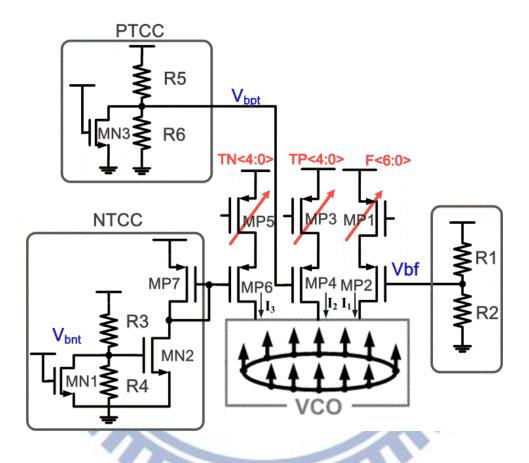

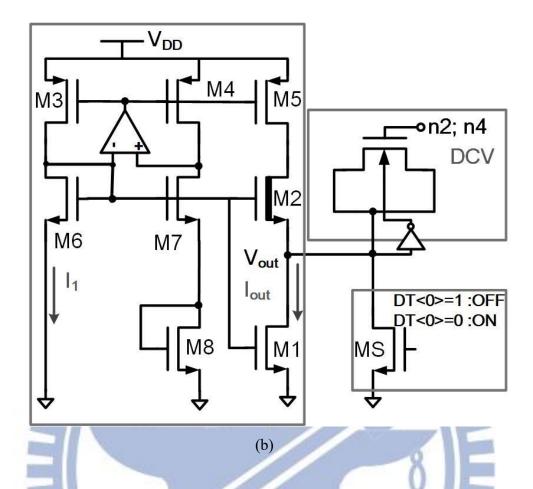

Figure 3.4 Block diagram of the PVT calibrated circuit.

#### 3.1.2. PVT Calibrated Circuit

The modified PVT calibrated CLCG architecture is demonstrated in Fig. 3.4. The calibrated circuits calibrate the variation by digital controlling bias circuit. There are three PVT calibrated mechanisms for CLCG. The digital code, F<6:0>, can calibrate the process and frequency variations. The digital code, TP<4:0>, can calibrate the positive temperature variation and the digital code, TN<4:0>, modifies the negative

temperature variation. The frequency calibration consists of MP1, MP2, R1, and R2. F<6:0> can control the current  $I_1$ , which can modify the VCO frequency. R1, R2, and MP2 are the bias circuit. The bias voltage  $V_{bf}$  is as follow.

$$V_{bf} = V_{DD} - (V_{SD(MP1)} + V_{SG(MP2)}) = \frac{R_2}{R_1 + R_2} V_{DD}$$

(1)

where  $V_{SD}(MP1)$  and  $V_{SG}(MP2)$  are the source-to-drain voltage of MP1 and the source-to-gate voltage of MP2, respectively. The voltage division of resistance has to keep MP2 operate at the saturation region.

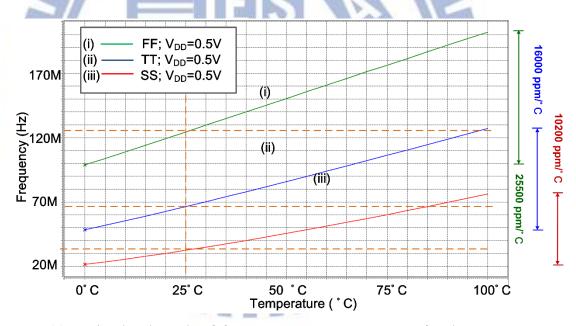

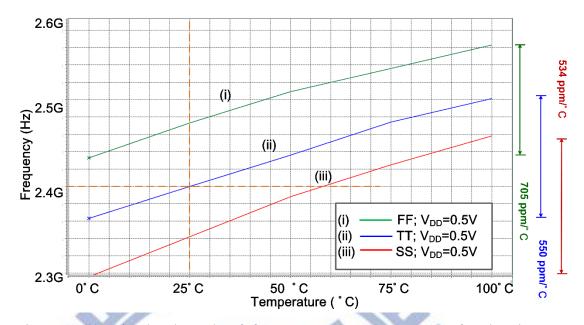

Figure 3.5 Simulated frequency versus temperature for the proposed DCO without temperature calibration.

Simulated frequency versus temperature for the CLCG without temperature calibrations is shown in Fig. 5. Temperature coefficients (TC) are -350, -505, and -901 ppm/°C of slow-slow (SS), typical-typical (TT) and fast-fast (FF) corners, respectively. The TC of CLCG are all negative temperature coefficients. The negative temperature coefficient calibration (NTCC) circuit calibrates negative TC. MP5, MP6, MP7, MN2, MN3, R5, and R6 consist of the NTCC. TN<4:0> can control the current I<sub>3</sub>, which can modify the VCO frequency. MP6 and MP7 can transfer the calibrated current to I3.

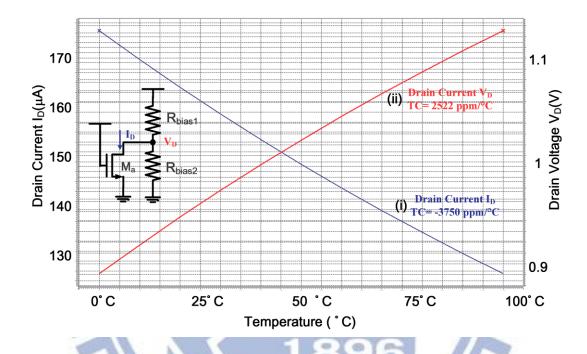

The simulated results of the temperature calibration part are shown in Fig. 3.6. The temperature calibration circuit consists one transistor Ma and two bias resistors Rbias1

and Rbias2. The MOSFET drain current ID is expressed as

$$I_D \propto \mu(T)(V_{DD} - V_{TH}(T))^{\alpha} \tag{2}$$

The threshold voltage  $V_{TH}(T)$  and mobility  $\mu(T)$  have temperature dependence [43], [44] as follows.

$$V_{TH}(T) = V_{TH}(T_0) - k(T - T_0)$$

(3)

$$\mu(T) = \mu(T_0) \left(\frac{T}{T_0}\right)^{-m} \tag{4}$$

Figure 3.6 Simulated drain current  $I_D$  and drain voltage  $V_D$  versus temperature for the temperature calibration part.

where T is the present temperature and  $T_0$  is the room temperature ( $T_0$ =300K).  $\alpha$  typical assumes 2. k is the threshold voltage temperature coefficient whose typical value is 2.5mV/K. m is mobility temperature exponent whose typical value is about 1.5~2. Both  $\mu$  and  $V_{TH}$  are negative temperature coefficient. The effect of drain current by  $\mu$  is much higher than that by  $V_{TH}$  as  $V_{DD}$  and  $V_{TH}(T)$  are relatively large, such as  $V_{DD}$ =1.8V and  $V_{TH}$  =0.7V [45]. Fig. 7 shows the same trend of drain current versus temperature where drain current is negative TC = -3750 ppm/°C. On the contrary, the effect of drain current by  $V_{TH}$  is higher than that by  $\mu$  as  $V_{DD}$  and  $V_{TH}(T)$  are relatively small, such as  $V_{DD}$ < 1V and  $V_{TH}$ =0.7V

The NTCC circuit consists of the temperature calibration part and a pair of current mirror. The temperature part includes R5, R6, and MN2. It produces the positive TC bias voltage V<sub>bnt</sub>. V<sub>bnt</sub> controls the drain current of MN2, I<sub>D(MN2)</sub>. As V<sub>bnt</sub> increases with temperature, I<sub>D(MN2)</sub> increases with temperature. With MP6 and MP7, I<sub>3</sub> is approximately proportional to absolute temperature (PTAT). Therefore, the output frequency can be pulled up with temperature by bias current I<sub>3</sub>. The PTAT current modifies a negative temperature coefficient via digital code, TN<4:0>.

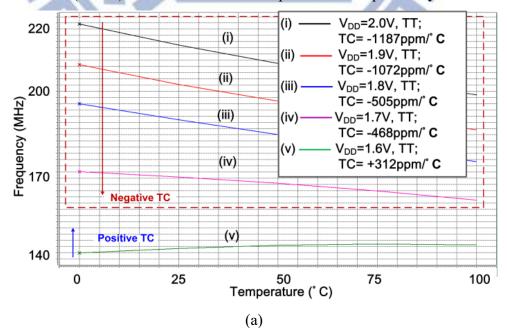

Fig. 3.7(a) is the simulation results of the frequency accuracy of CLCG under TT corner with supply voltage variation. TC are 312, -468, -505, -1072, and -1187 ppm/ $^{\circ}$ C of  $V_{DD}$  =1.6 V, 1.7 V, 1.8 V, 1.9 V, and 2.0 V. However, TC turns to the positive temperature coefficient as reducing the supply voltage of 1.6 V. As the MOS device has a large current, the CLCG can obtain a negative temperature coefficient easily.

When process corner and supply voltage variations (SS corner and low supply voltage), the CLCG becomes a positive temperature coefficient. For example, Fig. 3.7(b) shows the simulation results of the frequency accuracy of CLCG under SS corner. The TCs with V<sub>DD</sub>=1.6 V and V<sub>DD</sub>=1.7 V become positive temperature coefficients. It leads that the negative temperature calibrated circuit can't be applied under low voltage supplies. The main reason is that the additional bias circuit reduces the head room of the VCO. Applying long channel length devices of the oscillator keeps TC staying in a negative temperature coefficient. Besides, introducing the positive temperature calibrated circuit (PTCC) is the low cost and low power consumption way.

Figure 3.7 Simulated frequency versus temperature for the proposed VCO under(a)typical-typical and (b)slow-slow corner with supply voltage variation.

MP3, MP4, MN1, R3, and R4 consist of the positive temperature calibration, which is the same as Fig.6. TP<4:0> can control the current  $I_2$ , which can modify the frequency. As  $V_{bpt}$  increases with temperature,  $I_2=I_{D(mp4)}$  decreases. Therefore,  $I_2$  is complementary to absolute temperature (CTAT). The CTAT current modifies the positive temperature variation by digital code, TP<4:0>.

## 3.1.3. Level Shifter

Buffers are widely applied to amplify the digital signals. As the operating voltage increases to a high voltage, the output signal couldn't be properly amplified to full swing or even turn off to zero. The schematic of level shifter is shown in Fig. 3.8. The level shifter amplifies the output swing to ensure full swing outputs. The output signal of VCO provides low voltage supply ( $V_{DDL}$ ) input signal ( $P_{VCO}$ <i>) to level shifter. The function of two NMOS devices with gate connection to  $P_{VCO}$ < i > and  $P_{VCO}$ < i > is speed up the transition and avoid glitch during the transition. For example, as

Pvco<i>>=0 and bar Pvco<i>>=1, Gate of MP1=0 and MP1 is tuned on. MN3 also is tuned on to provide additional current. Fig. 3.9 shows the simulation with and without the two NMOS devices. It apparently finds that there are glitches which slow down the transition. The input signal which is low voltage level ensures that the CLCG could produce high voltage level output signal  $P_{LS}<$ i> under a low voltage supply. Furthermore, the power consumption of level shifter is lower than traditional buffers [46].

Figure 3.9 Simulation result of level shifter (a) without (b) with two NMOS devices.

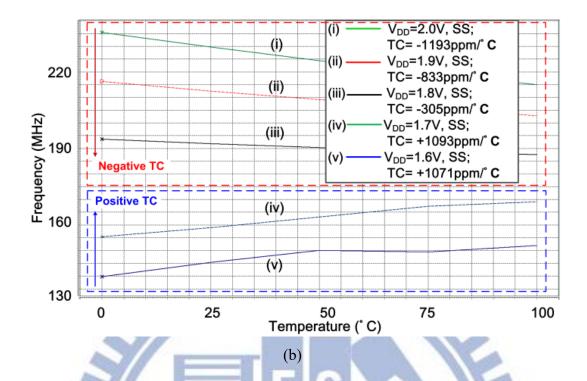

#### 3.2. Stability of Temperature Compensation Circuit

Fig. 8 shows the simulation result after temperature calibration. Temperature coefficients (TC) are 83, 62.5, and 46.9 ppm/°C of SS, TT and FF corners, respectively. TC at VDD = 1.6V is 119 ppm/°C of TT corner. The compensated curve of negative TC is concave, and the compensated curve of positive TC is convex on the contrary.

The frequency resolution of F<6:0> is  $\frac{\text{Tuning Range}}{2^N} = \frac{128\text{MHz}}{2^7} = 1MHz$ . Where N is digital code counts. Besides, the frequency resolution of TP<4:0> is  $\frac{\text{Tuning Range}}{2^N} = \frac{16\text{MHz}}{2^5} = 500 \text{ kHz}$ . Tuning step of TP<4:0> is 32.5 ppm/°C. The frequency resolution of TN<4:0> and TP<4:0> are 500 kHz.

Figure 3.10 Simulation results of frequency versus temperature for the proposed CLCG after calibration.

## 3.3. Experiment Results

In this chapter, we deal with the testing flowchart, including the environment setup and PVT compensation step. Beginning with the measured environment setup and experiment results of the proposed PVT compensation circuit, we present the measured results of the calibration mode and measurement mode. We also analyze and summarize the measured duty cycle error and phase-to-phase error on the proposed circuit.

#### 3.3.1. *Concept*

Compensation flow shows in Section 3.3.4 and related results show in Fig. 3.15. Temperature coefficient (TC) is 69.5 ppm/°C from 0 to 100°C, and 2-point calibration is applied to calibrate PVT variation. Phase to phase errors and duty cycle errors are less than 5.5% and 4.3%, respectively.

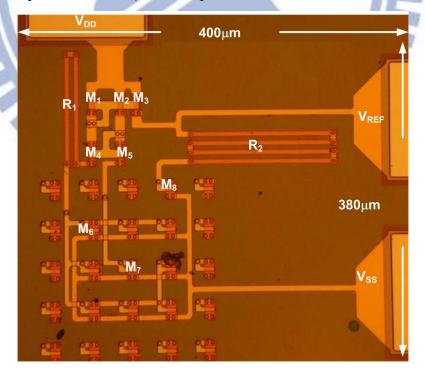

Figure 3.11 (a) Die photograph of the proposed circuit, and (b) block of output stage.

The proposed clock generator has been fabricated in a 0.18  $\mu$ m GP (general-purpose) CMOS process without specialized analog process options. Die photograph is shown in Fig. 3.11(a). The core dimension, which includes multiplexer (MUX) and output buffers, is 65  $\mu$ m x 145  $\mu$ m. The MUX and output buffers are used to measure the information of each phase output signal. Therefore, the CLCG core area is 65  $\mu$ m x 75  $\mu$ m.

In Fig. 3.11(b), the block of output stage for measuring phase to phase errors and duty cycle errors is illustrated. The output stage includes MUX and output buffers. The MUX is applied to select phases and phase to phase errors can be measured by selecting

two adjacent phases. The MUX is also capable to produce additional jitter each output phase. The output buffer includes tap buffers and resistances. The total power consumption is 1.1 mW at 1.8 V.

#### 3.3.2. Environment Setup

Figure 3.12 Measurement setup.

Fig. 3.12 shows the measurement environment. Temperature measurements were performed in a programmable thermal chamber. Frequency drift was measured with a real-time oscilloscope (Agilent 81204B).

#### 3.3.3. Jitter and Phase Noise Performance

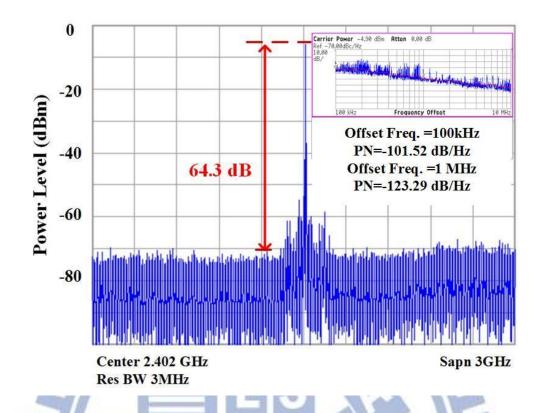

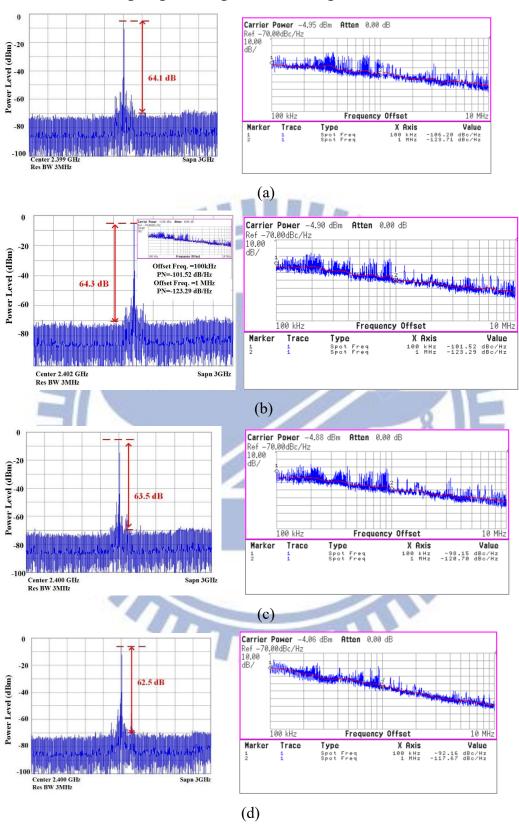

Fig. 3.13 represents the operating frequencies of CLCG at 20°C and the jitter histogram at 1.8 V. The CLCG output demonstrates a 4.58-ps RMS jitter and a 34.55-ps peak-to-peak jitter (P2P jitter) at 192MHz within 12.67k hits. The RMS and P2P period jitters are less than 0.088% and 0.665%, respectively. Fig. 3.14 shows the output spectrum of the VCO with a supply voltage of 1.8 V, and the phase noise of output

signal. As shown in Fig. 14, the phase noise is -102.03 dBc/Hz @ 1 MHz offset and -124.24 dBc/Hz @ 10 MHz.

Figure 3.13 Jitter performance where RMS=4.58ps and P2P=34.55ps of 192 MHz output at 1.8V.

Figure 3.14 Measured output spectrum and phase noise of 192MHz output of the VCO with a supply voltage of 1.8 V.

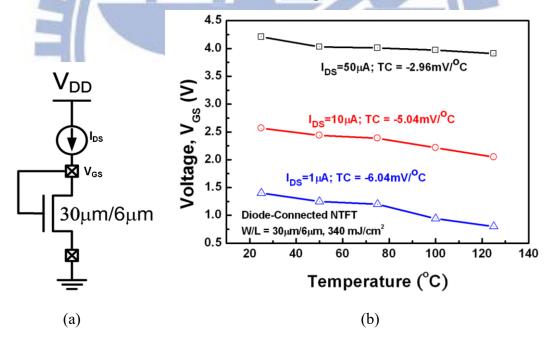

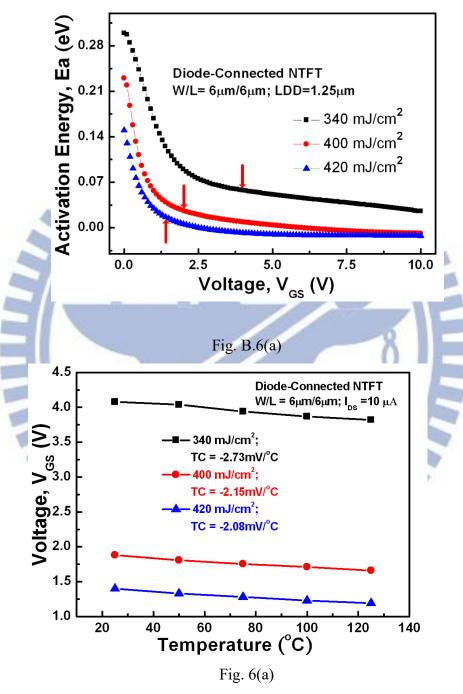

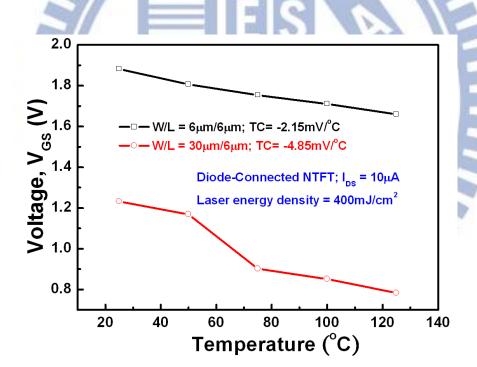

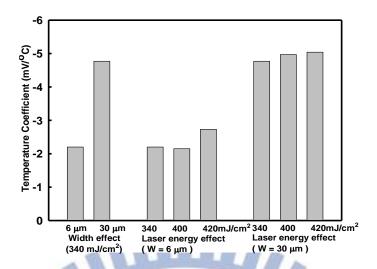

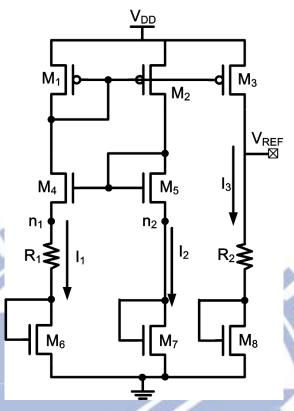

#### 3.3.4. Measurement of Temperature Compensation