# 國立交通大學

電子工程學系 電子研究所碩士班

碩士論文

佈局最佳化的低壓元件堆疊來達成高壓積體電路之靜電放電防護設計

Optimization of Stacked Low-Voltage PMOS for High-Voltage ESD Protection with Layout Consideration

研究生: 廖顯峰 (Seian-Feng Liao)

指導教授: 柯明道教授 (Prof. Ming-Dou Ker)

中華民國一〇四年九月

# 佈局最佳化的低壓元件堆疊來達成高壓積體電路之靜電放電防護設計

# Optimization of Stacked Low-Voltage PMOS for

### **High-Voltage ESD Protection with Layout Consideration**

研究生: 廖顯峰 Student: Seian-Feng Liao

指導教授: 柯明道教授 Advisor: Prof. Ming-Dou Ker

#### 國立交通大學

電子工程學系 電子研究所

碩士論文

#### A Thesis

Submitted to Department of Electronics Engineering and Institute of Electronics College of Electrical and Computer Engineering

> National Chiao Tung University in Partial Fulfillment of the Requirements for the Degree of Master of Science

> > in

Electronics Engineering September 2015 Hsinchu, Taiwan, Republic of China

中華民國一〇四年九月

# 佈局最佳化的低壓元件堆疊來達成高壓積體電路之靜電放電防護設計

學生: 廖顯峰 指導教授: 柯 明 道 教授

#### 國立交通大學

電子工程學系 電子研究所碩士班

靜電放電防護和門鎖效應 (latchup) 預防是在積體電路中兩個重要的可靠度議題, 尤其是在高壓應用方面。靜電放電可能發生在積體電路產品製造、封裝、組裝的過程中, 通常會造成在積體電路中嚴重的損害,而在電路正常操作情況下,雜訊可能會觸發積體 電路內部的寄生電晶體,所以在高壓靜電放電防護設計中,必須使持有電壓 (holding voltage) 高於電路操作電壓,否則在應用上可能會發生閂鎖效應 (latchup)。

高壓的靜電防護設計中,通常使用橫向擴散電晶體 (lateral diffused MOS, LDMOS), 但通常橫向擴散電晶體的持有電壓小於電路的操作電壓,會有閂鎖效應的風險,因此提 出使用低壓電晶體來做堆疊結構來達到在高壓中靜電防護有著高持有電壓的一種方法, 藉由調整元件的不同堆疊個數,使得在不同高壓應用來提供有效的靜電防護。

i

在此篇論文中,實驗並驗證堆疊結構,藉由多種不同的佈局方式來增加元件的靜電 耐受度,並且使用不同的防護環 (guard-ring) 的佈局方式,探討對持有電壓的影響。此 外,使用不同傳輸線脈衝產生器 (transmission line pulsing, TLP) 脈衝寬度對持有電壓的 影響,以及試著減少其佈局面積達到相同的靜電耐受度。

# Optimization of Stacked Low-Voltage PMOS for High-Voltage ESD Protection with Layout Consideration

Student: Seian-Feng Liao Advisor: Prof. Ming-Dou Ker

# Department of Electronics Engineering &Institute of Electronics National Chiao-Tung University

Electrostatic discharge (ESD) protection and latchup prevention are two important reliability issues to the CMOS integrated circuits, especially in high-voltage (HV) applications. ESD may occur accidentally during the fabrication, package, and assembling processes of IC products, which often caused serious damages on ICs. During normal circuit operation, the noise might unpredictably trigger the parasitic BJT of the ESD devices. Furthermore, to avoid latchup issue, the holding voltage (V<sub>h</sub>) should be larger than the supply voltage of the internal circuits in ESD protection design for HV applications.

Lateral DMOS (LDMOS) was often used as ESD protection device in HV process, but the holding voltage ( $V_h$ ) of LDMOS after snapback was smaller than the circuit operating voltage ( $V_{CC}$ ). Thus, the LDMOS was sensitive to latchup issue. Therefore, the stacked configuration of LV devices is a way to achieve a high holding voltage for ESD protection in

HV circuits. By adjusting the stacking numbers of stacked PMOSs, it can provide effective ESD protection for various HV applications.

In this thesis, stacks for ESD protection are implemented and verified, and it is discussed about different layout parameters to effectively improve ESD robustness of ESD devices. The guard-ring layout on the stacked LV devices was further investigated holding voltage in silicon chip. In addition, the pulse width of the transmission line pulsing (TLP) system was also investigated holding voltage in silicon chip. Decreasing the layout area to get high ESD robustness and latchup-free immunity for HV applications.

## Acknowledgements

首先要感謝柯明道老師,在碩士班這兩年的指導,在上台報告時,老師總能很快地 指出問題所在,讓我能透過問題,仔細思考後,得到新的知識,也非常謝謝老師可以推 薦我去公司工讀實習,能夠提早一步進入業界探索。

在此也要感謝「世界先進積體電路股份有限公司」,在我去工讀的期間,感謝元件工程處的各位,以及幫助過我操作失效分析機台及量測的同仁,謝謝你們的幫忙,在公司內,遇到任何問題,大家總是能夠一起討論,並且解決問題,才能夠讓我的研究順利完成。

而研究群的各位,也在研究有困難時,可以一起討論的夥伴們,感謝群祐學長、伯 硯學長、倍如學姊、Karuna 學長、艾菲學長、志聰學長、嘉岑學長、界廷學長、凱能學 長、冠宇學長、建豪學長、美蓮學姊、品歌學姊、信宏學長。同屆同學,一起打拼的義 傑、子毅、睿宏、菀學,學弟妹們,柏翰、易翰、鼎洋、道一、力瑾和安妮。感謝實驗 室的大家,有問題時可以一起討論,也能一起運動,出遊。

而我的好朋友們,子駒、銘哲、智州,能夠一起分享共同興趣,使得生活不會無聊, 也感謝逢甲電機系壘的學長學弟們,能夠在我畢業後,還能陪我一起打球及比賽,也感 謝一直一來的的心靈導師怡旬,總是在我遇到心情低落時,能夠當我最好的靠山,以及 任老師,讓我在有所抉擇時,給我最好的建議,以及幫助過我的大家,謝謝你們。

而最感謝的就是我的家人,能夠給我那麼好的環境,一路上的照顧及栽培,讓我能 毫無顧忌地專心研究,才會有現在的我,以及我的女朋友凱婷,總是能夠包容我的一切, 以及給我加油打氣,讓我能夠一路走來,可以如此順遂,畢業之後,我也會繼續努力, 不會讓你們失望。

廖顯峰

104年9月於竹塹交大

## **Contents**

| Abstract (Cl  | ninese)i                                                             |

|---------------|----------------------------------------------------------------------|

| Abstract      | iii                                                                  |

| Acknowledg    | ementsv                                                              |

| Contents      | vi                                                                   |

| List of Table | esviii                                                               |

| List of Figur | esxi                                                                 |

| Chapter 1     | Introduction1                                                        |

| 1.1           | Motivation1                                                          |

| 1.2           | ESD Protection Scheme in High-Voltage Integrated Circuits2           |

| 1.3           | Measurement Methods3                                                 |

| 1.4           | Thesis Organization5                                                 |

| Chapter 2     | Layout Optimization on the Stacked Low-Voltage PMOS for High-Voltage |

|               | ESD Protection6                                                      |

| 2.1           | Stacked Low-Voltage PMOS in a 0.5-µm HV Process6                     |

| 2.1           | .1 Stacking Units                                                    |

| 2.1           | 2 Device Types 8                                                     |

| 2.1           | 3 Experiment Results 9                                               |

| 2.2           | Stacked Low-Voltage PMOS in a 0.25-µm BCD Process16                  |

| 2.2           |                                                                      |

| 2.2           | .2 Layout Parameters of Test Devices18                               |

| 2.2           | .3 Experiment Results18                                              |

| 2.2           | .4 Discussion33                                                      |

| 2.3           | Summary74                                                            |

| Chapter 3     | Impact of Guard Ring Layout on the Stacked Low-Voltage PMOS for      |

|               | High-Voltage ESD Protection75                                        |

| 3.1           | Stacked Low-Voltage PMOS with Different Guard Ring Layout in a       |

|               | 0.5-μm HV Process75                                                  |

| 3.1           | .1 Test Devices75                                                    |

| 3.1           | .2 Experimental Results79                                            |

| 3.2           | Different Guard Ring Layout of Stacked Low-Voltage PMOS              |

|               | measured by TLP with different pulse widths in a 0.5-µm HV           |

|               | Process83                                                            |

| 3.2           | .1 Different TLP Pulse Widths83                                      |

| 3.2           | .2 Experiment Results84                                              |

| 3.3           | Different Guard Ring Layout of Stacked Low-Voltage PMOS              |

|               | measured by TLP in a 0.25-µm BCD Process | 102 |

|---------------|------------------------------------------|-----|

| 3.3.1         | Test Devices                             | 102 |

| 3.3.2         | Experiment Results                       | 105 |

| 3.3.3         | Discussion                               | 116 |

| 3.4           | Summary                                  | 132 |

| Chapter 4 Con | nclusions and Future Works               | 133 |

| 4.1           | Conclusions                              | 133 |

| 4.2           | Future Work                              | 133 |

| 4.2.1         | New Type Device                          | 133 |

| 4.2.2         | Guard Ring in Real Circuit Application   | 134 |

| Reference     |                                          | 135 |

| Vita          |                                          | 136 |

| PUBLICATION   | N LIST                                   | 137 |

## **List of Tables**

| Table 2.1         | The measurement data of device 110                                      |

|-------------------|-------------------------------------------------------------------------|

| Table 2.2         | The measurement data of device 211                                      |

| Table 2.3         | The measurement data of device 312                                      |

| Table 2.4         | The measurement data of device 413                                      |

| Table 2.5         | The measurement data of devices with guard-ring layout type one14       |

| Table 2.6         | The measurement data of devices with guard-ring layout type two15       |

| Table 2.7         | The measurement data of typical stacked LV PMOSs19                      |

| Table 2.8         | The measurement data of full silicide (no RPO) stacked LV PMOSs20       |

| Table 2.9         | The measurement data of silicide blocking (RPO_0µm) stacked LV PMOSs    |

|                   | 21                                                                      |

| <b>Table 2.10</b> | The measurement data of silicide blocking (RPO0.03µm) stacked LV        |

|                   | PMOSs22                                                                 |

| <b>Table 2.11</b> | The measurement data of silicide blocking (RPO0.06µm) stacked LV        |

|                   | PMOSs23                                                                 |

| <b>Table 2.12</b> | The measurement data of stacked LV PMOSs with d1 4µm25                  |

| <b>Table 2.13</b> | The measurement data of stacked LV PMOSs with d1 6µm26                  |

| <b>Table 2.14</b> | The measurement data of stacked LV PMOSs with drain contact number 4    |

|                   |                                                                         |

| <b>Table 2.15</b> | The measurement data of stacked LV PMOSs with d1 4µm and drain          |

|                   | contact number 428                                                      |

| <b>Table 2.16</b> | The measurement data of stacked LV PMOSs with d1 6µm and drain          |

|                   | contact number 429                                                      |

| <b>Table 2.17</b> | The measurement data of stacked LV PMOSs with channel length 1µm31      |

| <b>Table 2.18</b> | The measurement data of stacked LV PMOSs with total width 600µm and     |

|                   | the single finger width 50µm32                                          |

| <b>Table 2.19</b> | The measurement data of LV PMOS with different layout parameters36      |

| <b>Table 2.20</b> | The measurement data of 2-PMOSs with different layout parameters40      |

| <b>Table 2.21</b> | The measurement data of 3-PMOSs with different layout parameters43      |

| <b>Table 2.22</b> | The measurement data of 4-PMOSs with different layout parameters47      |

| <b>Table 2.23</b> | The measurement data of 5-PMOSs with different layout parameters 50     |

| <b>Table 2.24</b> | The measurement data of 6-PMOSs with different layout parameters53      |

| <b>Table 2.25</b> | The measurement data of 7-PMOSs with different layout parameters 56     |

| <b>Table 2.26</b> | The measurement data of 8-PMOSs with different layout parameters 59     |

| <b>Table 2.27</b> | The measurement data of 9-PMOSs with different layout parameters 62     |

| <b>Table 2.28</b> | The measurement data of 10-PMOSs with different layout parameters 65    |

| Table 3.1         | Summary of 2-PMOSs stacked structure with different guard-ring types 80 |

| <b>Table 3.2</b>  | Summary of 3-PMOSs stacked structure with different guard-ring types82 |

|-------------------|------------------------------------------------------------------------|

| Table 3.3         | Summary of 2-PMOSs with different guard-ring types measured by 100-ns  |

|                   | TLP84                                                                  |

| Table 3.4         | Summary of 2-PMOSs with different guard-ring types measured by 200-ns  |

|                   | TLP85                                                                  |

| <b>Table 3.5</b>  | Summary of 2-PMOSs with different guard-ring types measured by 500-ns  |

|                   | TLP86                                                                  |

| Table 3.6         | Summary of 2-PMOSs with different guard-ring types measured by 800-ns  |

|                   | TLP87                                                                  |

| <b>Table 3.7</b>  | Summary of 3-PMOSs with different guard-ring types measured by 100-ns  |

|                   | TLP92                                                                  |

| Table 3.8         | Summary of 3-PMOSs with different guard-ring types measured by 200-ns  |

|                   | TLP93                                                                  |

| Table 3.9         | Summary of 3-PMOSs with different guard-ring types measured by 500-ns  |

|                   | TLP94                                                                  |

| <b>Table 3.10</b> | Summary of 3-PMOSs with different guard-ring types measured by 800-ns  |

|                   | TLP95                                                                  |

| <b>Table 3.11</b> | Summary of 2-PMOSs with different guard-ring types measured by         |

|                   | different TLP pulse width101                                           |

| <b>Table 3.12</b> | Summary of 3-PMOSs with different guard-ring types measured by         |

|                   | different TLP pulse width101                                           |

| <b>Table 3.13</b> | The measurement data of type A (typical stacked LV PMOSs)106           |

| <b>Table 3.14</b> | The measurement data of type B (12μm)107                               |

| <b>Table 3.15</b> | The measurement data of type B (10μm)108                               |

| <b>Table 3.16</b> | The measurement data of type B (8µm)109                                |

| <b>Table 3.17</b> | The measurement data of type B (6μm)110                                |

| <b>Table 3.18</b> | The measurement data of type B (4µm)111                                |

| <b>Table 3.19</b> | The measurement data of type B (2μm)111                                |

| <b>Table 3.20</b> | The measurement data of type C (12 $\mu$ m)112                         |

| <b>Table 3.21</b> | The measurement data of type C (11 $\mu$ m)113                         |

| <b>Table 3.22</b> | The measurement data of type C $(10\mu m)$                             |

| <b>Table 3.23</b> | The measurement data of type C (9μm)115                                |

| <b>Table 3.24</b> | Area information and comparison of 2-PMOSs117                          |

| <b>Table 3.25</b> | Area information and comparison of 3-PMOSs118                          |

| <b>Table 3.26</b> | Area information and comparison of 4-PMOSs119                          |

| <b>Table 3.27</b> | Area information and comparison of 5-PMOSs120                          |

| <b>Table 3.28</b> | Area information and comparison of 6-PMOSs121                          |

| <b>Table 3.29</b> | Area information and comparison of 7-PMOSs122                          |

| <b>Table 3.30</b> | Area information and comparison of 8-PMOSs123                          |

| <b>Table 3.31</b> | Area information and comparison of 9-PMOSs       | 124 |

|-------------------|--------------------------------------------------|-----|

| <b>Table 3.32</b> | Area information and comparison of 10-PMOSs      | 125 |

| <b>Table 3.33</b> | Multi-finger uniform turn-on of type A (typical) | 126 |

| <b>Table 3.34</b> | Multi-finger uniform turn-on of type B (12μm)    | 127 |

| <b>Table 3.35</b> | Multi-finger uniform turn-on of type C (12μm)    | 127 |

| <b>Table 3.36</b> | Summary of 60V ESD devices                       | 130 |

| <b>Table 3.37</b> | Summary of 80V ESD devices                       | 131 |

## **List of Figures**

| Fig. 1.1  | A typical whole-chip ESD protection scheme2                                               |

|-----------|-------------------------------------------------------------------------------------------|

| Fig. 1.2  | The ESD protection design window [10]3                                                    |

| Fig. 1.3  | Equivalent circuits of (a) HBM and (b) MM4                                                |

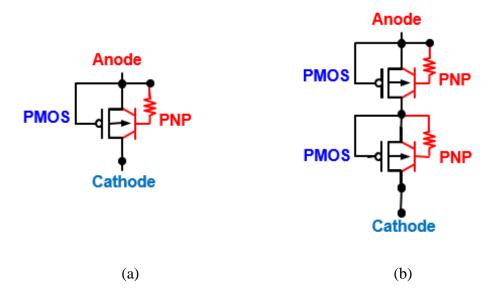

| Fig. 2.1  | Equivalent circuits of (a) a single LV PMOS and (b) stacked LV PMOSs                      |

|           | structure7                                                                                |

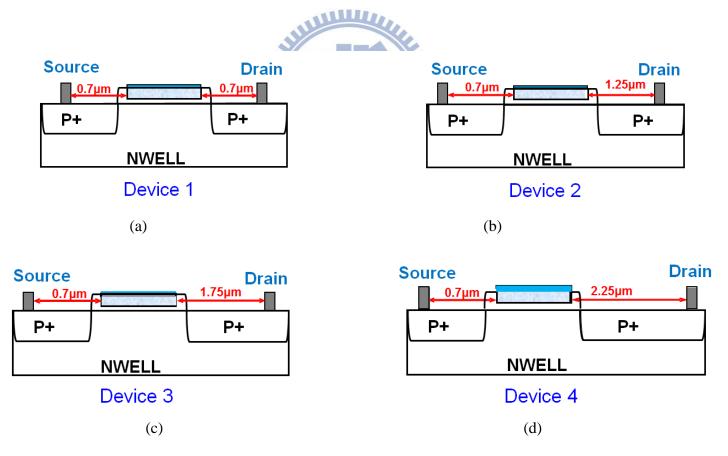

| Fig. 2.2  | The cross-section views of PMOS stacking unit drawn with (a) the drain                    |

|           | contact to poly-gate edge (d1) spacing of 0.7 µm, (b) the d1 spacing of                   |

|           | $1.25\mu m$ , (c) the d1 spacing of $1.75\mu m$ , and (d) the d1 spacing of $1.25\mu m$ 7 |

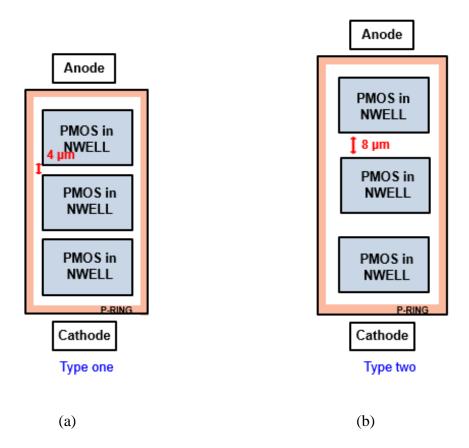

| Fig. 2.3  | The two types of guard-ring layout for 3-PMOSs stacked structure, (a) with                |

|           | one whole p-ring and NWELL spacing of 4µm and (b) with one whole                          |

|           | p-ring and NWELL spacing of 8µm8                                                          |

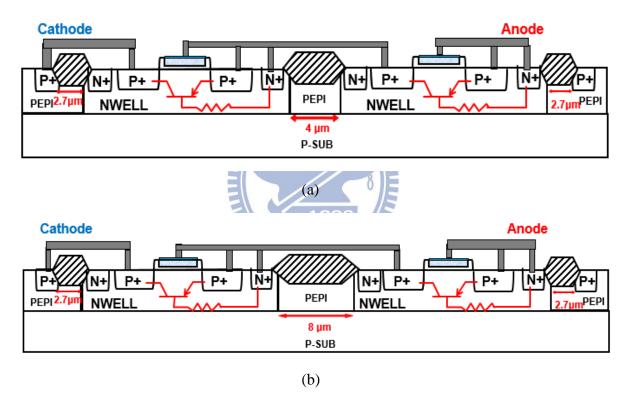

| Fig. 2.4  | The cross-sectional views of stacked structure with two LV PMOSs drawn                    |

|           | with (a) the NWELL spacing of 4µm (type one) and (b) the NWELL spacing                    |

|           | of 8µm (type two). Each LV PMOS has its own separated N-well in the                       |

|           | stacked structure9                                                                        |

| Fig. 2.5  | The TLP-measured I-V characteristics of device 1 with different guard-ring                |

|           | layouts                                                                                   |

| Fig. 2.6  | The TLP-measured I-V characteristics of device 2 with different guard-ring                |

|           | layouts11                                                                                 |

| Fig. 2.7  | The TLP-measured I-V characteristics of device 3 with different guard-ring                |

|           | layouts12                                                                                 |

| Fig. 2.8  | The TLP-measured I-V characteristics of device 4 with different guard-ring                |

|           | layouts                                                                                   |

| Fig. 2.9  | The TLP-measured I-V characteristics of devices with guard-ring layout                    |

|           | type one14                                                                                |

| Fig. 2.10 | The TLP-measured I-V characteristics of devices with guard-ring layout                    |

|           | type two15                                                                                |

| Fig. 2.11 | The cross-section view of typical PMOS17                                                  |

| Fig. 2.12 | The (a) schematic of stacked LV PMOSs with different stacking numbers                     |

|           | and (b) top view for 3-PMOSs stacked structure17                                          |

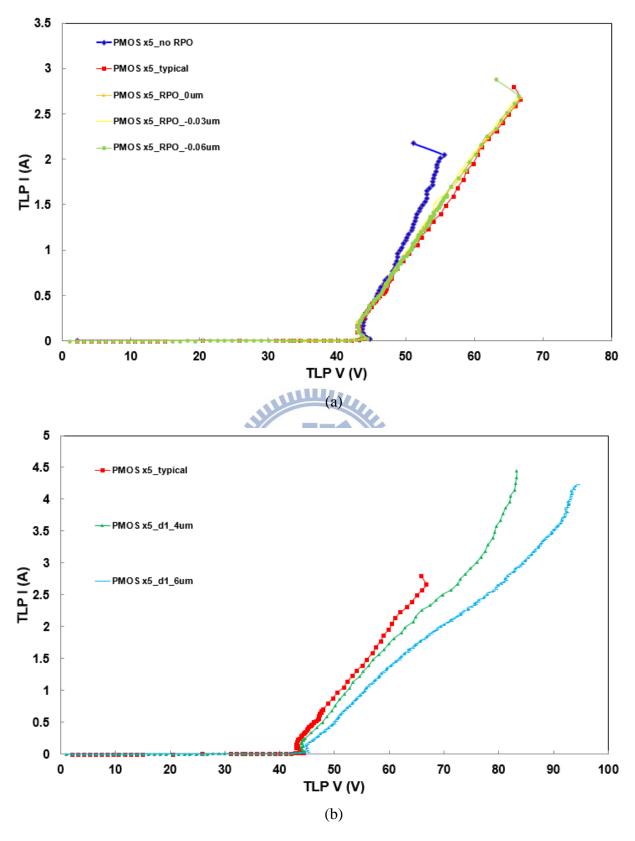

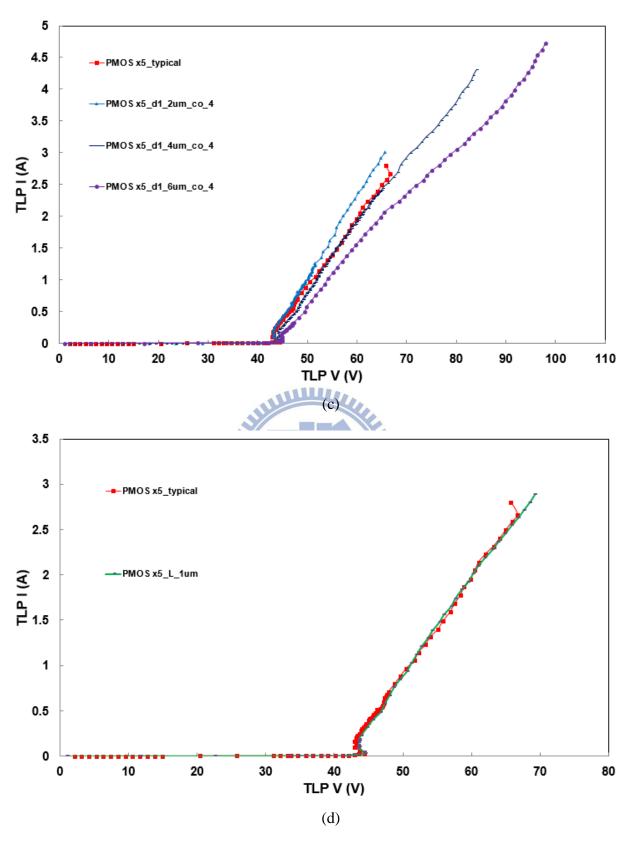

| Fig. 2.13 | The TLP-measured I-V characteristics of typical stacked LV PMOSs19                        |

| Fig. 2.14 | The TLP-measured I-V characteristics of full silicide (no RPO) stacked LV                 |

| _         | PMOSs20                                                                                   |

| Fig. 2.15 | The TLP-measured I-V characteristics of silicide blocking (RPO_0µm)                       |

| J         | stacked LV PMOSs 21                                                                       |

| Fig. 2.16 | The TLP-measured I-V characteristics of silicide blocking (RPO0.03μm)      |

|-----------|----------------------------------------------------------------------------|

|           | stacked LV PMOSs22                                                         |

| Fig. 2.17 | The TLP-measured I-V characteristics of silicide blocking (RPO0.06μm)      |

|           | stacked LV PMOSs23                                                         |

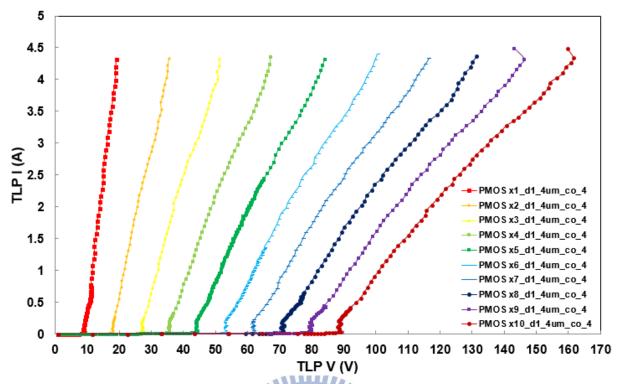

| Fig. 2.18 | The TLP-measured I-V characteristics of stacked LV PMOSs with d1 4µm       |

| E: 2.10   |                                                                            |

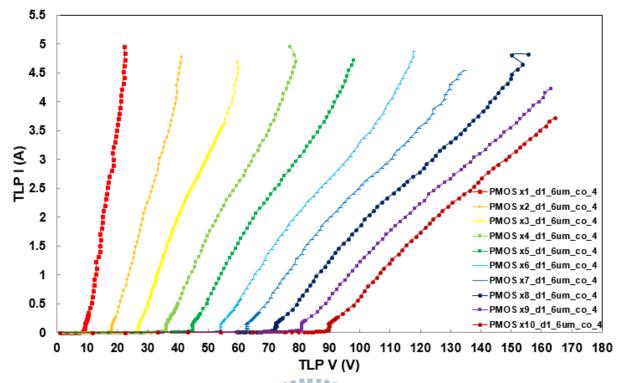

| Fig. 2.19 | The TLP-measured I-V characteristics of stacked LV PMOSs with d1 6µm25     |

| Fig. 2.20 | The TLP-measured I-V characteristics of stacked LV PMOSs with drain        |

|           | contact number 427                                                         |

| Fig. 2.21 | The TLP-measured I-V characteristics of stacked LV PMOSs with d1 4µm       |

|           | and drain contact number 428                                               |

| Fig. 2.22 | The TLP-measured I-V characteristics of stacked LV PMOSs with d1 6µm       |

|           | and drain contact number 429                                               |

| Fig. 2.23 | The TLP-measured I-V characteristics of stacked LV PMOSs with channel      |

|           | length 1µm30                                                               |

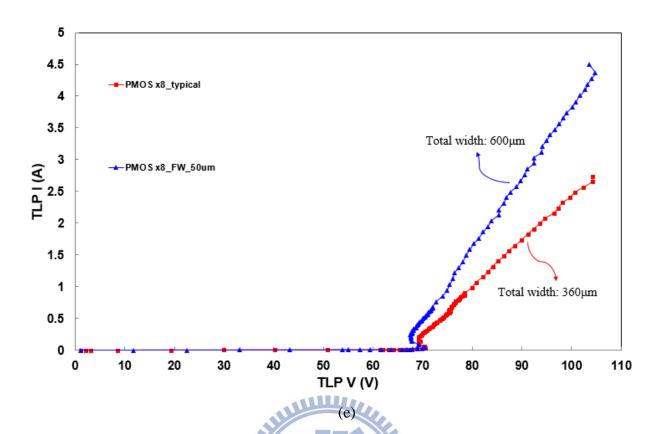

| Fig. 2.24 | The TLP-measured I-V characteristics of stacked LV PMOSs with total        |

|           | width 600μm and the single finger width 50μm32                             |

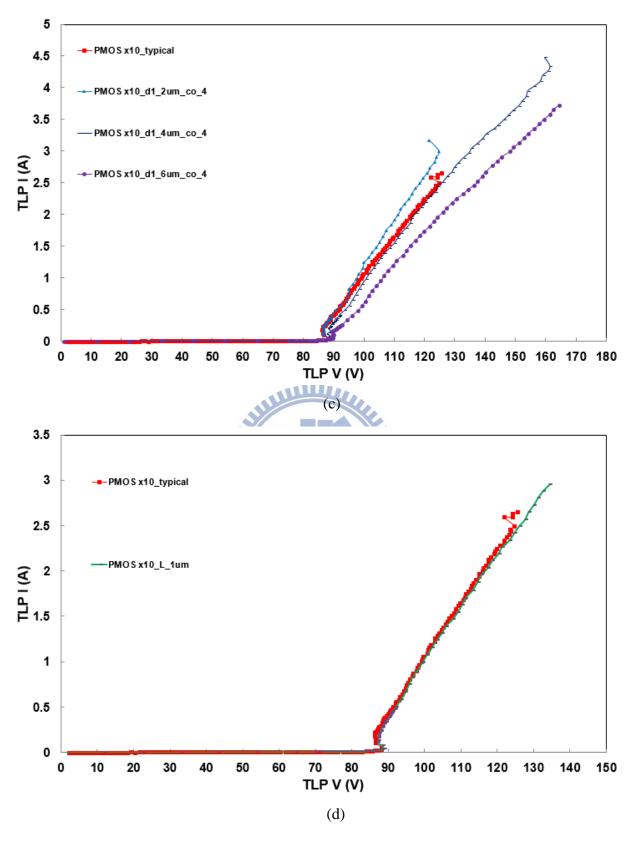

| Fig. 2.25 | The TLP measured I-V curves of LV PMOS with different (a) RPO splits       |

|           | and (b) d1 splits                                                          |

| Fig. 2.25 | The TLP measured I-V curves of LV PMOS with different (c) d1 and drain     |

|           | contact number (co) splits and (d) L splits35                              |

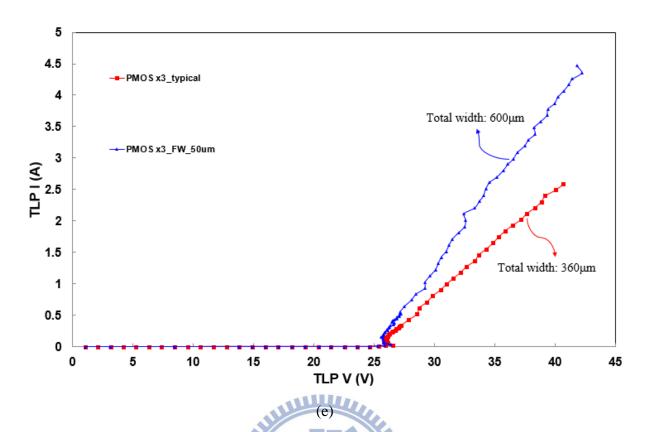

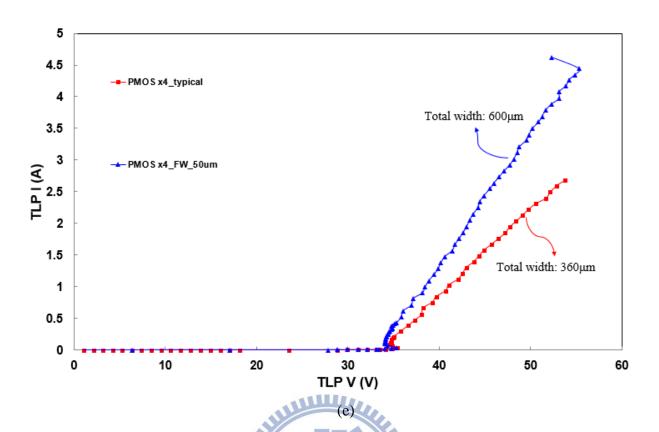

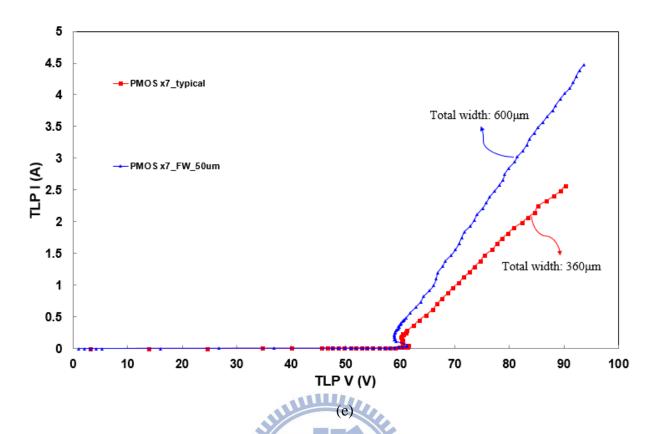

| Fig. 2.25 | The TLP measured I-V curves of LV PMOS with different (e) total width      |

|           | splits36                                                                   |

| Fig. 2.26 | The TLP measured I-V curves of 2-PMOSs with different (a) RPO splits37     |

| Fig. 2.26 | The TLP measured I-V curves of 2-PMOSs with different (b) d1 splits and    |

|           | (c) d1 and drain contact number (co) splits38                              |

| Fig. 2.26 | The TLP measured I-V curves of 2-PMOSs with different (d) L splits and (e) |

|           | total width splits39                                                       |

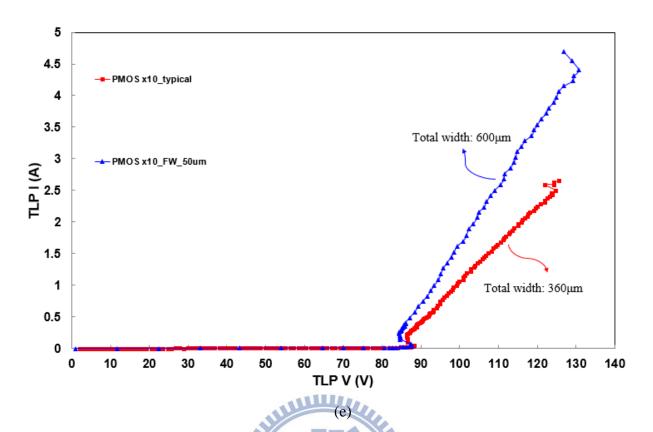

| Fig. 2.27 | The TLP measured I-V curves of 3-PMOSs with different (a) RPO splits       |

|           | and (b) d1 splits41                                                        |

| Fig. 2.27 | The TLP measured I-V curves of 3-PMOSs with different (c) d1 and drain     |

|           | contact number (co) splits and (d) L splits42                              |

| Fig. 2.27 | The TLP measured I-V curves of 3-PMOSs with different (e) total width      |

|           | splits43                                                                   |

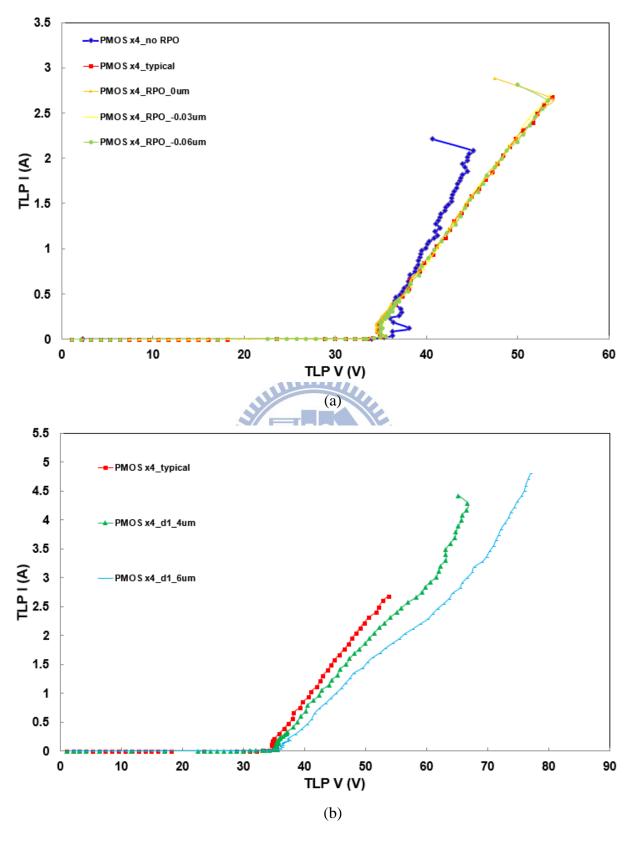

| Fig. 2.28 | The TLP measured I-V curves of 4-PMOSs with different (a) RPO splits       |

|           | and (b) d1 splits45                                                        |

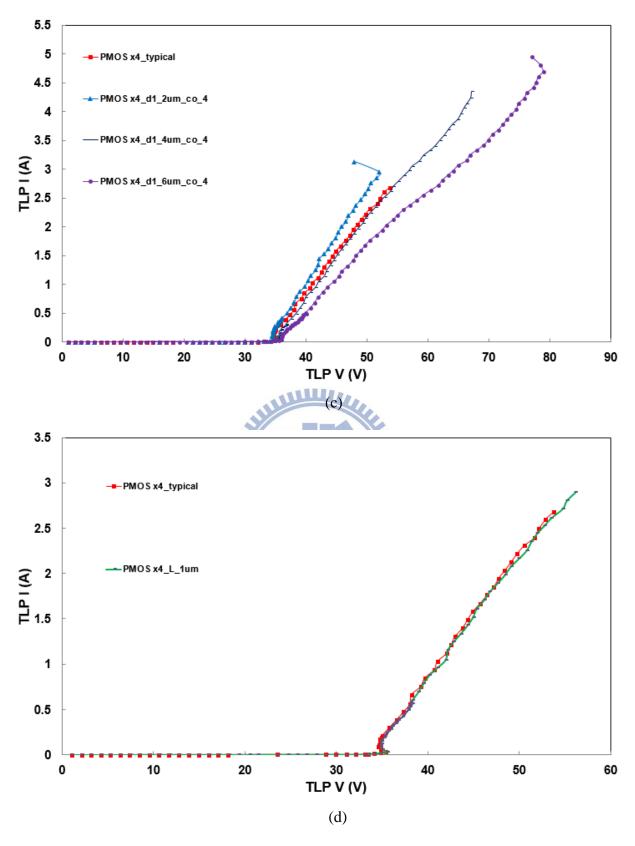

| Fig. 2.28 | The TLP measured I-V curves of 4-PMOSs with different (c) d1 and drain     |

|           | contact number (co) splits and (d) L splits46                              |

| Fig. 2.28 | The TLP measured I-V curves of 4-PMOSs with different (e) total width   |

|-----------|-------------------------------------------------------------------------|

|           | splits47                                                                |

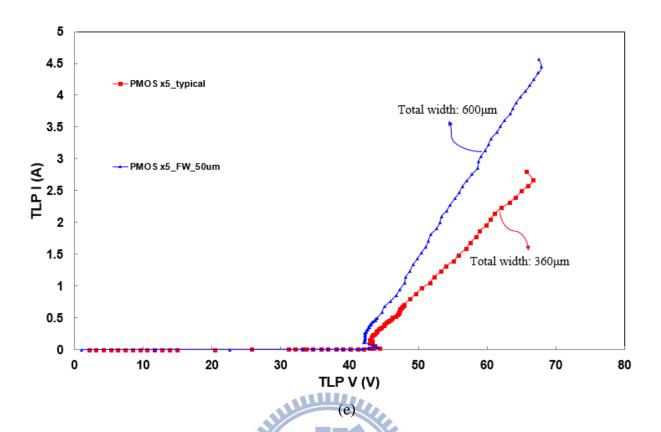

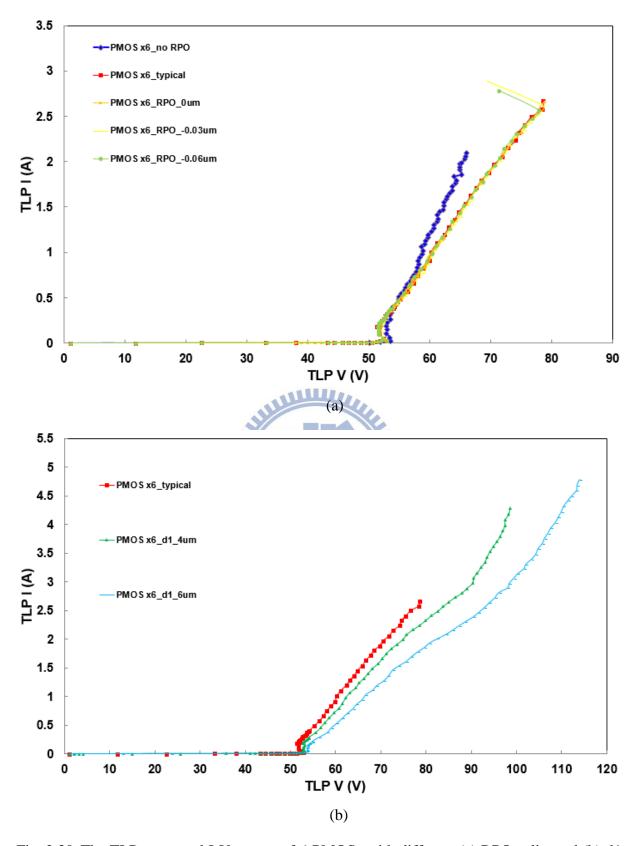

| Fig. 2.29 | The TLP measured I-V curves of 5-PMOSs with different (a) RPO splits    |

|           | and (b) d1 splits48                                                     |

| Fig. 2.29 | The TLP measured I-V curves of 5-PMOSs with different (c) d1 and drain  |

|           | contact number (co) splits and (d) L splits49                           |

| Fig. 2.29 | The TLP measured I-V curves of 5-PMOSs with different (e) total width   |

|           | splits50                                                                |

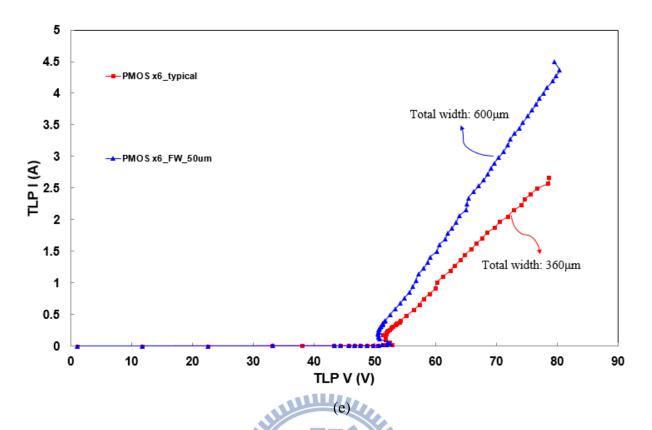

| Fig. 2.30 | The TLP measured I-V curves of 6-PMOSs with different (a) RPO splits    |

|           | and (b) d1 splits51                                                     |

| Fig. 2.30 | The TLP measured I-V curves of 6-PMOSs with different (c) d1 and drain  |

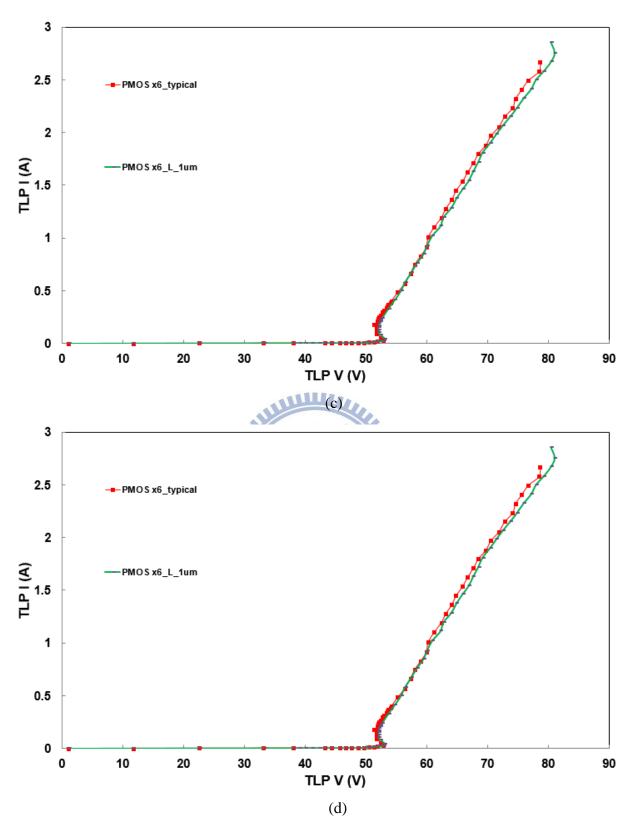

|           | contact number (co) splits and (d) L splits52                           |

| Fig. 2.30 | The TLP measured I-V curves of 6-PMOSs with different (e) total width   |

|           | splits53                                                                |

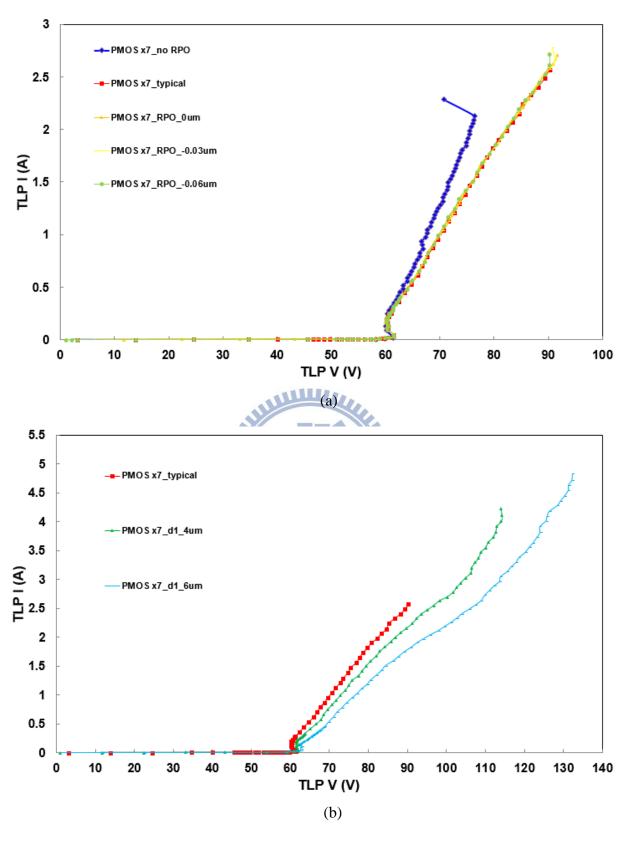

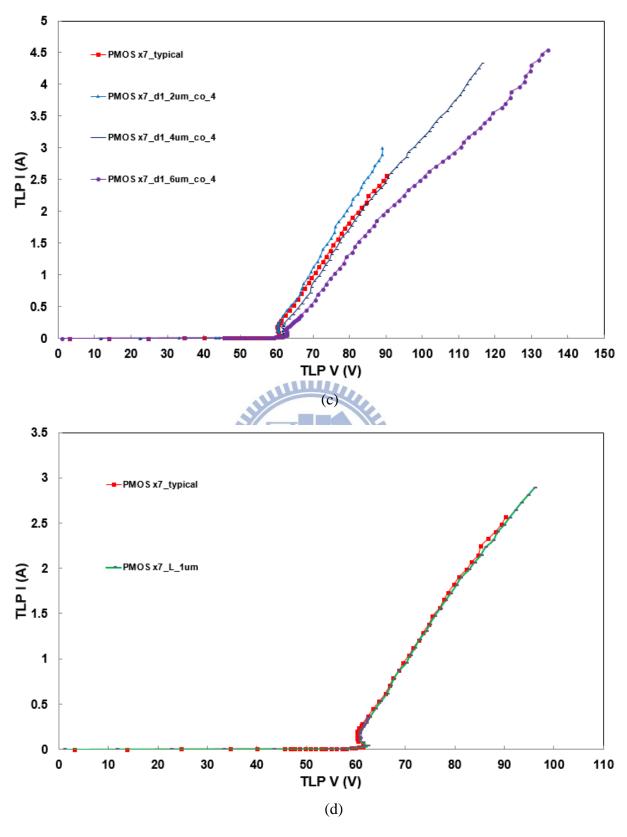

| Fig. 2.31 | The TLP measured I-V curves of 7-PMOSs with different (a) RPO splits    |

|           | and (b) d1 splits54                                                     |

| Fig. 2.31 | The TLP measured I-V curves of 7-PMOSs with different (c) d1 and drain  |

|           | contact number (co) splits and (d) L splits55                           |

| Fig. 2.31 | The TLP measured I-V curves of 7-PMOSs with different (e) total width   |

|           | splits56                                                                |

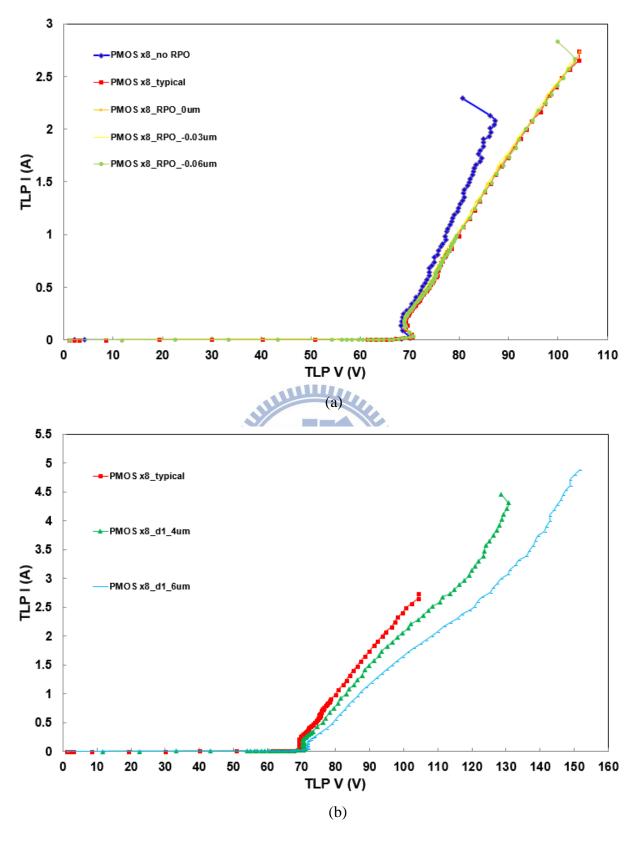

| Fig. 2.32 | The TLP measured I-V curves of 8-PMOSs with different (a) RPO splits    |

|           | and (b) d1 splits57                                                     |

| Fig. 2.32 | The TLP measured I-V curves of 8-PMOSs with different (c) d1 and drain  |

|           | contact number (co) splits and (d) L splits58                           |

| Fig. 2.32 | The TLP measured I-V curves of 8-PMOSs with different (e) total width   |

|           | splits59                                                                |

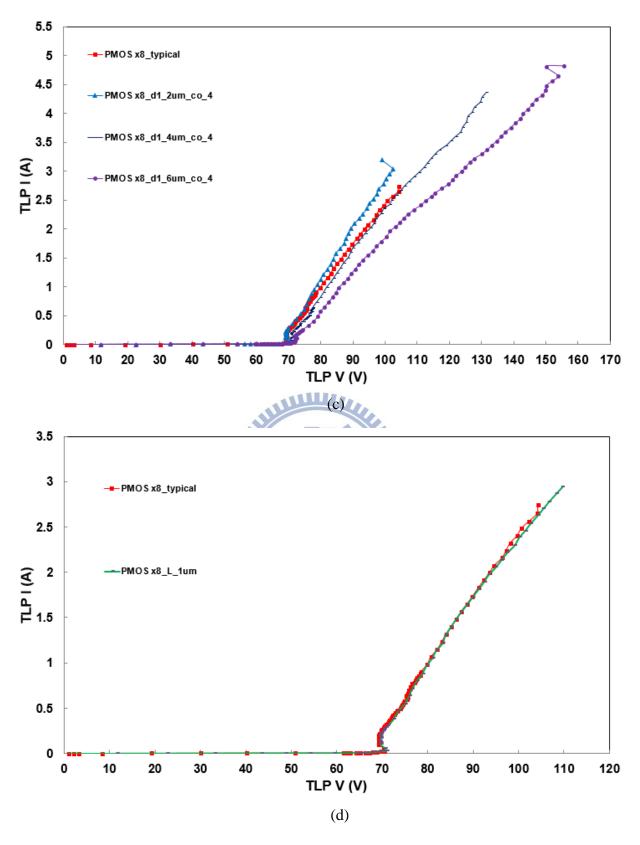

| Fig. 2.33 | The TLP measured I-V curves of 9-PMOSs with different (a) RPO splits    |

|           | and (b) d1 splits60                                                     |

| Fig. 2.33 | The TLP measured I-V curves of 9-PMOSs with different (c) d1 and drain  |

|           | contact number (co) splits and (d) L splits61                           |

| Fig. 2.33 | The TLP measured I-V curves of 9-PMOSs with different (e) total width   |

|           | splits62                                                                |

| Fig. 2.34 | The TLP measured I-V curves of 10-PMOSs with different (a) RPO splits   |

|           | and (b) d1 splits63                                                     |

| Fig. 2.34 | The TLP measured I-V curves of 10-PMOSs with different (c) d1 and drain |

|           | contact number (co) splits and (d) L splits64                           |

| Fig. 2.34 | The TLP measured I-V curves of 10-PMOSs with different (e) total width  |

|           | splits65                                                                |

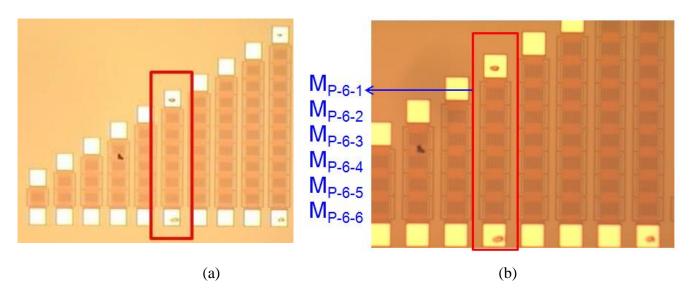

| Fig. 2.35 | The optical microscope (OM) pictures of 6-PMOSs with d1 2um after MM    |

|                 | stress (a) top view and (b) partial enlarged drawing66                                                                    |

|-----------------|---------------------------------------------------------------------------------------------------------------------------|

| Fig. 2.36       | The optical microscope (OM) pictures of 6-PMOSs with d1_6µm after MM                                                      |

|                 | stress67                                                                                                                  |

| Fig. 2.37       | The optical microscope (OM) pictures of 10-PMOSs with d1_2µm after MM                                                     |

| E:~ 2 20        | stress                                                                                                                    |

| Fig. 2.38       | stress                                                                                                                    |

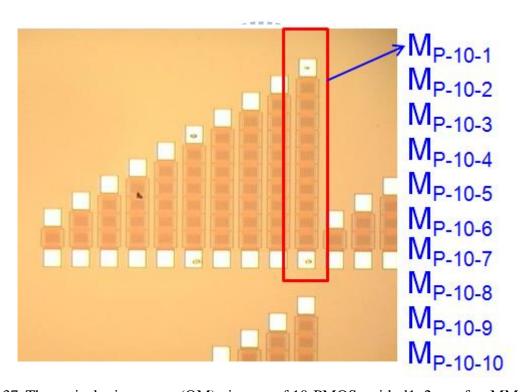

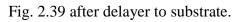

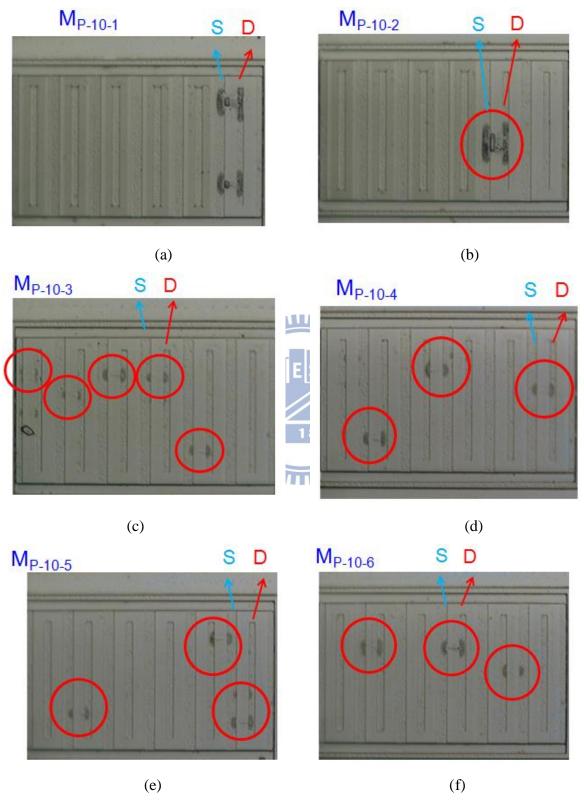

| Fig. 2.39       | The OM pictures of 10-PMOSs with d1_2µm (typical) after delayer to                                                        |

| 116. 2.07       | substrate (a) $M_{P-10-1}$ , (b) $M_{P-10-2}$ , (c) $M_{P-10-3}$ , (d) $M_{P-10-4}$ (e) $M_{P-10-5}$ , and (f)            |

|                 | M <sub>P-10-6</sub>                                                                                                       |

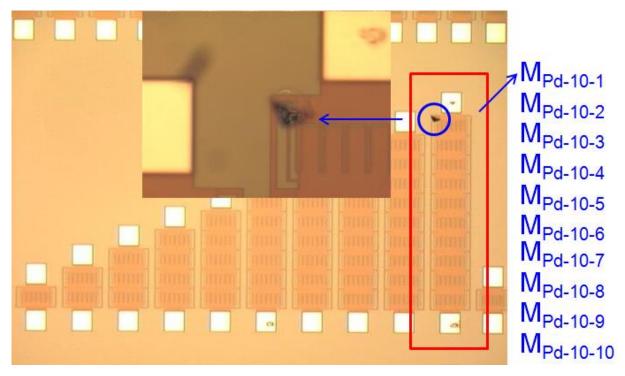

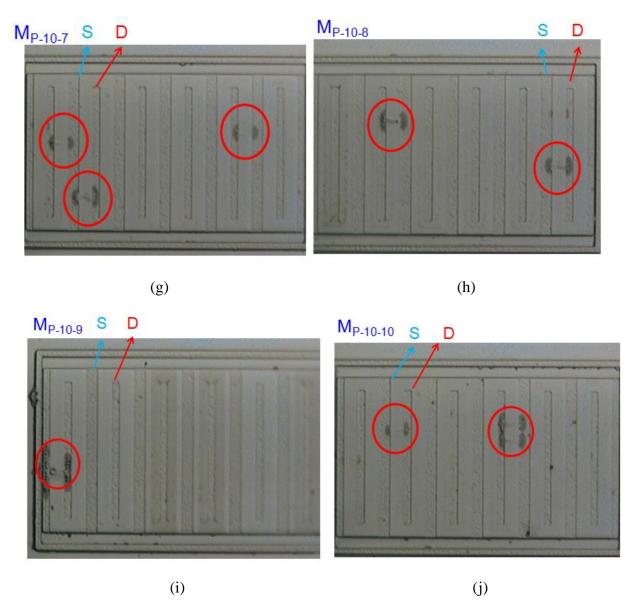

| Fig. 2.39       | The OM pictures of 10-PMOSs with d1_2µm (typical) after delayer to                                                        |

| 1.8. 2.0>       | substrate (g) $M_{P-10-7}$ , (h) $M_{P-10-8}$ , (i) $M_{P-10-9}$ , and (j) $M_{P-10-10}$ 70                               |

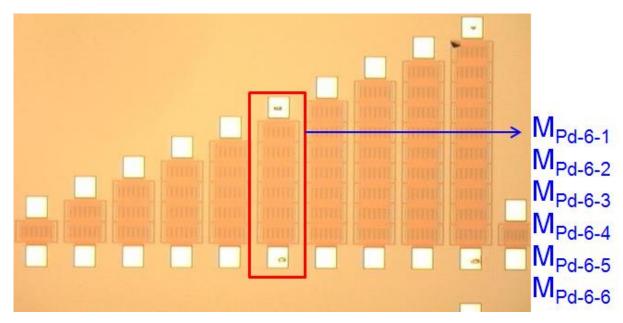

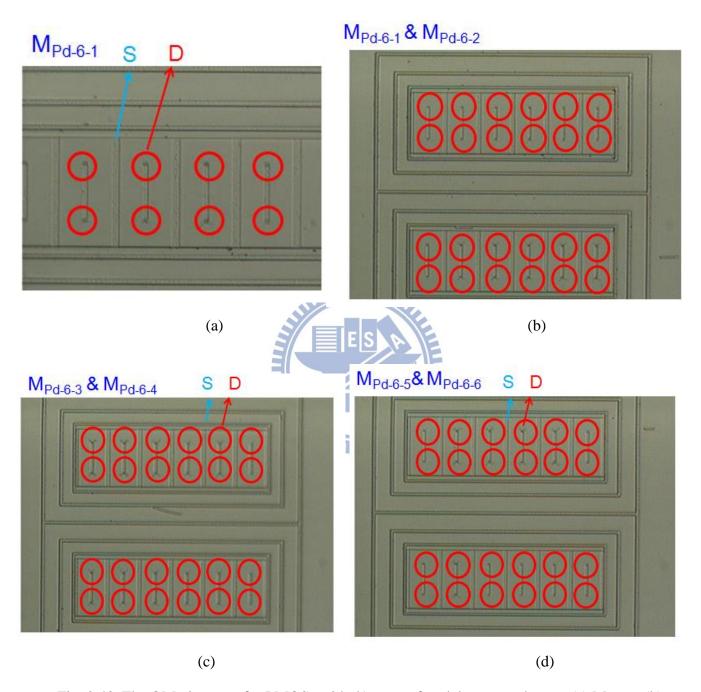

| Fig. 2.40       | The OM pictures of 6-PMOSs with d1_6μm after delayer to substrate (a)                                                     |

| <b>g</b> : _::: | $M_{Pd-6-1}$ , (b) $M_{Pd-6-2}$ & $M_{Pd-6-2}$ , (c) $M_{Pd-6-3}$ & $M_{Pd-6-4}$ , and (d) $M_{Pd-6-5}$ & $M_{Pd-6-6}$ 71 |

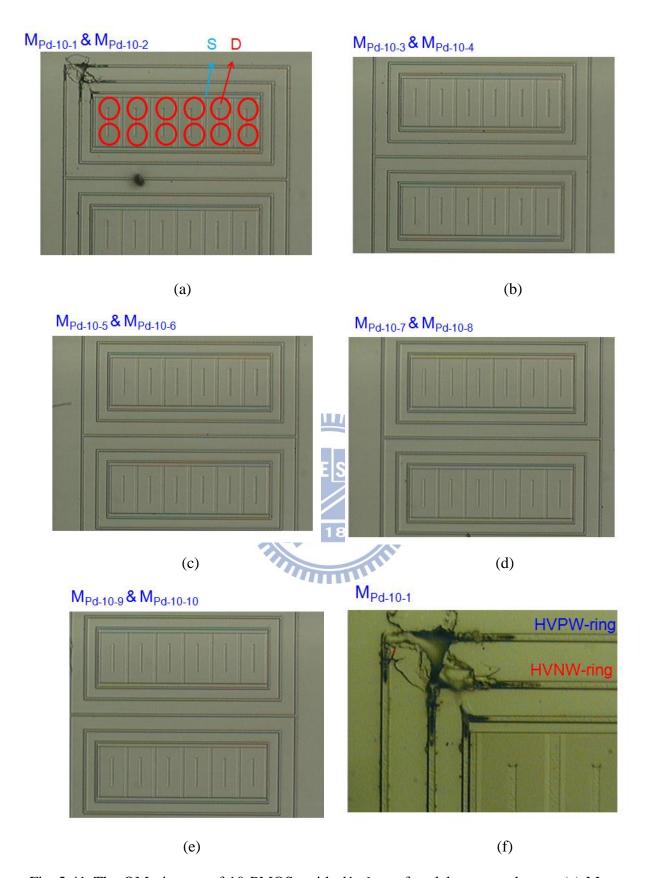

| Fig. 2.41       | The OM pictures of 10-PMOSs with d1_6µm after delayer to substrate (a)                                                    |

| 8               | $M_{Pd-10-1}$ & $M_{Pd-10-2}$ , (b) $M_{Pd-10-3}$ & $M_{Pd-10-4}$ , (c) $M_{Pd-10-5}$ & $M_{Pd-10-6}$ , (d) $M_{Pd-10-7}$ |

|                 | & $M_{Pd-10-8}$ , (e) $M_{Pd-10-9}$ & $M_{Pd-10-10}$ , and (f) the edge of $M_{Pd-10-1}$ 72                               |

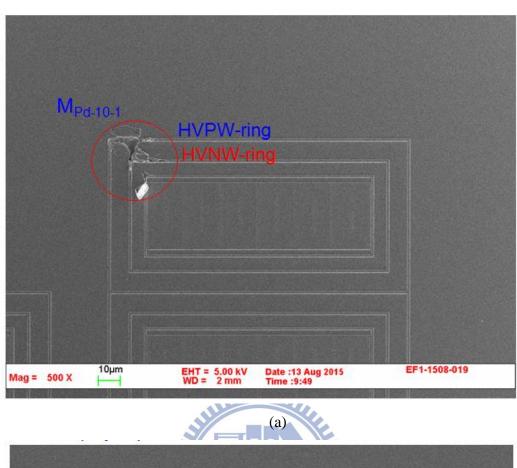

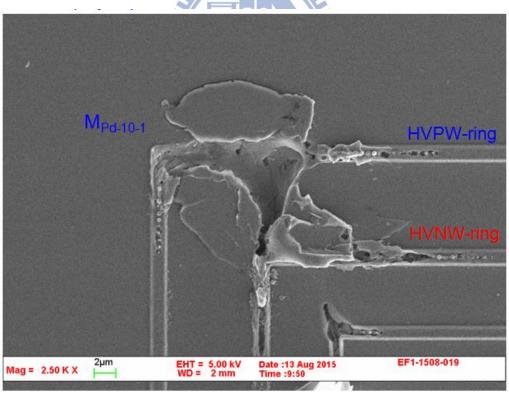

| Fig. 2.42       | The SEM pictures of 10-PMOSs with d1_6µm after delayer to substrate (a)                                                   |

| <b>9</b> :=     | $M_{Pd-10-1}$ , (b) the edge of $M_{Pd-10-1}$                                                                             |

| Fig. 2.43       | The two types of guard-ring layout for 3-PMOSs stacked structure, (a) with                                                |

|                 | one whole p-ring and NWELL spacing of 4µm and (b) with one whole                                                          |

|                 | p-ring and NWELL spacing of 8μm8                                                                                          |

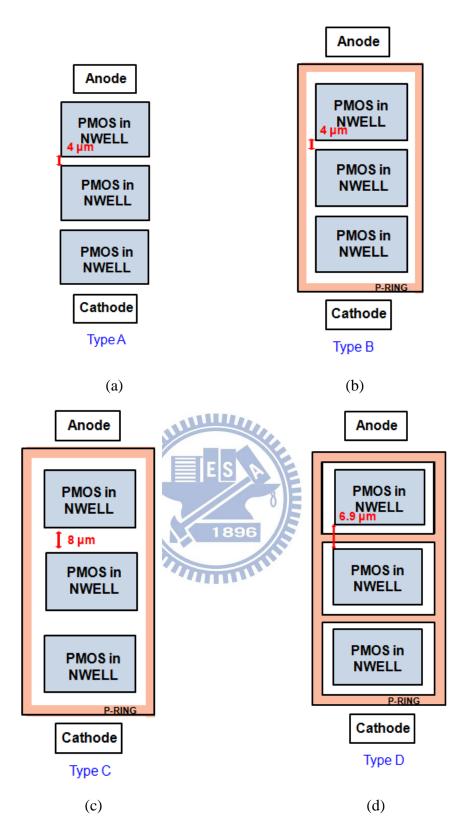

| Fig. 3.1        | The four types of guard-ring layout for 3-PMOSs stacked structure, (a)                                                    |

|                 | without p-ring, (b) with one whole p-ring and NWELL spacing of $4\mu m,(c)$                                               |

|                 | with one whole p-ring and NWELL spacing of $8\mu m,$ and (d) with inserted                                                |

|                 | p-ring to surround each LV PMOS77                                                                                         |

| Fig. 3.2        | The cross-sectional views of stacked structure with two LV PMOSs drawn                                                    |

|                 | with (a) without p-ring, (b) the NWELL spacing of $4\mu m$ , (c) the NWELL                                                |

|                 | spacing of 8μm, and (d) with inserted p-ring to surround each LV PMOS.                                                    |

|                 | Each LV PMOS has its own separated N-well in the stacked structure78                                                      |

| Fig. 3.3        | The TLP-measured I-V characteristics of 2-PMOSs with different                                                            |

|                 | guard-ring layouts79                                                                                                      |

| Fig. 3.4        | The TLP-measured I-V characteristics of 3-PMOSs with different                                                            |

| T. 2.5          | guard-ring layouts                                                                                                        |

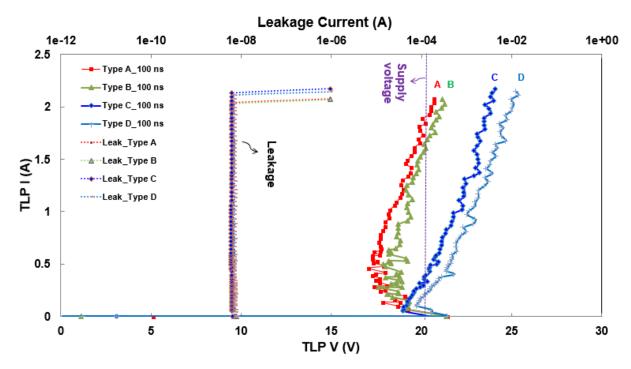

| Fig. 3.5        | The TLP-measured I-V characteristics of the stacked 2-PMOSs and                                                           |

| E:- 2.6         | 3-PMOSs with the guard-ring layout of type D                                                                              |

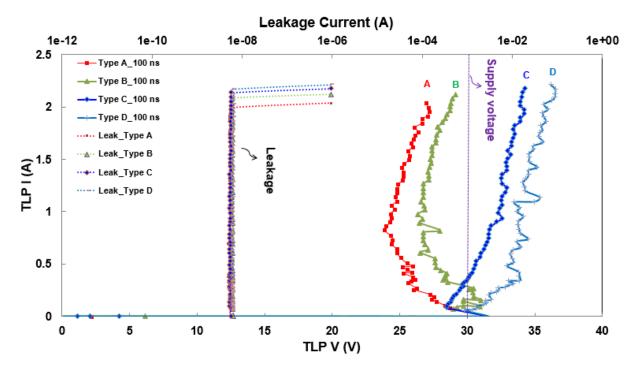

| Fig. 3.6        | The 100-ns TLP-measured I-V characteristics of 2-PMOSs with different                                                     |

| Fig. 2.7        | guard-ring layouts                                                                                                        |

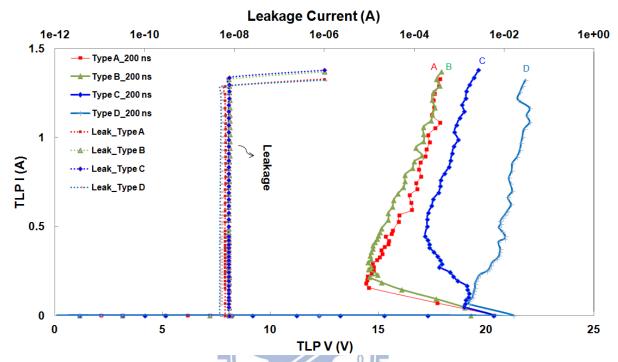

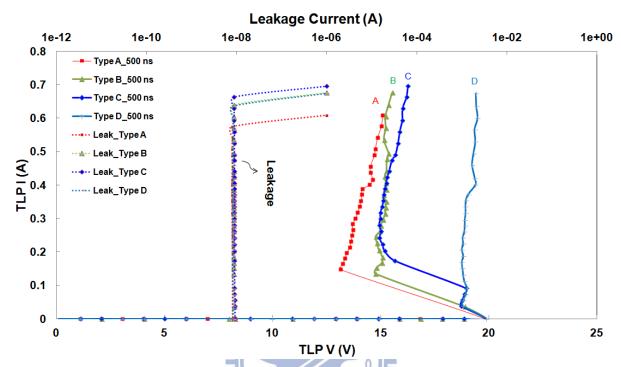

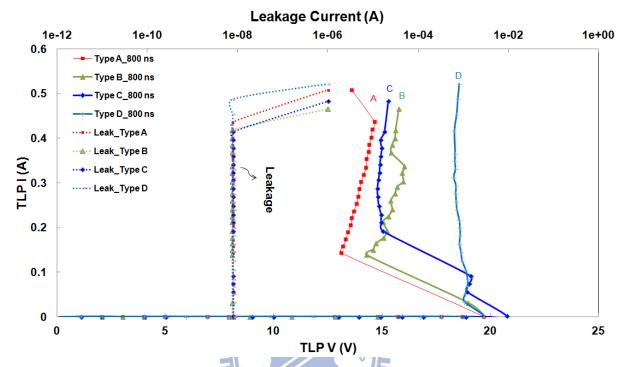

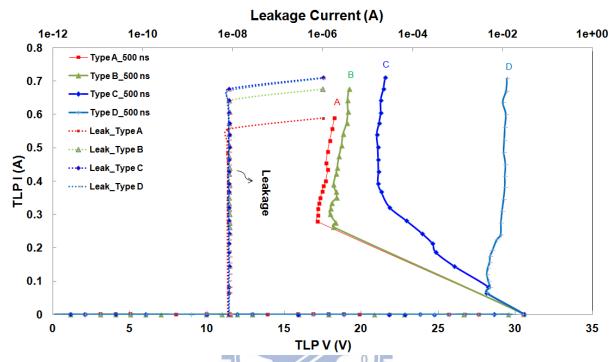

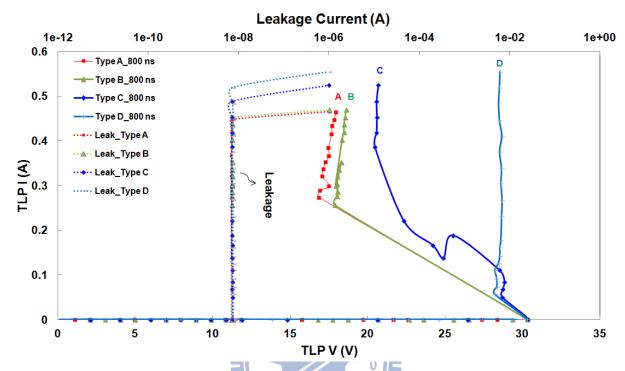

| Fig. 3.7        | The 200-ns TLP-measured I-V characteristics of 2-PMOSs with different                                                     |

|           | guard-ring layouts85                                                       |

|-----------|----------------------------------------------------------------------------|

| Fig. 3.8  | The 500-ns TLP-measured I-V characteristics of 2-PMOSs with different      |

|           | guard-ring layouts86                                                       |

| Fig. 3.9  | The 800-ns TLP-measured I-V characteristics of 2-PMOSs with different      |

|           | guard-ring layouts87                                                       |

| Fig. 3.10 | The TLP-measured I-V characteristics of 2-PMOSs_type A with different      |

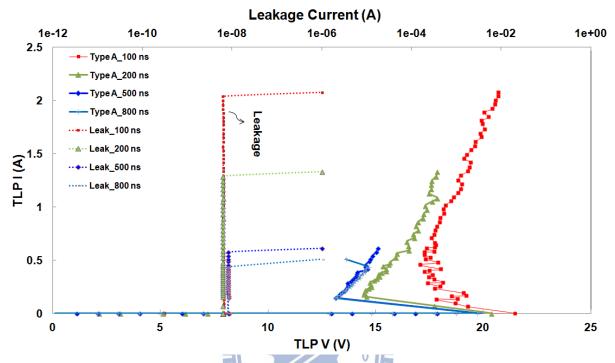

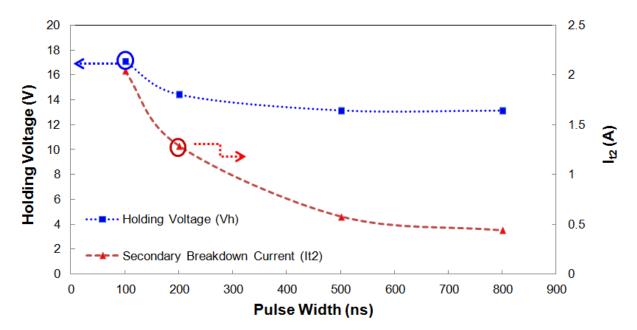

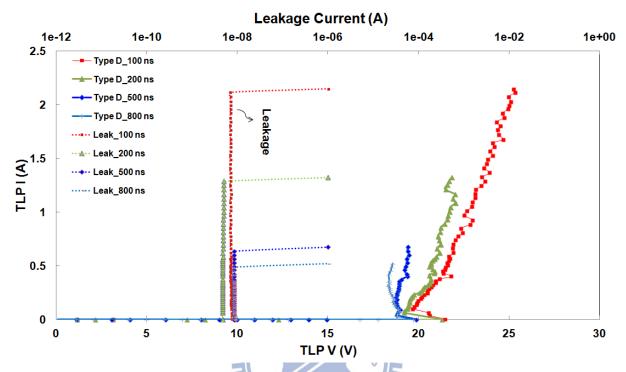

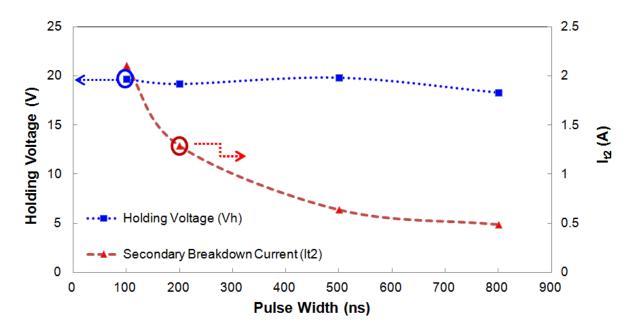

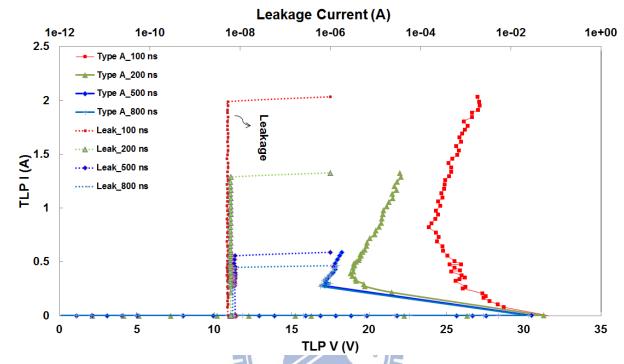

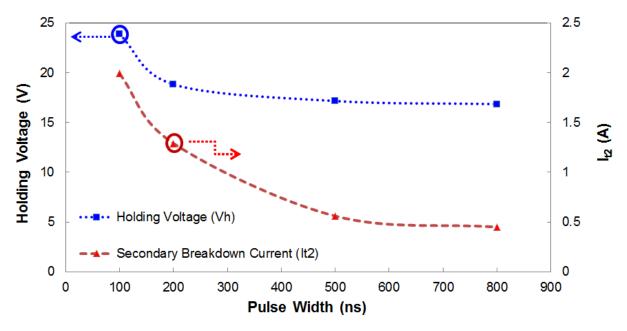

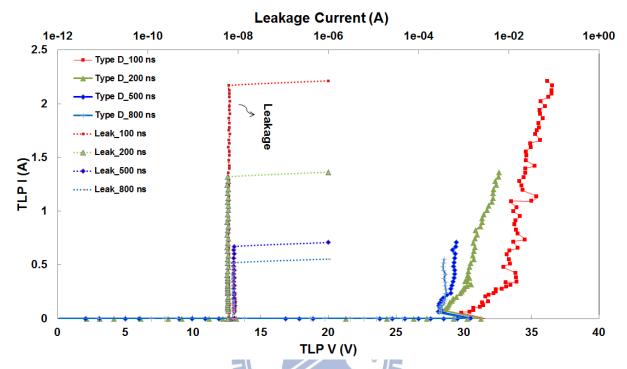

|           | TLP pulse widths88                                                         |

| Fig. 3.11 | The $V_h$ and $I_{t2}$ of 2-PMOSs_type A with different TLP pulse widths88 |

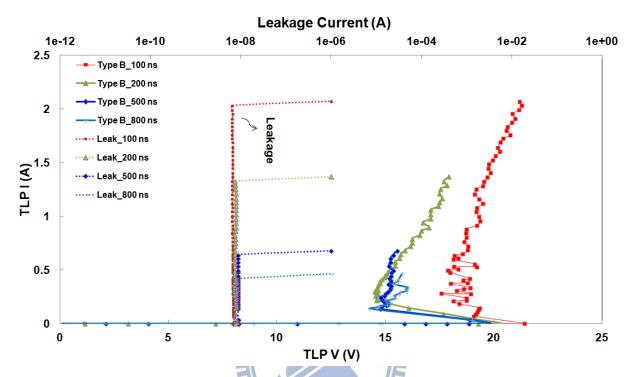

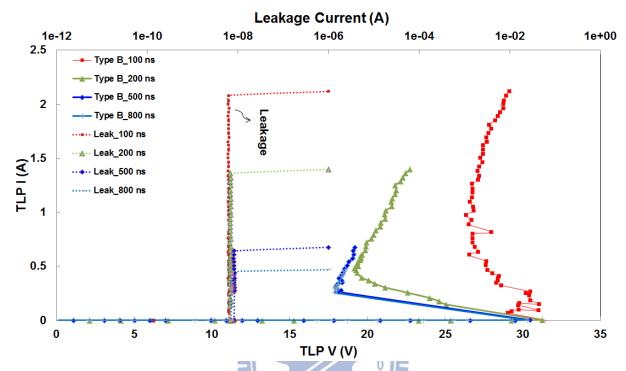

| Fig. 3.12 | The TLP-measured I-V characteristics of 2-PMOSs_type B with different      |

|           | TLP pulse widths89                                                         |

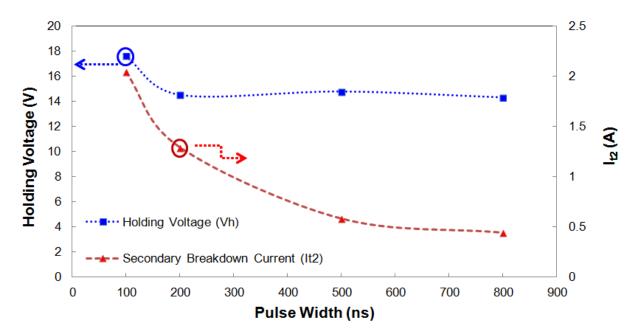

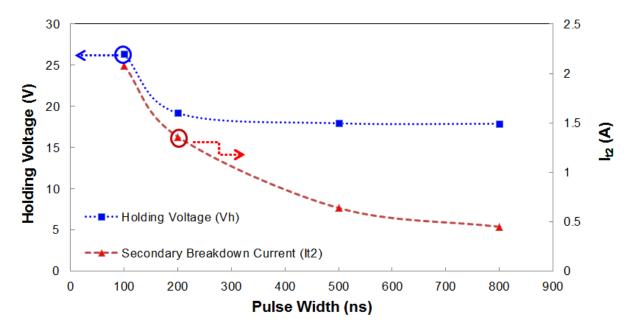

| Fig. 3.13 | The $V_h$ and $I_{t2}$ of 2-PMOSs_type B with different TLP pulse widths89 |

| Fig. 3.14 | The TLP-measured I-V characteristics of 2-PMOSs_type C with different      |

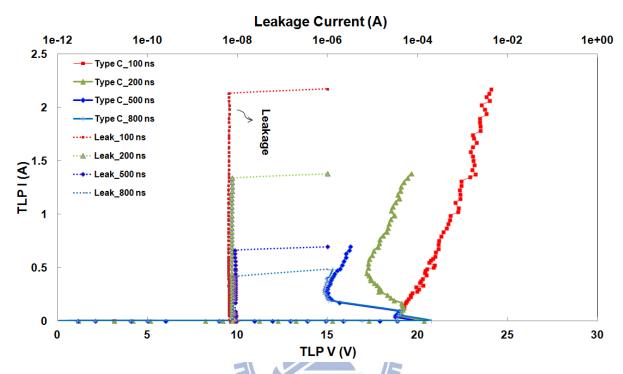

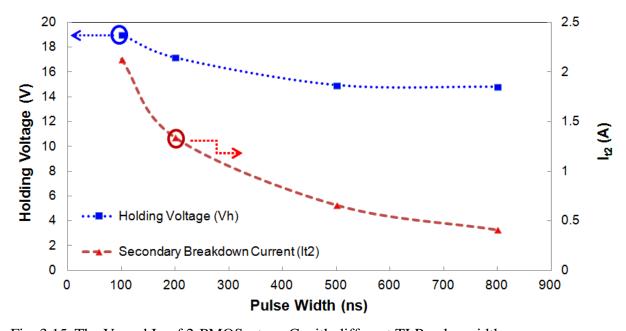

|           | TLP pulse widths90                                                         |

| Fig. 3.15 | The $V_h$ and $I_{t2}$ of 2-PMOSs_type C with different TLP pulse widths90 |

| Fig. 3.16 | The TLP-measured I-V characteristics of 2-PMOSs_type D with different      |

|           | TLP pulse widths91                                                         |

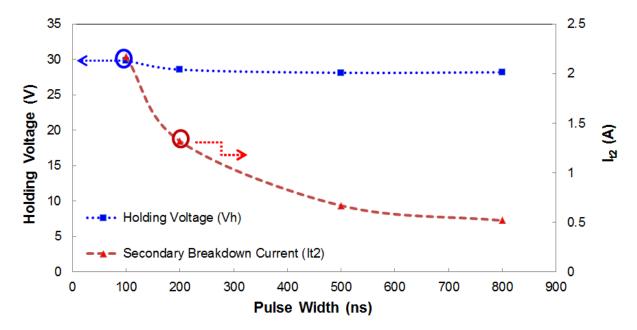

| Fig. 3.17 | The $V_h$ and $I_{t2}$ of 2-PMOSs_type D with different TLP pulse widths91 |

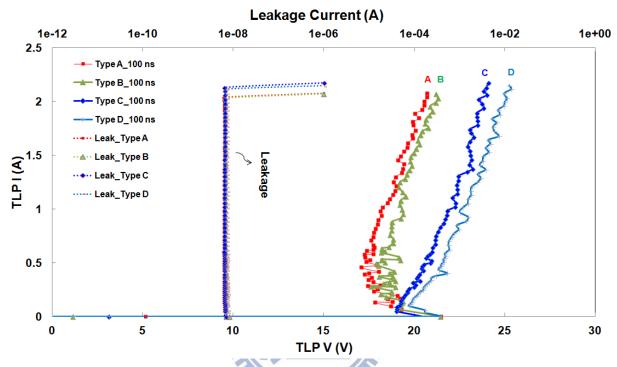

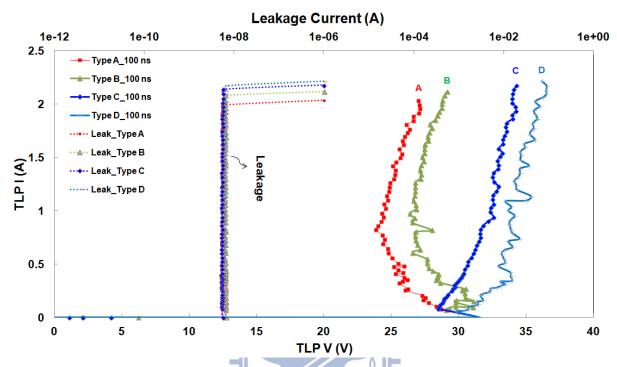

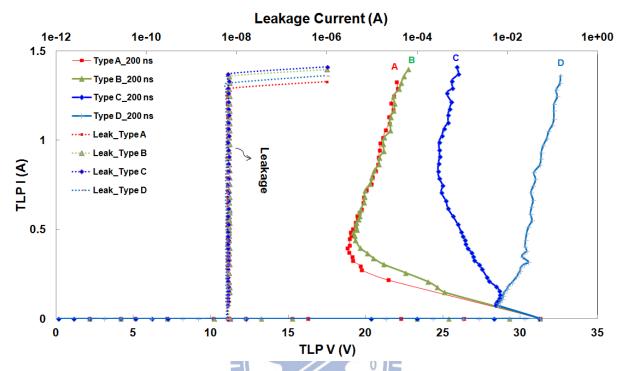

| Fig. 3.18 | The 100-ns TLP-measured I-V characteristics of 3-PMOSs with different      |

|           | guard-ring layouts92                                                       |

| Fig. 3.19 | The 200-ns TLP-measured I-V characteristics of 3-PMOSs with different      |

|           | guard-ring layouts93                                                       |

| Fig. 3.20 | The 500-ns TLP-measured I-V characteristics of 3-PMOSs with different      |

|           | guard-ring layouts94                                                       |

| Fig. 3.21 | The 800-ns TLP-measured I-V characteristics of 3-PMOSs with different      |

|           | guard-ring layouts95                                                       |

| Fig. 3.22 | The TLP-measured I-V characteristics of 3-PMOSs_type A with different      |

|           | TLP pulse widths96                                                         |

| Fig. 3.23 | The $V_h$ and $I_{t2}$ of 3-PMOSs_type A with different TLP pulse widths96 |

| Fig. 3.24 | The TLP-measured I-V characteristics of 3-PMOSs_type B with different      |

|           | TLP pulse widths97                                                         |

| Fig. 3.25 | The $V_h$ and $I_{t2}$ of 3-PMOSs_type B with different TLP pulse widths97 |

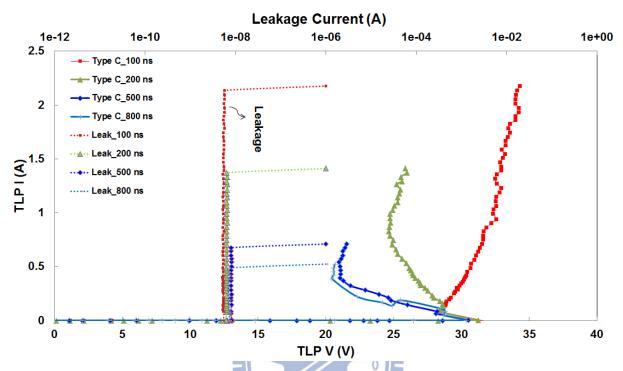

| Fig. 3.26 | The TLP-measured I-V characteristics of 3-PMOSs_type C with different      |

|           | TLP pulse widths98                                                         |

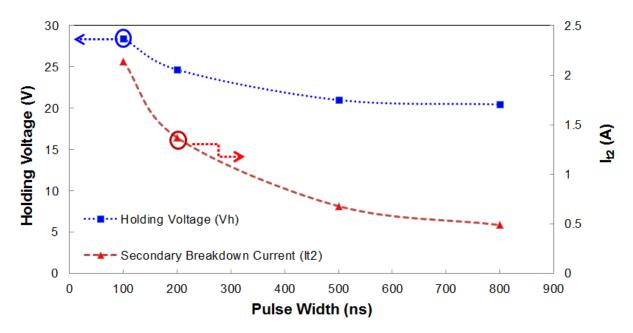

| Fig. 3.27 | The $V_h$ and $I_{t2}$ of 3-PMOSs_type C with different TLP pulse widths98 |

| Fig. 3.28 | The TLP-measured I-V characteristics of 3-PMOSs_type D with different      |

|           | TLP pulse widths99                                                         |

| Fig. 3.29 | The $V_h$ and $I_{t2}$ of 3-PMOSs_type D with different TLP pulse widths99 |

| Fig. 3.30 | The Tek370-measured I-V characteristics of 2-PMOSs with different          |

|           | guard-ring layouts100                                                      |

| Fig. 3.31 | The Tek370-measured I-V characteristics of 3-PMOSs with different            |       |

|-----------|------------------------------------------------------------------------------|-------|

|           | guard-ring layouts                                                           | 100   |

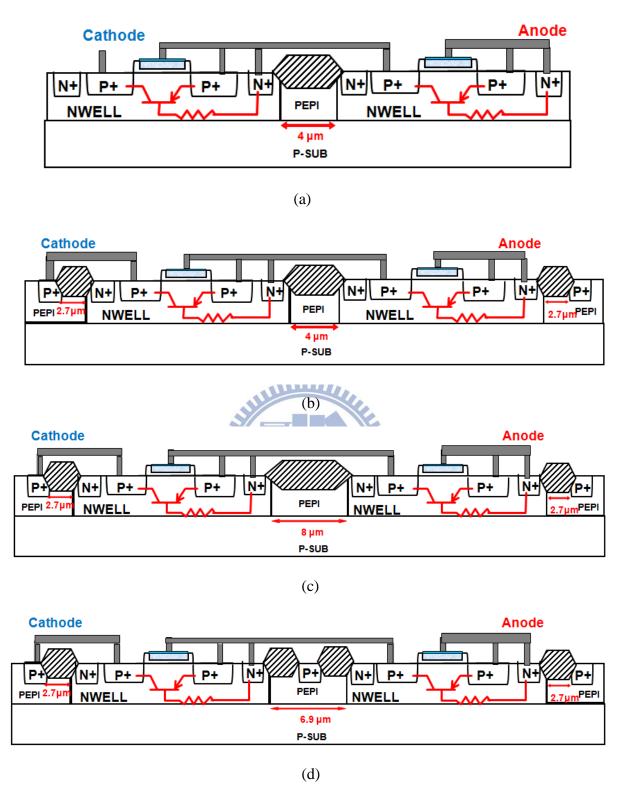

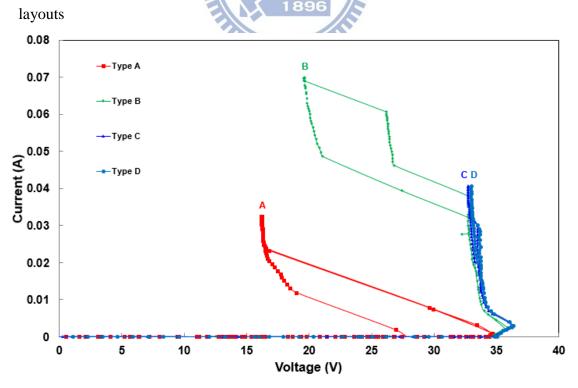

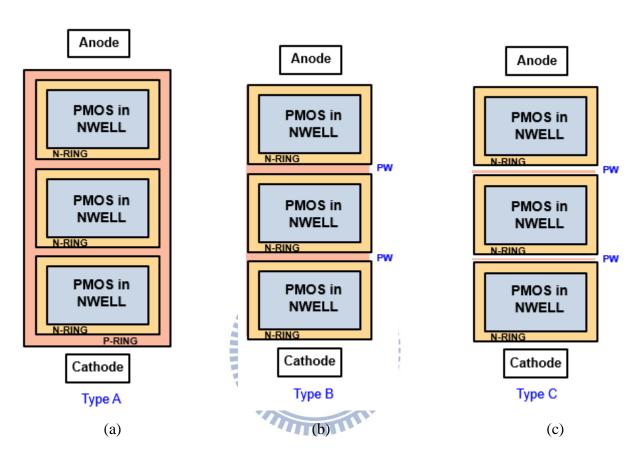

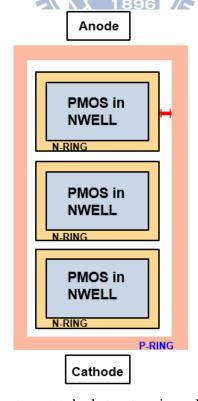

| Fig. 3.32 | The three types of guard-ring layout for 3-PMOSs stacked structure, (a       | )     |

|           | type A (typical), (b) type B, and (c) type C                                 | 103   |

| Fig. 3.33 | The schematic of 3-PMOSs in BCD process                                      | 103   |

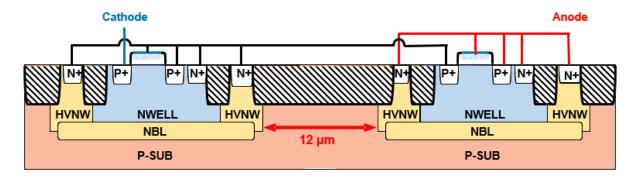

| Fig. 3.34 | The cross-sectional views of stacked structure with two LV PMOSs draw        | wn    |

|           | (a) type A (typical), (b) type B (12μm), and (c) type C (12μm)               |       |

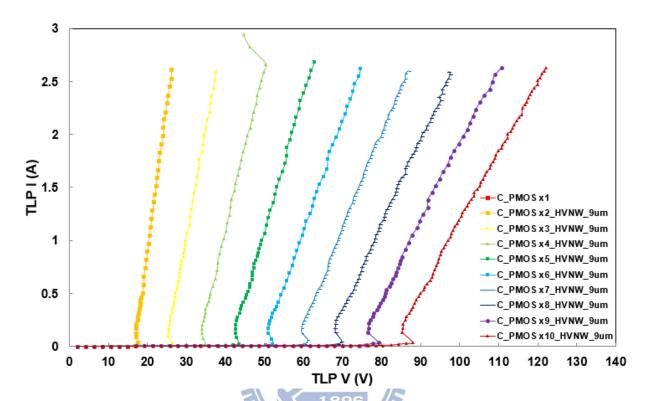

| Fig. 3.35 | The TLP-measured I-V characteristics of type A (typical stacked LV           |       |

|           | PMOSs)                                                                       | 106   |

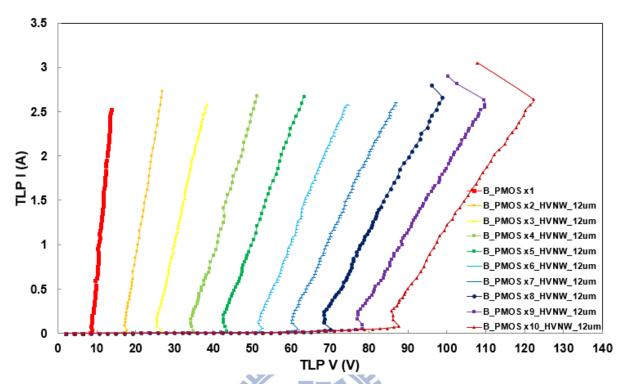

| Fig. 3.36 | The TLP-measured I-V characteristics of type B (12μm)                        | 107   |

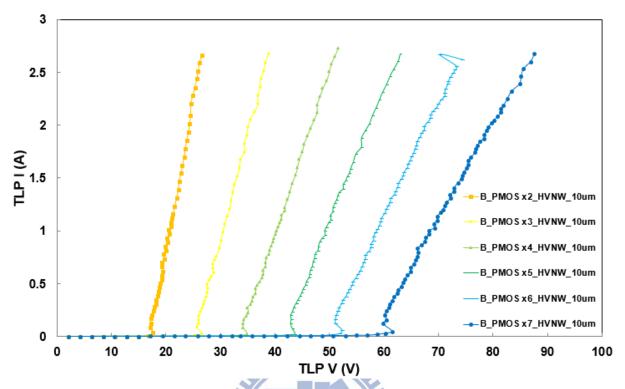

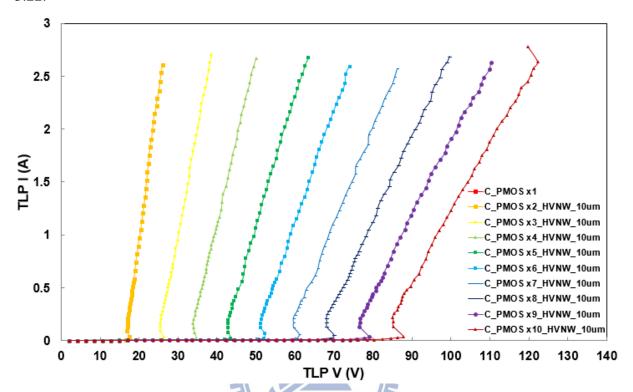

| Fig. 3.37 | The TLP-measured I-V characteristics of type B (10μm)                        |       |

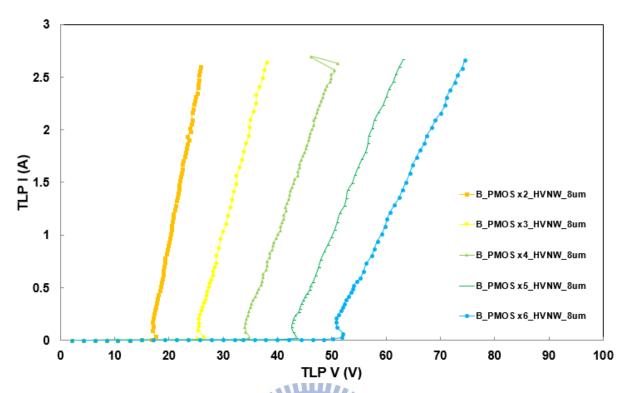

| Fig. 3.38 | The TLP-measured I-V characteristics of type B (8µm)                         |       |

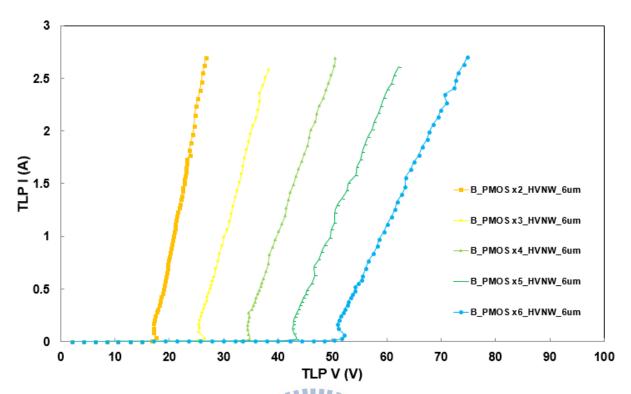

| Fig. 3.39 | The TLP-measured I-V characteristics of type B (6μm)                         |       |

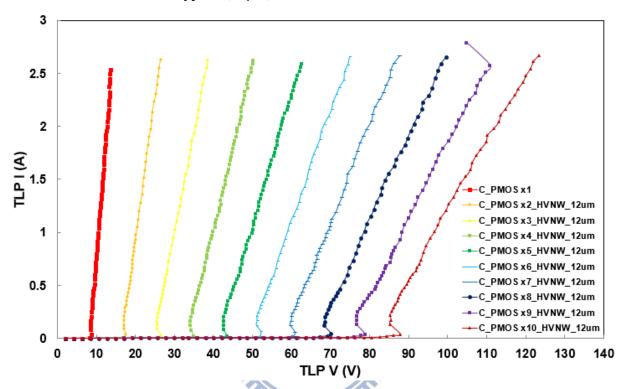

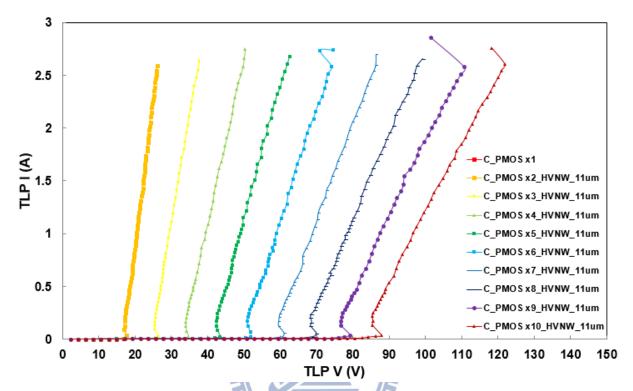

| Fig. 3.40 | The TLP-measured I-V characteristics of type C (12μm)                        |       |

| Fig. 3.41 | The TLP-measured I-V characteristics of type C (11μm)                        |       |

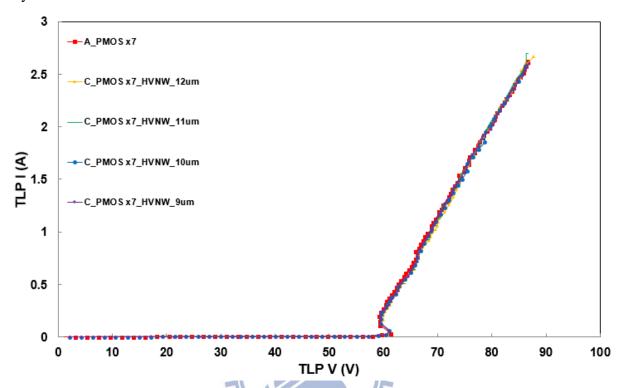

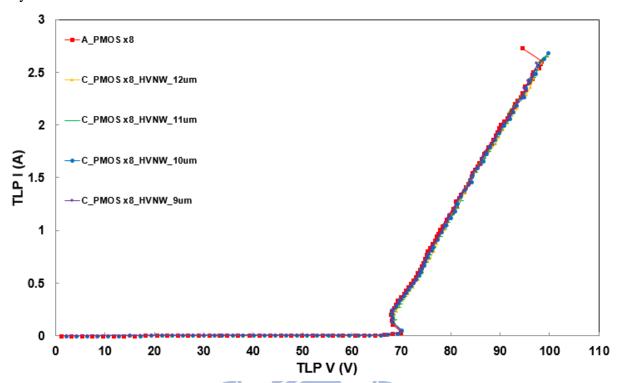

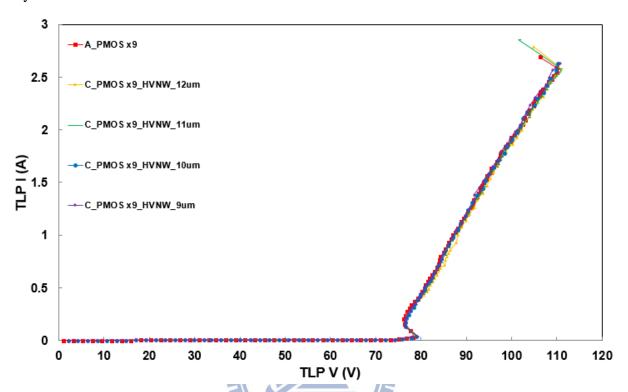

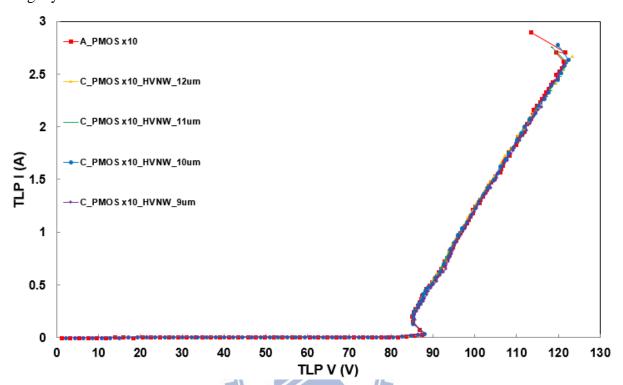

| Fig. 3.42 | The TLP-measured I-V characteristics of type C (10μm)                        |       |

| Fig. 3.43 | The TLP-measured I-V characteristics of type C (9µm)                         |       |

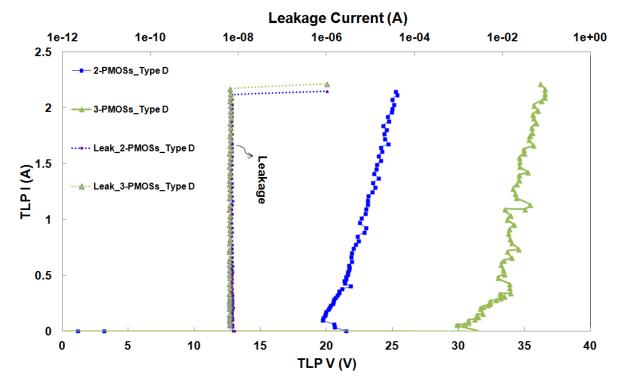

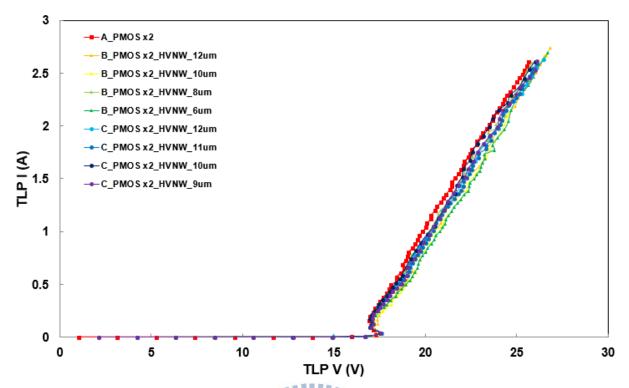

| Fig. 3.44 | The TLP-measured I-V characteristics of 2-PMOSs with different types         |       |

|           | layout                                                                       |       |

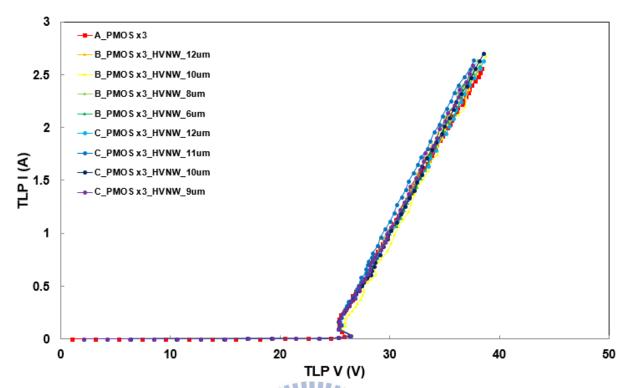

| Fig. 3.45 | The TLP-measured I-V characteristics of 3-PMOSs with different types         |       |

|           | layout                                                                       |       |

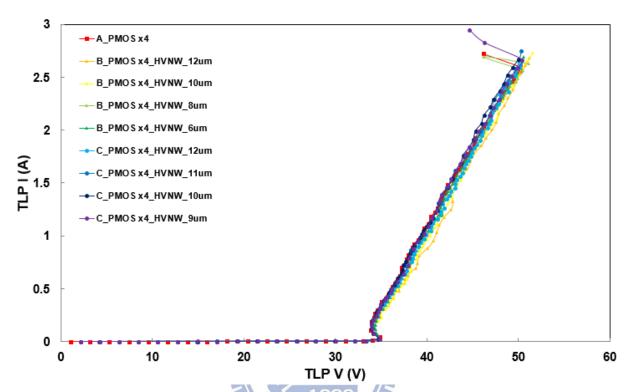

| Fig. 3.46 | The TLP-measured I-V characteristics of 4-PMOSs with different types         |       |

|           | layout                                                                       |       |

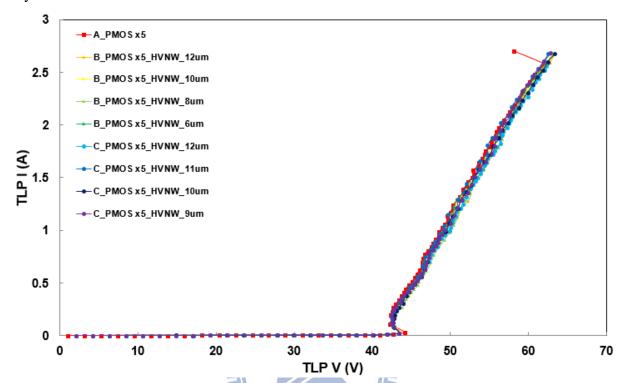

| Fig. 3.47 | The TLP-measured I-V characteristics of 5-PMOSs with different types         | of    |

|           | layout                                                                       | 120   |

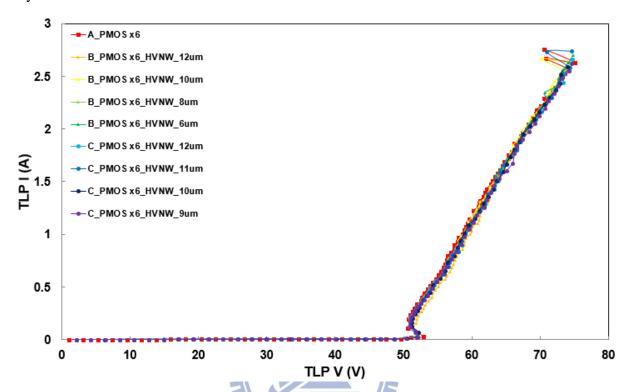

| Fig. 3.48 | The TLP-measured I-V characteristics of 6-PMOSs with different types         | of    |

|           | layout                                                                       | 121   |

| Fig. 3.49 | The TLP-measured I-V characteristics of 7-PMOSs with different types         | of    |

|           | layout                                                                       | 122   |

| Fig. 3.50 | The TLP-measured I-V characteristics of 8-PMOSs with different types         | of    |

|           | layout                                                                       | 123   |

| Fig. 3.51 | The TLP-measured I-V characteristics of 9-PMOSs with different types         | of    |

|           | layout                                                                       | 124   |

| Fig. 3.52 | The TLP-measured I-V characteristics of 10-PMOSs with different type         | es of |

| J         | layout                                                                       |       |

| Fig. 3.53 | The $V_h$ and $I_{t2}$ of stacked PMOSs with the type A of guard ring layout |       |

| Fig. 3.54 | The $V_h$ and $I_{t2}$ of stacked PMOSs with the type B of guard ring layout |       |

| Fig. 3.55 | The $V_h$ and $I_{t2}$ of stacked PMOSs with the type C of guard ring layout |       |

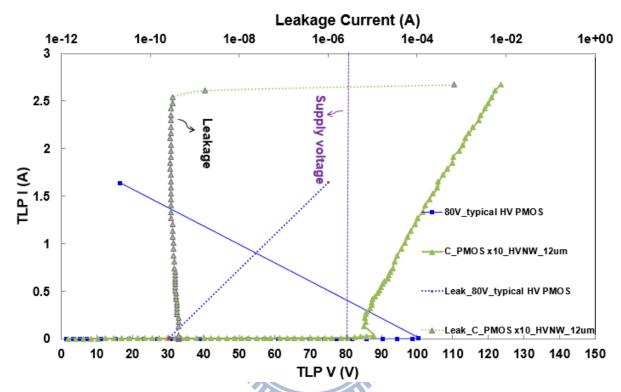

| Fig. 3.56 | The TLP-measured I-V characteristics of 60V ESD devices                      |       |

| Fig. 3.57 | The TLP-measured I-V characteristics of 80V ESD devices131                 |

|-----------|----------------------------------------------------------------------------|

| Fig. 4.1  | The cross-sectional views of new type stacked structure with two LV        |

|           | PMOSs drawn134                                                             |

| Fig. 4.2  | The top view of new type stacked structure in real circuit application 134 |

## **Chapter 1**

#### Introduction

In this chapter, the motivation of this thesis is depicted first. The chapter shows the advantage of stacking in high-voltage (HV) applications, and different guard-ring layout types can achieve both of good ESD robustness and high latchup-free immunity with reasonable total layout area. Electrostatic discharge (ESD) protection scheme reveals the typical arrangement for integrated circuits (ICs). It also introduces the concerns of ESD protection design and testing methods. Finally, thesis organization is included in the end of this chapter.

#### 1.1 Motivation

Electrostatic discharge (ESD) may occur accidentally to cause damages on IC products during the fabrication, package, and assembling processes, which often caused serious damages on ICs. High-voltage (HV) ICs were found with bad ESD robustness [1]-[2].

Lateral DMOS (LDMOS) was often used as ESD protection device in HV process, but the holding voltage ( $V_h$ ) of LDMOS after snapback was smaller than the circuit operating voltage ( $V_{CC}$ ) [3]-[4]. Thus, the LDMOS was sensitive to latchup issue. Therefore, the stacked configuration of LV devices is a way to achieve a high holding voltage for ESD protection in HV circuits [5]-[7]. It is suggested that ICs should require 2kV in human body model (HBM) and 200V in machine model (MM) [8], [9].

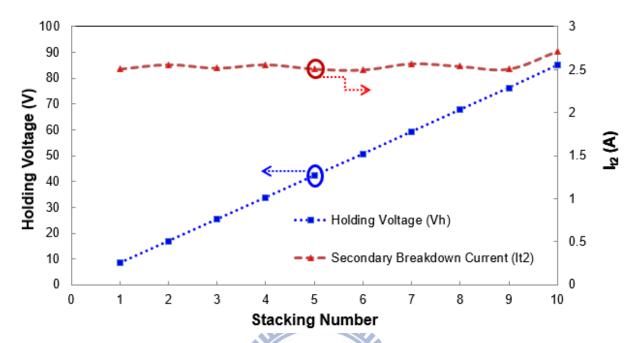

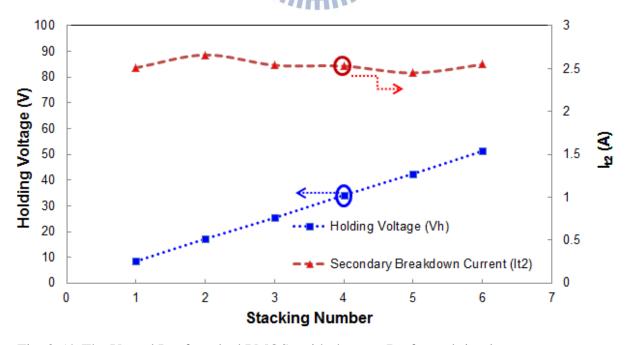

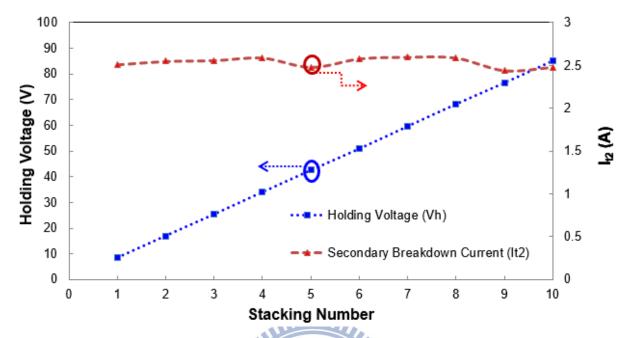

Stacking low-voltage devices is an excellent solution for latchup immunity and ESD robustness. The total holding voltage of stacked PMOSs is the multiple of the holding voltage of single PMOS. The total trigger voltage ( $V_{t1}$ ) of stacked PMOSs is also the multiple of the trigger voltage of single PMOS. The secondary breakdown current ( $I_{t2}$ ) of stacked PMOSs are almost the same in spite of different stacking numbers [10]. The main layout parameters to

affect ESD robustness of CMOS devices are the channel width, the channel length, the clearance from contact to poly-gate edge at drain and source regions, the spacing from the drain diffusion to the guard-ring diffusion, and the finger width of each unit finger. The optimized layout parameters have been verified to effectively improve ESD robustness of CMOS devices [11]. Try to use different layout methods to improve ESD robustness on stacking low-voltage devices effectively. In addition, the ESD devices should be surrounded by the guard ring in real circuit application. The ESD device without the guard ring can reduce the layout area, but it might cause the latchup issue under the normal circuit operation.

#### 1.2 ESD Protection Scheme in High-Voltage Integrated Circuits

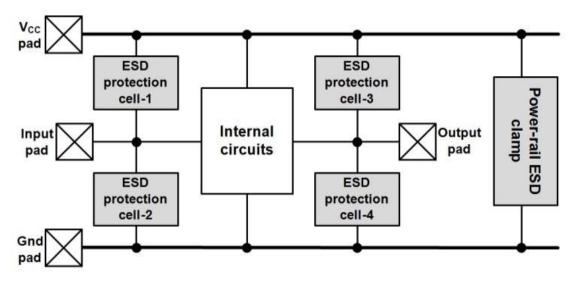

A typical whole-chip ESD protection scheme is shown in Fig. 1.1. The ESD stresses on each I/O pin have four stress modes of pin combination with the relatively grounded GND pin or VDD/VCC pin [12]. The ESD stresses could also happen from the VCC pin to the GND pin with positive or negative voltage pulses [12]. Stacked devices can be the ESD protection cells at the input or output pads or the power-rail ESD clamp between the VCC/GND power lines.

Fig. 1.1 A typical whole-chip ESD protection scheme

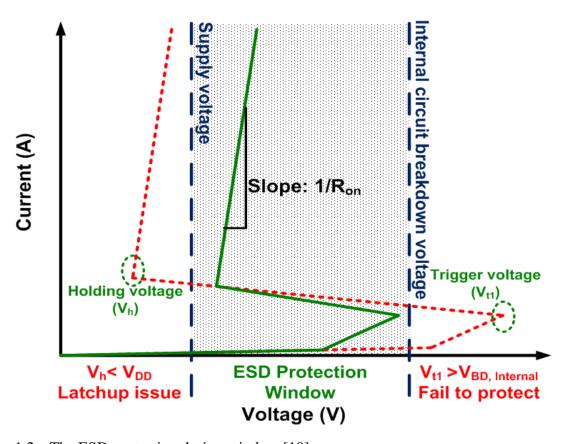

The typical I-V characteristics of ESD protection devices are illustrated in Fig. 1.2.

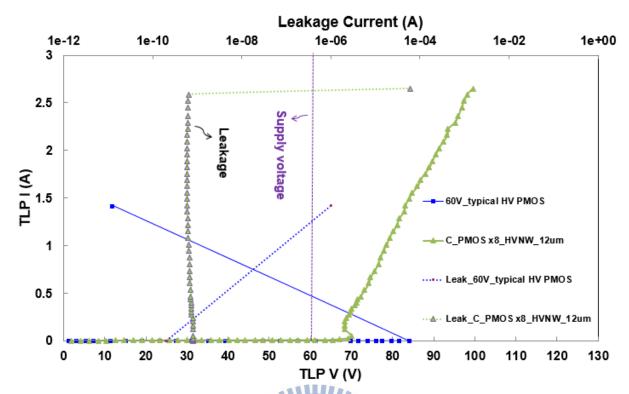

Breakdown voltage ( $V_{BD}$ ) and supply voltage ( $V_{DD}$  or  $V_{CC}$ ) of the internal circuits divide the plot into three parts. The middle part is the desired ESD protection window. The green curve is an example of the desired ESD device's I-V characteristics. To get an effective ESD protection, the trigger voltage ( $V_{t1}$ ) should be smaller than breakdown voltage of the internal circuits. Furthermore, to avoid latchup issue, the holding voltage ( $V_h$ ) should be larger than the supply voltage of the internal circuits. The on-resistance of an ESD protection device should be as small as possible to get a high ESD robustness. The I-V characteristics of ESD devices should fit into this window for both effective ESD protection and latchup-free design.

Fig. 1.2 The ESD protection design window [10]

#### 1.3 Measurement Methods

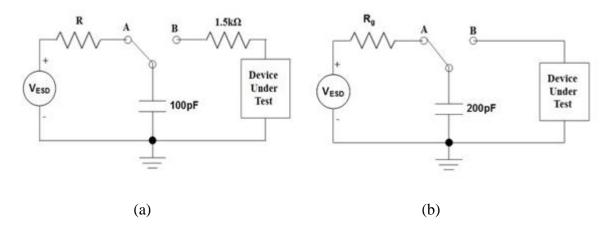

ESD could induce serious yield > loss in ICs. Change may accumulate in human bodies and machines. When one pin connected to ground, the ESD current may damage ICs. It is suggested that ICs should require 2kV in human body model (HBM) and 200V in machine

model (MM). There are several ways to test ESD robustness. The equivalent models of HBM and MM are illustrated in Fig. 1.3.

Fig. 1.3 Equivalent circuits of (a) HBM and (b) MM

Transmission line pulse (TLP) system can measure the ESD-related device parameters for ESD protection design. The Barth pulse curve tracer 4002 TLP is used to measure the TLP I-V curve. It is common to use 100-ns pulse width. It can be obtained device parameters such as trigger voltage  $(V_{t1})$ , holding voltage  $(V_{b})$ , secondary breakdown current  $(I_{t2})$  and on-resistance  $(R_{on})$  from TLP I-V curve. Higher secondary breakdown current usually means a higher ESD level.

The holding voltage of n-channel LDMOS in an HV BCD process has been investigated by TLP measurements with different pulse widths and dc curve tracer. It is found that the holding voltages of an n-channel LDMOS measured by 100-ns TLP system and curve tracer are substantially different [13]. The I-V curve of the long pulse width TLP measured by TLP celestron-1 in this thesis. The TLP I-V curve can be measured by 100-ns, 200-ns, 500-ns and 800-ns pulse width. The I-V curve can be measured by curve tracer Tek370 in a dc condition. During latchup test, the positive or negative current of up to 200mA will be directly applied to the I/O pin [14]. Such latchup-test current will be injected into the substrate through the on-chip ESD device that is often drawn with the I/O pad together to provide ESD protection.

#### 1.4 Thesis Organization

This thesis focuses on optimization of stacked low-voltage devices for good ESD robustness and latchup immunity. In chapter 1, it introduces research motivation, measurement methods and an ESD protection scheme.

It describes the dependence of layout parameters on ESD robustness of stacked LV PMOSs in chapter 2. Chapter 3 shows stacked PMOSs with different guard ring layouts for HV ESD protection. In this thesis, the stacked LV PMOS devices have been successfully verified in a VIS 0.5-μm HV process and 0.25-μm 80V BCD process. In chapter 4, conclusions and future work.

## Chapter 2

# Layout Optimization on the Stacked Low-Voltage PMOS for High-Voltage ESD Protection

Stacking is a good way to reach high holding voltage for high-voltage ESD protection. The trigger voltage and the holding voltage of stacked configuration can be adjusted to meet different HV applications. In this chapter, the dependence of layout parameters on ESD robustness of stacked LV PMOSs. In this work, the stacked LV PMOS devices have been successfully verified in a VIS 0.5-µm HV process and 0.25-µm 80V BCD process.

### 2.1 Stacked Low-Voltage PMOS in a 0.5-µm HV Process

#### 2.1.1 Stacking Units

1896

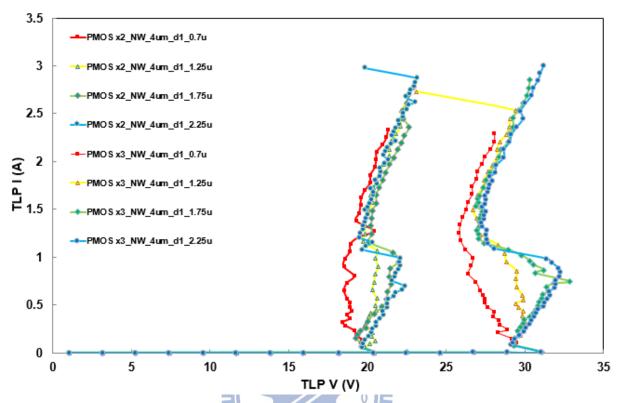

A PMOS was fabricated in a 0.5- $\mu$ m HV process, which has a device dimension of W/L = 800 $\mu$ m/0.5 $\mu$ m. The equivalent circuits are showed in Fig. 2.1. The stacked LV PMOSs with two and three stacking numbers are investigated in this work, which are designed to meet 20-V and 30-V HV applications. There are four different stacking units, the spacing from drain contact to poly-gate edge (d1) of PMOS devices are investigated through the fabricated test chips. The cross-section view of PMOS stacking units are showed in Fig. 2.2. The d1 spacing of stacking units are drawn with 0.7 $\mu$ m, 1.25 $\mu$ m, 1.75 $\mu$ m, and 2.25 $\mu$ m in Fig. 2(a), Fig. 2(b), Fig. 2(c) and Fig. 2(d).

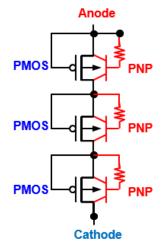

Fig. 2.1 Equivalent circuits of (a) a single LV PMOS and (b) stacked LV PMOSs structure

Fig. 2.2 The cross-section views of PMOS stacking unit drawn with (a) the drain contact to poly-gate edge (d1) spacing of  $0.7\mu m$ , (b) the d1 spacing of  $1.25\mu m$ , (c) the d1 spacing of  $1.75\mu m$ , and (d) the d1 spacing of  $1.25\mu m$

#### 2.1.2 Device Types

The ESD devices should be surrounded by the guard ring in real circuit application. These four kinds of devices have different types of the guard ring layouts. There are two types (type one and type two) of the guard ring layouts to surround the stacked PMOSs, as shown in Fig. 2.3, where 3-PMOSs stacked structure is demonstrated. In type one and type two, the stacked PMOSs were surrounded by one P-ring that is typically connected to cathode. The NWELL spacing between each N-well in the type one (type two) is 4µm (8µm). The clearance of P-ring to the N-well edge is kept at 2.7µm, which is a layout rule specified by the foundry in the given 0.5-µm process.

Fig. 2.3 The two types of guard-ring layout for 3-PMOSs stacked structure, (a) with one whole p-ring and NWELL spacing of 4μm and (b) with one whole p-ring and NWELL spacing of 8μm

Each LV PMOS in the stacked configuration is drawn with the total channel width of 800μm and a channel length of 0.5μm. The cross-sectional view of stacked structure with two LV PMOSs is shown in Fig. 2.4. The NWELL spacings of the two LV PMOSs are drawn with 4μm and 8μm in Fig. 2.4(a) and Fig. 2.4(b), respectively. The gate of each PMOS is connected to its local high potential point, so each PMOS in the stacked structure is kept in the off state during the normal circuit operation. The P+ diffusion (drain) of the bottom PMOS in the stacked PMOSs is connected to the cathode. The P-ring is connected to the cathode, which is typically biased at ground with the common p-substrate.

Fig. 2.4 The cross-sectional views of stacked structure with two LV PMOSs drawn with (a) the NWELL spacing of 4μm (type one) and (b) the NWELL spacing of 8μm (type two). Each LV PMOS has its own separated N-well in the stacked structure

#### 2.1.3 Experiment Results

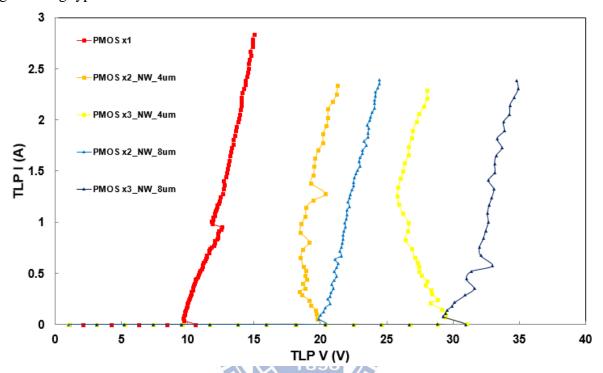

All test devices of stacked PMOSs had been fabricated in a 0.5-µm HV process. Each PMOS in all stacked structure is drawn with a channel width of 800µm and a channel length

of 0.5μm. Every layout type has 2-PMOSs and 3-PMOSs stacked structures. The TLP-measured I-V characteristics of device 1 with the two types of guard ring layout are shown in Fig. 2.5. The detailed characteristics of device 1 stacked structure with different guard-ring types are listed in Table 2.1.

Fig. 2.5 The TLP-measured I-V characteristics of device 1 with different guard-ring layouts

Table 2.1

The measurement data of device 1

| d1 is 0.7 μm   |                     | TLP                   |                        |                     |           | ESD (*)     |           |

|----------------|---------------------|-----------------------|------------------------|---------------------|-----------|-------------|-----------|

|                | V <sub>t1</sub> (V) | V <sub>h</sub><br>(V) | R <sub>on</sub><br>(Ω) | I <sub>t2</sub> (A) | BV<br>(V) | HBM<br>(kV) | MM<br>(V) |

| PMOS x1        | 10.57               | 9.68                  | 1.91                   | 2.79                | 11.1      | 5.5         | 250       |

| PMOS x2_NW_4µm | 20.39               | 18.41                 | 1.44                   | 2.25                | 20.5      | 4.5         | 300       |

| PMOS x3_NW_4µm | 31.02               | 25.81                 | 2.32                   | 2.21                | 34        | 4.5         | 300       |

| PMOS x2_NW_8µm | 20.4                | 19.88                 | 1.98                   | 2.35                | 22.1      | 4.5         | 300       |

| PMOS x3_NW_8µm | 30.99               | 29.27                 | 2.54                   | 2.3                 | 33.5      | 4.5         | 300       |

#DC BV:  $I = 1\mu A$  \*ESD failure criteria: I-V curve shift > 10%

In Table 2.1, the trigger voltage of stacked PMOSs is the multiple of the trigger voltage of single PMOS, but the holding voltage of type one is smaller than type two. It will be discussed about guard-ring layout in the chapter 3. The breakdown voltage of stacked PMOSs

is the multiple of the breakdown voltage of single PMOS. The breakdown voltage is defined the off current equal  $1\mu A$  in DC measurement. All of stacked structure with two guard-ring types can pass 4.5 kV in the human-body-model (HBM) ESD test and 300 V in the machine-model (MM) ESD test.

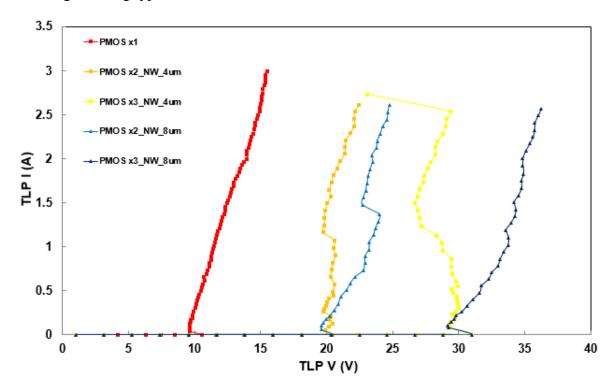

The TLP-measured I-V characteristics of device 2 with the two types of guard ring layout are shown in Fig. 2.6. The detailed characteristics of device 2 stacked structure with different guard-ring types are listed in Table 2.2.

Fig. 2.6 The TLP-measured I-V characteristics of device 2 with different guard-ring layouts

Table 2.2

The measurement data of device 2

| d1 is 1.25 µm  | TLP                 |                       |                        |                     | DC (#)    | ESD (*)     |           |

|----------------|---------------------|-----------------------|------------------------|---------------------|-----------|-------------|-----------|

|                | V <sub>t1</sub> (V) | V <sub>h</sub><br>(V) | R <sub>on</sub><br>(Ω) | I <sub>t2</sub> (A) | BV<br>(V) | HBM<br>(kV) | MM<br>(V) |

| PMOS x1        | 10.59               | 9.62                  | 2.02                   | 2.95                | 11.1      | 6           | 300       |

| PMOS x2_NW_4µm | 20.43               | 19.74                 | 1.75                   | 2.54                | 20.4      | 5           | 300       |

| PMOS x3_NW_4µm | 31.02               | 26.69                 | 2.62                   | 2.53                | 30.9      | 5           | 300       |

| PMOS x2_NW_8µm | 20.34               | 19.61                 | 2.05                   | 2.52                | 22.3      | 5           | 300       |

| PMOS x3_NW_8µm | 30.98               | 29.17                 | 2.88                   | 2.49                | 34        | 5           | 300       |

#DC BV:  $I = 1\mu A$  \*ESD failure criteria: I-V curve shift > 10%

The TLP-measured I-V characteristics of device 3 with the two types of guard ring layout are shown in Fig. 2.7. The detailed characteristics of device 3 stacked structure with different guard-ring types are listed in Table 2.3.

Fig. 2.7 The TLP-measured I-V characteristics of device 3 with different guard-ring layouts

Table 2.3

The measurement data of device 3

| d1 is 1.75 µm  | TLP                    |                       |                        |                     | DC (#)    | ESI         | O (*)     |

|----------------|------------------------|-----------------------|------------------------|---------------------|-----------|-------------|-----------|

|                | V <sub>t1</sub><br>(V) | V <sub>h</sub><br>(V) | R <sub>on</sub><br>(Ω) | I <sub>t2</sub> (A) | BV<br>(V) | HBM<br>(kV) | MM<br>(V) |

| PMOS x1        | 10.57                  | 9.68                  | 2.14                   | 3.12                | 10.1      | 6           | 300       |

| PMOS x2_NW_4µm | 20.38                  | 19.26                 | 1.29                   | 2.69                | 20.4      | 5           | 300       |

| PMOS x3_NW_4µm | 31.09                  | 26.85                 | 2.74                   | 2.77                | 34        | 5.5         | 300       |

| PMOS x2_NW_8µm | 20.36                  | 19.57                 | 2.33                   | 2.81                | 22.3      | 5.5         | 300       |

| PMOS x3_NW_8µm | 30.91                  | 29.13                 | 3.05                   | 2.8                 | 34        | 5.5         | 300       |

#DC BV:  $I = 1\mu A$  \*ESD failure criteria: I-V curve shift > 10%

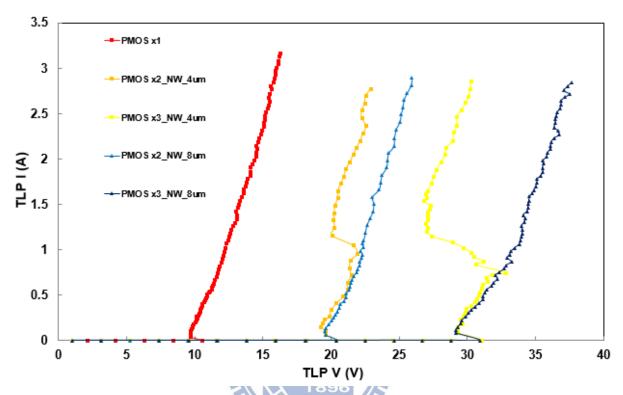

The TLP-measured I-V characteristics of device 4 with the two types of guard ring layout are shown in Fig. 2.8. The detailed characteristics of device 4 stacked structure with different guard-ring types are listed in Table 2.4.

Fig. 2.8 The TLP-measured I-V characteristics of device 4 with different guard-ring layouts

Table 2.4

The measurement data of device 4

| d1 is 2.25 µm  | TLP                    |                       |                        |                     | DC (#)    | ESD (*)     |           |

|----------------|------------------------|-----------------------|------------------------|---------------------|-----------|-------------|-----------|

|                | V <sub>t1</sub><br>(V) | V <sub>h</sub><br>(V) | R <sub>on</sub><br>(Ω) | I <sub>t2</sub> (A) | BV<br>(V) | HBM<br>(kV) | MM<br>(V) |

| PMOS x1        | 10.55                  | 9.76                  | 2.04                   | 3.25                | 10.1      | 6           | 300       |

| PMOS x2_NW_4µm | 20.36                  | 19.47                 | 2.2                    | 2.87                | 20.4      | 5.5         | 300       |

| PMOS x3_NW_4µm | 31.01                  | 27.24                 | 2.4                    | 2.92                | 34.5      | 5.5         | 300       |

| PMOS x2_NW_8µm | 20.35                  | 19.58                 | 2.49                   | 2.96                | 22.3      | 5.5         | 300       |

| PMOS x3_NW_8µm | 30.99                  | 29.18                 | 2.91                   | 3.23                | 33.9      | 5.5         | 350       |

#DC BV:  $I = 1\mu A$  \*ESD failure criteria: I-V curve shift > 10%

The TLP-measured I-V characteristics of the stacked 2-PMOSs and 3-PMOSs with the guard-ring layout type one (type two) are compared in Fig. 2.9 (Fig. 2.10). The detailed

characteristics of different devices with same type guard ring layout are listed in Table 2.5 and Table 2.6.

Fig. 2.9 The TLP-measured I-V characteristics of devices with guard-ring layout type one

Table 2.5

The measurement data of devices with guard-ring layout type one

| type one                  | TLP                    |                       |                        |                     | DC (#)    | ESD (*)     |           |

|---------------------------|------------------------|-----------------------|------------------------|---------------------|-----------|-------------|-----------|

|                           | V <sub>t1</sub><br>(V) | V <sub>h</sub><br>(V) | R <sub>on</sub><br>(Ω) | I <sub>t2</sub> (A) | BV<br>(V) | HBM<br>(kV) | MM<br>(V) |

| PMOS x2_NW_4μm_d1_0.7 μm  | 20.39                  | 18.41                 | 1.44                   | 2.25                | 20.5      | 4.5         | 300       |

| PMOS x2_NW_4μm_d1_1.25 μm | 20.43                  | 19.74                 | 1.75                   | 2.54                | 20.4      | 5           | 300       |

| PMOS x2_NW_4μm_d1_1.75 μm | 20.38                  | 19.26                 | 1.29                   | 2.69                | 20.4      | 5           | 300       |

| PMOS x2_NW_4μm_d1_2.25 μm | 20.36                  | 19.47                 | 2.2                    | 2.87                | 20.4      | 5.5         | 300       |

| PMOS x3_NW_4μm_d1_0.7 μm  | 31.02                  | 25.81                 | 2.32                   | 2.21                | 34        | 4.5         | 300       |

| PMOS x3_NW_4μm_d1_1.25 μm | 31.02                  | 26.69                 | 2.62                   | 2.53                | 30.9      | 5           | 300       |

| PMOS x3_NW_4μm_d1_1.75 μm | 31.09                  | 26.85                 | 2.74                   | 2.77                | 34        | 5.5         | 300       |

| PMOS x3_NW_4μm_d1_2.25 μm | 31.01                  | 27.24                 | 2.4                    | 2.92                | 34.5      | 5.5         | 300       |

#DC BV:  $I = 1\mu A$  \*ESD failure criteria: I-V curve shift > 10%

Fig. 2.10 The TLP-measured I-V characteristics of devices with guard-ring layout type two

Table 2.6

The measurement data of devices with guard-ring layout type two

| type two                  | TLP                 |                       |                        | DC (#)              | ESD (*)   |             |           |

|---------------------------|---------------------|-----------------------|------------------------|---------------------|-----------|-------------|-----------|

| · ·                       | V <sub>t1</sub> (V) | V <sub>h</sub><br>(V) | R <sub>on</sub><br>(Ω) | I <sub>t2</sub> (A) | BV<br>(V) | HBM<br>(kV) | MM<br>(V) |

| PMOS x2_NW_8μm_d1_0.7 μm  | 20.4                | 19.88                 | 1.98                   | 2.35                | 22.1      | 4.5         | 300       |

| PMOS x2_NW_8μm_d1_1.25 μm | 20.34               | 19.61                 | 2.05                   | 2.52                | 22.3      | 5           | 300       |

| PMOS x2_NW_8μm_d1_1.75 μm | 20.36               | 19.57                 | 2.33                   | 2.81                | 22.3      | 5.5         | 300       |

| PMOS x2_NW_8μm_d1_2.25 μm | 20.35               | 19.58                 | 2.49                   | 2.96                | 22.3      | 5.5         | 300       |

| PMO\$ x3_NW_8μm_d1_0.7 μm | 30.99               | 29.27                 | 2.54                   | 2.3                 | 33.5      | 4.5         | 300       |

| PMOS x3_NW_8μm_d1_1.25 μm | 30.98               | 29.17                 | 2.88                   | 2.49                | 34        | 5           | 300       |

| PMOS x3_NW_8μm_d1_1.75 μm | 30.91               | 29.13                 | 3.05                   | 2.8                 | 34        | 5.5         | 300       |

| PMOS x3_NW_8μm_d1_2.25 μm | 30.99               | 29.18                 | 2.91                   | 3.23                | 33.9      | 5.5         | 350       |

#DC BV:  $I = 1\mu A$  \*ESD failure criteria: I-V curve shift > 10%

From the experimental results, the larger d1 parameter can cause larger  $I_{t2}$  of stacked PMOS devices. From above results with TLP-measured  $I_{t2}$  and ESD test, the device 4 among is the best choice for the stacked PMOSs structure for HV ESD protection. All of device 4

with two guard-ring types can pass 5.5 kV in the human-body-model (HBM) ESD test and 300 V in the machine-model (MM) ESD test. The holding voltage of type one still suffers latchup risk for 20 V and 30 V application. During ESD zapping, the ESD current unpredictably trigger the other parasitic BJT of the ESD devices. It induces the holding voltage ( $V_h$ ) of type one smaller than the holding voltage ( $V_h$ ) of type two. Guard-ring layout will be discussed in the Chapter 3. The type two among is the best choice for the stacked PMOSs structure for HV ESD protection.

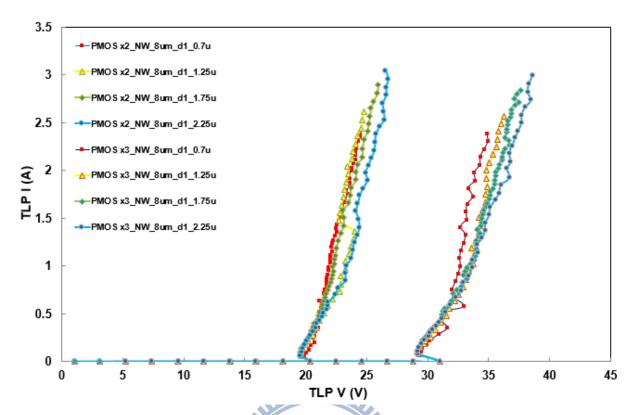

#### 2.2 Stacked Low-Voltage PMOS in a 0.25-µm BCD Process

#### 2.2.1 Typical Devices

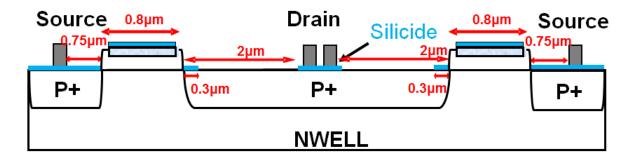

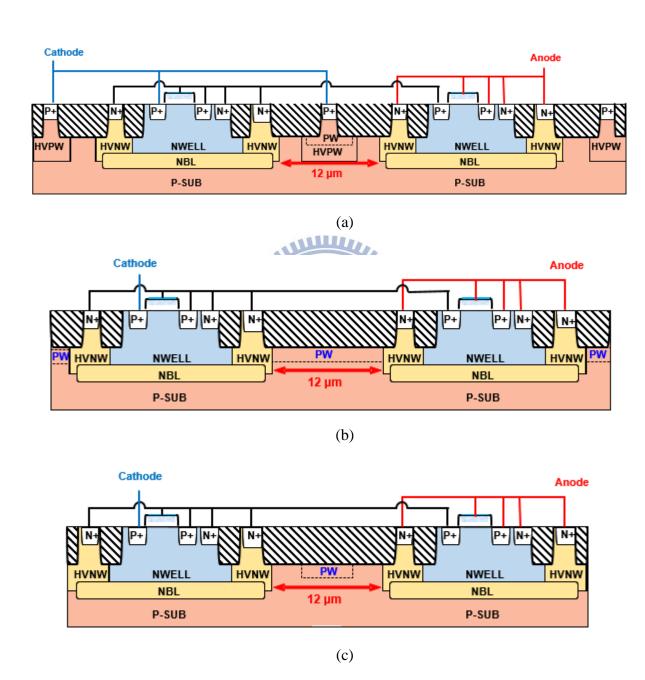

The test devices were all fabricated in a VIS 0.25-μm Bipolar-CMOS-DMOS (BCD) process. The main layout parameters to affect ESD robustness of ESD devices are the silicide blocking, the spacing from drain contact to poly-gate edge (d1), contact number, the channel length, and total width. The optimized layout parameters have been verified to effectively improve ESD robustness of ESD devices. Try to achieve this concept in stacked LV PMOS structure. Stacking number was from 1 to 10 in this test. Typical PMOS devices in this investigation, the clearance from the resist-protection-oxide (RPO) to poly-gate edge, the clearance from the drain contact to poly-gate edge (d1), the drain contact number (co), the channel length (L), the single finger width, and the total width are kept at 0.3μm, 2μm, 2, 0.8μm, 30μm ,and 360μm, respectively. The cross-section view of typical PMOS stacking unit is showed in Fig. 2.11.

Fig. 2.11 The cross-section view of typical PMOS

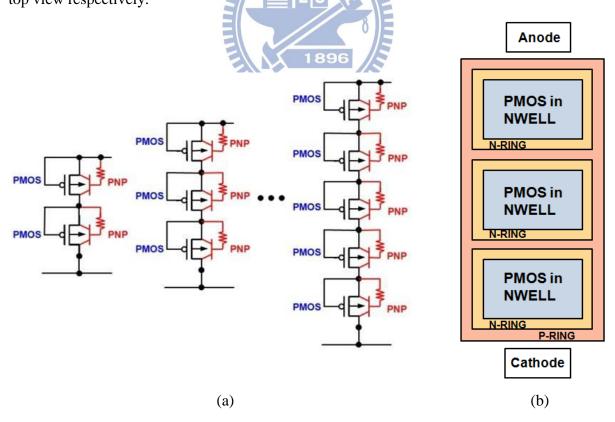

Low-voltage devices should be surrounded by isolation ring for HV applications. Isolation rings are composed by a HV-NWELL ring and a HV-PWELL ring. The P+ diffusion (drain) of the bottom PMOS in the stacked PMOSs is connected to the cathode. The HV-PWELL ring is connected to the cathode, which is typically biased at ground with the common p-substrate. The HV-NWELL ring is tied to relative high potential point. Fig. 2.12(a) and Fig. 2.12(b) show the schematic of stacked LV PMOSs for HV ESD protection and the top view respectively.

Fig. 2.12 The (a) schematic of stacked LV PMOSs with different stacking numbers and (b) top view for 3-PMOSs stacked structure

## 2.2.2 Layout Parameters of Test Devices

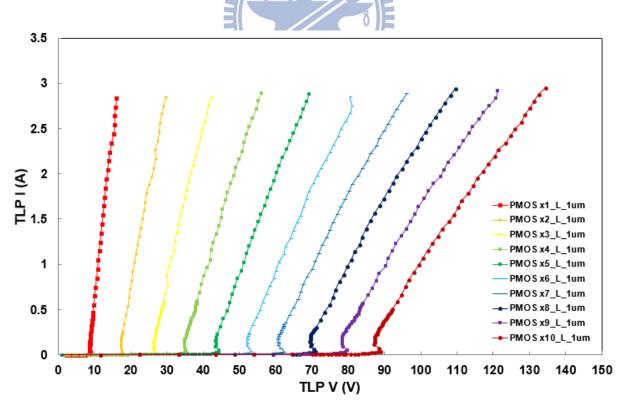

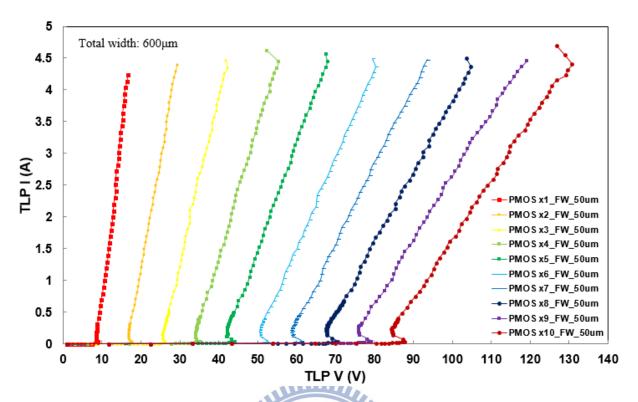

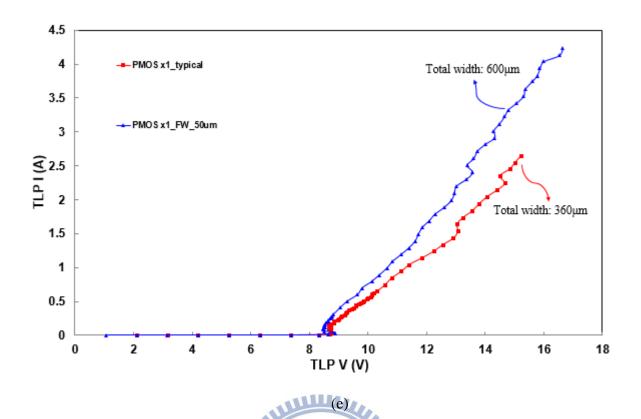

There are four splits about RPO effect of PMOS, which focus on full silicide (no RPO) and silicide blocking. The RPO spacing is decrease from 0.3μm (typical) to -0.06μm at the drain region. There are several splits about the drain contact to poly-gate edge (d1) effect and drain contact number (co). The spacings of the drain contact to poly-gate edge (d1) are 2μm (typical), 4μm, and 6μm, and the clearance variation on the drain contact number (co) splits from 2 (typical) to 4. There are two splits about channel length (L) effect of PMOS, the clearance variation are 0.8μm (typical) and 1μm. The clearance variation on total width splits from 360μm (typical) to 600μm. The single finger width of the PMOS devices with total width of 360μm (typical) and 600μm are 30μm and 50μm, respectively.

## 2.2.3 Experiment Results

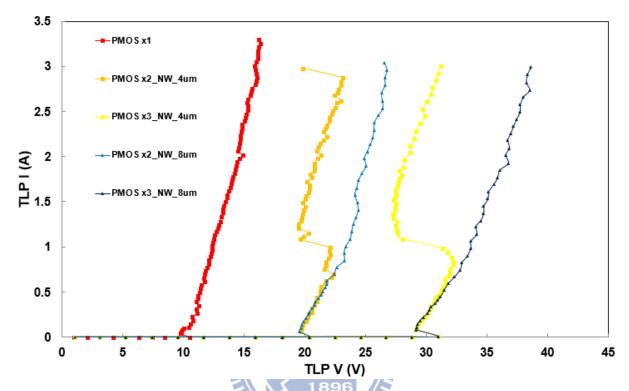

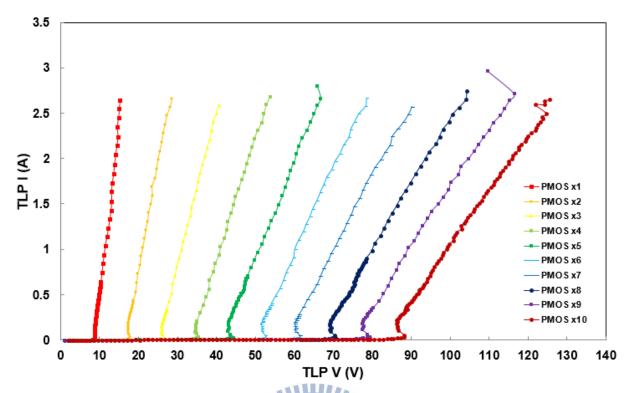

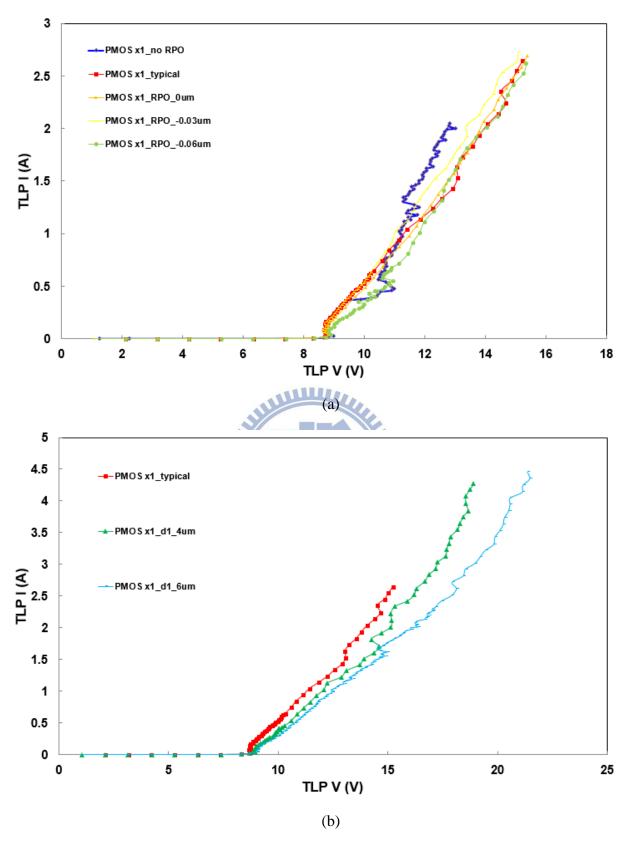

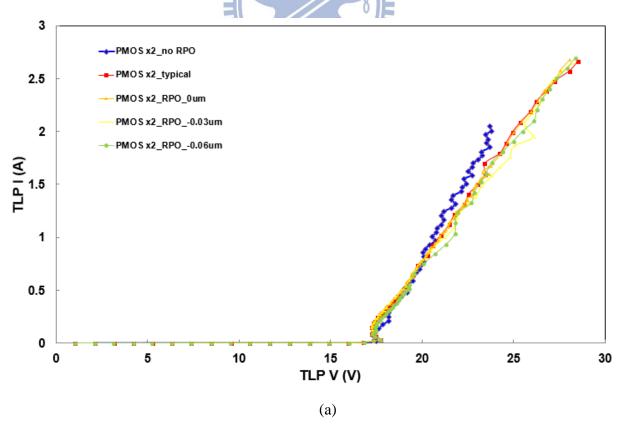

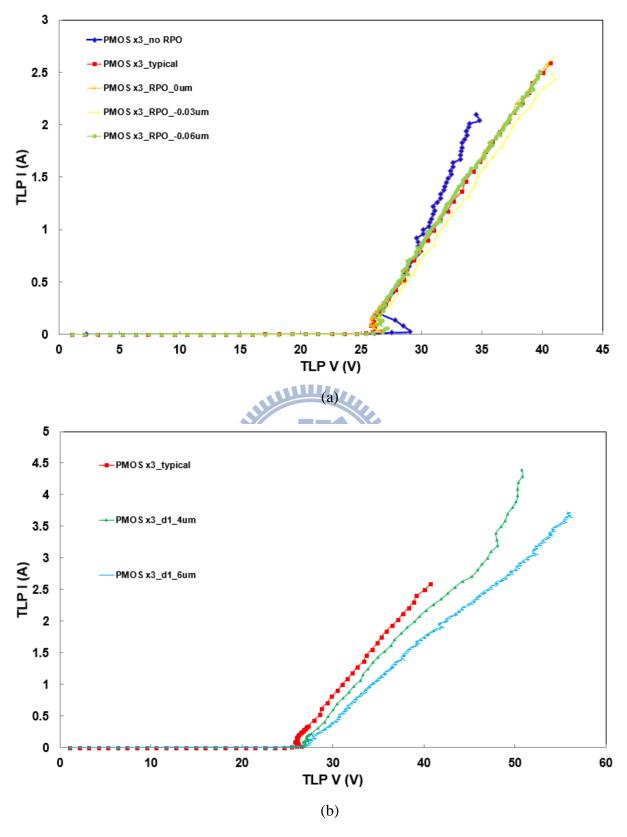

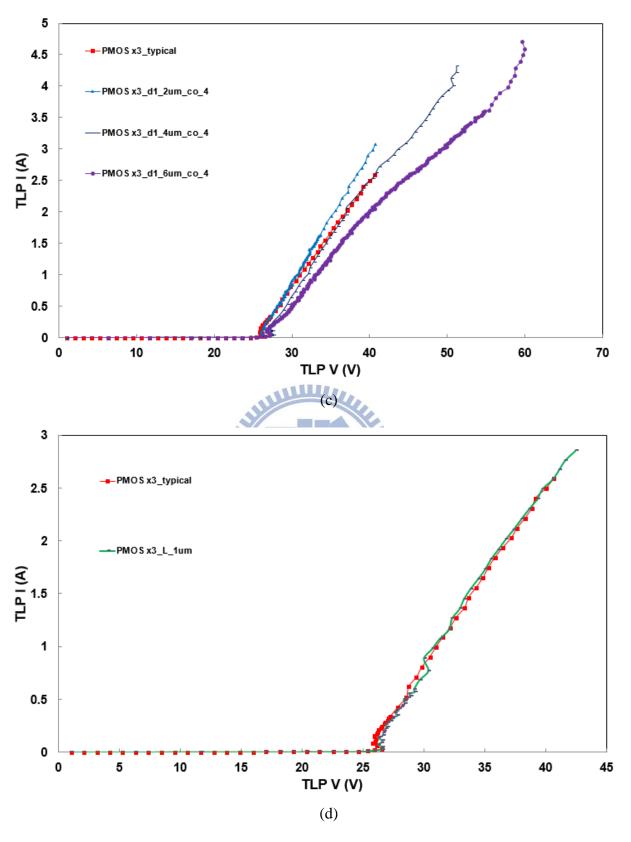

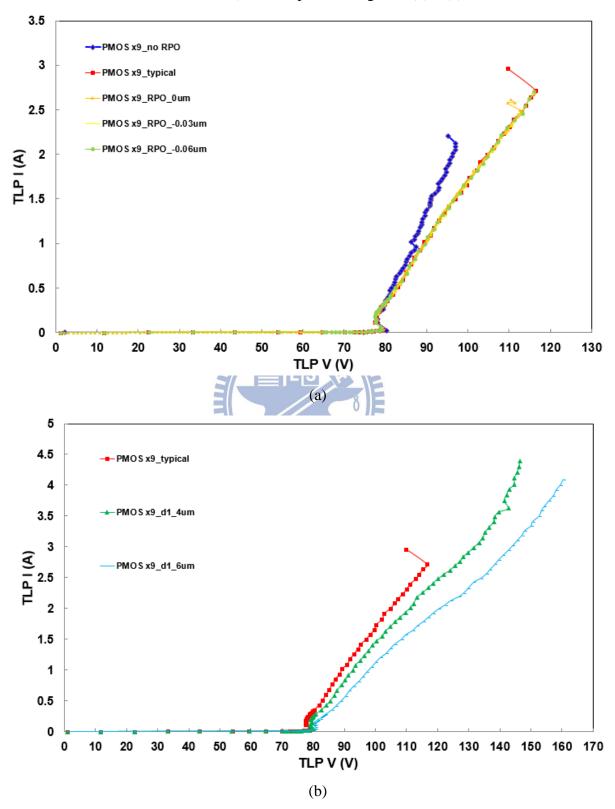

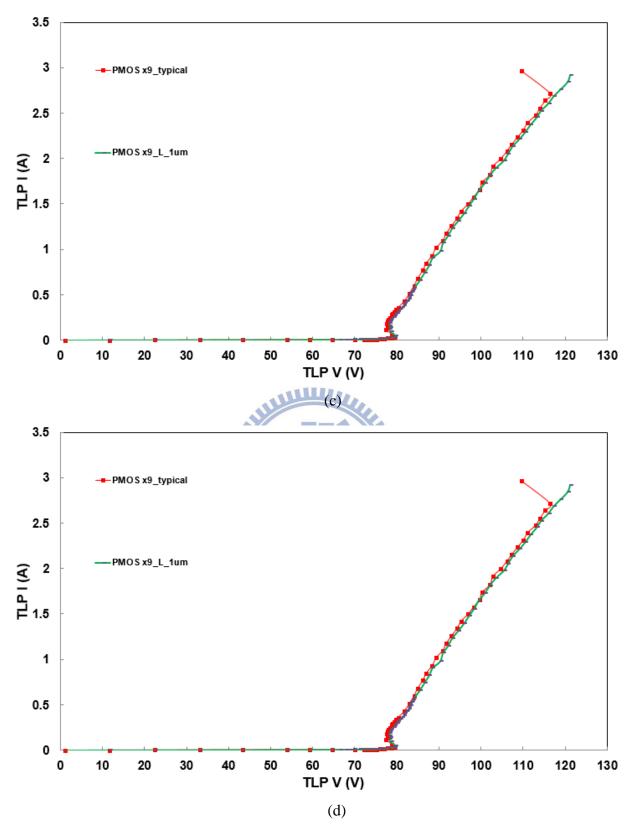

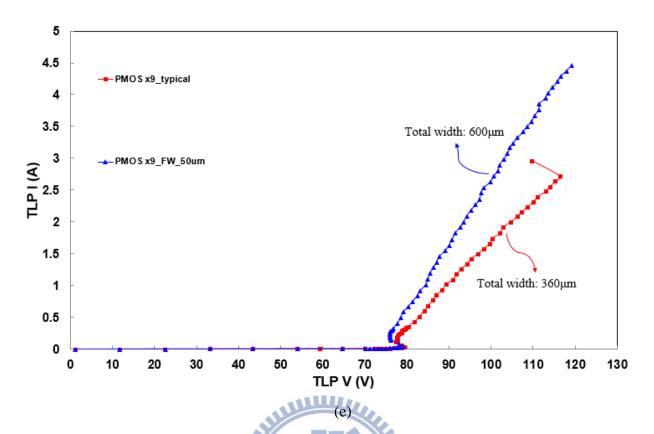

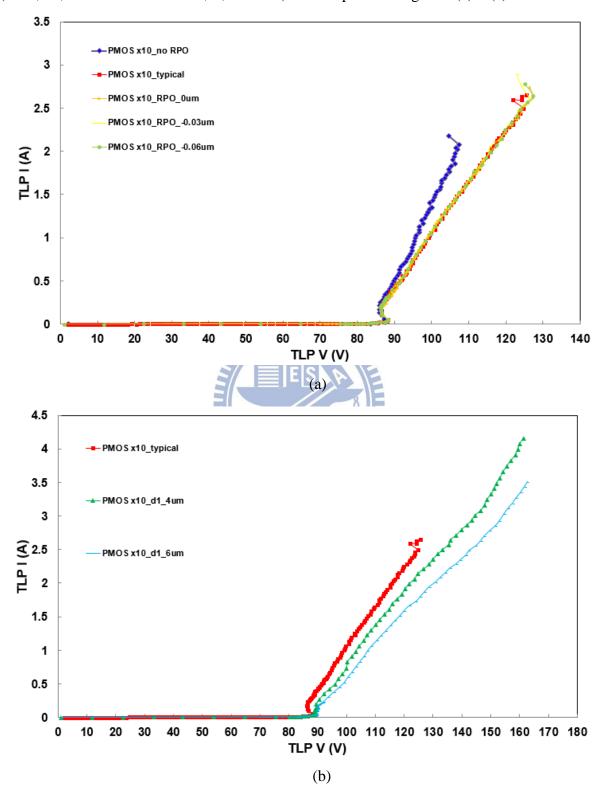

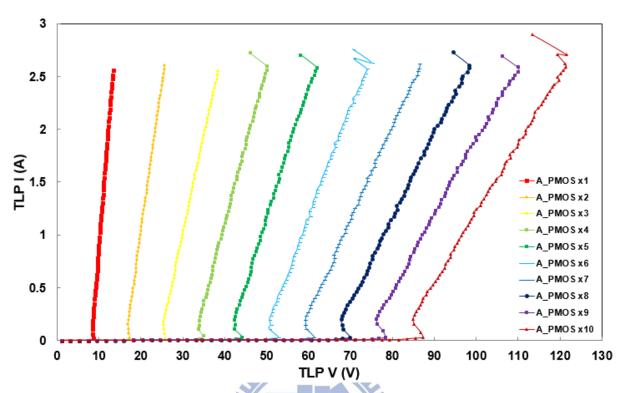

The TLP measured I-V characteristics of typical stacked LV PMOSs are shown in Fig. 2.13. The holding voltages of stacked LV PMOSs with different stacking numbers can be found in Fig. 2.13. The total holding voltage of stacked PMOSs is the multiple of the holding voltage of single PMOS. The total trigger voltage of stacked PMOSs is also the multiple of the trigger voltage of single PMOS. The secondary breakdown current (I<sub>12</sub>) of stacked PMOSs are almost the same in spite of different stacking numbers. The detailed characteristics of typical stacked LV PMOSs are listed in Table 2.7.

WILLIAM .

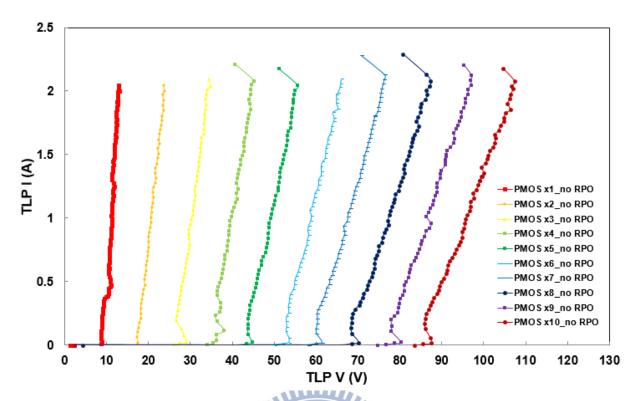

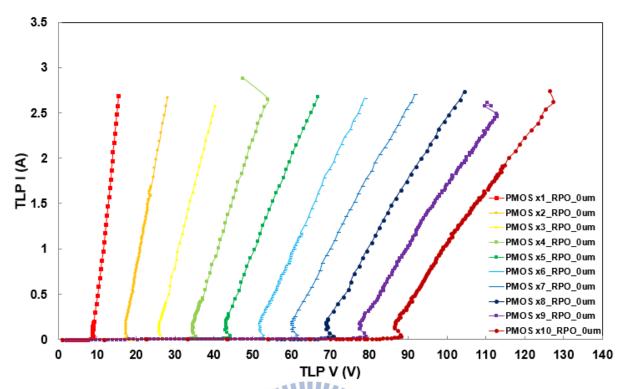

The TLP measured I-V characteristics of full silicide (no RPO) stacked LV PMOSs are shown in Fig. 2.14. All of full silicide (no RPO) stacked LV PMOSs can pass 4 kV in the human-body-model (HBM) ESD test and 200 V in the machine-model (MM) ESD test. The detailed characteristics of full silicide (no RPO) stacked LV PMOSs are listed in Table 2.7. The TLP measured I-V characteristics of silicide blocking stacked LV PMOSs are shown in Fig. 2.14, Fig. 2.15, Fig. 2.16. The spacings of RPO are 0μm (overlap poly-gate), -0.03μm, and -0.06μm. The detailed characteristics of silicide blocking stacked LV PMOSs are listed in Table 2.8, Table 2.9, and Table 2.10.

Fig. 2.13 The TLP-measured I-V characteristics of typical stacked LV PMOSs

Table 2.7

The measurement data of typical stacked LV PMOSs

|          |                     | TLP                |                     |        | ESD      | (*)    |

|----------|---------------------|--------------------|---------------------|--------|----------|--------|

|          | V <sub>t1</sub> (V) | V <sub>h</sub> (V) | I <sub>t2</sub> (A) | BV (V) | HBM (kV) | MM (V) |

| 1 unit   | 8.81                | 8.67               | 2.55                | 8.2    | 4.5      | 300    |

| 2 units  | 17.74               | 17.25              | 2.57                | 16.3   | 4.5      | 300    |

| 3 units  | 26.54               | 25.82              | 2.49                | 24.4   | 4.5      | 300    |

| 4 units  | 35.41               | 34.54              | 2.6                 | 32.6   | 5        | 350    |

| 5 units  | 44.34               | 42.92              | 2.66                | 40.7   | 5        | 350    |

| 6 units  | 52.79               | 51.36              | 2.58                | 48.8   | 5        | 400    |

| 7 units  | 61.49               | 60.21              | 2.49                | 57     | 5        | 400    |

| 8 units  | 70.56               | 69.15              | 2.65                | 65.2   | 5        | 400    |

| 9 units  | 79.37               | 77.43              | 2.72                | 73.2   | 5        | 450    |

| 10 units | 88.23               | 86.26              | 2.63                | 81.6   | 5        | 450    |

Fig. 2.14 The TLP-measured I-V characteristics of full silicide (no RPO) stacked LV PMOSs

Table 2.8

The measurement data of full silicide (no RPO) stacked LV PMOSs

|          |                     | TLP                |                     |        | ESD      | (*)    |

|----------|---------------------|--------------------|---------------------|--------|----------|--------|

|          | V <sub>t1</sub> (V) | V <sub>h</sub> (V) | I <sub>t2</sub> (A) | BV (V) | HBM (kV) | MM (V) |

| 1 unit   | 8.99                | 8.66               | 2.02                | 8.2    | 4        | 200    |

| 2 units  | 17.49               | 17.36              | 2                   | 16.4   | 4        | 250    |

| 3 units  | 29.01               | 26.58              | 2.04                | 24.6   | 4        | 250    |

| 4 units  | 36.3                | 35.96              | 2.08                | 32.8   | 4        | 250    |

| 5 units  | 44.76               | 43.84              | 2.05                | 41     | 4        | 300    |

| 6 units  | 53.53               | 52.86              | 2.06                | 49     | 4        | 300    |

| 7 units  | 61.49               | 60.17              | 2.13                | 57.2   | 4        | 300    |

| 8 units  | 70.11               | 68.24              | 2.13                | 65.4   | 4        | 300    |

| 9 units  | 80.27               | 77.83              | 2.12                | 74     | 4        | 350    |

| 10 units | 87.46               | 85.95              | 2.08                | 81.8   | 4        | 350    |

|          |                     |                    |                     |        |          |        |

Fig. 2.15 The TLP-measured I-V characteristics of silicide blocking (RPO\_0μm) stacked LV PMOSs

Table 2.9

The measurement data of silicide blocking (RPO\_0µm) stacked LV PMOSs

|          |                     |                    |                     | DC (#) |          |        |

|----------|---------------------|--------------------|---------------------|--------|----------|--------|

|          |                     | TLP                |                     |        | ESD      | (*)    |

|          | V <sub>t1</sub> (V) | V <sub>h</sub> (V) | I <sub>t2</sub> (A) | BV (V) | HBM (kV) | MM (V) |

| 1 unit   | 8.85                | 8.73               | 2.58                | 8.2    | 4.5      | 300    |

| 2 units  | 17.69               | 17.23              | 2.58                | 16.3   | 5        | 300    |

| 3 units  | 26.63               | 25.77              | 2.48                | 24.4   | 4.5      | 350    |

| 4 units  | 35.29               | 34.46              | 2.66                | 32.6   | 4.5      | 350    |

| 5 units  | 44.08               | 42.93              | 2.59                | 40.7   | 5        | 350    |

| 6 units  | 52.77               | 51.52              | 2.58                | 48.8   | 5        | 400    |

| 7 units  | 61.41               | 60.01              | 2.62                | 57     | 5        | 400    |

| 8 units  | 70.75               | 68.8               | 2.64                | 65     | 5        | 400    |

| 9 units  | 79.23               | 77.36              | 2.46                | 73.2   | 5        | 450    |

| 10 units | 88.21               | 86.43              | 2.46                | 81.4   | 5        | 450    |

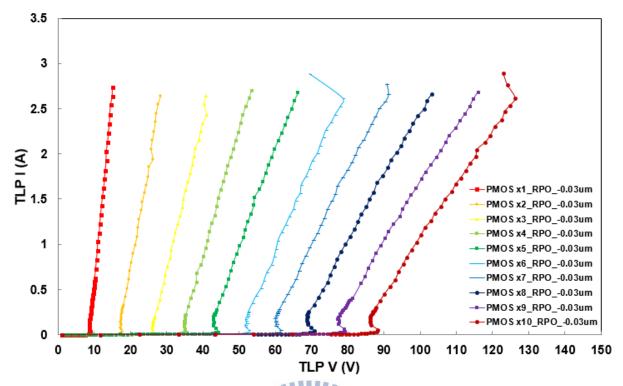

Fig. 2.16 The TLP-measured I-V characteristics of silicide blocking (RPO\_-0.03μm) stacked LV PMOSs

Table 2.10

The measurement data of silicide blocking (RPO\_-0.03 $\mu m$ ) stacked LV PMOSs

|          |                     | TLP                |                     |        | ESD      | (*)    |

|----------|---------------------|--------------------|---------------------|--------|----------|--------|

|          | V <sub>t1</sub> (V) | V <sub>h</sub> (V) | I <sub>t2</sub> (A) | BV (V) | HBM (kV) | MM (V) |

| 1 unit   | 8.81                | 8.62               | 2.63                | 8.2    | 4.5      | 300    |

| 2 units  | 17.68               | 17.2               | 2.55                | 16.3   | 4.5      | 300    |

| 3 units  | 26.55               | 26                 | 2.55                | 24.4   | 5        | 350    |

| 4 units  | 35.6                | 34.82              | 2.61                | 32.6   | 4.5      | 350    |

| 5 units  | 44.42               | 42.92              | 2.58                | 40.7   | 4.5      | 350    |

| 6 units  | 52.81               | 51.64              | 2.62                | 48.8   | 5        | 400    |

| 7 units  | 61.54               | 60.07              | 2.66                | 57     | 5        | 400    |

| 8 units  | 70.68               | 68.61              | 2.59                | 65.2   | 5        | 400    |

| 9 units  | 79.4                | 77.25              | 2.61                | 73.2   | 5        | 450    |

| 10 units | 88.25               | 86.12              | 2.76                | 81.4   | 5        | 450    |

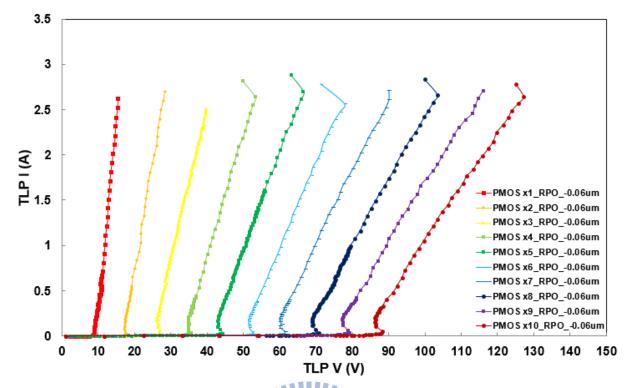

Fig. 2.17 The TLP-measured I-V characteristics of silicide blocking (RPO\_-0.06μm) stacked

LV PMOSs

Table 2.11

The measurement data of silicide blocking (RPO\_-0.06µm) stacked LV PMOSs

|          |                     | TLP                |                     |        | ESD (*)  |        |

|----------|---------------------|--------------------|---------------------|--------|----------|--------|

|          | V <sub>t1</sub> (V) | V <sub>h</sub> (V) | I <sub>t2</sub> (A) | BV (V) | HBM (kV) | MM (V) |

| 1 unit   | 8.89                | 8.81               | 2.52                | 8.2    | 4.5      | 300    |

| 2 units  | 17.74               | 17.27              | 2.59                | 16.3   | 4.5      | 300    |

| 3 units  | 27.17               | 26.07              | 2.49                | 24.4   | 4.5      | 350    |

| 4 units  | 35.48               | 34.83              | 2.64                | 32.5   | 4.5      | 350    |

| 5 units  | 44.35               | 42.97              | 2.7                 | 40.7   | 5        | 350    |

| 6 units  | 52.9                | 51.42              | 2.57                | 48.8   | 5        | 400    |

| 7 units  | 61.58               | 60.17              | 2.62                | 57     | 5        | 400    |

| 8 units  | 70.67               | 68.91              | 2.67                | 65     | 5        | 450    |

| 9 units  | 79.26               | 77.3               | 2.62                | 73.2   | 5        | 450    |

| 10 units | 88.21               | 86.08              | 2.64                | 81.4   | 5        | 450    |

All of silicide blocking stacked LV PMOSs can pass 4.5 kV in the human-body-model (HBM) ESD test and 300 V in the machine-model (MM) ESD test. Three silicide blocking devices have almost similar I<sub>t2</sub> and ESD robustness. The ESD robustness of stacked PMOS devices with silicide blocking on drain side are better than stacked PMOS devices with full silicide in the TLP test.

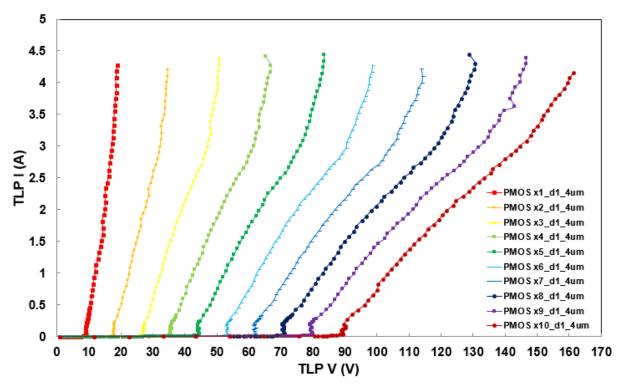

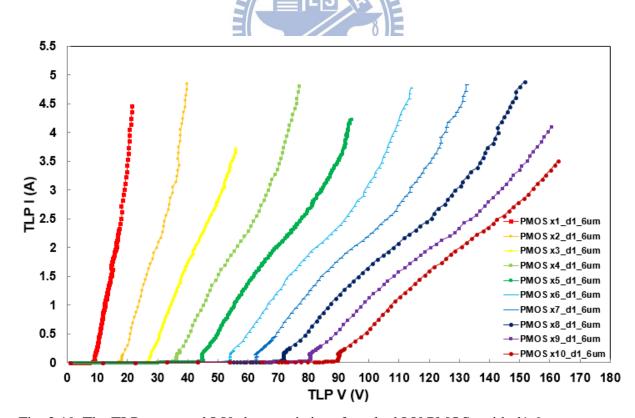

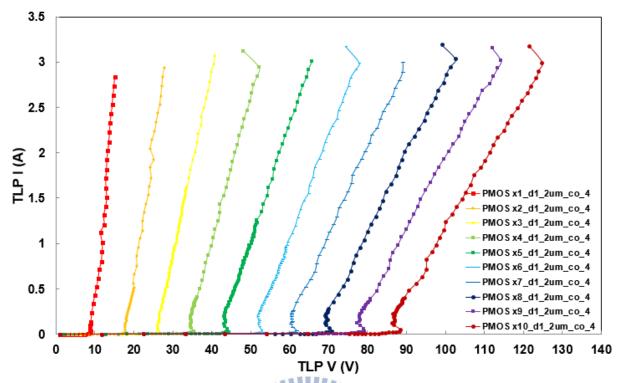

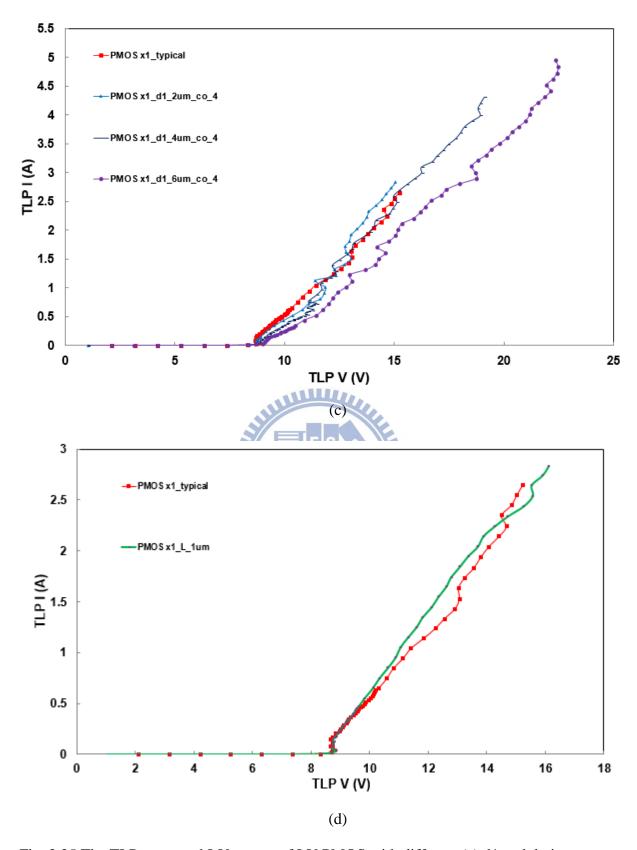

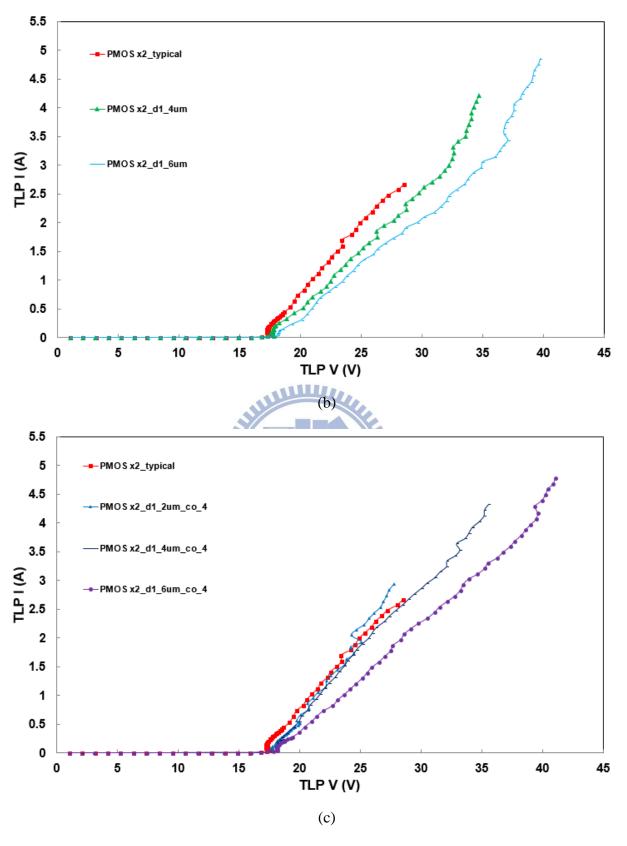

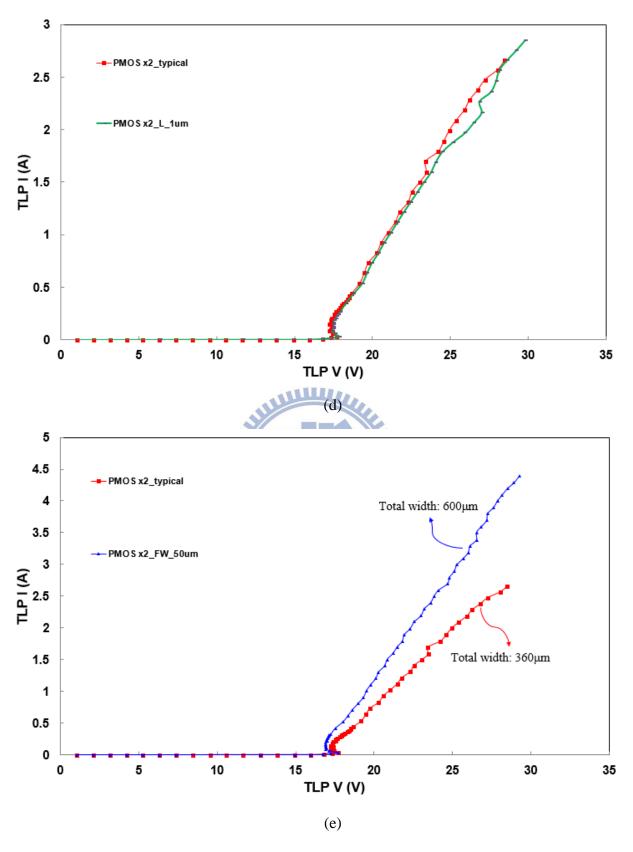

The TLP measured I-V characteristics of stacked LV PMOSs with different drain contact to poly-gate edge (d1) are shown in Fig. 2.18, Fig. 2.19. The spacings of d1 are 4μm and 6μm. The detailed characteristics of stacked LV PMOSs with different drain contact to poly-gate edge (d1) are listed in Table 2.12 and Table 2.13.

Fig. 2.18 The TLP-measured I-V characteristics of stacked LV PMOSs with d1 4µm

All of stacked LV PMOSs with d1 4 $\mu$ m can pass 7 kV in the human-body-model (HBM) ESD test and 450 V in the machine-model (MM) ESD test. The ESD robustness of stacked LV PMOSs with d1 4 $\mu$ m are better than typical stacked PMOS devices in the TLP test.