# 國立交通大學

電子研究所

碩士論文

應用於900-1800MHz GSM規格的 高功率CMOS T/R開關之靜電放電防護設計

# ESD Protection Design of 900–1800MHz High-Power CMOS T/R Switch for GSM Cellular Applications

研究生:洪道一 (Tao-Yi Hung)

指導教授: 柯明道教授 (Prof. Ming-Dou Ker)

中華民國一〇六年九月

## 應用於900-1800MHz GSM規格的 高功率CMOS T/R開關之靜電放電防護設計

## ESD Protection Design of 900–1800MHz High-Power CMOS T/R Switch for GSM Cellular Applications

研究生:洪道一 Student: Tao-Yi Hung

指導教授: 柯明道教授 Advisor: Prof. Ming-Dou Ker

國立交通大學電子研究所領士論文

A Thesis

Submitted to

Institute of Electronics

College of Electrical and Computer Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of

Master of Science

in

Electronics Engineering

September 2017 Hsinchu, Taiwan, Republic of China

中華民國一〇六年九月

# 應用於900-1800MHz GSM規格的 高功率CMOS T/R開關之靜電放電防護設計

學生: 洪道一 指導教授: 柯 明 道 教授

近年來,隨著矽製程的演進,射頻積體電路(radio-frequency integrated circuits, RFICs)已經可以在一般的 CMOS 製程中實現,如此以來,不但可以降低製造成本,也可以提升與其他射頻電路區塊的整合性。而隨著電晶體尺寸微縮,雖然達到了提升邏輯閘的運算速度以及降低電源功率消耗的目的,但來自靜電放電(electrostatic discharge, ESD)的威脅,卻不會因為製程的先進而降低,因此靜電放電防護設計是在積體電路的可靠度中是一個不可忽略的問題。在射頻積體電路中,靜電放電防護設計除了要能夠達到一定的工業規格之外,也不能影響到射頻電路中敏感的射頻效能參數及正常的電路操作。因此,必須以非常嚴格的標準來設計 ESD 防護元件以期將其所帶來的寄生效應對高速射頻訊號的影響降至最低。

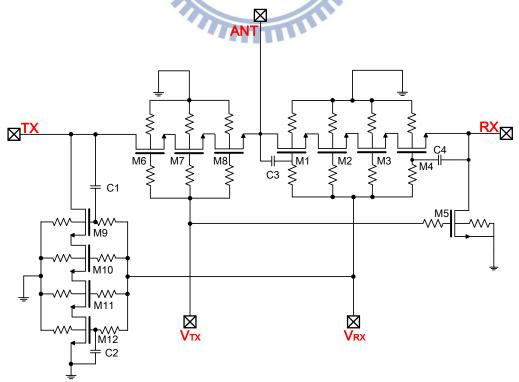

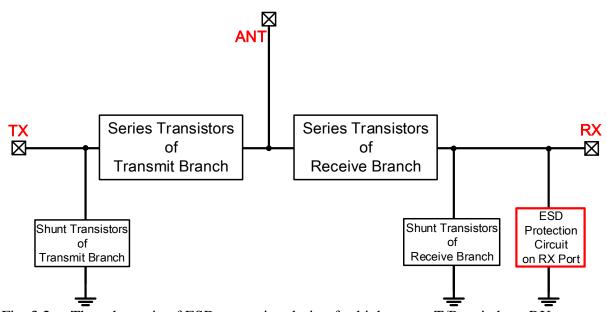

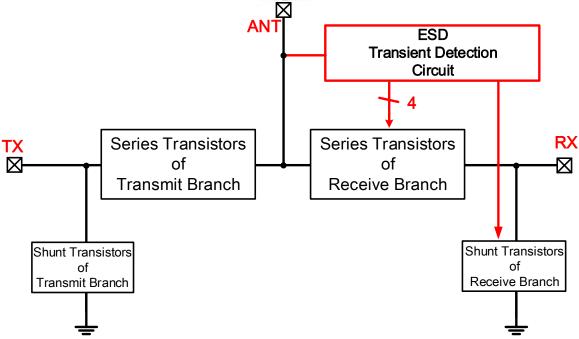

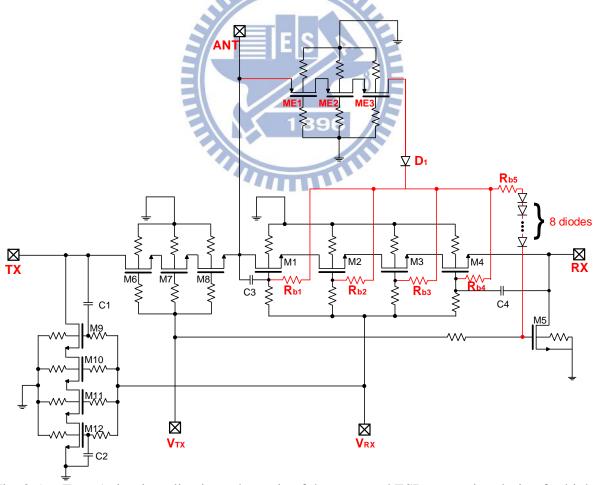

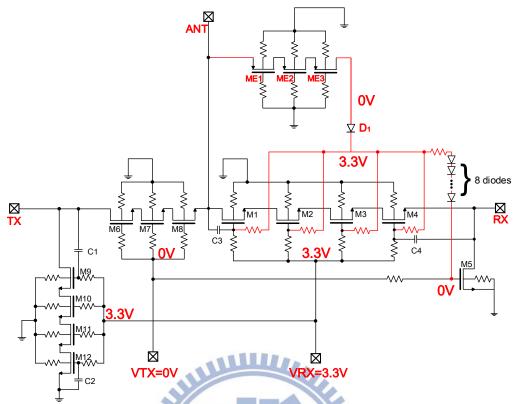

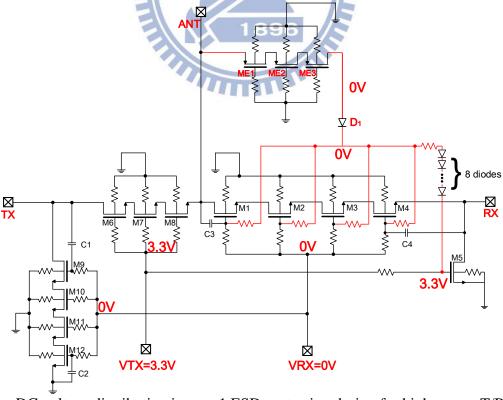

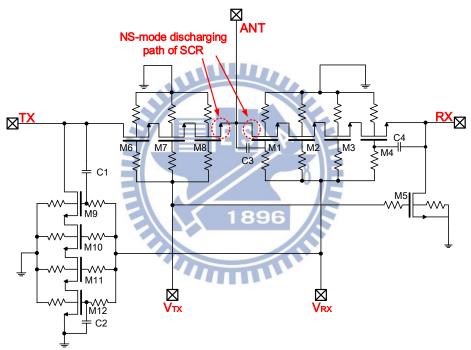

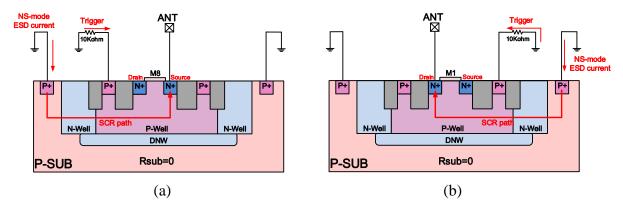

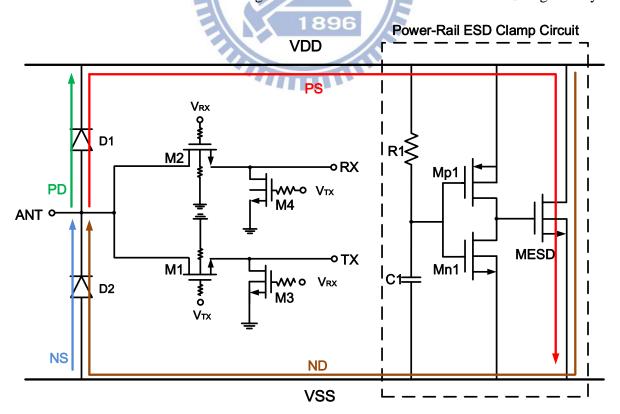

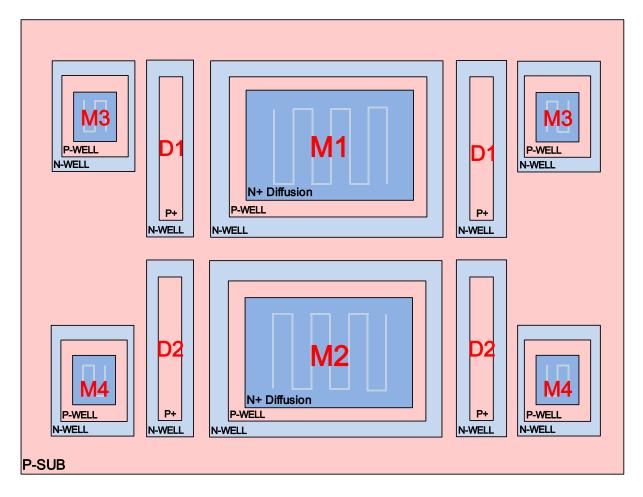

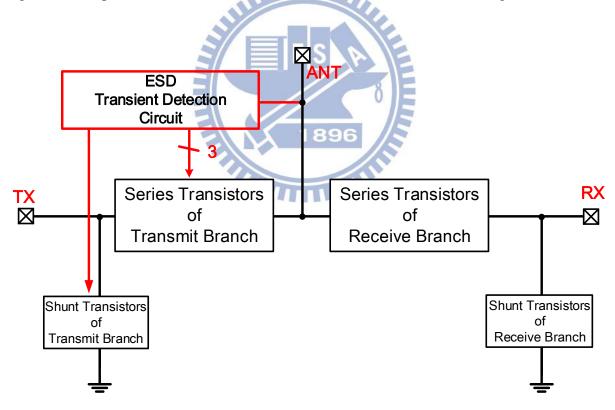

本論文分為兩大部分,第一部分為針對應用於手機通訊中的高功率 T/R 開關 (transmit/receive switch, T/R switch) 電路架構所設計的 ESD 靜電放電設計。在高功率 T/R 開關的堆疊 (multi-stacked) 架構中,由於射頻訊號大振幅與高頻率,會使得一般傳統的靜電放電防護設計將正常的射頻訊號誤判為靜電,將正常的射頻訊號排放到地而造成失真。本論文所提出新的靜電放電防護設計並不使用額外的電流疏通路徑,而是利用辨識射頻訊號和 ESD 的行為差異,可以在靜電來臨時開啟自身電晶體的方式來將電流導入到地。此設計已在 0.18 微米 CMOS 製程中實現,相較於未加入靜電放電防護設計的原始電路,能夠達到良好的靜電防護效果。ESD 的耐受度及 T/R 開關射頻電路的參數特性將在論文中完整的討論。

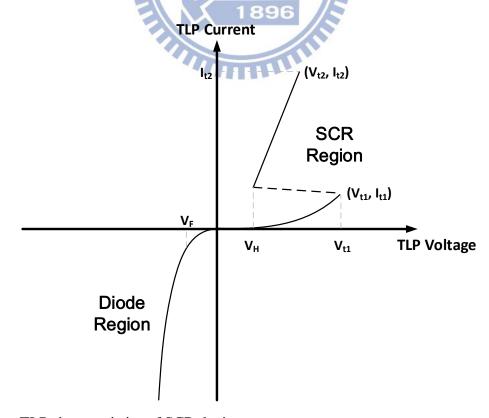

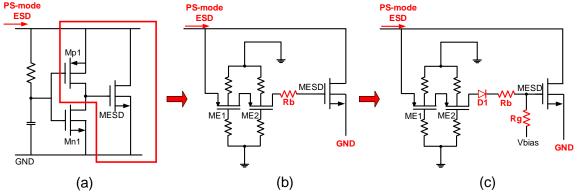

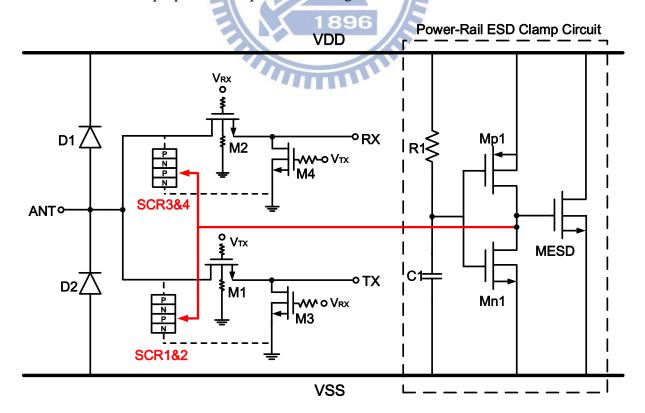

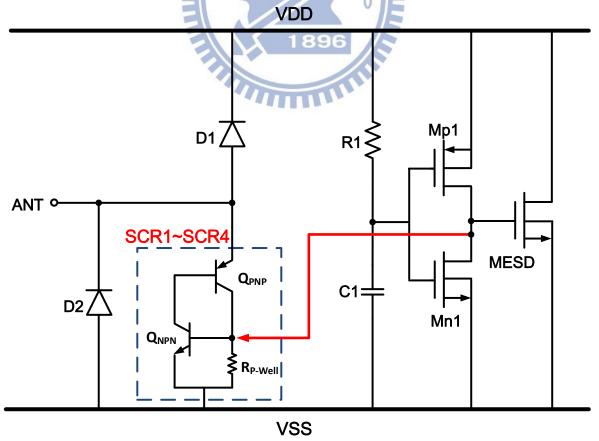

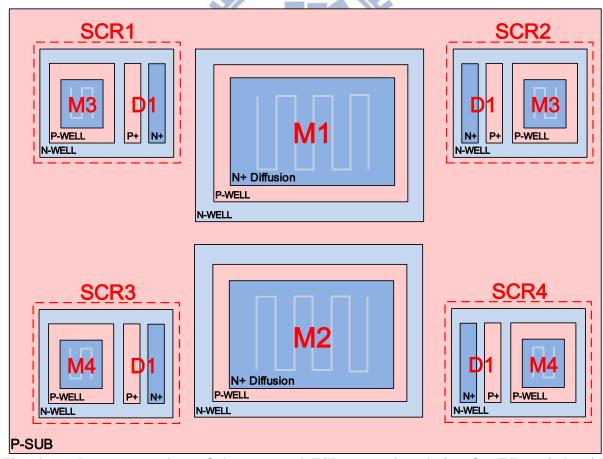

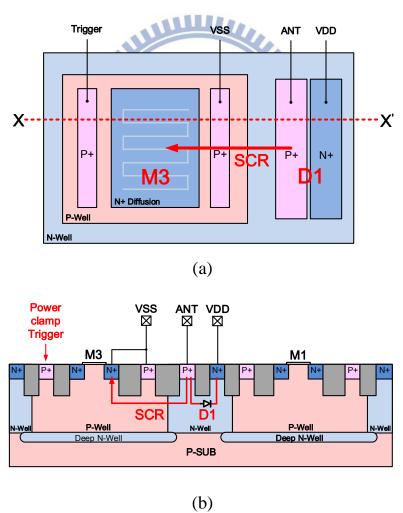

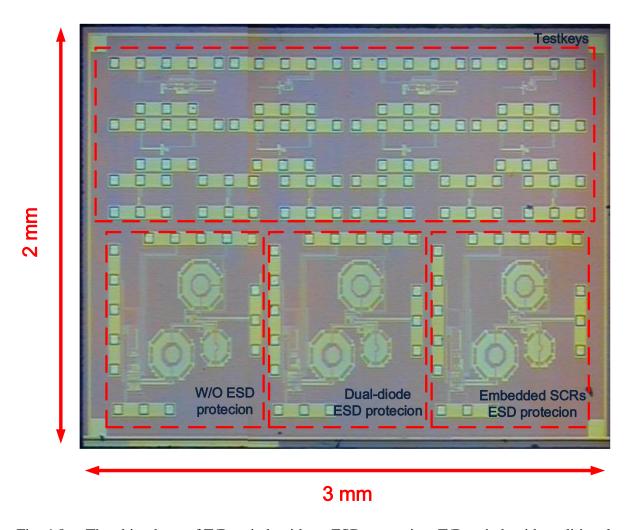

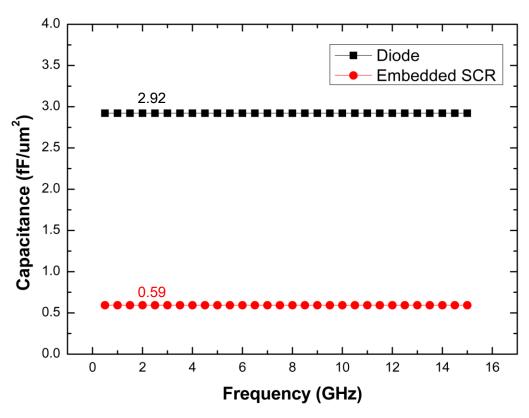

第二部分為應用在典型 T/R 開關中的靜電放電防護元件,利用原本就存在於傳統靜電放電防護電路之中的二極體 (diode) 以及金氧半電晶體 (MOS transistor) 之間的寄生路徑,透過電路佈局技巧組合出一個嵌入式矽控整流器 (embedded silicon-controlled rectifier) 並實現於 90 奈米 CMOS 製程中。此外,藉由電源與地之間的靜電放電箝制電路 (power-rail ESD clamp circuit) 的偵測電路提供觸發訊號將嵌入式矽控整流器在靜電來臨時開啟,成功地降低導通電阻 (Ron) 並提高 T/R switch 對 PS-mode ESD 的耐受度。

# ESD Protection Design of 900–1800MHz High-Power CMOS T/R Switch for GSM Cellular Applications

Student: Tao-Yi Hung Advisor: Prof. Ming-Dou Ker

Institute of Electronics

National Chiao-Tung University

Abstract

In recent years, radio-frequency integrated circuits (RFICs) have been successfully implemented in CMOS process thanks to the fast development of CMOS technologies. In this way, the RFICs can be integrated in a system on chip (SOC) for mass production with lower cost of IC manufacturing. As the transistors scale down rapidly, the oxide thickness becomes thinner and provide faster logic operations with lower energy consumption. However, the threat from electrostatic discharge (ESD) phenomenon was not alleviated as technology advances. In RFICs, the ESD protection circuit must provide enough ESD robustness without disturbing the normal circuit operations. Thus, the ESD protection design must be strictly conducted in order to minimize the parasitic effect of the ESD devices lest it should degrade the performance of the high-speed RF signal.

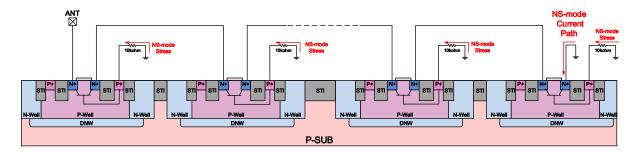

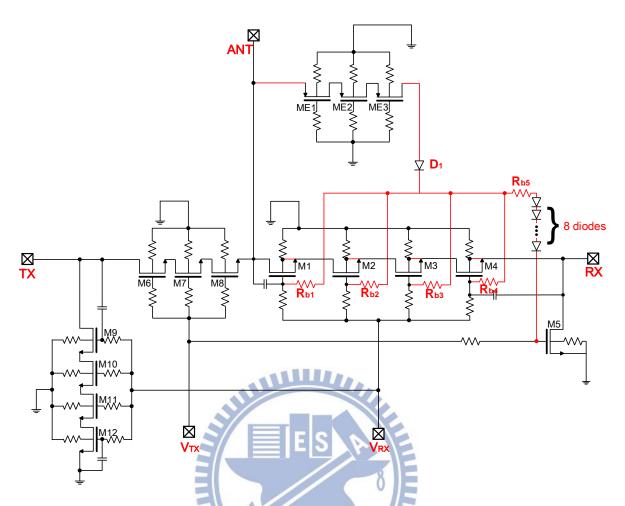

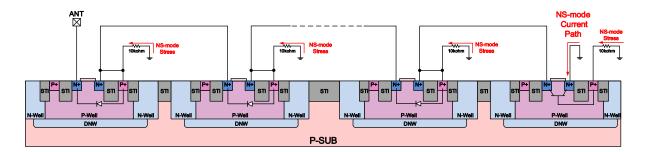

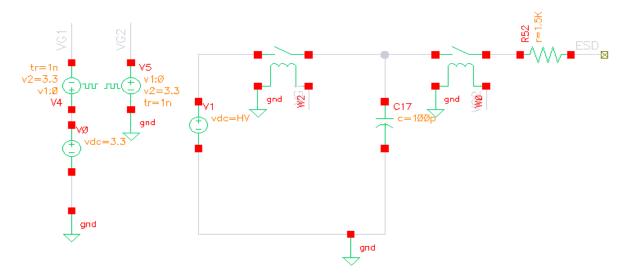

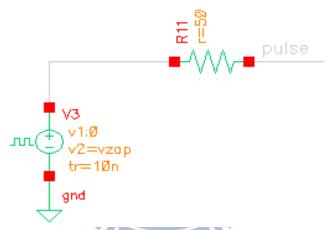

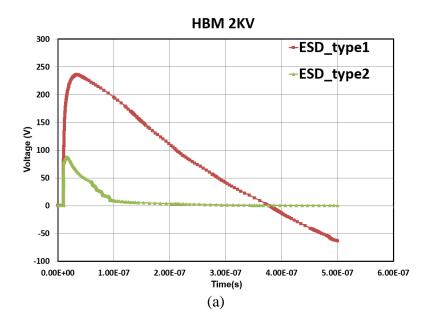

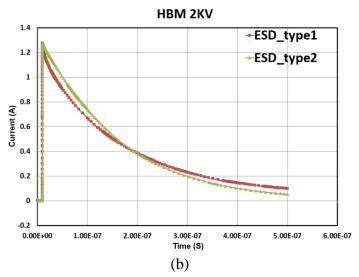

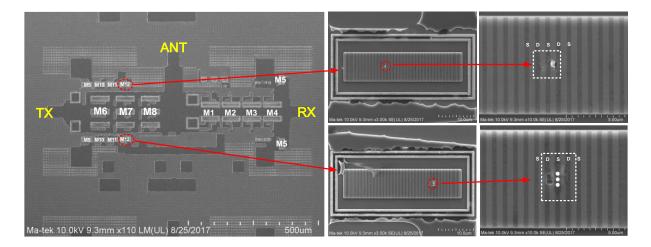

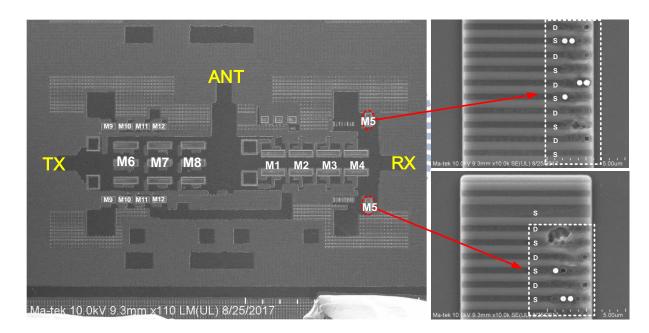

There are two major parts in this thesis. The first part of the thesis targets on the T/R switch which is applied for cellular device. In a high-power T/R switch, traditional ESD protection method cannot be used since the large amplitude and high frequency of the RF signal will mistrigger the traditional ESD protection design. As a consequence, in this work, there is no additional discharging path employed to discharge the ESD current. Instead, by identifying the behavior of the ESD transients and the normal RF signal, the transistors in the proposed ESD protection design can trigger the inherent transistors of the T/R switch in the PS-mode zapping event and discharge the ESD current. The proposed ESD protection design for high-power T/R switch has been fabricated in a 0.18-µm CMOS process and achieved good ESD levels. RF performance and ESD characteristics are measured and analyzed in the thesis.

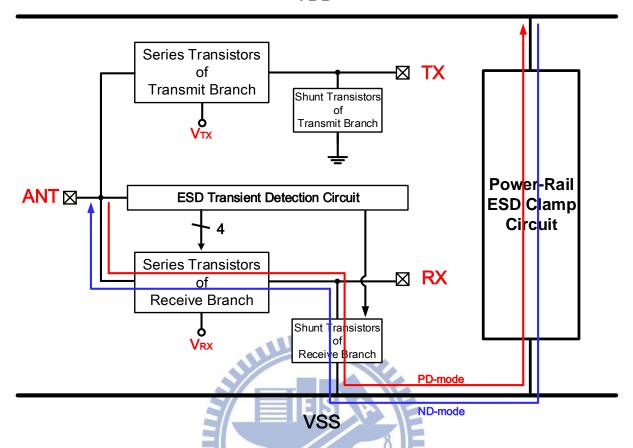

The second part focuses on an ESD protection device for typical T/R switch applications. By using the diodes and MOS transistors which are already designed in the T/R switch with conventional ESD protection, embedded silicon-controlled rectifiers (embedded SCR) are implemented in a 90-nm CMOS process by layout skill. The proposed ESD protection with embedded SCRs and power-rail ESD clamp triggered can enhance the PS-mode ESD robustness of the T/R switch successfully.

## 謝誌

在碩士班的學習期間,首先要感謝的是我的指導教授柯明道教授,老師在類比電子電路領域上有著非常豐富的專業知識及實務經驗,常能一眼就看出電路的核心問題並引導學生朝著正確的方向去思考解決。另外,老師在研究討論之餘,亦不乏針砭時事,提醒學生在忙碌研究時,仍保有產業市場脈動的國際觀。最後,老師認真的研究態度、嚴謹的文章審查、重點式的報告技巧,致力於提升學生水準的諄諄教誨,令我銘記在心!

再來感謝實驗室的博士班學長們:戴家岑學長 curve tracer 使用、羅志聰學長電老鼠手法、陳界廷學長 TLP 系統及 ESD tester 操作、吳維旻學長 90nm 製程下線經驗及電磁模擬的 ADS 教學、張榮堃學長 RF 電路及羽毛球小技巧等等,他們各式各樣的研究知識傳承,與生活經驗都給予我非常大的幫助。碩士班的學長:劉睿閱學長一同討論實驗研究與射頻電路入門教學、楊子毅學長和鄭莞學學長一起耍宅打球、廖顯峰學長、黃義傑學長和吳柏翰學長在課業上的懶人包,吳易翰學長與顏鼎洋學長的生活上的小撇步等等,以及實驗室的 ESD 小徒兒:陳文捷和陳俊成,你們在研究上的問題都能使我教學相長、增廣見聞,還有生醫電路的謝佳琪與林曉平,希望你們能夠一起讓實驗室的歡樂風氣繼續傳遞下去。感謝同一屆的同學們:康宵瑞,讓我見識到不同於台灣的大國見識、魏安妮,使我理解不同的生涯選擇、游力瑾,一路從大三開始一起跌跌撞撞互相扶持、互相勉勵、還要忍受我的牛脾氣,最後跟我一同飛去成都參加研討會看熊貓,實在是太感謝妳了!

最後感謝我的父母,讓我能夠在新竹安心讀書沒有後顧之憂,爸爸還順便一起念了博士,真是太厲害了!希望所有我認識的人們,都能夠身體健康,事事順利!

洪道一

丁酉年 誌於 新竹交大

| 摘要      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | i             |

|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Abstra  | act     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | iii           |

| 謝誌      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | v             |

| Table ( | Captio  | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | viii          |

| Figure  | e Capti | ons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ix            |

| Chapt   | er 1    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1             |

| 1.1     |         | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1             |

| 1.2     |         | Thesis Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4             |

| Chapt   | er 2    | Basics of T/R Switch and ESD Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5             |

| 2.1     |         | General Considerations of T/R Switch Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5             |

|         | 2.1.1   | S-parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5             |

|         | 2.1.2   | Insertion Loss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7             |

|         | 2.1.3   | Power Handling Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9             |

|         | 2.1.4   | Isolation E.S. A. L. E.S. A. L. E. S. L. E. S. A. L. E. L. E. S. A. L. E. E. S. A. L. E. S. A. L. E. E. S. L. E. E. S. L. E. E. S. A. L. E. E. S. A. L. E. E. S | 13            |

| 2.2     |         | RF Simulations and Layout Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14            |

|         | 2.2.1   | Pre-Simulation and Post-Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |

|         | 2.2.2   | Layout Considerations and RF Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 17            |

| 2.3     |         | Conventional ESD Protection Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20            |

|         | 2.3.1   | Architecture of Conventional Whole-Chip ESD Protection Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20            |

|         | 2.3.2   | Power-Rail ESD Clamp Circuit and I/O ESD Clamp Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 21            |

| 2.4     |         | ESD Protection Design for RFICs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23            |

|         | 2.4.1   | Conventional RF ESD Protection Design Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23            |

|         | 2.4.2   | Issues of ESD Protection Design on T/R Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29            |

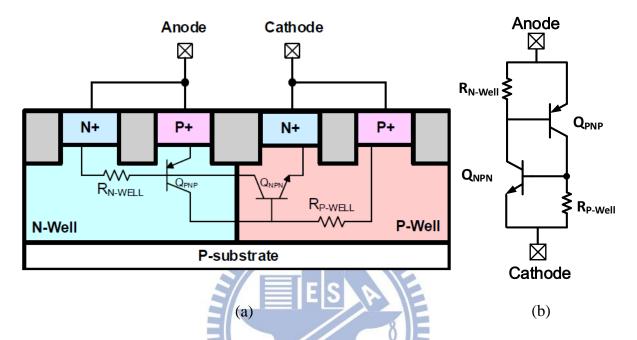

|         | 2.4.3   | Conventional Silicon-Controlled Rectifier for ESD Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 30            |

| Chapt   | er 3    | ESD Protection Design for High-Power T/R Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32            |

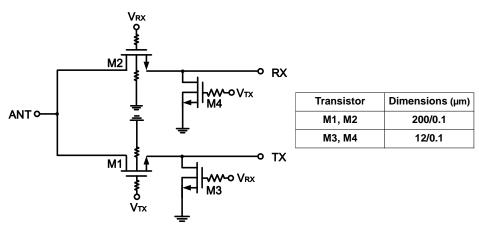

| 3.1     |         | Circuit Design of High-Power T/R Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 32            |

| 3.2     |         | Proposed ESD Protection Design for High-Power T/R Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34            |

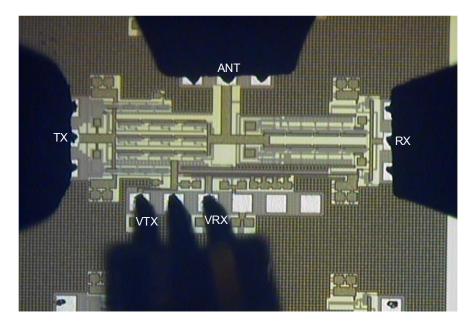

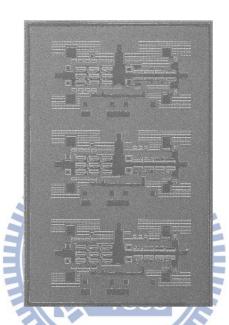

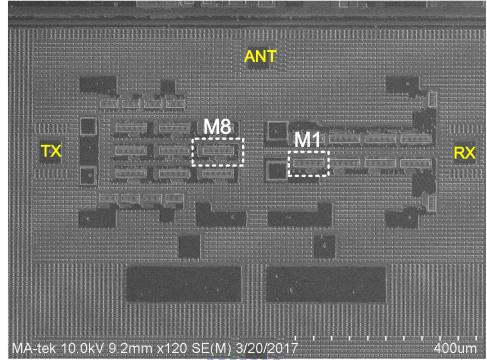

| 3.3     |         | Experimental Results of High-Power T/R Switch with Proposed ESD Protect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ction Designs |

|         |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 49            |

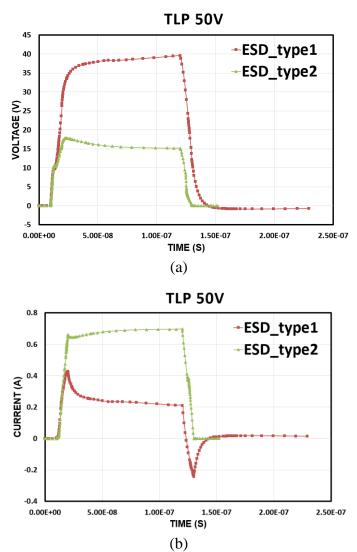

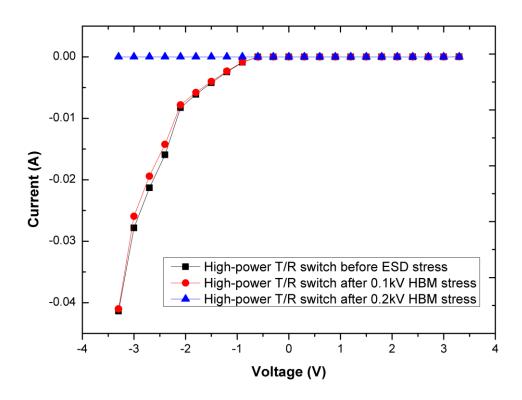

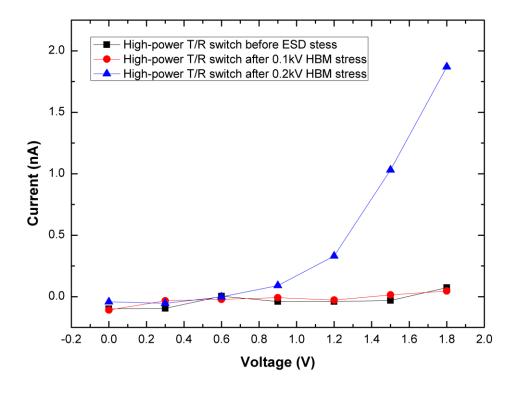

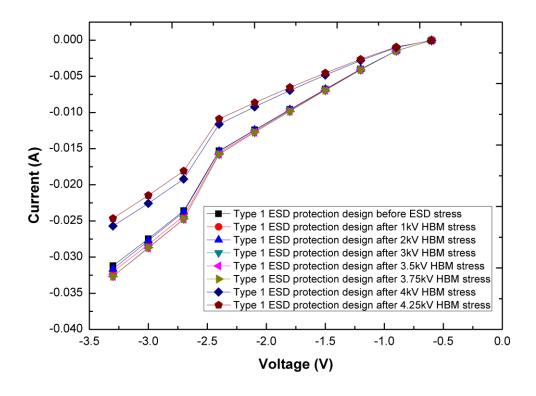

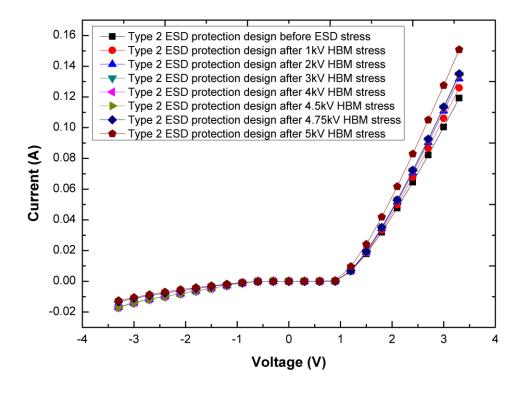

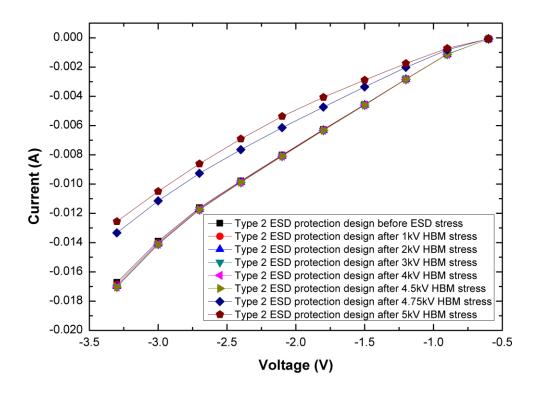

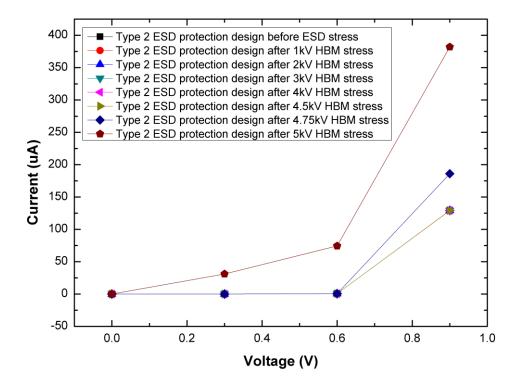

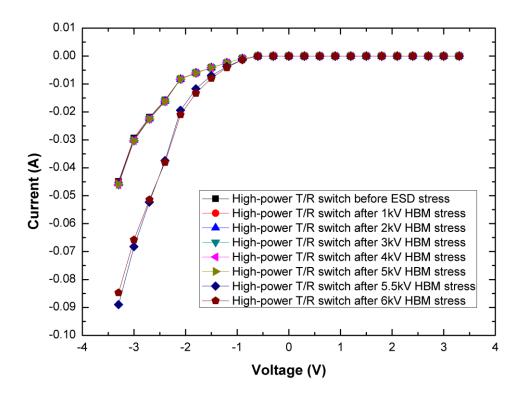

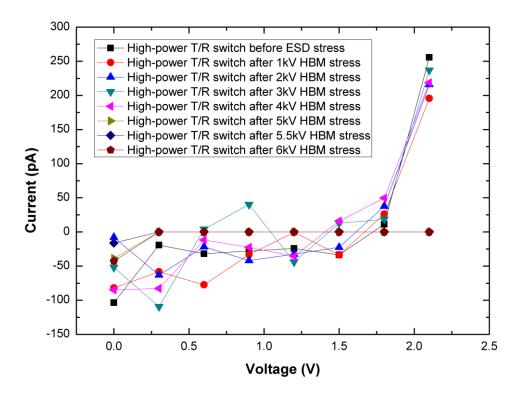

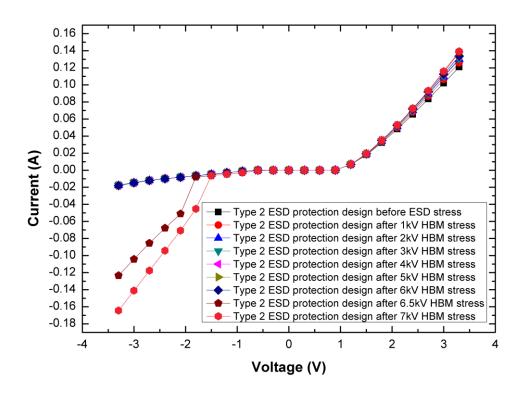

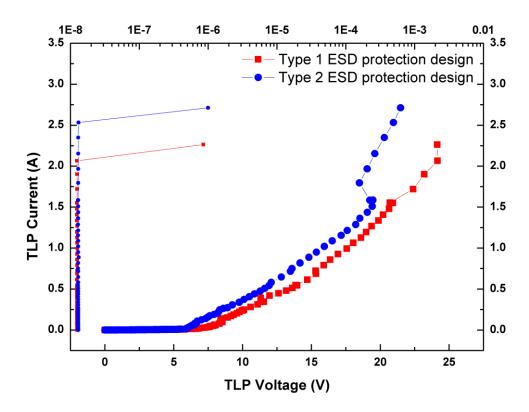

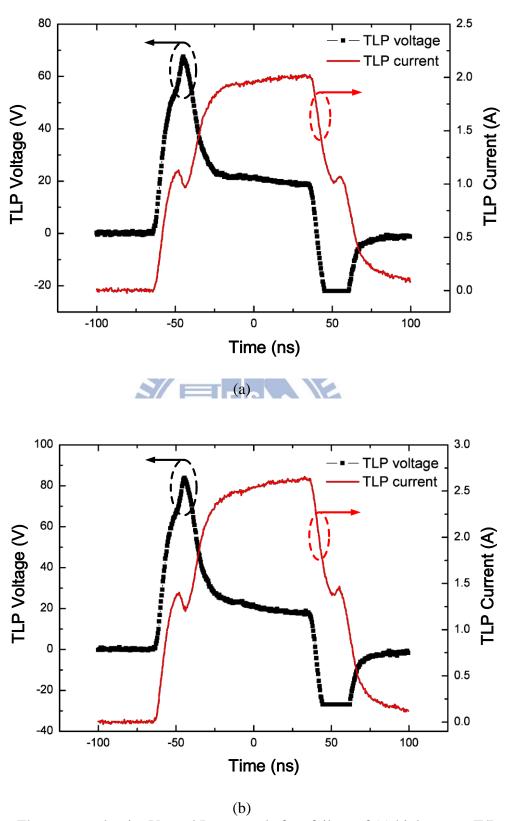

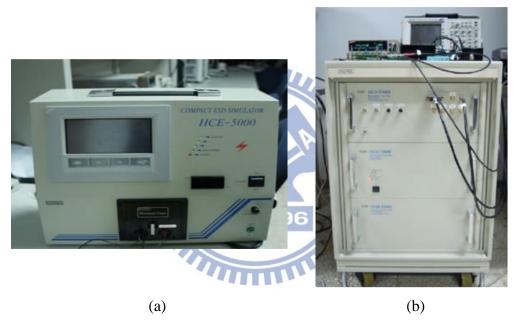

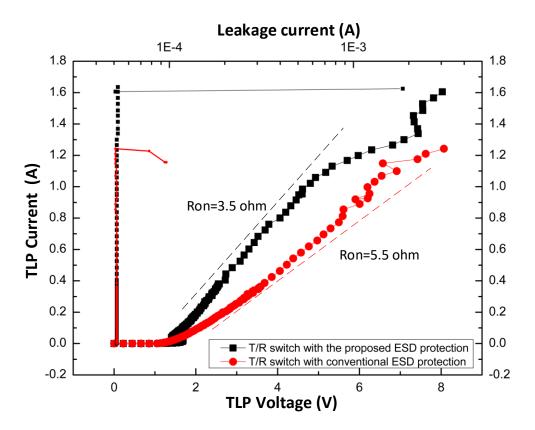

|         | 3.3.1   | ESD Levels Measured with ESD HBM Tester and TLP Systemvi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 52            |

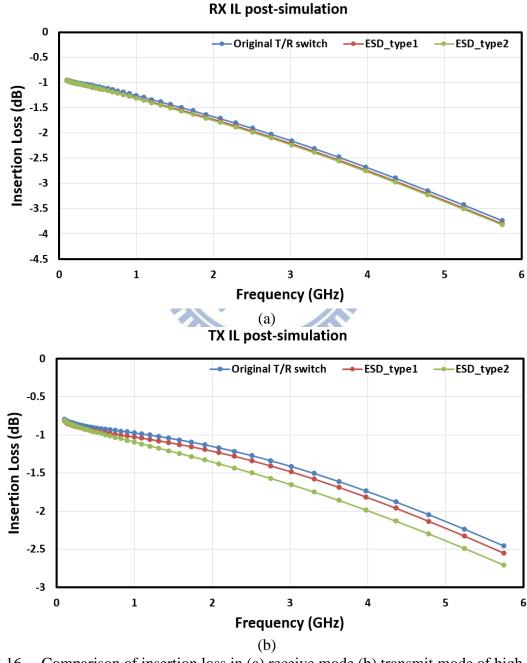

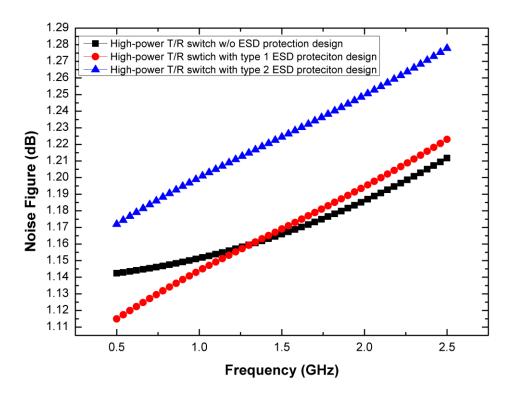

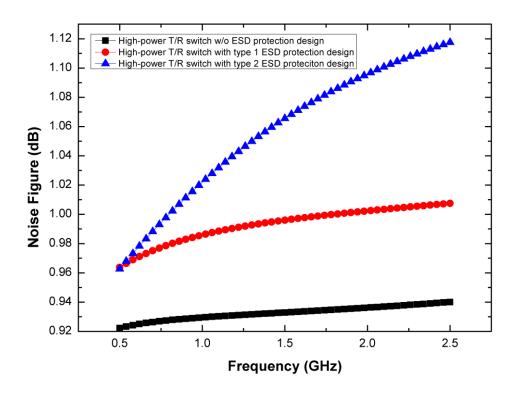

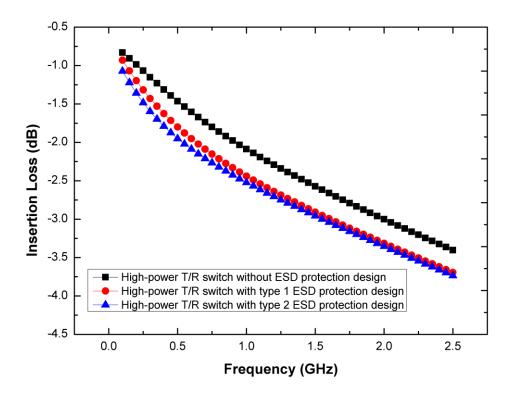

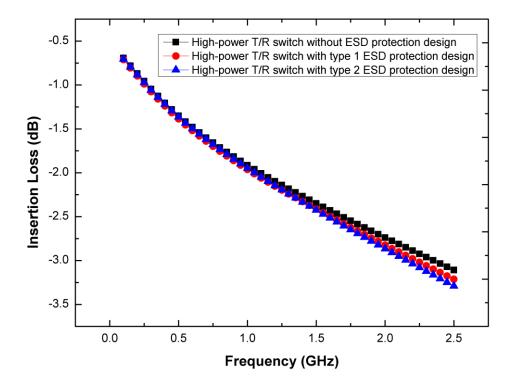

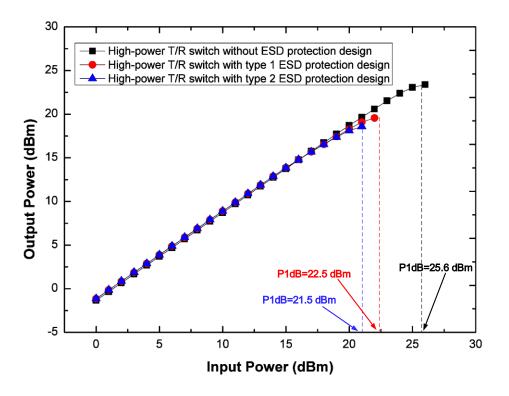

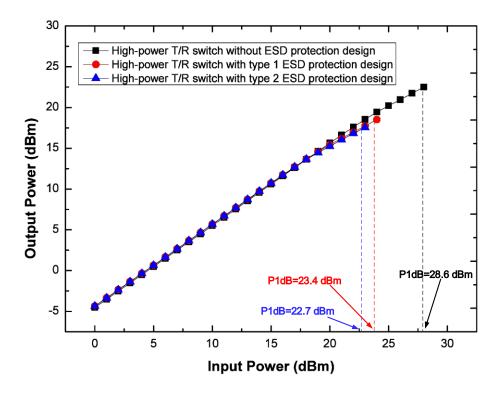

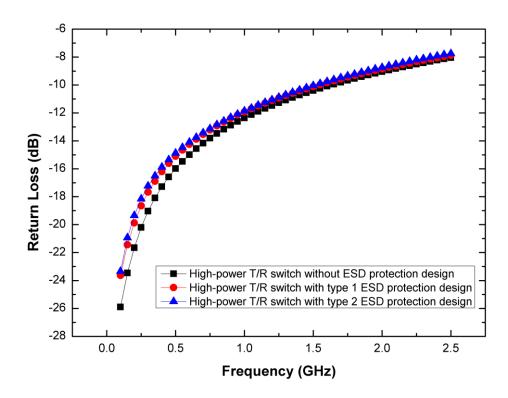

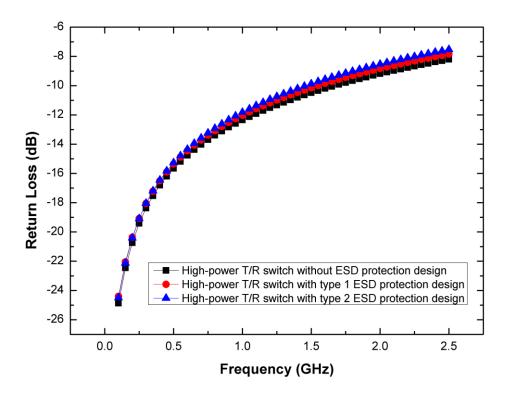

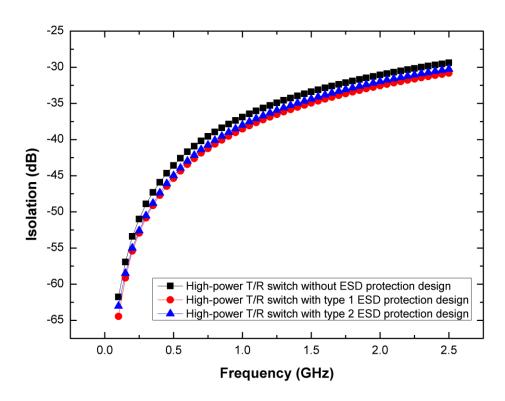

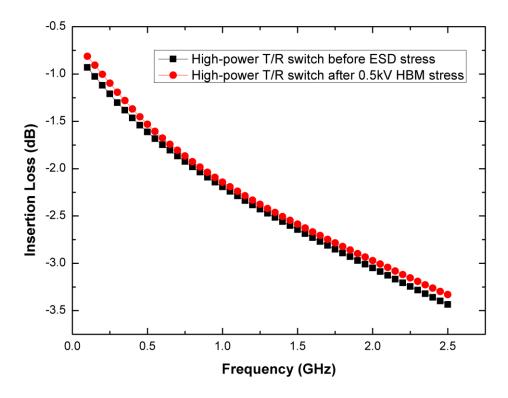

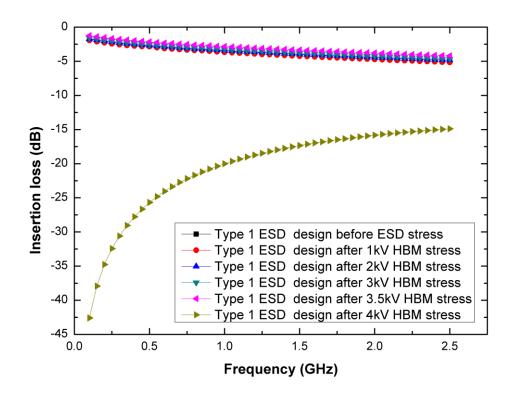

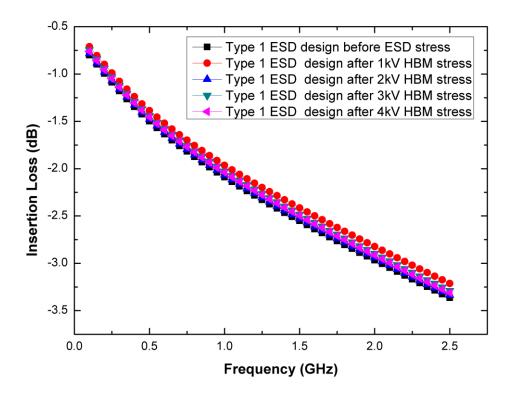

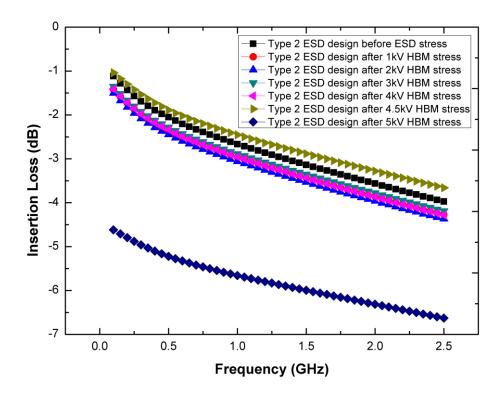

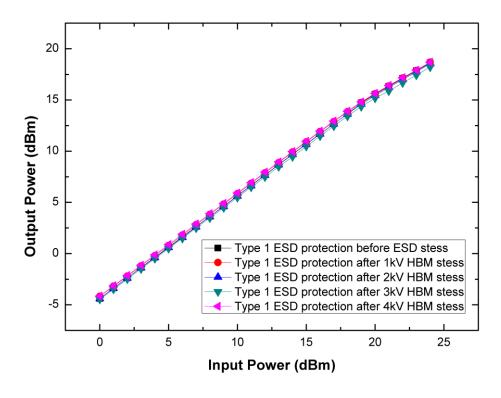

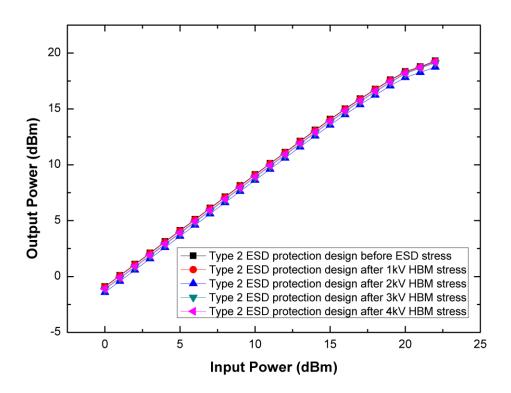

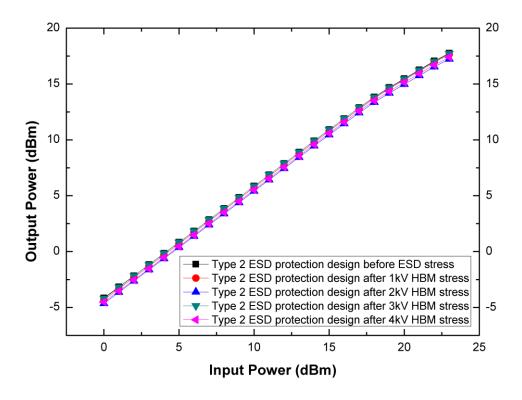

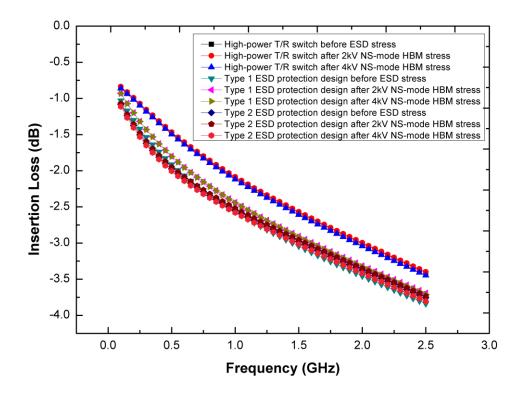

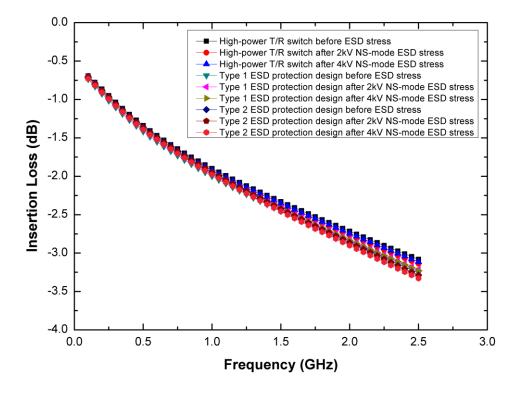

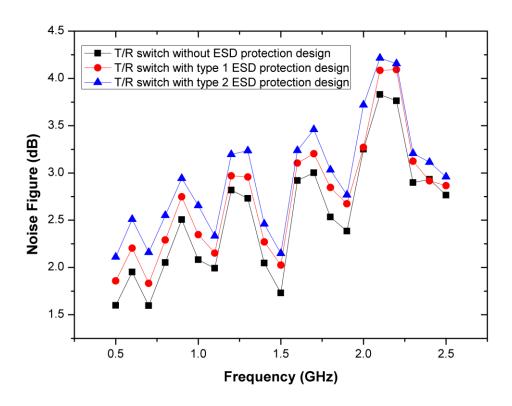

|                | 3.3.2 | Comparison of RF Performances Before ESD Stress                        | 62          |

|----------------|-------|------------------------------------------------------------------------|-------------|

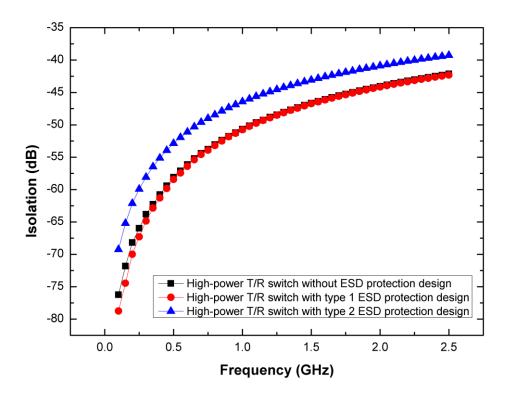

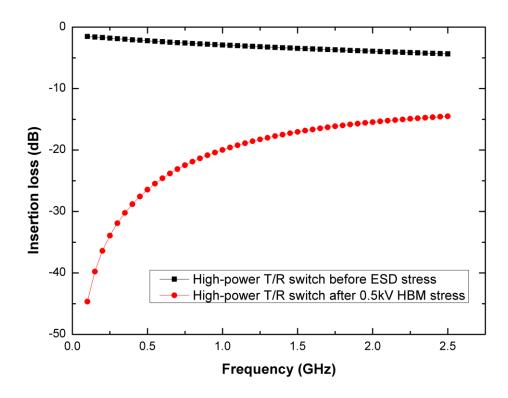

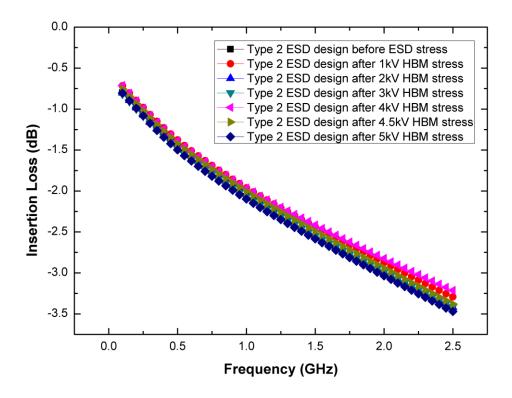

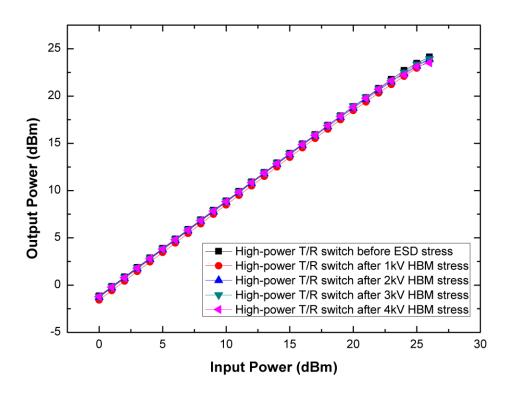

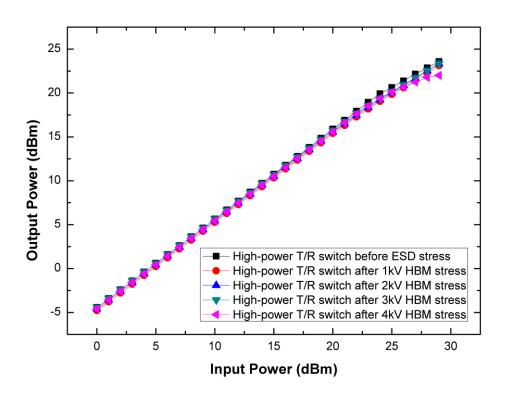

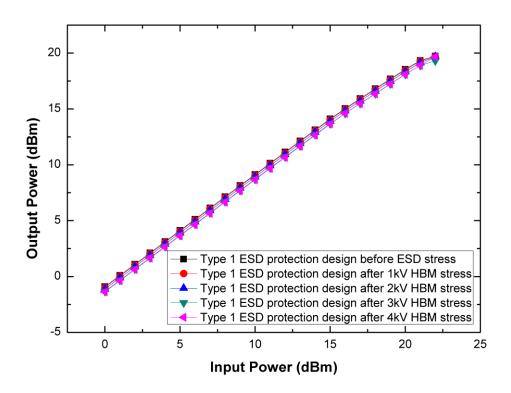

|                | 3.3.3 | Comparison of RF Performances After ESD Stress                         | 68          |

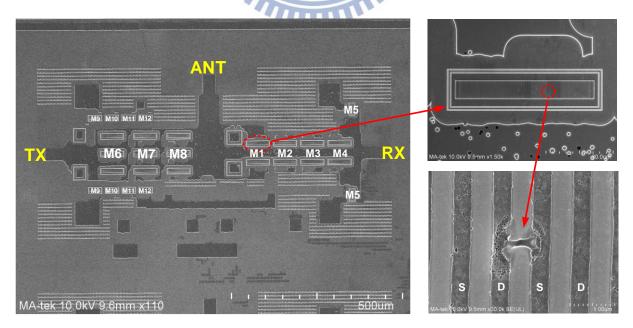

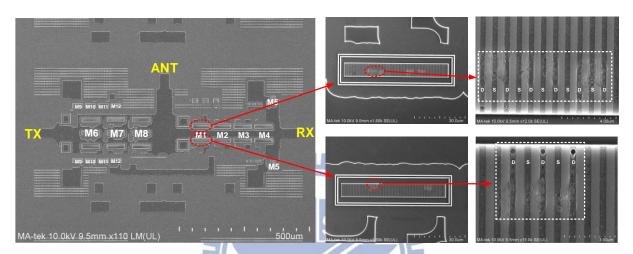

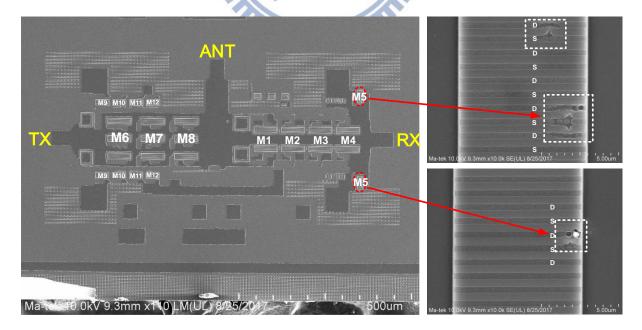

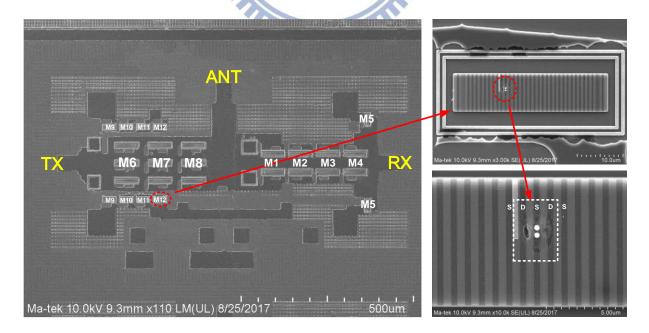

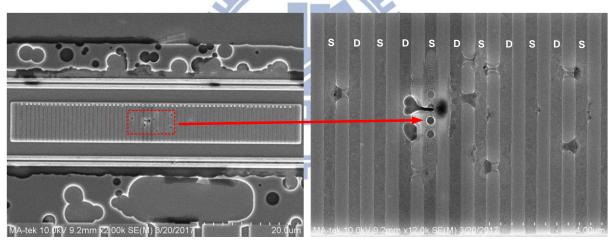

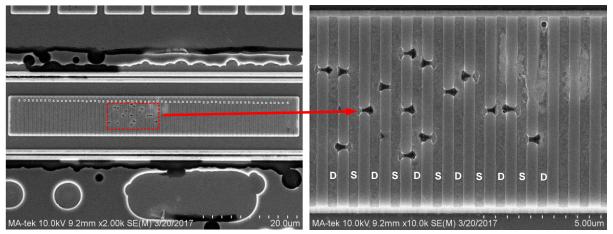

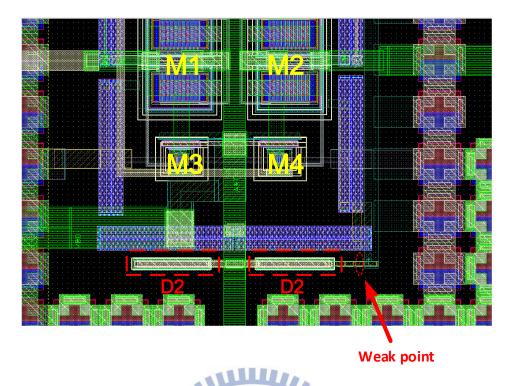

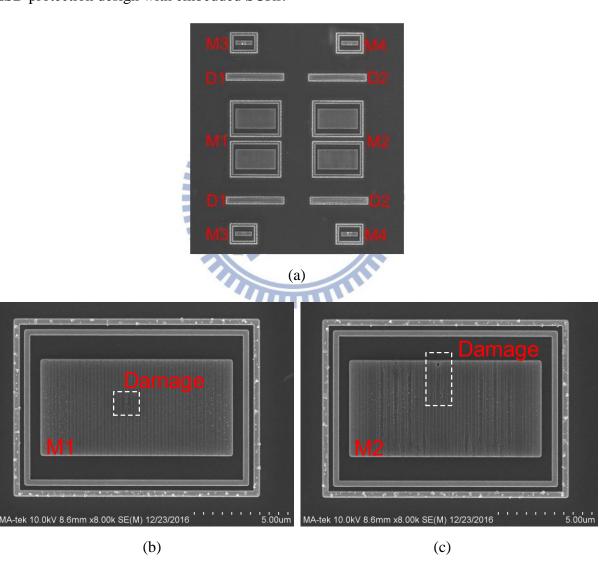

|                | 3.3.4 | Failure Analysis and Discussion                                        | 78          |

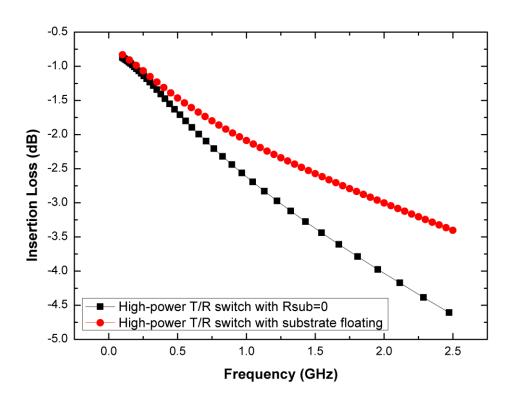

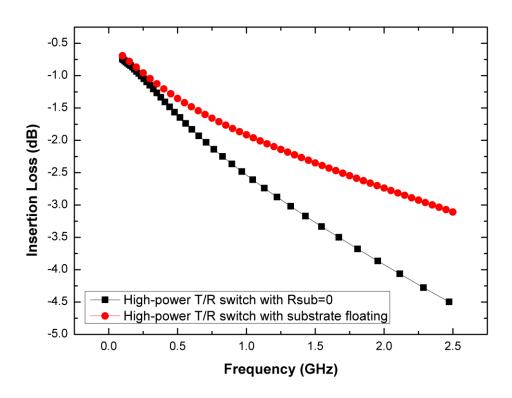

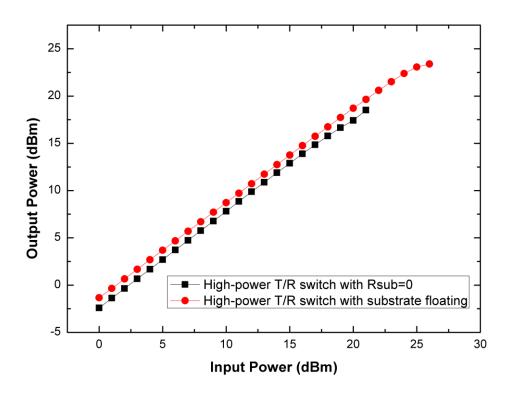

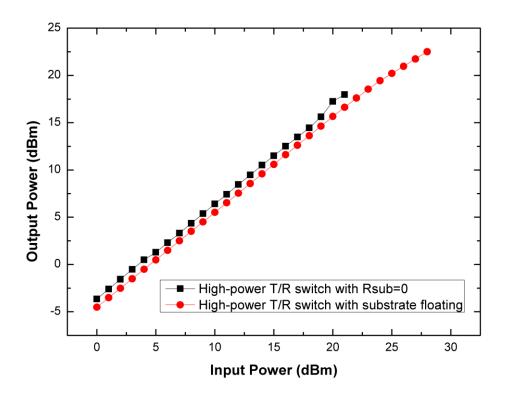

|                | 3.3.5 | The Effect of the Substrate Resistance                                 | 82          |

| 3.4            |       | Summary                                                                | 87          |

| Chapte         | er 4  | ESD Protection Design for Conventional T/R Switch                      | 88          |

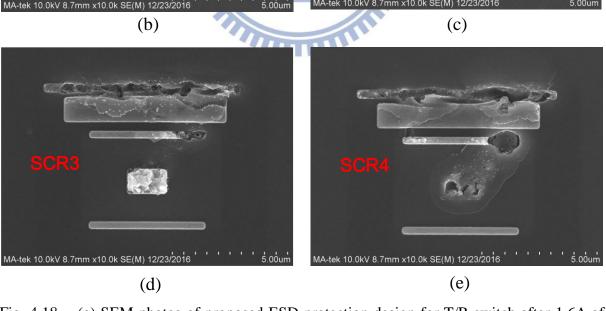

| 4.1            |       | Circuit Design of Conventional T/R Switch                              | 88          |

| 4.2            |       | Traditional ESD Protection Design for Conventional T/R Switch          | 89          |

| 4.3            |       | Proposed ESD Protection Design for Conventional T/R Switch             | 91          |

| 4.4            |       | Experimental Results of Conventional T/R Switch with Proposed ESD Prot | _           |

|                | 4.4.1 |                                                                        |             |

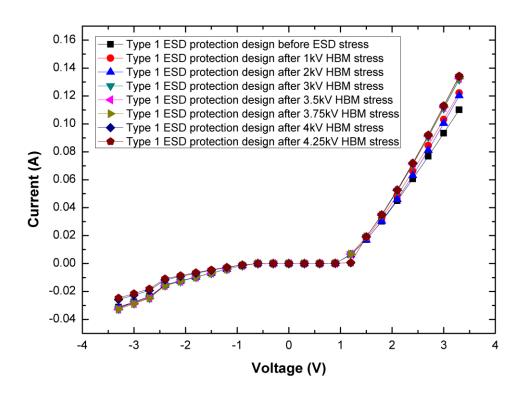

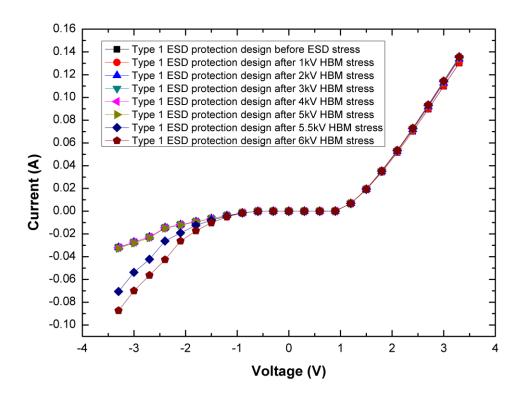

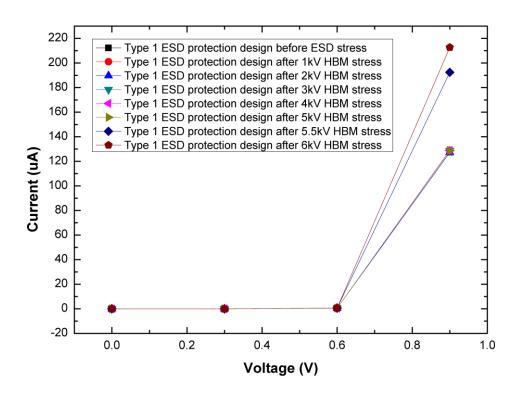

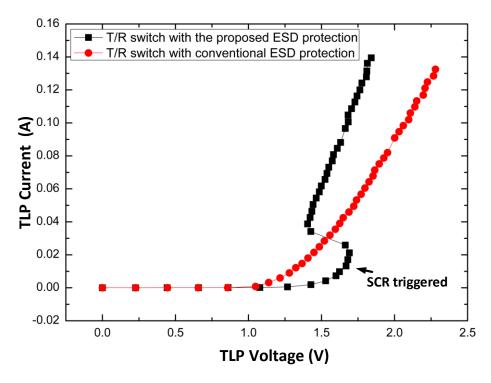

|                | 4.4.1 | ESD Levels Measured with ESD HBM Tester and TLP System                 |             |

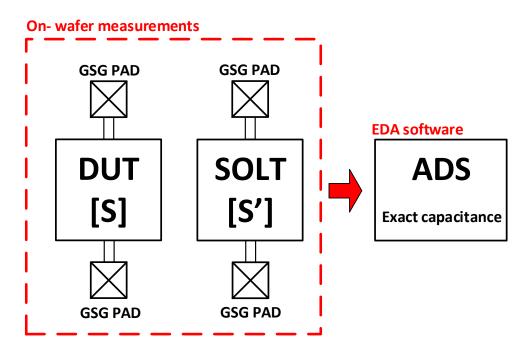

|                | 4.4.2 | Extracted Parasitic Capacitance after De-embedding Method              |             |

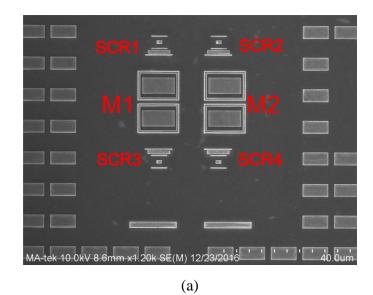

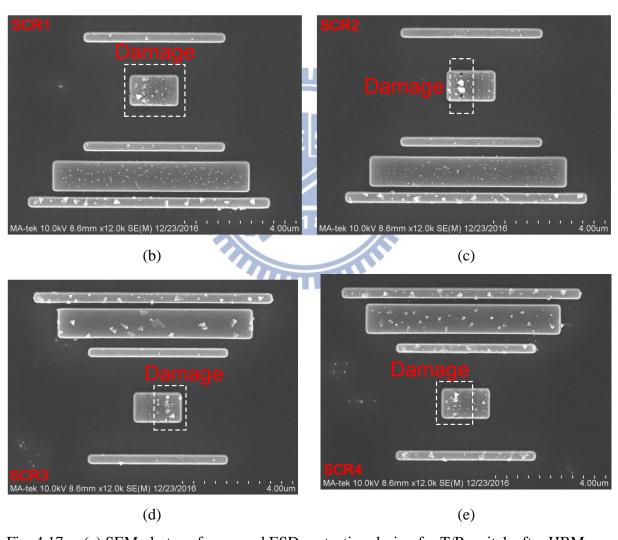

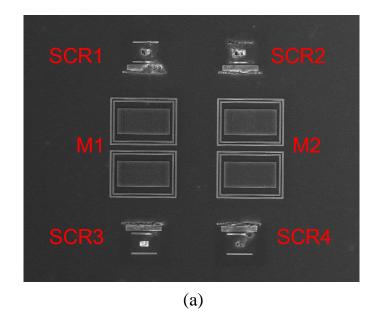

|                | 4.4.3 | Failure Analysis and Discussion                                        | 101         |

| 4.5            |       | Summary                                                                | 105         |

| Chapte         | er 5  | Future Work                                                            | 106         |

| 5.1            |       | Conclusions 1896                                                       | 106         |

| 5.2            |       | Future Work                                                            | 108         |

|                | 5.2.1 | Improvement of the Power Handling Capability of the T/R Switch         | 108         |

|                | 5.2.2 | ESD Protection Design for Different T/R Switches                       | 110         |

| Referei        | nce   |                                                                        | <b></b> 111 |

| <b>5</b> 724 - |       |                                                                        | 112         |

|                |       |                                                                        |             |

## **Table Captions**

| Table 3.1 | Simulation results of high-power T/R switch with ESD protection designs | 46  |

|-----------|-------------------------------------------------------------------------|-----|

| Table 3.2 | Measured HBM ESD levels of high-power T/R switch by ETS HBM simulator   | 53  |

| Table 3.3 | RF parameters of the high-power T/R switches measured at 0.9GHz         | 63  |

| Table 3.4 | RF parameters of the high-power T/R switches measured at 1.8GHz         | 63  |

| Table 3.5 | Comparison of HBM levels judged by DCIV curves and RF performance       | 77  |

| Table 3.6 | Comparison of HBM levels between Rsub=0 and substrate floating          | 85  |

| Table 4.1 | Measured HBM ESD levels by HBM tester                                   | 96  |

| Table 4.2 | Measured failure current (It2) by TLP systems                           | 97  |

| Table 4.3 | Comparison of ESD characteristics on PS-mode.                           | 105 |

## **Figure Captions**

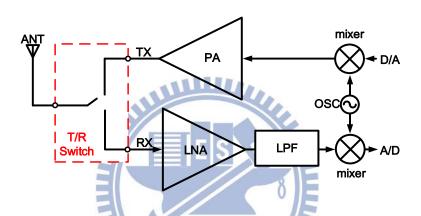

| Fig. 1.1.  | RF transceiver front-end circuit with T/R switch.                                                                                                                                                                                                                      | 2        |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

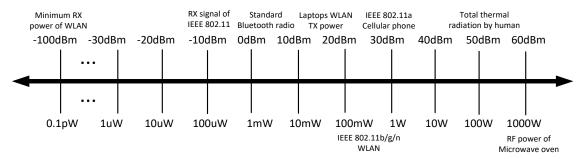

| Fig. 1.2.  | Spectrum of RF wireless applications.                                                                                                                                                                                                                                  | 3        |

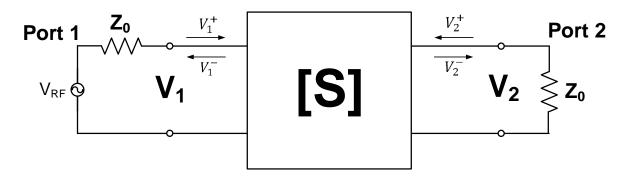

| Fig. 2.1.  | A two-port network describe with S-parameters.                                                                                                                                                                                                                         | 6        |

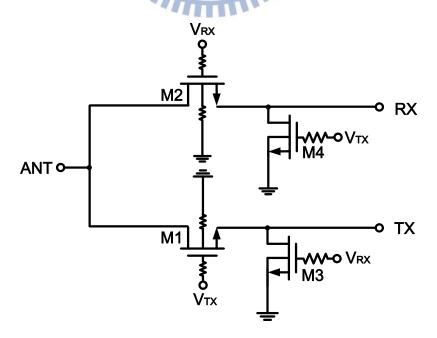

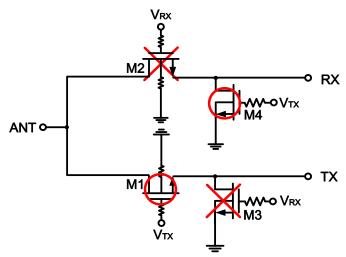

| Fig. 2.2.  | Conventional T/R switch without ESD protection.                                                                                                                                                                                                                        | 7        |

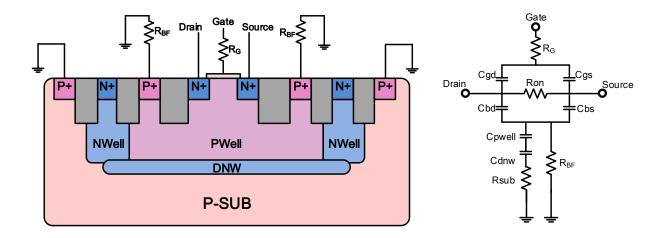

| Fig. 2.3.  | Cross-section view and equivalent circuit of the NMOS in T/R switch.                                                                                                                                                                                                   | 8        |

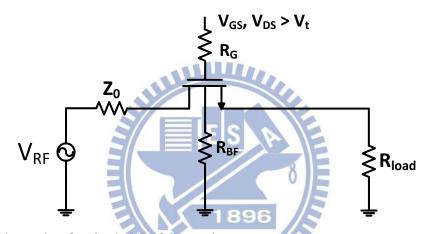

| Fig. 2.4.  | Schematic of a single NMOS transistor.                                                                                                                                                                                                                                 | 8        |

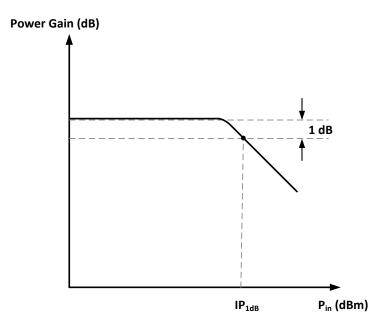

| Fig. 2.5.  | The plot of power gain versus input power.                                                                                                                                                                                                                             | 10       |

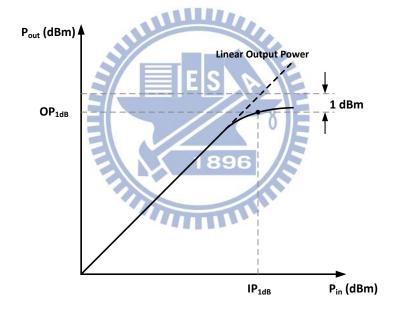

| Fig. 2.6.  | The plot of output power versus input power.                                                                                                                                                                                                                           | 10       |

| Fig. 2.7.  | T/R switch operates in transmit mode                                                                                                                                                                                                                                   | 11       |

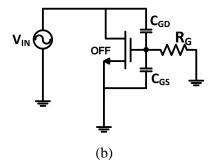

| Fig. 2.8.  | Off-state transistors (a) without gate resistor and (b) with gate resistor                                                                                                                                                                                             | 11       |

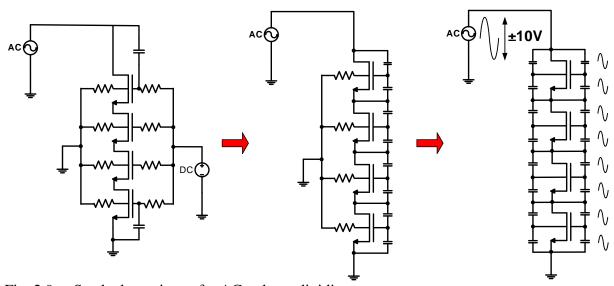

| Fig. 2.9.  | Stacked transistors for AC voltage dividing.                                                                                                                                                                                                                           | 12       |

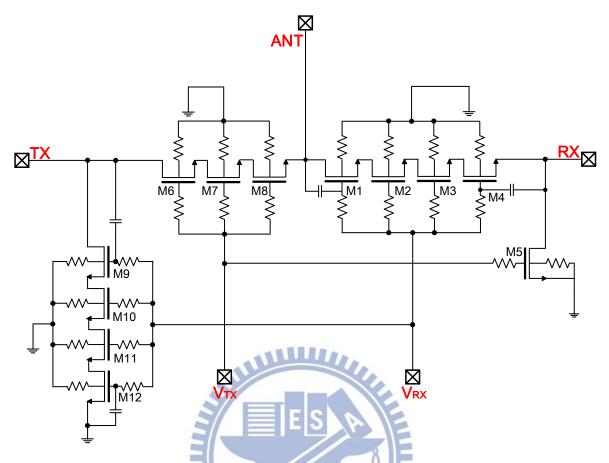

| Fig. 2.10. | High-power T/R switch without ESD protection circuit.                                                                                                                                                                                                                  | 13       |

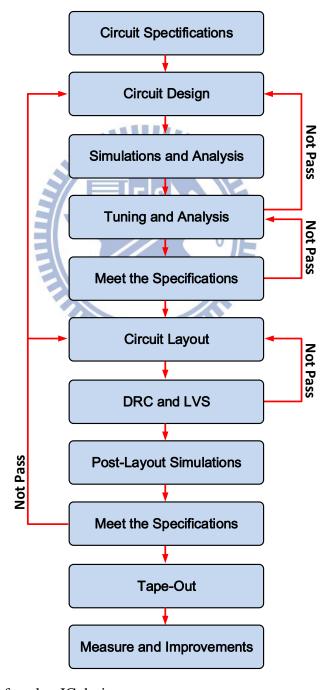

| Fig. 2.11. | Flow chart of analog IC design.                                                                                                                                                                                                                                        | 14       |

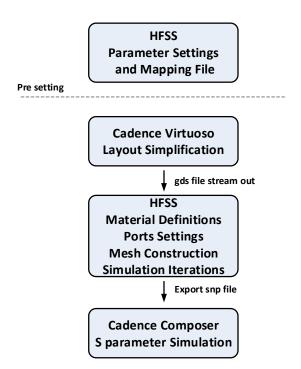

| Fig. 2.12. | Flow chart of analog IC design.  Design flow of electromagnetic simulation.                                                                                                                                                                                            |          |

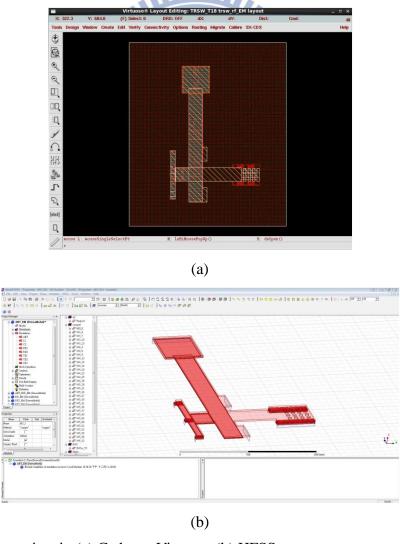

| Fig. 2.13. | Layout view in (a) Cadence Virtuoso (b) HFSS                                                                                                                                                                                                                           | 16       |

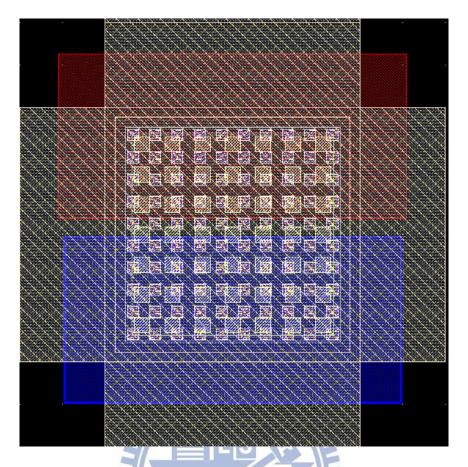

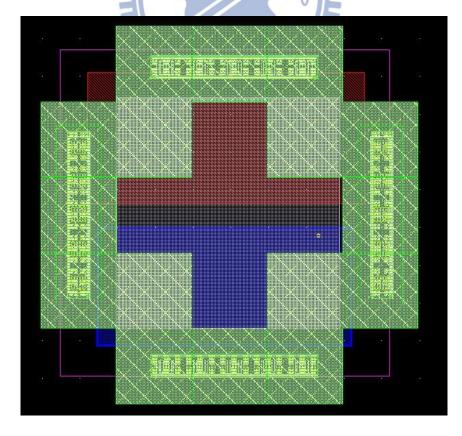

| Fig. 2.14. | Layout example of dummy cell for 0.18-µm process (6 metal layers).                                                                                                                                                                                                     | 18       |

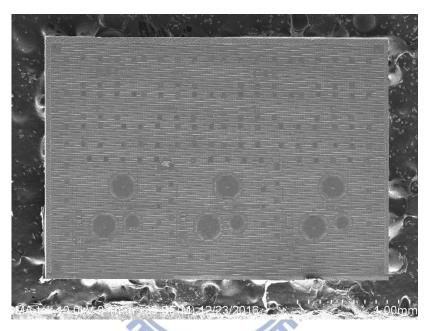

| Fig. 2.15. | Layout example of dummy cell for 90-nm process (9 metal layers)                                                                                                                                                                                                        | 18       |

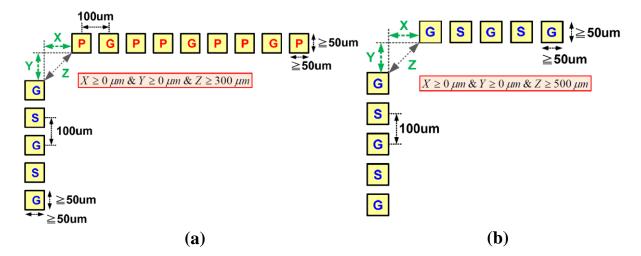

| Fig. 2.16. | Layout rules for (a) RF pads and DC pads and (b) RF pads and RF pads of 20-GHz or measurement in CIC (2016.10)                                                                                                                                                         | 19       |

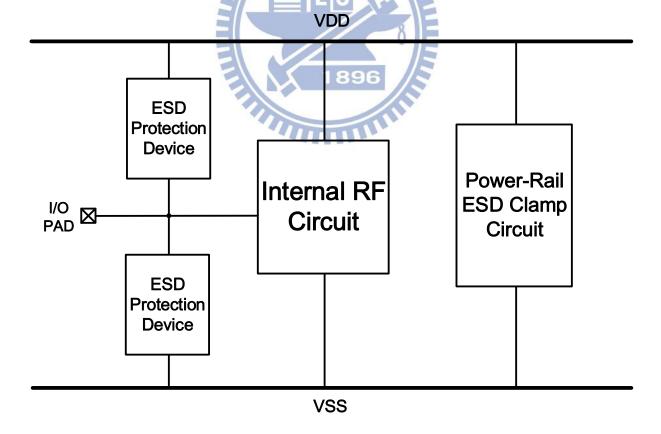

| Fig. 2.17. | Architecture of whole-chip ESD protection                                                                                                                                                                                                                              | 20       |

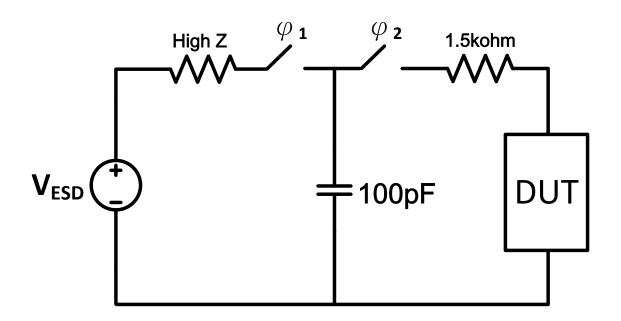

| Fig. 2.18. | Equivalent circuit of human body model ESD test.                                                                                                                                                                                                                       | 21       |

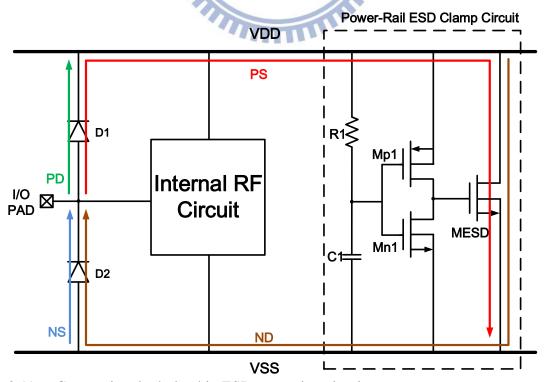

| Fig. 2.19. | Conventional whole-chip ESD protection circuit                                                                                                                                                                                                                         | 22       |

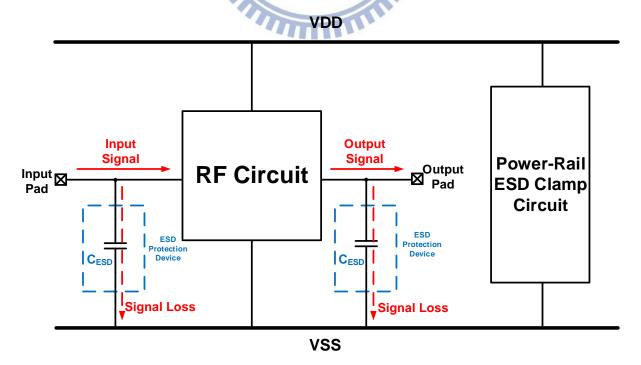

| Fig. 2.20. | Signal loss caused by the ESD protection device in RF circuit system.                                                                                                                                                                                                  | 23       |

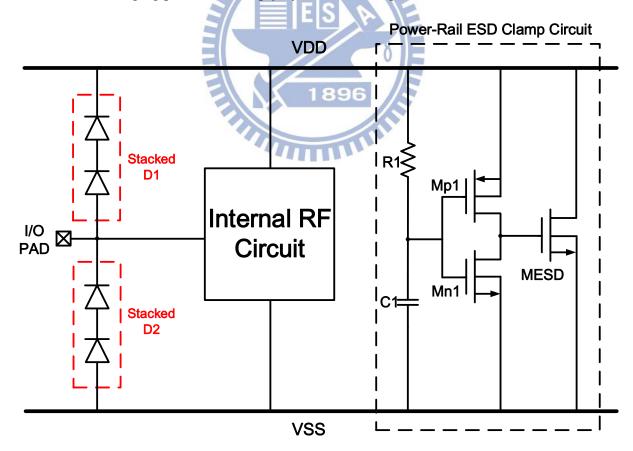

| Fig. 2.21. | ESD protection design with stacked diodes architecture.                                                                                                                                                                                                                | 24       |

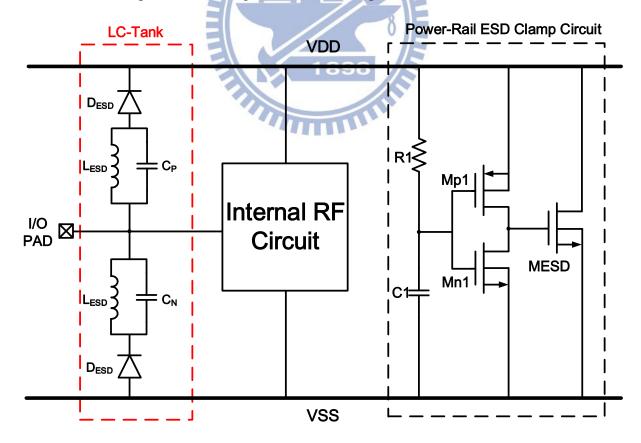

| Fig. 2.22. | ESD protection design with LC-tanks architecture.                                                                                                                                                                                                                      | 25       |

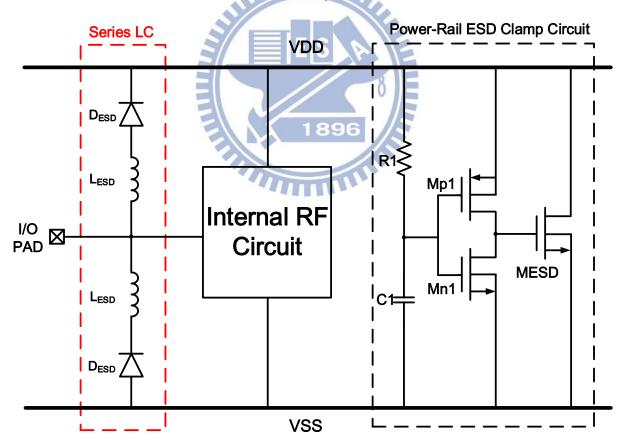

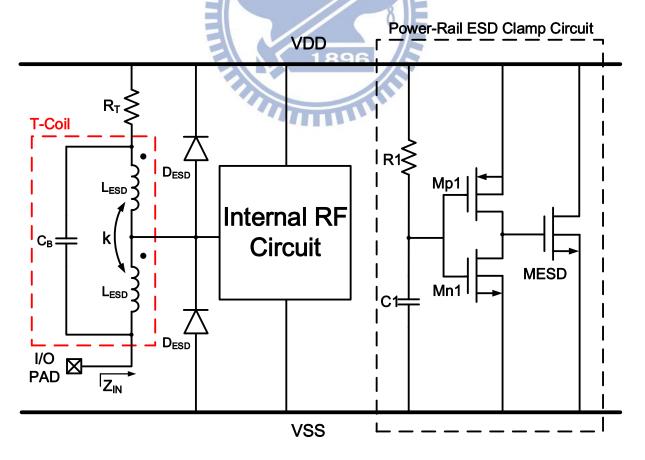

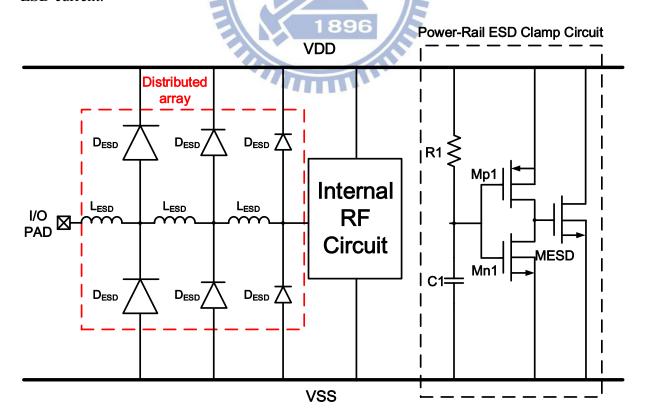

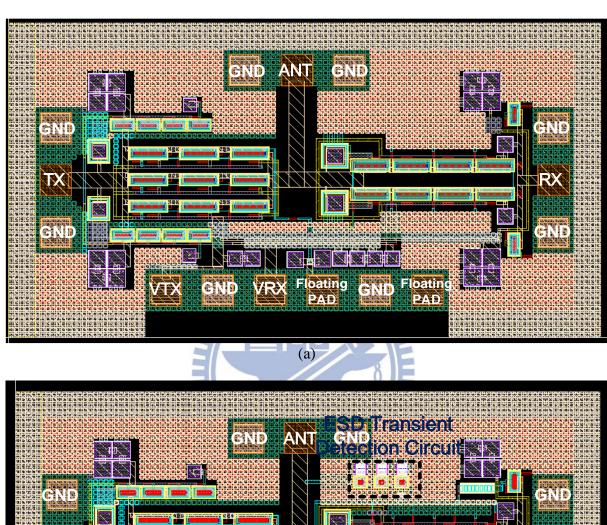

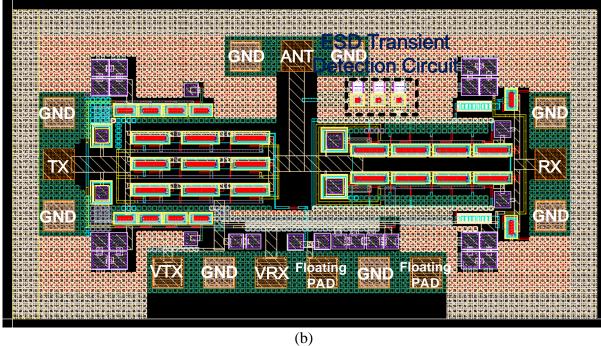

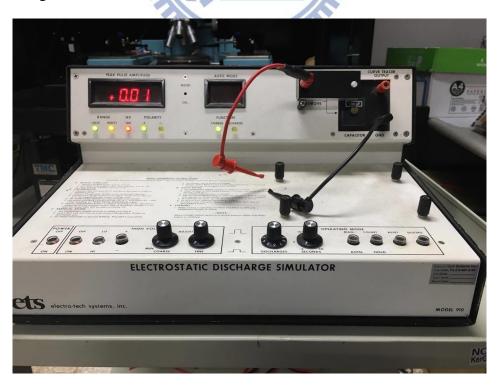

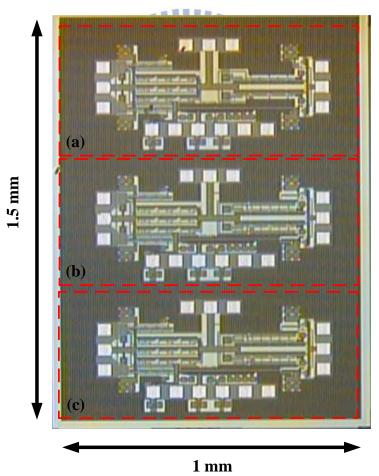

| Fig. 2.23. | ESD protection design with series LC architecture.                                                                                                                                                                                                                     | 26       |