# 國立交通大學電機學院電子工程學系 電子研究所博士論文

全金屬矽化物互補式金氧半奈米晶片之 静電放電防護電路設計與實現

DESIGN AND IMPLEMENTATION OF ESD PROTECTION

CIRCUITS IN NANOSCALE FULLY SILICIDED CMOS

#### **TECHNOLOGY**

研究生:葉致廷 (Chih-Ting Yeh)

指導教授:柯明道 (Ming-Dou Ker)

中華民國一〇二年二月

## 全金屬矽化物互補式金氧半奈米晶片之 靜電放電防護電路設計與實現

## DESIGN AND IMPLEMENTATION OF ESD PROTECTION CIRCUITS IN NANOSCALE FULLY SILICIDED CMOS TECHNOLOGY

研究生: 葉致廷 Student: Chih-Ting Yeh

指導教授: 柯明道 Adviser: Ming-Dou Ker

國立交通大學電機學院

電子工程學系電子研究所

博士論文

#### **A Dissertation**

Submitted to Department of Electronics Engineering

& Institute of Electronics

College of Electrical and Computer Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of Doctor of Philosophy

. . .

**Electronics Engineering**

February 2013 Hsinchu, Taiwan, Republic of China

中華民國一〇二年二月

## 全金屬矽化物互補式金氧半奈米晶片之 靜電放電防護電路設計與實現

研究生:葉致廷 指導教授:柯明道 博士

國立交通大學電機學院電子工程學系電子研究所

#### 摘要

隨著互補式金氧半製程的持續發展並微縮至奈米等級,閘極氧化層變得愈來愈薄且 擴散區的接面深度變得愈來愈淺,這些製程上的發展導致金氧半場效電晶體的閘極氧化 層崩潰電壓下降以及金氧半場效電晶體的閘極漏電流增加。閘極氧化層崩潰電壓的下降 會使得金氧半場效電晶體更容易受到靜電放電(Electrostatic Discharge, ESD)的轟擊而受 損,因為靜電放電的本質並未隨著金氧半製程的發展而微縮,閘極漏電流的增加會使得 靜電放電防護電路裡的金氧半場效電晶體在靜電放電事件與正常電路操作的情況下發 生電性功能失常的問題。在可靠度(Reliability)領域中,靜電放電已成為積體電路產品在 量產過程中最為重要的問題,對於所有的電子產品在設計階段時就必須謹慎地將靜電放 電等問題納入考慮以符合可靠度的各種規範。為了達到全晶片靜電放電防護設計,所有 的銲墊(Pad),包括輸入/輸出(input/output)銲墊以及電源/接地(VDD/VSS)銲墊,皆必 須具有靜電放電防護電路以提供有效的靜電放電防護予積體電路。介於輸入/輸出銲墊 以及電源/接地銲墊的靜電放電防護元件無可避免地會對射頻(Radio Frequency, RF)與 高速電路的訊號路徑產生寄生效應,而這些電路對於寄生效應是非常敏感的,因為過大 的寄生效應會造成射頻與高速電路的電路性能嚴重衰減,因此對於應用在射頻與高速電 路的靜電放電防護元件之挑戰則是靜電放電防護元件能夠承受最大的靜電放電耐受度 並且達到其寄生效應的最小化。此外,介於電源/接地銲墊之間的靜電放電防護電路則 可在電源軌線間提供有效的靜電放電防護,雖然電源軌線間靜電放電箝制電路的寄生效 應對於內部電路毫無影響,但是金氧半場效電晶體閘極氧化層崩潰電壓的下降以及閘極 漏電流的增加仍然大幅提高了靜電放電防護設計上的困難度。另外,積體電路的單位面 積製作成本隨著互補式金氧半製程的持續微縮而快速地增加,因此,在佈局面積上具有 高度效益的電源軌線間靜電放電箝制電路也是另一個設計上的挑戰。基於以上所提及之 設計挑戰,本論文的研究主題包括:(1)適用於射頻與高速輸入/輸出電路的靜電放電防 護二極體、(2)不需電容元件之電源軌線間靜電放電箝制電路、(3)具有等效靜電放電偵

測機制的電源軌線間靜電放電箝制電路、(4)具有閘極漏電流與閘極氧化層可靠度之設計考量的電源軌線間靜電放電箝制電路、(5)不需電阻元件之電源軌線間靜電放電箝制電路。

本論文第二章提出可適用於射頻前端與高速輸入/輸出銲墊的新型靜電放電防護二極體元件,其佈局型式分為八角形、四方中空形、八角中空形、多重四方形、以及多重四方中空形。在 90 奈米互補式金氧半製程的實驗結果顯示,相較於長條形與四方形佈局型式的二極體元件在相同的靜電放電耐受度之下可以達到較小的寄生電容,因此射頻前端與高速輸入/輸出電路的訊號衰減程度可以被降低。

在本論文第三章中,不需使用電容元件的新型靜電放電偵測電路已被提出並且驗證在 65 奈米 1.2 伏特的互補式金氧半製程。相較於傳統的 RC-based 靜電放電偵測電路,新型設計的佈局面積可縮小超過 54%,具有可調整維持電壓的新型設計在快速電源啟動以及暫態雜訊干擾的情形下擁有非常好的抗誤觸發與抗暫態引起的閂鎖效應之能力。

本論文第四章提出一個以大通道電晶體作為靜電放電箝制元件並且利用大通道電晶體的寄生二極體之電源軌線間靜電放電箝制電路,並且驗證在65 奈米1.2 伏特的互補式金氧半製程。利用二極體連接方式的電晶體作為等效電阻以及利用大通道電晶體寄生逆偏二極體作為等效電容,新型的電容耦合以及 RC-based 靜電放電偵測機制可不使用實際的電阻與電容元件就能達成,並且相較於傳統的 RC-based 靜電放電偵測電路,可顯著地縮小所需之佈局面積達82%。

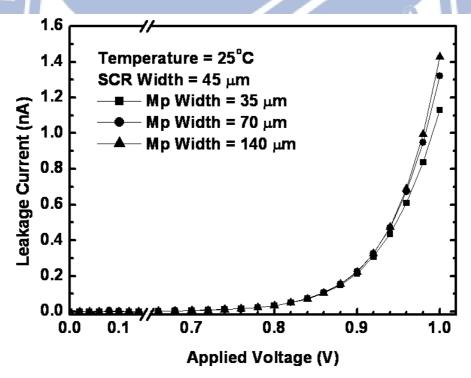

本論文第五章提出一個僅使用薄閘極氧化層元件以及使用矽控整流器 (Silicon-Controlled Rectifier, SCR)作為靜電放電箝制元件的電源軌線間靜電放電箝制電路,並且驗證在65 奈米1 伏特的互補式金氧半製程。藉由降低在靜電放電偵測電路中元件閘極氧化層的跨壓,提出的電源軌線間靜電放電箝制電路可具有低漏電流,此外,藉由佈局的方式還可以將靜電放電偵測電路完全嵌入至矽控整流器元件中。在本章中,一個可操作在2倍 VDD 的電源軌線間靜電放電箝制電路也被提出,並且驗證在相同的製程。根據實驗結果,提出的電源軌線間靜電放電箝制電路搭配50微米寬的矽控整流器元件在偏壓1 伏特的正常電路操作與室溫的情形下僅消耗34.1 奈安培的漏電流。

本論文第六章提出一個僅使用薄閘極氧化層元件、使用矽控整流器作為靜電放電箝制元件、以及不需使用電阻元件的電源軌線間靜電放電箝制電路,並且驗證在65 奈米1 伏特的互補式金氧半製程。技巧性地使用閘極漏電流以實現等效電阻,RC-based 靜電放電偵測機制可不使用實際的電阻元件就能達成並且顯著地縮小所需之佈局面積。不需電阻元件的電源軌線間靜電放電箝制電路搭配45 微米寬的矽控整流器在偏壓1 伏特的正常電路操作與室溫的情形下僅消耗1.43 奈安培的極低漏電流。

第七章總結本論文的研究成果,並提出數個接續本論文研究方向的研究題目。本論 文所提出的各項新型設計,皆已經由實驗晶片進行驗證。本論文已有數篇國際期刊與國 際研討會論文發表。

## DESIGN AND IMPLEMENTATION OF ESD PROTECTION CIRCUITS IN NANOSCALE FULLY SILICIDED CMOS TECHNOLOGY

Student: Chih-Ting Yeh Adviser: Dr. Ming-Dou Ker

Department of Electronics Engineering and Institute of Electronics

College of Electrical and Computer Engineering

National Chiao Tung University

#### **Abstract**

As CMOS technology is continuously scaled down to nanoscale, the gate oxide becomes thinner and the diffusion junction depth becomes shallower. These lead to the reduced gate oxide breakdown voltage and increased gate leakage current of MOS transistor. The reduced gate oxide breakdown voltage makes the MOS transistor more vulnerable to electrostatic discharge (ESD) because ESD is not scaled down with the CMOS technology. The gate leakage current makes the MOS transistors in ESD protection circuit malfunction during ESD stresses and normal circuit operating condition. ESD is one of the most important reliability issues for the integrated circuit (IC) during mass production. It must be taken into consideration during the design phase to meet the reliability specifications for all microelectronic products. For whole-chip ESD protection design, all pads, including the input/output (I/O) pads and VDD/VSS pads, are necessary to be implemented with ESD protection circuits to provide effective ESD protection for the IC. The ESD protection devices between the I/O pads and VDD/VSS pads inevitably cause parasitic effects on the signal path of RF front-end and high-speed circuits, which are very sensitive to those parasitic effects. The challenge of ESD protection devices for RF front-end and high-speed circuits is to sustain the highest ESD level and to achieve the smallest parasitic effects. Moreover, the ESD protection circuits between the VDD/VSS pads are necessary to provide ESD protection between the power rails. Although the parasitic effects of power-rail ESD clamp circuit have no impact on the internal circuits, the reduced gate oxide breakdown voltage and increased gate leakage current of MOS transistor greatly increase the difficulty of ESD protection design. In addition, the fabricated cost per unit area of the IC is dramatically increased with the continuously scaled-down CMOS technology. Therefore, the power-rail ESD clamp circuit with high efficiency of layout area is another design challenge. The research topics based on aforementioned design challenges in this dissertation including: (1) ESD protection diode for RF and high-speed I/O applications, (2) capacitor-less power-rail ESD clamp circuit, (3) power-rail ESD clamp circuit with equivalent ESD-transient detection mechanism, (4) power-rail ESD clamp circuit with considerations of gate leakage current and gate oxide reliability, and (5) resistor-less power-rail ESD clamp circuit.

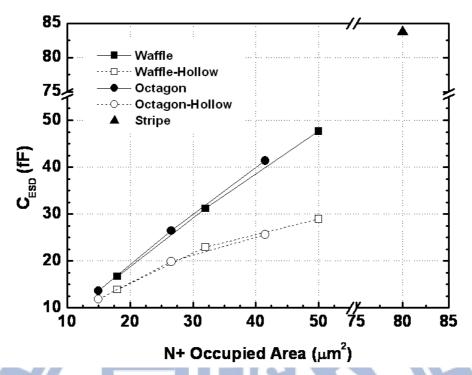

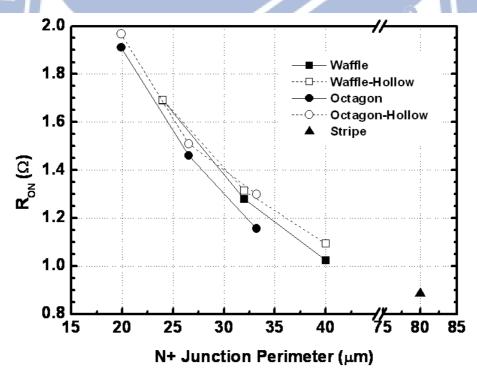

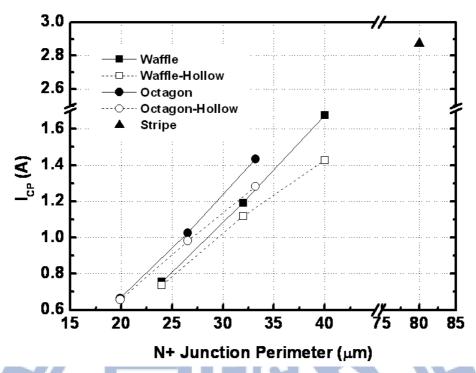

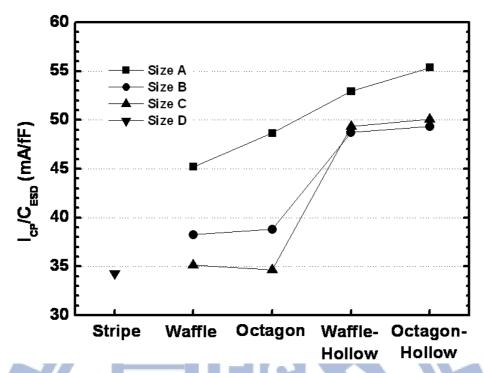

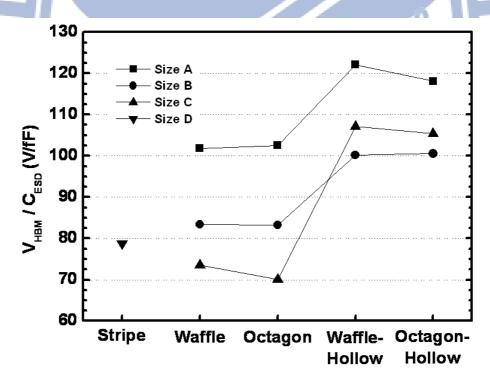

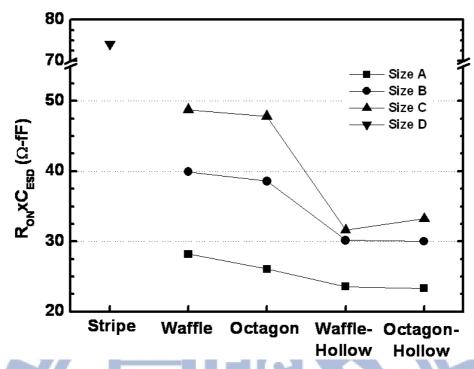

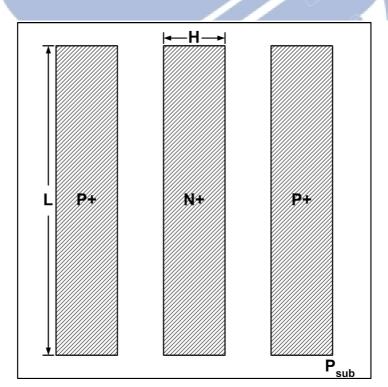

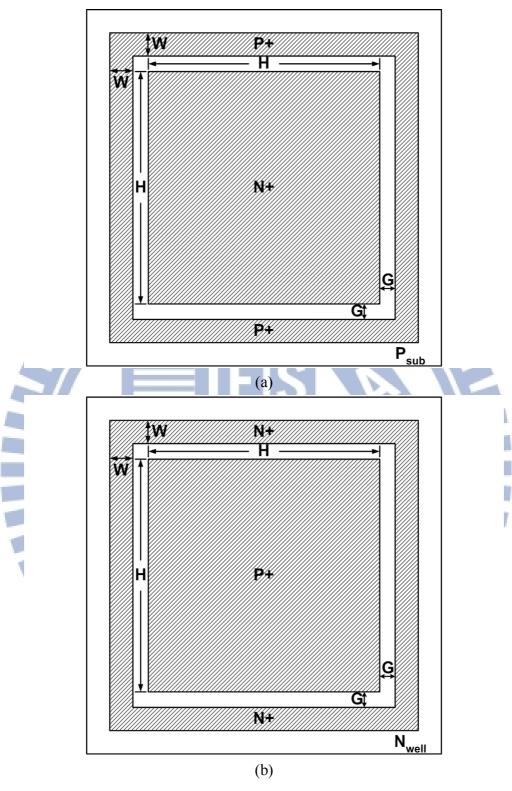

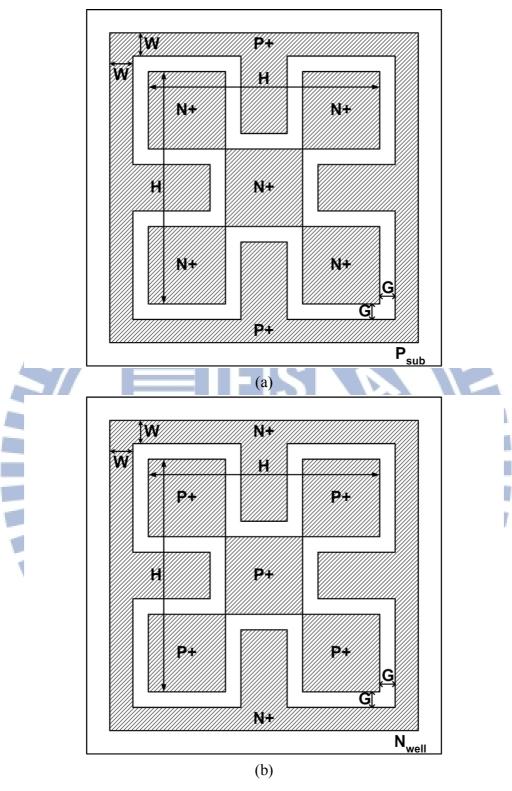

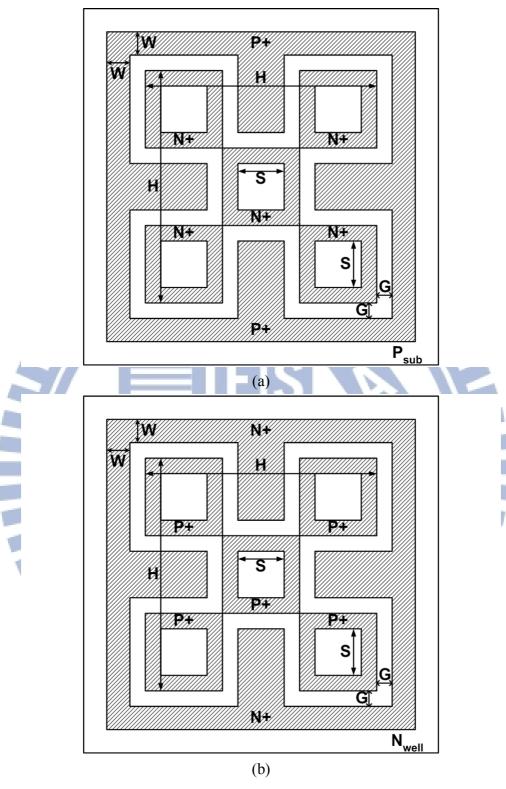

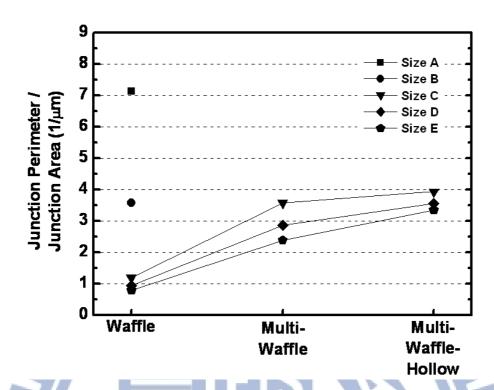

In Chapter 2, new ESD protection diodes drawn in the octagon, waffle-hollow, octagon-hollow, multi-waffle, and multi-waffle-hollow layout styles are presented in a 90nm CMOS process. The experimental results confirmed that they can achieve smaller parasitic capacitance under the same ESD robustness level as compared to the stripe and waffle diodes. Therefore, the signal degradation of RF and high-speed transmission can be reduced.

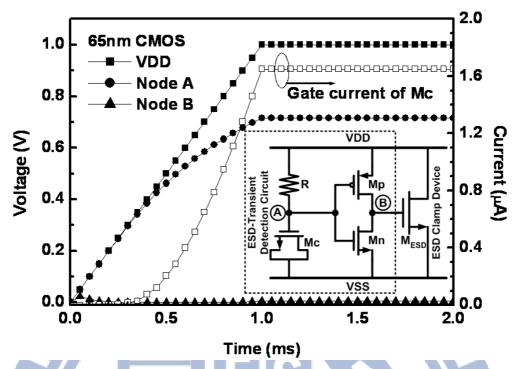

In Chapter 3, a new ESD-transient detection circuit without using the capacitor has been proposed and verified in a 65nm 1.2V CMOS process. The layout area of the new ESD-transient detection circuit can be greatly reduced by more than 54%, as compared to the traditional *RC*-based one. The new ESD-transient detection circuit with adjustable holding voltage has better immunity against mis-trigger and transient-induced latch-on event under the fast power-on and transient noise conditions.

In Chapter 4, a power-rail ESD clamp circuit realized with ESD clamp device drawn in the layout style of BigFET, and with parasitic diode of BigFET, is proposed and verified in a 65nm 1.2V CMOS process. Utilizing the diode-connected MOS transistor as the equivalent large resistor and parasitic reverse-biased diodes of BigFET as the equivalent capacitors, the new RC-based and capacitance-coupling ESD-transient detection mechanism can be achieved without using an actual resistor and capacitor to significantly reduce the layout area by  $\sim 82\%$ , as compared to the traditional RC-based ESD-transient detection circuit.

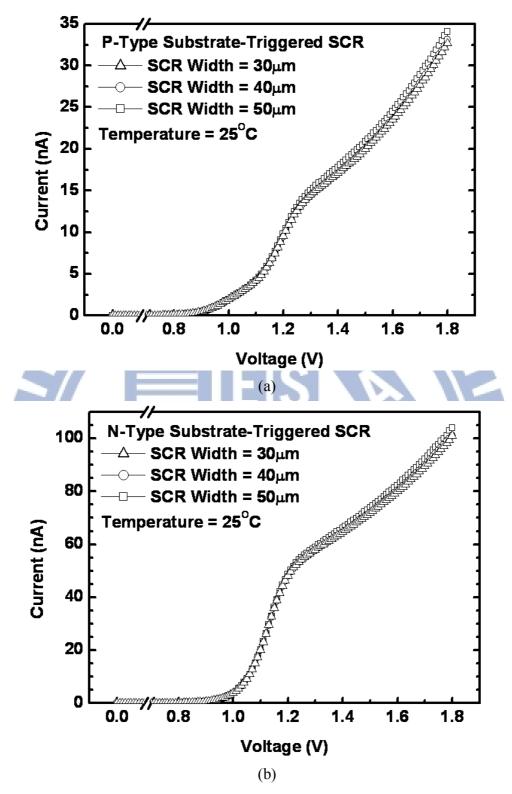

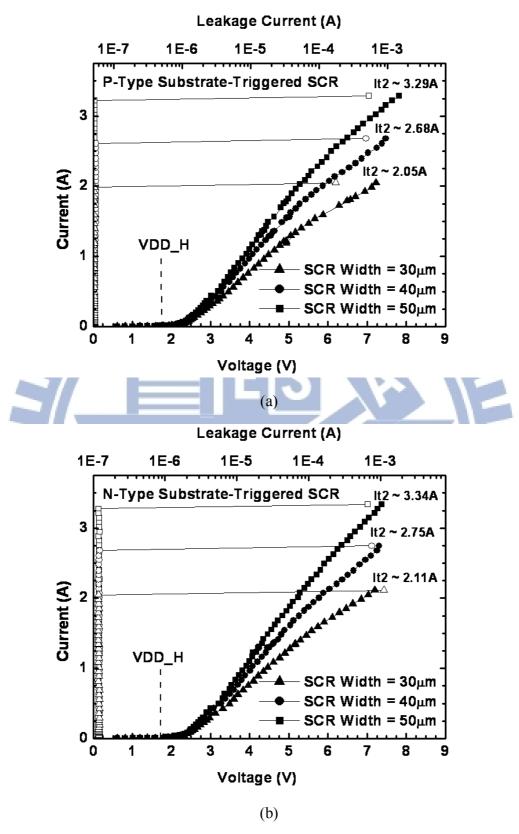

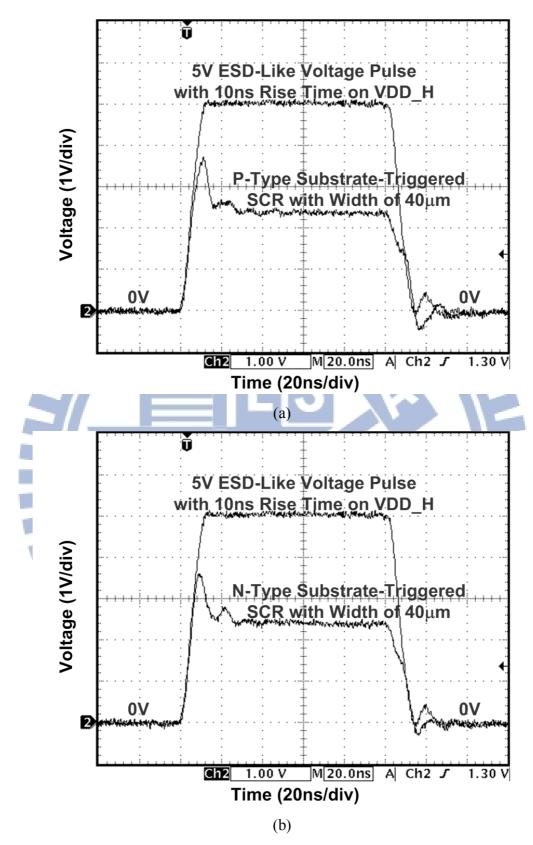

In Chapter 5, a power-rail ESD clamp circuit realized with only thin gate oxide devices and with SCR as main ESD clamp device has been proposed and verified in a 65nm 1V CMOS process. By reducing the voltage difference across the gate oxide of the devices in the ESD-transient detection circuit, the proposed design can achieve a low standby leakage current. In addition, the ESD-transient detection circuit can be totally embedded in the SCR device by modifying the layout structure. In this chapter, a 2×VDD-tolerant power-rail ESD clamp circuit has also been proposed and verified in the same CMOS process. The proposed design with SCR width of 50µm can achieve a low standby leakage current of 34.1nA at room temperature under the normal circuit operating condition with 1.8V bias.

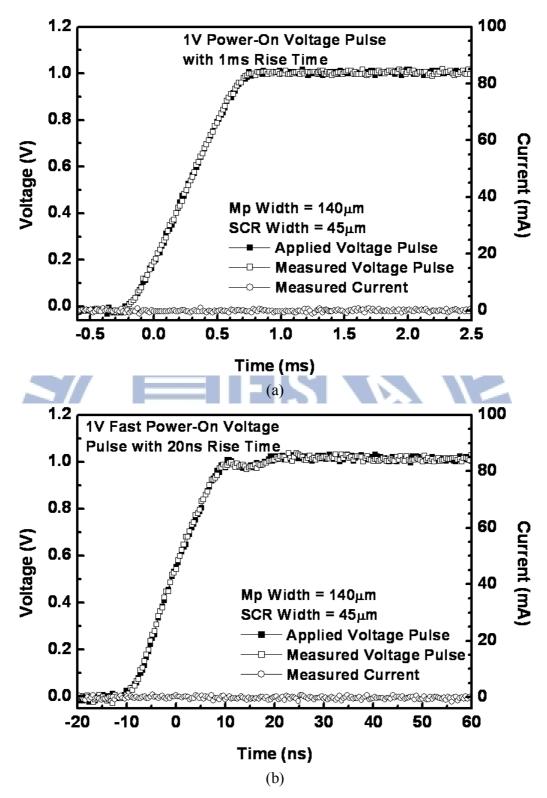

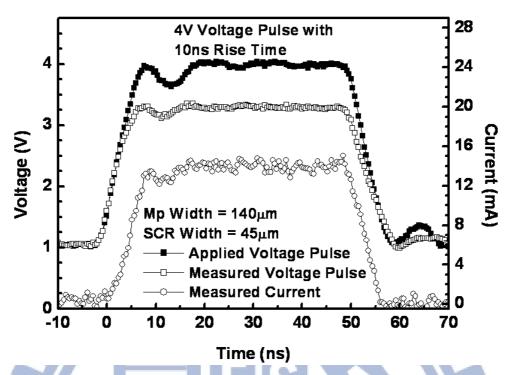

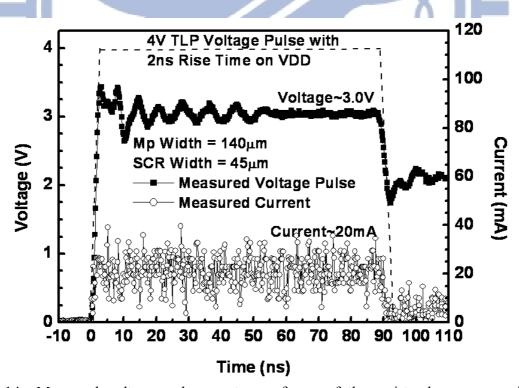

In Chapter 6, a resistor-less power-rail ESD clamp circuit realized with only thin gate oxide devices, and with SCR as main ESD clamp device, has been proposed and verified in a 65nm 1V CMOS process. Skillfully utilizing the gate leakage current to realize the equivalent resistor, the *RC*-based ESD-transient detection mechanism can be achieved without using an actual resistor. The resistor-less power-rail ESD clamp circuit with SCR width of 45µm can achieve an ultra-low standby leakage current of 1.43nA at room temperature under the normal circuit operating condition with 1V bias.

In this dissertation, several novel designs have been proposed in the aforementioned research topics. Measured results of the fabricated test chips have demonstrated the performance improvement. The innovative designs and achievements of this dissertation have been published or submitted to several international journals and conferences.

#### 誌 謝

首先我要感謝我的指導教授柯明道教授三年多來的耐心指導與鼓勵,使我能夠順利 完成博士學業。在指導教授循序漸進的教誨下,讓我得以在積體電路靜電放電防護設計 的領域中,由入門到能夠獨立解決問題。此外,指導教授認真的研究態度與嚴謹的處事 原則,也讓我學習到挑戰困難與解決問題的正確態度與方法。雖然在過程中倍感艱辛, 也經歷了不少挫折,然而卻讓我獲益良多。指導教授為研究群同學爭取的許多福利,更 讓人感念在心。

感謝吳重雨教授、王朝欽教授、郭治群教授、陳科宏教授、晶焱科技的姜信欽副總 以及國家晶片系統設計中心的邱進峯博士在百忙之中抽空擔任我的口試委員,並給予珍 貴的指導與建議,讓此博士論文更加完整。

在求學的這段過程中,「工業技術研究院資訊與通訊研究所」的「測試工程部」對於我的研究給予最大的支持與協助,從實驗晶片的下線及量測設備的支援協助,都是使得我的實驗研究能夠順利完成的主要原因。在此特別感謝吳文慶組長、朱元華組長、吳忠霖經理所給予的支持與鼓勵,也要感謝梁詠智、蔡昆儒以及曾任職於工研院的陳世宏博士、張伯瑋、江哲維、張信源、蔡孟庭、梁佑瑋、日本阪和電子的長谷部先生、長谷川先生、澤田先生在知識上與實驗上的協助,使我的研究論文能夠在國際上順利發表,獲得肯定。

感謝實驗室的顏承正博士、林群祐博士、王暢資博士、王資閱博士、陳穩義博士、 竹立煒博士、邱柏硯、陸亭州、蔡惠雯、艾飛、黃筱晴、李易儒、郭品宏、蔡翔宇、戴 嘉岑諸位實驗室學長、同學及學弟妹們,在我博士班的這個階段,於各方面給了我不少 的幫忙,使我能順利完成我的論文。也感謝實驗室助理卓慧貞小姐在實驗室行政事務上 的許多協助。

最後,我要致上我最深的感謝給予我的先父葉學文先生、母親郭瑞香女士、岳父江正國先生、已故岳母李玉玲女士、妹妹葉純茵小姐、愛妻江庭筠小姐、兒子葉詠齊以及女兒葉詠恩,有了你們無怨無悔、永無止盡的付出、鼓勵、支持、照顧與歡笑,才有我今日的成就,在此衷心地感謝你們。另外,在這幾年所有與我相處過的師長、朋友、同事、學長姐與學弟妹們,能與你們同在這一階段成長是我畢生的榮幸,願大家都能平安喜樂。

葉 致 廷謹誌於竹塹交大一○二年 二月

### **Contents**

| Abstract (Chinese)                                                    | i      |

|-----------------------------------------------------------------------|--------|

| Abstract (English)                                                    | iv     |

| Acknowledgements                                                      | vii    |

| Contents                                                              | viii   |

| Figure Captions                                                       | xiv    |

| Figure Captions  Table Captions  Chapter 1 Introduction               | xxviii |

| Chapter 1 Introduction                                                | 1      |

| 1.1 Background of Whole-Chip ESD Protection Design                    | 1      |

| 1.2 Organization of This Dissertation                                 | 3      |

| Chapter 2 ESD Protection Diode for RF and High-Speed I/O Applications | 9      |

| 2.1 Background                                                        | 9      |

| 2.2 Octagon, Waffle-Hollow, and Octagon-Hollow Layout Styles          | 11     |

| 2.2.1 Diode with Stripe Layout Style                                  | 11     |

| 2.2.2 Diodes with Waffle and Octagon Layout Styles                    | 11     |

| 2.2.3 Diodes with Waffle-Hollow and Octagon-Hollow Layout Styles      | 12     |

| 2.2.4 Interconnect Routing of the Diodes                              | 13     |

| 2.2.5 Performance Evaluations                                         | 13     |

| 2.2.6 Experimental Results                                            | 14     |

| 2.2.6.1 Parasitic Capacitance                                         | 14     |

| 2.2.6.2 Transmission Line Pulsing (TLP) Measurement                   | 15     |

| 2.2.6.3 ESD Robustness                                                | 16     |

| 2.2.7 FOM Comparison and Discussion                                   | 16     |

| 2.3 Multi-Waffle and Multi-Waffle-Hollow Layout Styles                             | 18 |

|------------------------------------------------------------------------------------|----|

| 2.3.1 Diodes with Stripe and Waffle Layout Styles                                  | 18 |

| 2.3.2 Diodes with Multi-Waffle and Multi-Waffle-Hollow Layout Styles               | 19 |

| 2.3.3 Performance Evaluations                                                      | 21 |

| 2.3.4 Experimental Results                                                         | 21 |

| 2.3.4.1 Parasitic Capacitance                                                      | 21 |

| 2.3.4.2 TLP Measurement 2.3.4.3 ESD Robustness 2.3.5 FOM Comparison and Discussion | 22 |

| 2.3.4.3 ESD Robustness                                                             | 23 |

| 2.3.5 FOM Comparison and Discussion                                                | 23 |

| 2.4 Summary ES                                                                     | 25 |

| Chapter 3 Capacitor-Less Design of Power-Rail ESD Clamp Circuit                    | 53 |

| 3.1 Background                                                                     | 53 |

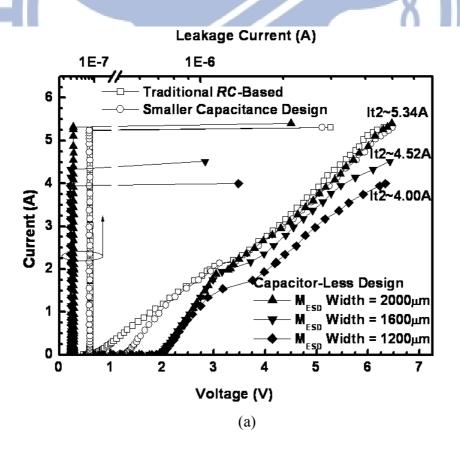

| 3.2 Power-Rail ESD Clamp Circuit with ESD Clamp nMOS Transistor                    | 54 |

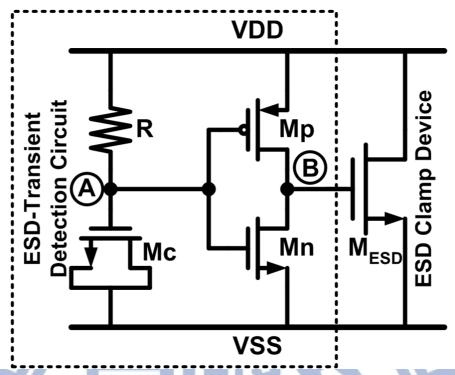

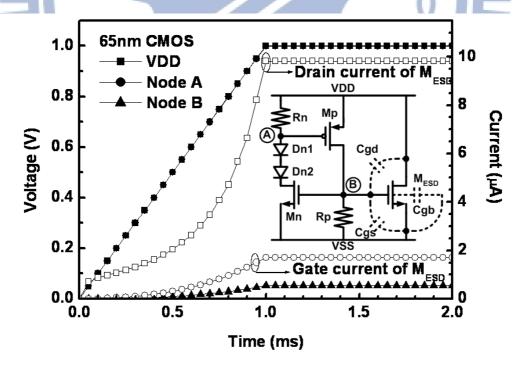

| 3.2.1 ESD-Transient Detection Circuit Scheme                                       | 54 |

| 3.2.2 Operation Principles                                                         | 55 |

| 3.2.3 Experimental Results                                                         | 58 |

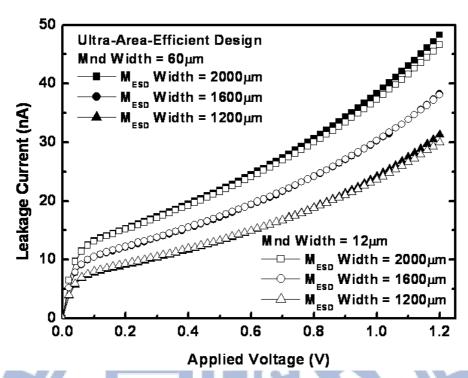

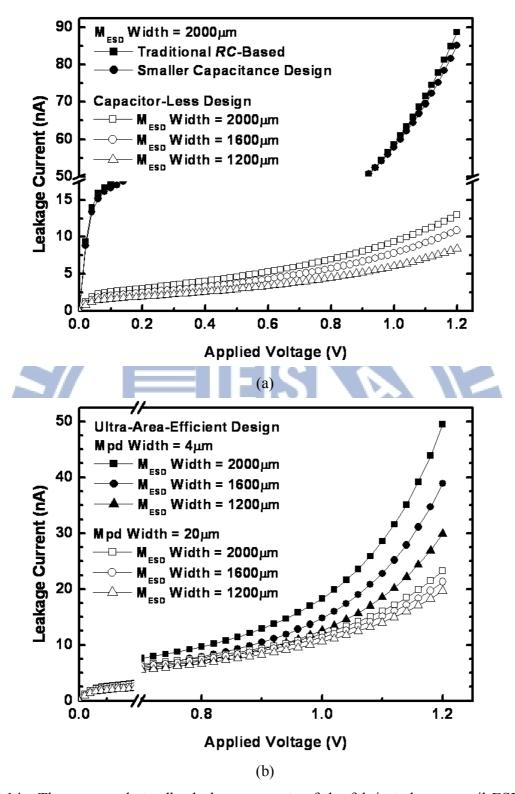

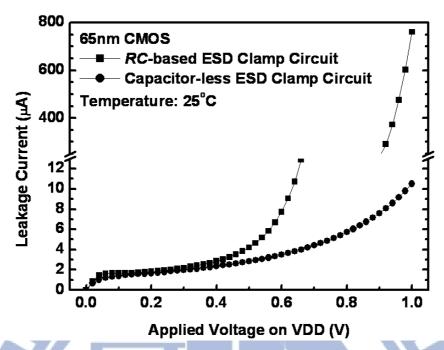

| 3.2.3.1 Standby Leakage Current                                                    | 58 |

| 3.2.3.2 TLP Measurement and ESD Robustness                                         | 58 |

| 3.2.3.3 Turn-On Verification                                                       | 59 |

| 3.2.3.4 Transient-Induced Latch-Up (TLU) Measurement                               | 60 |

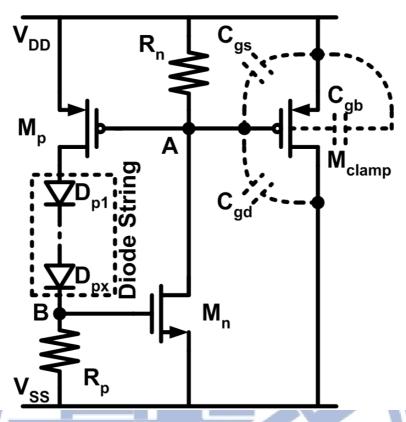

| 3.3 Power-Rail ESD Clamp Circuit with ESD Clamp pMOS Transistor                    | 61 |

| 3.3.1 ESD-Transient Detection Circuit Scheme                                       | 61 |

| 3.3.2 Operation Principles                                                         | 62 |

| 3.3.3 Experimental Results                                                         | 64 |

| 3.3.3.1 Standby Leakage Current                                                    | 64 |

| 3.3.3.2 TLP Measurement and ESD Robustness                                          | 64 |

|-------------------------------------------------------------------------------------|----|

| 3.3.3.3 Turn-On Verification                                                        | 64 |

| 3.3.3.4 TLU Measurement                                                             | 65 |

| 3.4 Summary                                                                         | 66 |

|                                                                                     |    |

| Chapter 4 Power-Rail ESD Clamp Circuit with Equivalent ESD-Transient                | 91 |

| Detection Mechanism                                                                 |    |

| Detection Mechanism  4.1 Background  4.2 Prior Arts of Power-Rail ESD Clamp Circuit | 91 |

| 4.2 Prior Arts of Power-Rail ESD Clamp Circuit                                      | 92 |

| 4.2.1 Traditional RC-Based Power-Rail ESD Clamp Circuit                             | 92 |

| 4.2.2 Power-Rail ESD Clamp Circuit with Smaller Capacitance                         | 92 |

| 4.2.3 Capacitor-Less Design of Power-Rail ESD Clamp Circuit                         | 92 |

| 4.3 ESD Clamp Circuit with Equivalent Capacitance-Coupling Detection                | 93 |

| Mechanism                                                                           |    |

| 4.3.1 Circuit Schematic                                                             | 93 |

| 4.3.2 Operation Mechanism under ESD Transition                                      | 94 |

| 4.3.3 Experimental Results                                                          | 94 |

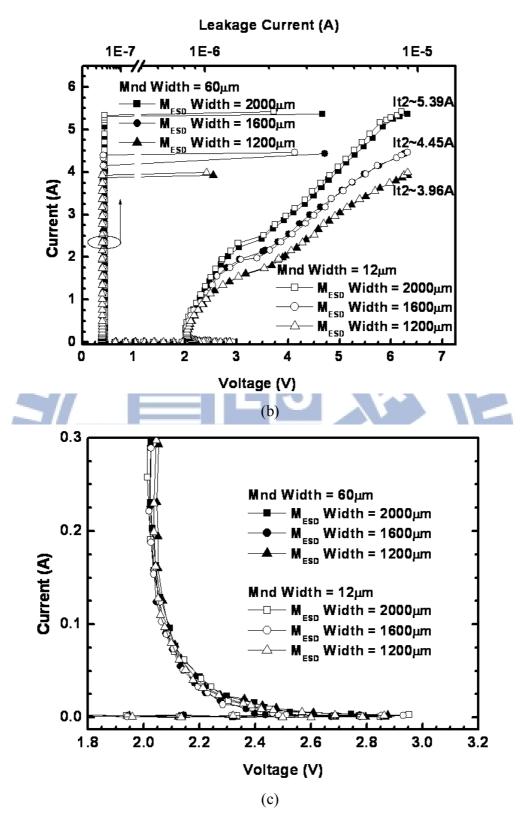

| 4.3.3.1 Standby Leakage Current                                                     | 94 |

| 4.3.3.2 TLP Measurement and ESD Robustness                                          | 95 |

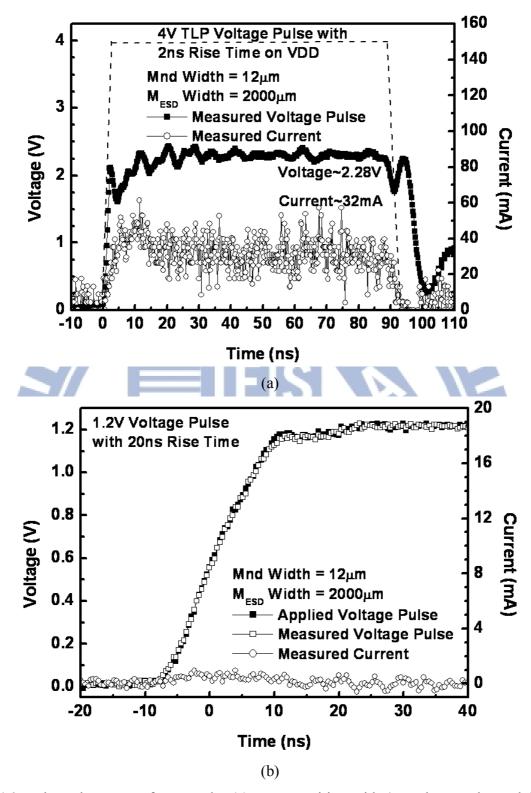

| 4.3.3.3 Turn-On Verification                                                        | 95 |

| 4.4 ESD Clamp Circuit with Equivalent RC-Based Detection Mechanism                  | 96 |

| 4.4.1 Circuit Schematic                                                             | 96 |

| 4.4.2 Operation Principles                                                          | 96 |

| 4.4.2.1 Normal Power-On Transition                                                  | 96 |

| 4.4.2.2 ESD Transition                                                              | 97 |

| 4.4.3 Experimental Results                                                          | 98 |

| 4.4.3.1 Standby Leakage Current                                                                                        | 98    |

|------------------------------------------------------------------------------------------------------------------------|-------|

| 4.4.3.2 TLP Measurement and ESD Robustness                                                                             | 99    |

| 4.4.3.3 Turn-On Verification                                                                                           | 100   |

| 4.5 Summary                                                                                                            | 101   |

|                                                                                                                        |       |

| Chapter 5 Power-Rail ESD Clamp Circuit with Considerations of Gate                                                     | 121   |

| Leakage Current and Gate Oxide Reliability                                                                             |       |

| 5.1 Background                                                                                                         | 121   |

| 5.2 Gate Leakage Current in the Conventional Power-Rail ESD Clamp                                                      | 123   |

| Circuits                                                                                                               |       |

| 5.2.1 Traditional RC-Based Power-Rail ESD Clamp Circuit                                                                | 123   |

| 5.2.2 Capacitor-Less Design of Power-Rail ESD Clamp Circuit                                                            | 123   |

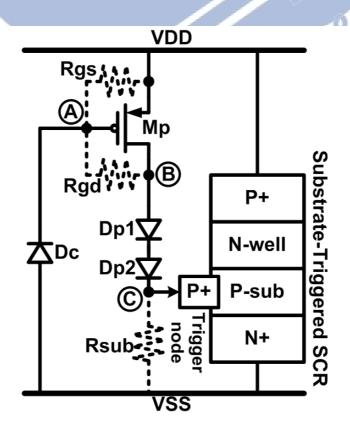

| 5.3 Power-Rail ESD Clamp Circuit for 1×VDD Applications                                                                | 124   |

| 5.3.1 Design Concept of ESD-Transient Detection Circuit                                                                | 124   |

| 5.3.2 Silicon-Controlled Rectifier (SCR) Embedded into ESD-Transient                                                   | 126   |

| Detection Circuit 1996                                                                                                 |       |

| 5.3.3 Operation Mechanism                                                                                              | 127   |

| 5.3.3.1 Normal Power-On Transition                                                                                     | 127   |

| 5.3.3.2 ESD Transition                                                                                                 | 127   |

| <ul><li>5.3.3.1 Normal Power-On Transition</li><li>5.3.3.2 ESD Transition</li><li>5.3.4 Experimental Results</li></ul> | 128   |

| 5.3.4.1 TLP Measurement and ESD Robustness                                                                             | 128   |

| 5.3.4.2 Standby Leakage Current                                                                                        | 129   |

| 5.3.4.3 Turn-On Verification                                                                                           | 130   |

|                                                                                                                        | 131   |

| 5.4 High-Voltage-Tolerant Power-Rail ESD Clamp Circuit                                                                 | 131   |

| 3 /L L LIGOTON L ONCONT OT HINLL LEGICOLONI LIGIDON L'IPOUT                                                            | 1 7 1 |

| 5.4.2 Operation Principles                                                                                            | 133 |

|-----------------------------------------------------------------------------------------------------------------------|-----|

| 5.4.2.1 Normal Power-On Transition                                                                                    | 133 |

| 5.4.2.2 ESD Transition                                                                                                | 134 |

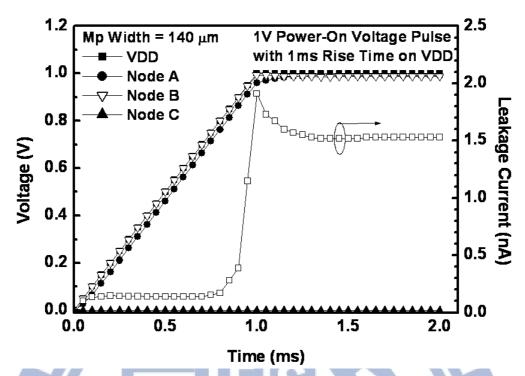

| 5.4.3 Experimental Results                                                                                            | 134 |

| 5.4.3.1 Standby Leakage Current                                                                                       | 134 |

| 5.4.3.2 TLP Measurement and ESD Robustness                                                                            | 135 |

| 5.4.3.3 Turn-On Verification                                                                                          | 135 |

| 5.4.3.3 Turn-On Verification  5.5 Summary                                                                             | 136 |

|                                                                                                                       |     |

| Chapter 6 Resistor-Less Design of Power-Rail ESD Clamp Circuit                                                        | 161 |

| 6.1 Background                                                                                                        | 161 |

| 6.2 Gate Leakage Current in the Conventional Power-Rail ESD Clamp                                                     | 162 |

| Circuits                                                                                                              |     |

| 6.2.1 Traditional RC-Based Power-Rail ESD Clamp Circuit                                                               | 162 |

| 6.2.2 Capacitor-Less Design of Power-Rail ESD Clamp Circuit                                                           | 162 |

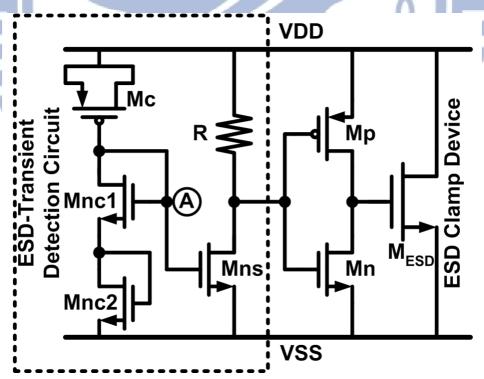

| 6.3 Resistor-Less Design of ESD-Transient Detection Circuit                                                           | 163 |

| 6.3.1 Circuit Schematic                                                                                               | 164 |

| <ul><li>6.3.2 Operation Mechanism</li><li>6.3.2.1 Normal Power-On Transition</li><li>6.3.2.2 ESD Transition</li></ul> | 164 |

| 6.3.2.1 Normal Power-On Transition                                                                                    | 164 |

| 6.3.2.2 ESD Transition                                                                                                | 165 |

| 6.3.3 Experimental Results                                                                                            | 166 |

| 6.3.3.1 TLP Measurement and ESD Robustness                                                                            | 166 |

| 6.3.3.2 Standby Leakage Current                                                                                       | 167 |

| 6.3.3.3 Turn-On Verification                                                                                          | 167 |

| 6.4 Summary                                                                                                           | 168 |

| Chapter 7 Conclusions and Future Works      | 179 |

|---------------------------------------------|-----|

| 7.1 Main Contributions of This Dissertation | 179 |

| 7.2 Future Works                            | 181 |

|                                             |     |

| References                                  | 185 |

| Vita                                        | 191 |

| Vita Publication List                       | 193 |

|                                             |     |

|                                             |     |

|                                             |     |

|                                             |     |

|                                             |     |

|                                             |     |

|                                             |     |

|                                             |     |

| <b>2\\\\</b> 1896 //>                       |     |

|                                             |     |

|                                             |     |

|                                             |     |

|                                             |     |

## **Figure Captions**

| Chapter | 1 |

|---------|---|

| Chapter | - |

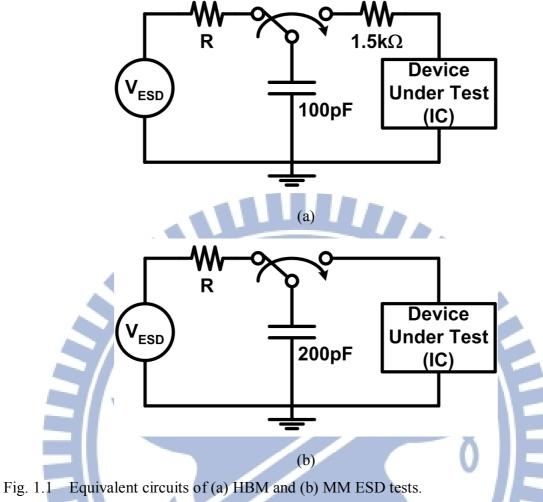

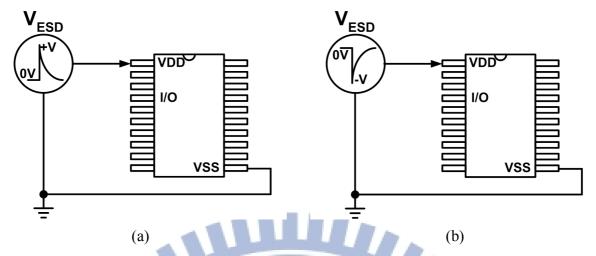

| Fig. 1.1 | Equivalent circuits of (a) HBM and (b) MM ESD tests.                            | 5  |

|----------|---------------------------------------------------------------------------------|----|

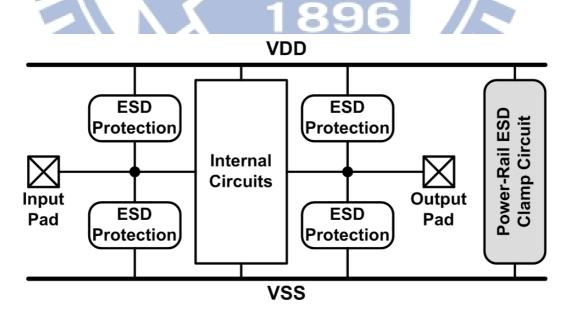

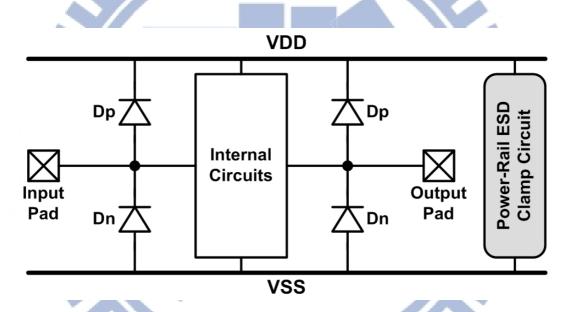

| Fig. 1.2 | Design concept of whole-chip ESD protection circuits in CMOS ICs.               | 5  |

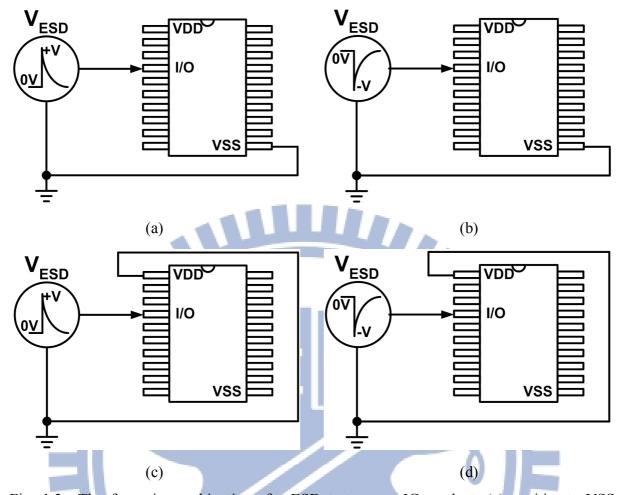

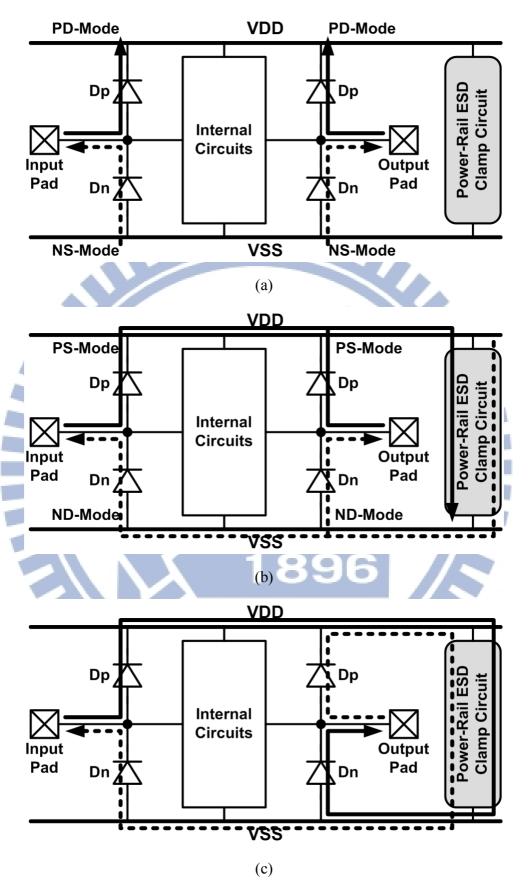

| Fig. 1.3 | The four pin combinations for ESD test on an IC product: (a)                    | 6  |

|          | positive-to-VSS (PS-mode), (b) negative-to-VSS (NS-mode), (c)                   |    |

|          | positive-to-VDD (PD-mode), and (d) negative-to-VDD (ND-mode).                   |    |

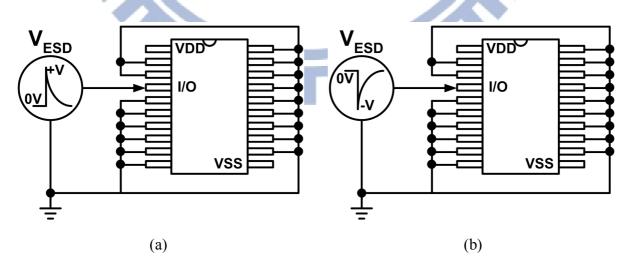

| Fig. 1.4 | Pin-to-pin ESD tests: (a) positive mode and (b) negative mode.                  | 6  |

| Fig. 1.5 | VDD-to-VSS ESD tests: (a) positive mode and (b) negative mode.                  | 7  |

| Fig. 1.6 | Typical on-chip double-diode ESD protection scheme.                             | 7  |

| Fig. 1.7 | ESD current discharging paths in the typical double-diode ESD protection        | 8  |

|          | scheme under (a) PD-mode, NS-mode, (b) PS-mode, ND-mode, and (c)                |    |

| Chantes  | pin-to-pin ESD stresses.                                                        |    |

| Chapter  | 1996                                                                            | 20 |

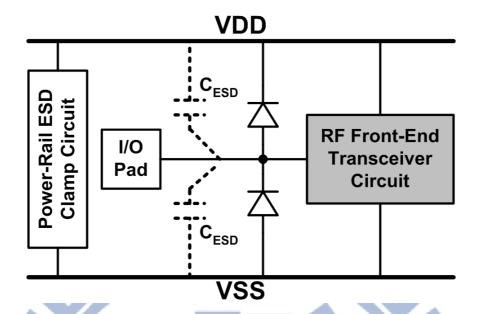

| Fig. 2.1 | Typical ESD protection scheme with double diodes for RF front-end or            | 29 |

|          | high-speed I/O applications.                                                    |    |

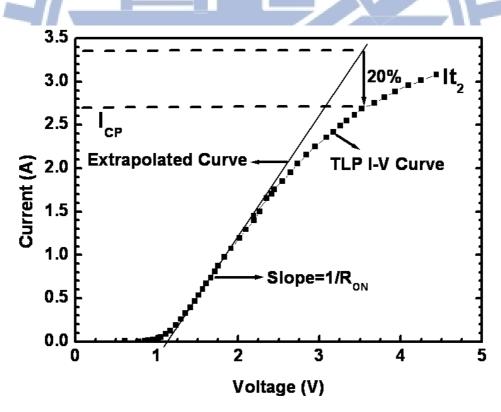

| Fig. 2.2 | The measured TLP <i>I-V</i> curve of the ESD protection diode. The current      | 29 |

|          | compression point $(I_{CP})$ is defined as the current level at which the       |    |

|          | measured <i>I-V</i> curve deviates from its linearly extrapolated value by 20%. |    |

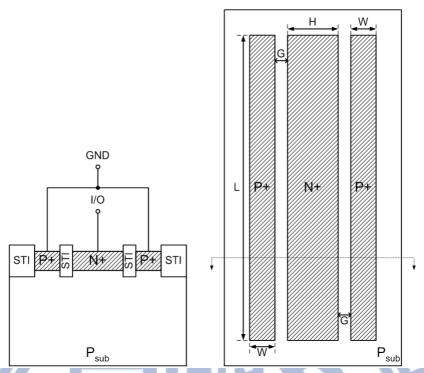

| Fig. 2.3 | Device cross-sectional view and layout top view of the ESD protection           | 30 |

|          | diode with typical stripe layout style.                                         |    |

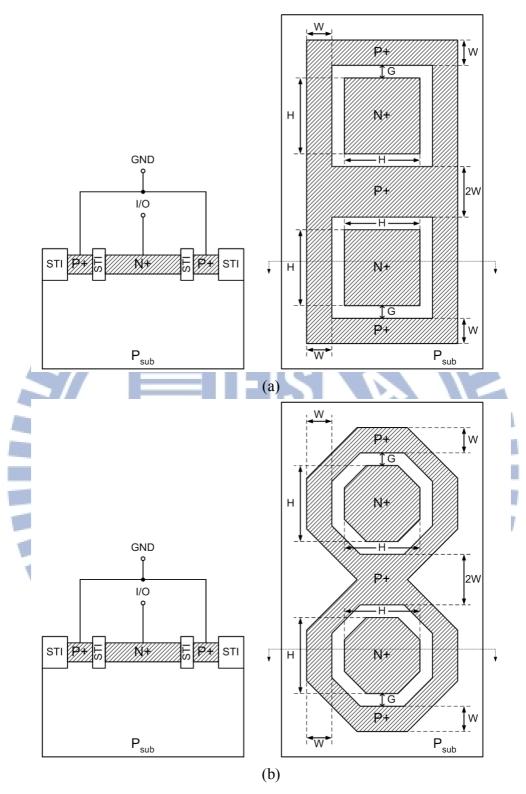

| Fig. 2.4 | Device cross-sectional view and layout top view of the ESD protection           | 31 |

|          | diodes with (a) waffle layout style and (b) octagon layout style.               |    |

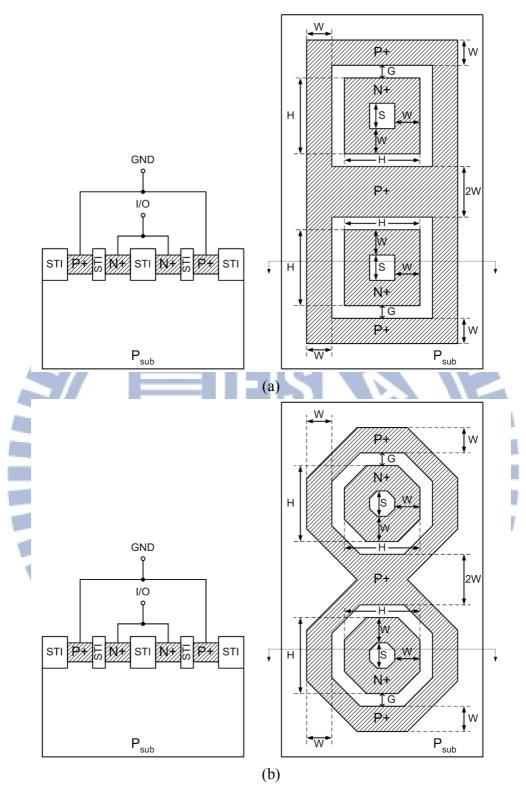

| Fig. 2.5 | Device cross-sectional view and layout top view of the ESD protection           | 32 |

|           | style. The center region is drawn with the STI region to effectively reduce              |    |

|-----------|------------------------------------------------------------------------------------------|----|

|           | the parasitic capacitance.                                                               |    |

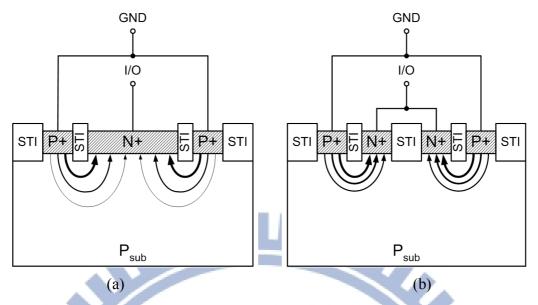

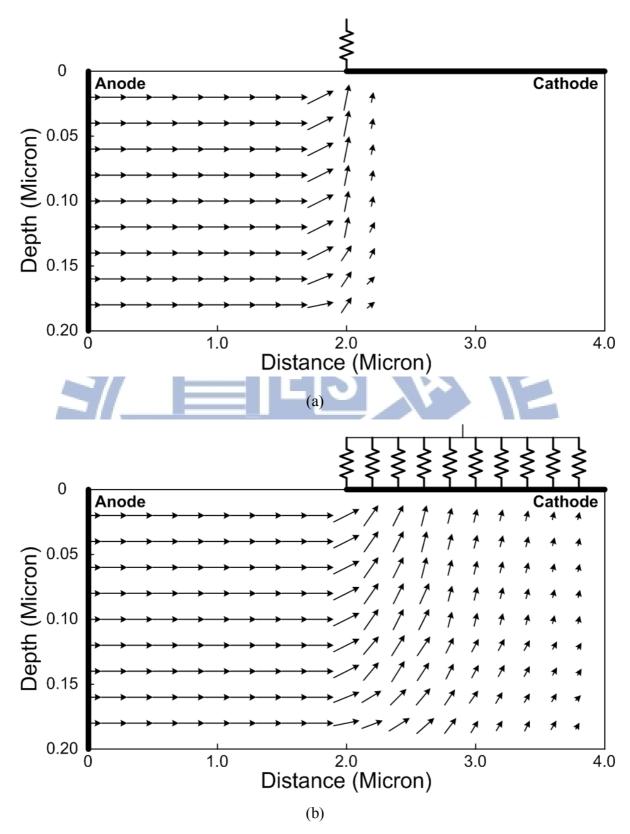

| Fig. 2.6  | Device cross-sectional view to explain ESD current flows in the diodes                   | 33 |

|           | with (a) waffle layout style and (b) waffle-hollow layout style.                         |    |

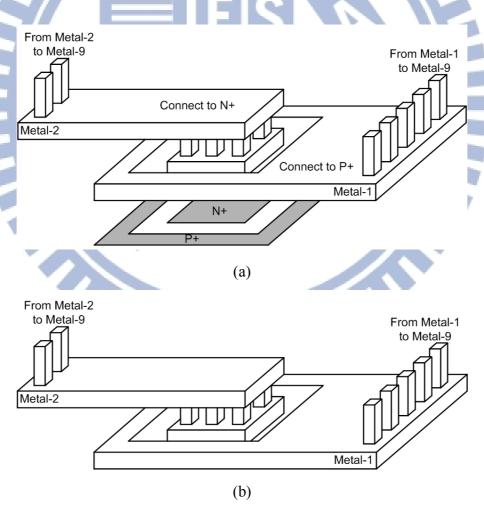

| Fig. 2.7  | The 3D views of metal layer arrangement for (a) interconnect routing of                  | 33 |

|           | N+/P <sub>sub</sub> diodes, and (b) the corresponding open pad structure.                |    |

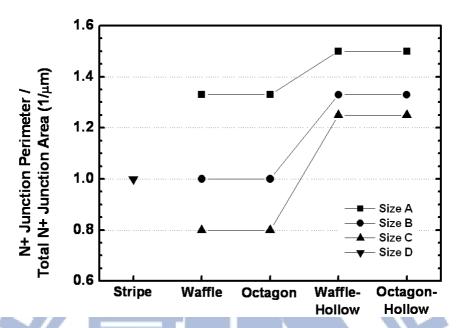

| Fig. 2.8  | The performance evaluations with the factors of N+ junction perimeter /                  | 34 |

|           | total N+ junction area under different diode layout styles.                              |    |

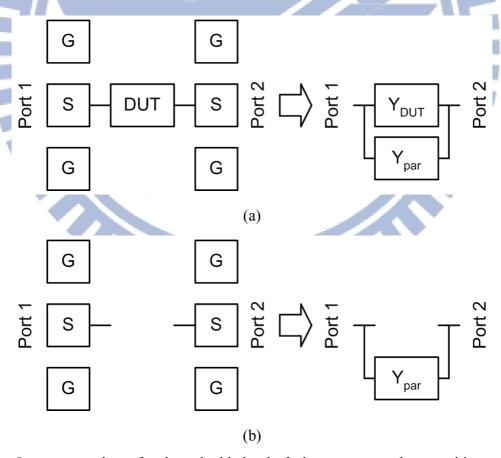

| Fig. 2.9  | Layout top views for de-embedded calculation to extract the parasitic                    | 34 |

| i         | capacitance of the fabricated ESD diodes with (a) including-DUT pattern                  |    |

|           | and (b) excluding-DUT pattern.                                                           |    |

| Fig. 2.10 | Dependence of C <sub>ESD</sub> extracted from S-parameter at 2.5GHz under zero DC        | 35 |

|           | bias on the N+ occupied area of diode devices with different layout styles.              |    |

| Fig. 2.11 | Dependence of TLP-measured R <sub>ON</sub> on the N+ junction perimeter of diode         | 35 |

|           | devices with different layout styles.                                                    |    |

| Fig. 2.12 | Dependence of TLP-measured $I_{CP}$ on the N+ junction perimeter of diode                | 36 |

|           | devices with different layout styles.                                                    |    |

| Fig. 2.13 | The simulated vectors of ESD discharging current along the cross section                 | 37 |

|           | of waffle diode with a (a) small, and (b) large, device size.                            |    |

| Fig. 2.14 | The $(I_{CP}/C_{ESD})$ FOM of ESD protection diodes with different layout styles.        | 38 |

| Fig. 2.15 | The $(V_{\text{HBM}}/C_{\text{ESD}})$ FOM of ESD protection diodes with different layout | 38 |

|           | styles.                                                                                  |    |

| Fig. 2.16 | The $(R_{ON} \times C_{ESD})$ FOM of ESD protection diodes with different layout         | 39 |

|           | styles.                                                                                  |    |

diodes with (a) waffle-hollow layout style and (b) octagon-hollow layout

| Fig. 2.17 | STI-bound N+/P <sub>sub</sub> ESD protection diode with typical stripe layout style.          | 39 |

|-----------|-----------------------------------------------------------------------------------------------|----|

|           | The major current conduction path of the stripe diode occurs along the                        |    |

|           | length (L) of the diode.                                                                      |    |

| Fig. 2.18 | Layout top view of the STI-bound (a) N+/P <sub>sub</sub> ESD protection diode and (b)         | 40 |

|           | P+/N <sub>well</sub> ESD protection diode with waffle layout style.                           |    |

| Fig. 2.19 | Layout top view of the STI-bound (a) N+/P <sub>sub</sub> ESD protection diode and (b)         | 41 |

|           | P+/N <sub>well</sub> ESD protection diode with multi-waffle layout style.                     |    |

| Fig. 2.20 | Layout top view of the STI-bound (a) N+/P <sub>sub</sub> ESD protection diode and (b)         | 42 |

|           | P+/N <sub>well</sub> ESD protection diode with multi-waffle-hollow layout style. The          |    |

|           | N+ (P+) center diffusion region of N+/P <sub>sub</sub> (P+/N <sub>well</sub> ) diode with     |    |

|           | multi-waffle-hollow layout style is removed to reduce the parasitic                           |    |

|           | capacitance.                                                                                  |    |

| Fig. 2.21 | The performance evaluations with the ratio of (junction perimeter) /                          | 43 |

|           | (junction area) under different layout styles.                                                |    |

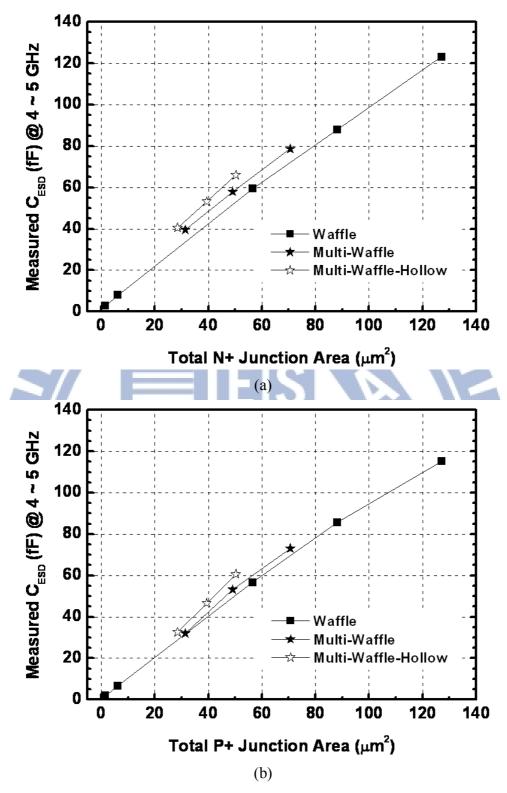

| Fig. 2.22 | Dependence of measured C <sub>ESD</sub> extracted from S-parameter from 4 to 5GHz             | 44 |

|           | under zero DC bias on the (a) total N+ junction area of N+/P <sub>sub</sub> diodes and        |    |

|           | (b) total P+ junction area of P+/N <sub>well</sub> diodes with different layout styles.       |    |

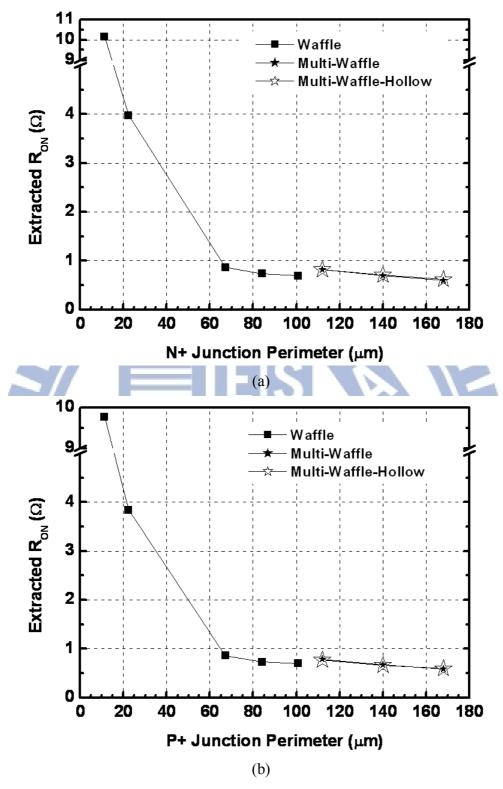

| Fig. 2.23 | Dependence of extracted on-resistance R <sub>ON</sub> on the (a) N+ junction                  | 45 |

|           | perimeter of N+/P <sub>sub</sub> diodes and (b) P+ junction perimeter of P+/N <sub>well</sub> |    |

|           | diodes with different layout styles.                                                          |    |

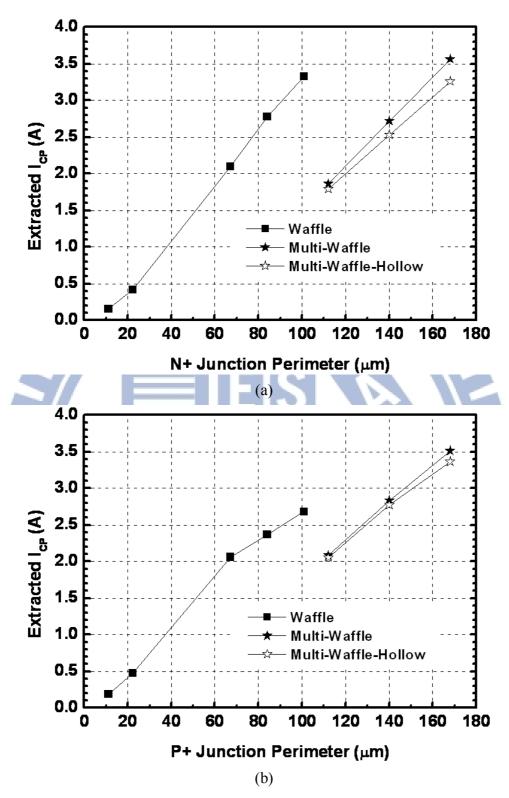

| Fig. 2.24 | Dependence of extracted current compression point I <sub>CP</sub> on the (a) N+               | 46 |

|           | junction perimeter of N+/P <sub>sub</sub> diodes and (b) P+ junction perimeter of             |    |

|           | P+/N <sub>well</sub> diodes with different layout styles.                                     |    |

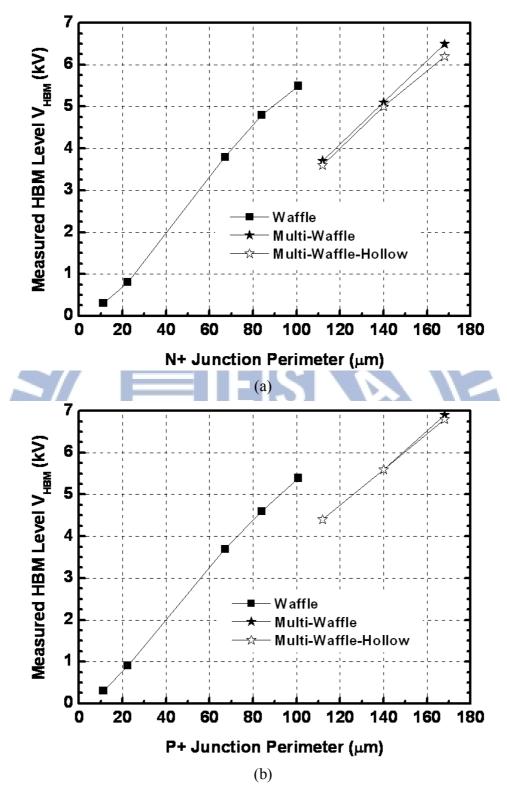

| Fig. 2.25 | Dependence of measured HBM level V <sub>HBM</sub> on the (a) N+ junction                      | 47 |

|           | perimeter of N+/P <sub>sub</sub> diodes and (b) P+ junction perimeter of P+/N <sub>well</sub> |    |

|           | diodes with different layout styles.                                                                     |    |

|-----------|----------------------------------------------------------------------------------------------------------|----|

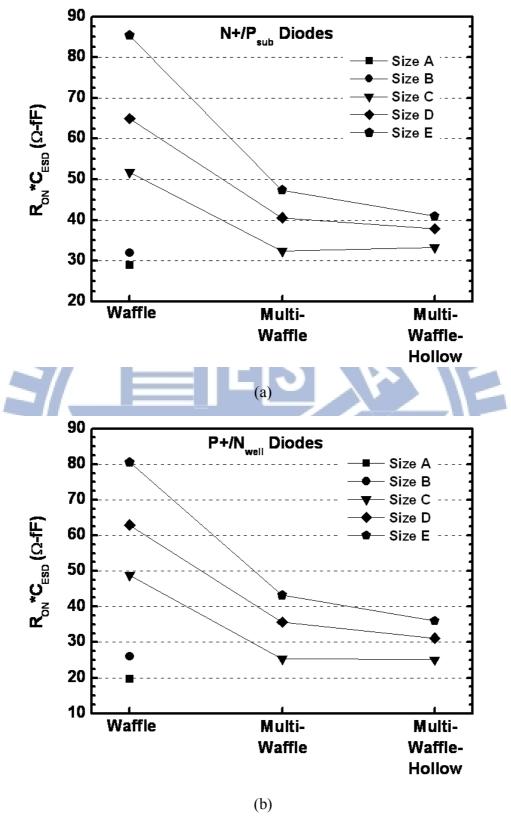

| Fig. 2.26 | The exact values of $R_{ON} {^*C}_{ESD}$ of the (a) N+/P $_{sub}$ diodes and (b) P+/N $_{well}$          | 48 |

|           | diodes with different layout styles.                                                                     |    |

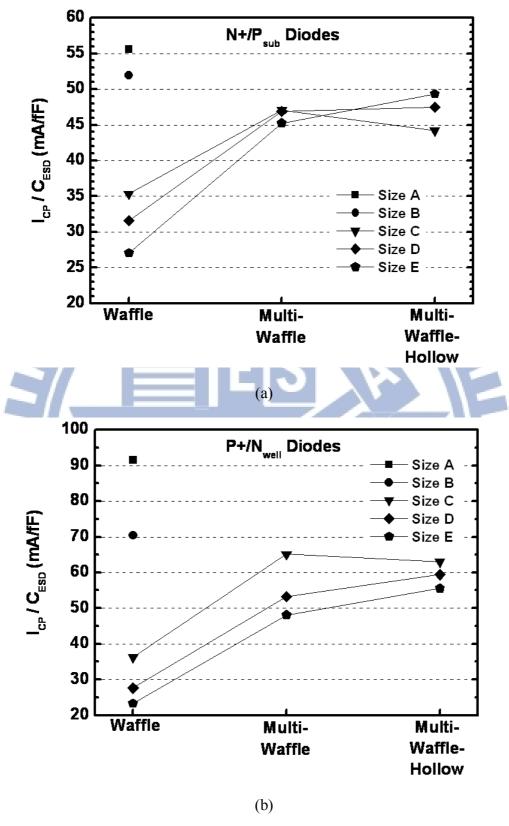

| Fig. 2.27 | The exact values of $I_{CP}/C_{ESD}$ of the (a) $N+\!/P_{sub}$ diodes and (b) $P+\!/N_{well}$            | 49 |

|           | diodes with different layout styles.                                                                     |    |

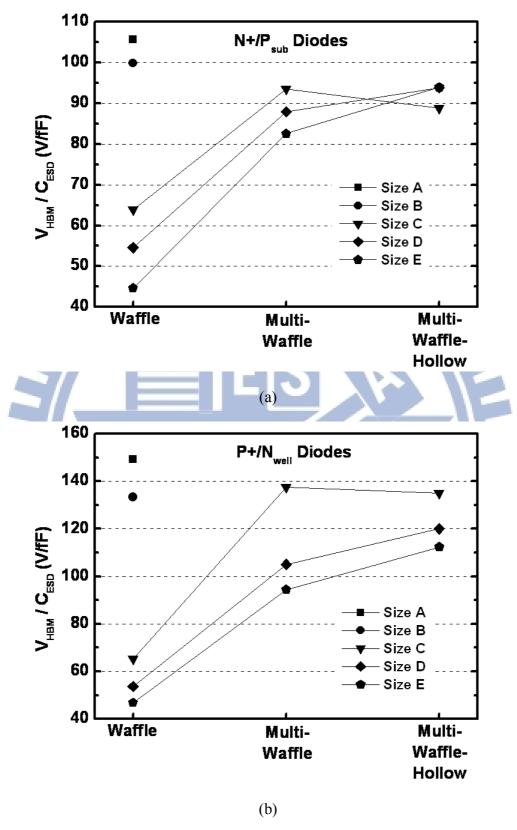

| Fig. 2.28 | The FOM $V_{HBM}/C_{ESD}$ of the (a) N+/P <sub>sub</sub> diodes and (b) P+/N <sub>well</sub> diodes with | 50 |

|           | different layout styles.                                                                                 |    |

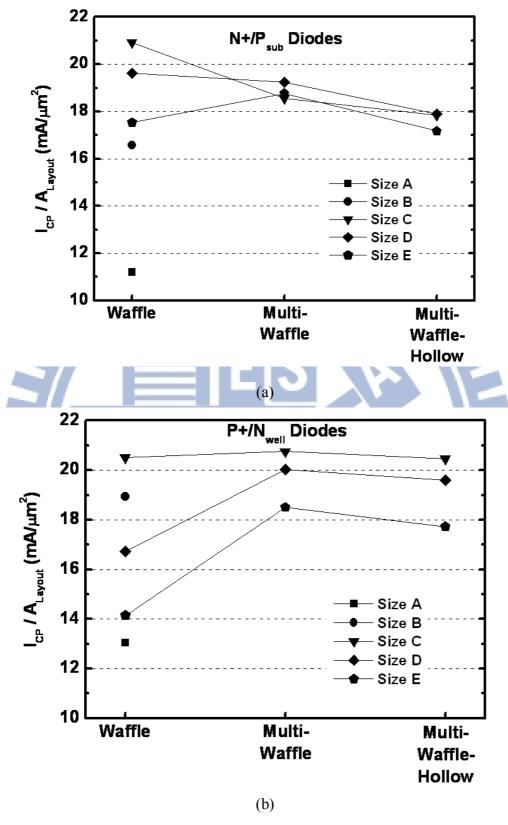

| Fig. 2.29 | The FOM $I_{CP}/A_{Layout}$ of the (a) N+/P $_{sub}$ diodes and (b) P+/N $_{well}$ diodes with           | 51 |

|           | different layout styles.                                                                                 |    |

|           |                                                                                                          |    |

| Chapter   | 3-// E   E   3   3   1   5                                                                               |    |

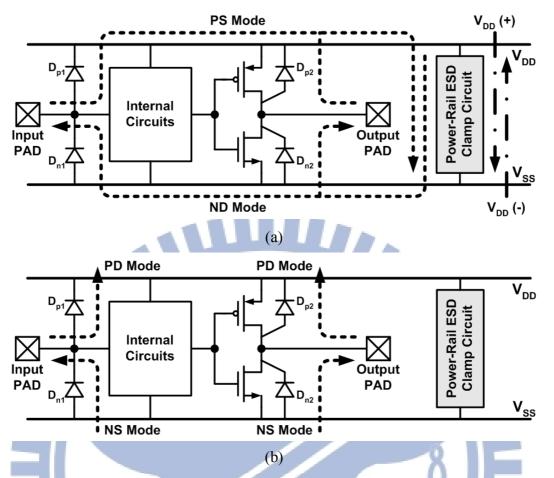

| Fig. 3.1  | Typical on-chip ESD protection design with active power-rail ESD clamp                                   | 69 |

|           | circuit under (a) PS-mode / ND-mode, and (b) PD-mode / NS-mode, ESD stress conditions.                   |    |

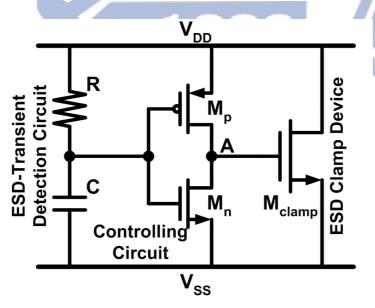

| Fig. 3.2  | Typical implementation of the RC-based power-rail ESD clamp circuit with                                 | 69 |

| ,         | ESD-transient detection circuit, controlling circuit, and ESD clamp device.                              |    |

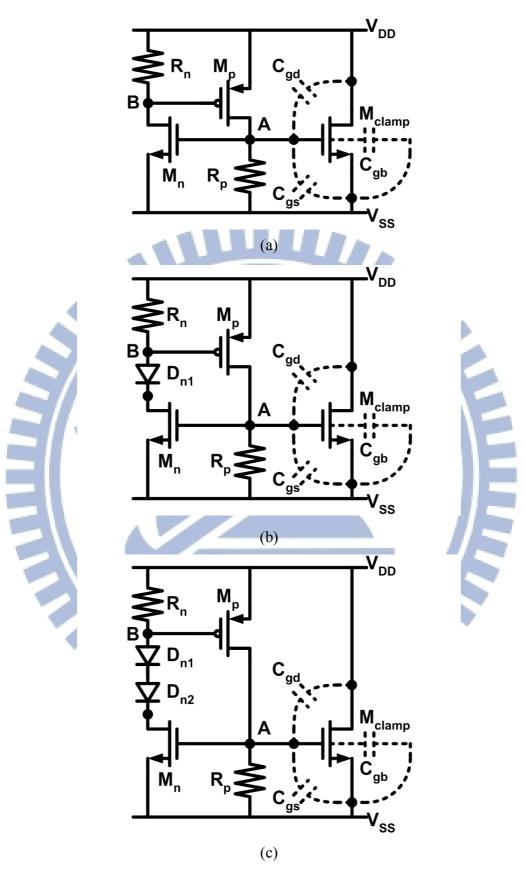

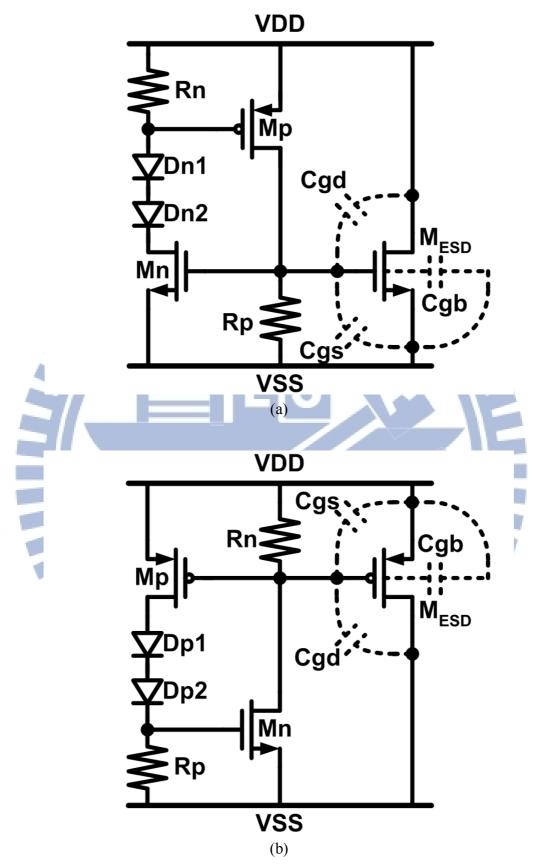

| Fig. 3.3  | New proposed power-rail ESD clamp circuits with ESD clamp nMOS                                           | 70 |

|           | transistor. There are (a) zero diode, (b) one diode, and (c) two diodes used                             |    |

|           | in the ESD-transient detection circuit, respectively.                                                    |    |

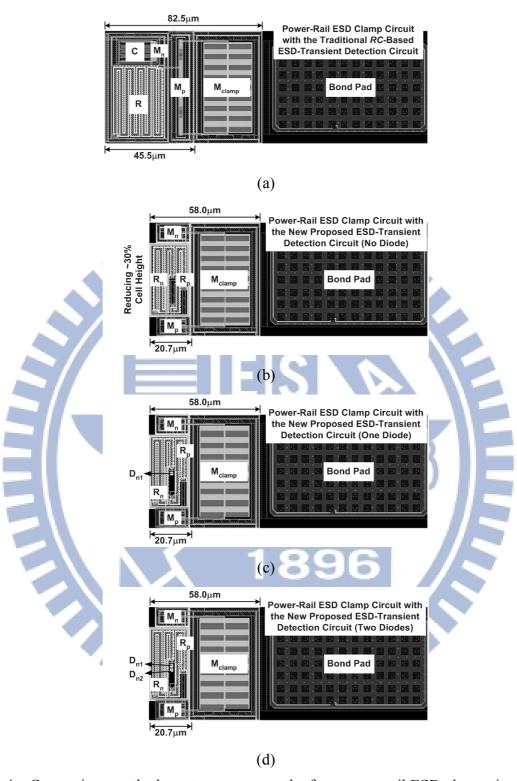

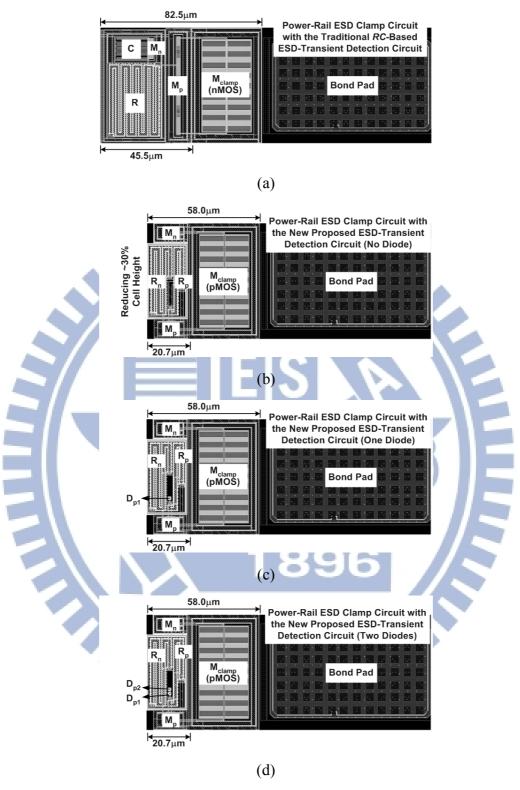

| Fig. 3.4  | Comparison on the layout areas among the four power-rail ESD clamp                                       | 71 |

|           | circuits. The ESD clamp nMOS transistor $M_{\text{clamp}}$ is drawn in a BigFET                          |    |

|           | layout style with the same W/L=2000 $\mu$ m/0.1 $\mu$ m, which is triggered by (a)                       |    |

|           | the traditional RC-based ESD-transient detection circuit, (b) the proposed                               |    |

|           | ESD-transient detection circuit with no diode, (c) the proposed                                          |    |

ESD-transient detection circuit with one diode, and (d) the proposed

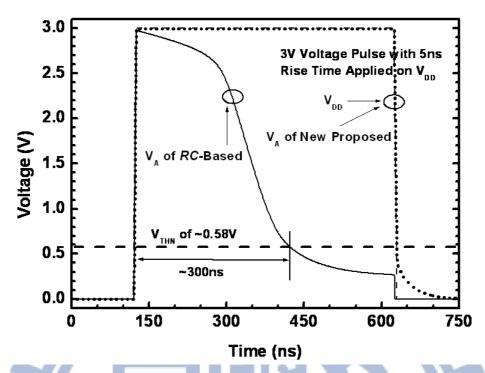

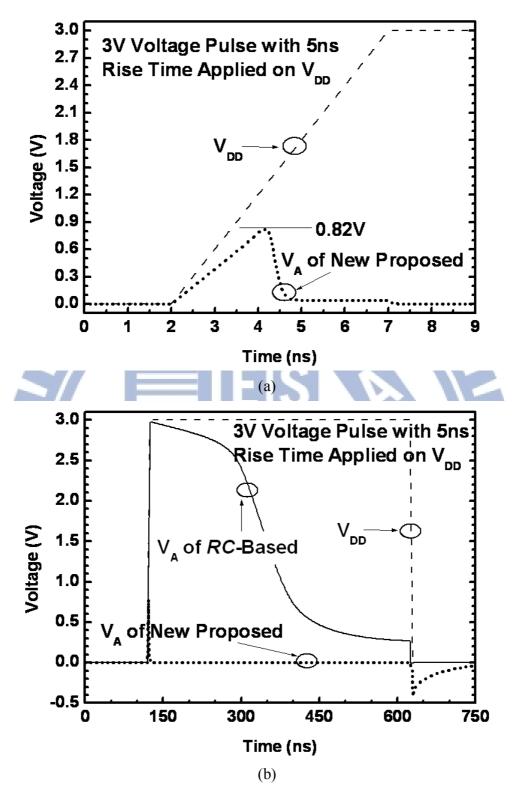

| Fig. 3.5  | ESD-like simulation results of the voltage at the gate terminal of the ESD            | 72 |

|-----------|---------------------------------------------------------------------------------------|----|

|           | clamp nMOS transistor controlled by the RC-based and the new proposed                 |    |

|           | ESD-transient detection circuit.                                                      |    |

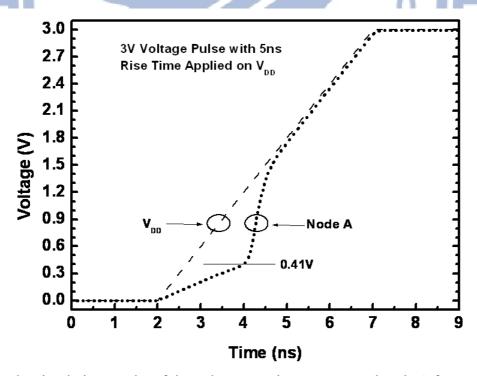

| Fig. 3.6  | The simulation results of the voltage transient on $V_{\text{DD}}$ and node A for new | 72 |

|           | proposed power-rail ESD clamp circuit with ESD clamp nMOS transistor.                 |    |

|           | The 3V ESD-like voltage pulse with $5$ ns rise time is applied on $V_{DD}$ .          |    |

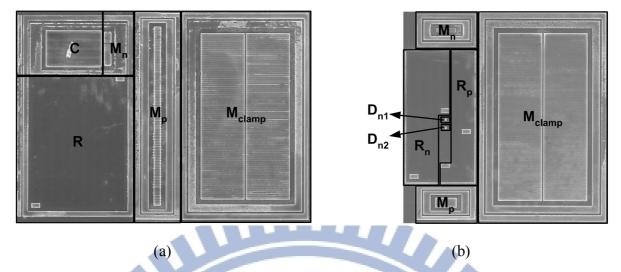

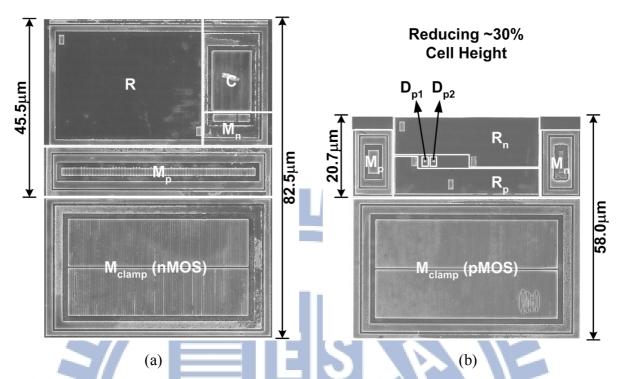

| Fig. 3.7  | Chip microphotographs of the fabricated power-rail ESD clamp circuit,                 | 73 |

|           | realized with (a) the traditional RC-based ESD-transient detection circuit            |    |

|           | and (b) the proposed ESD-transient detection circuit with two diodes.                 |    |

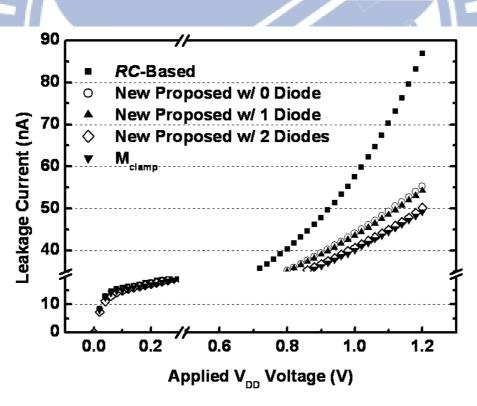

| Fig. 3.8  | The measured standby leakage current of the RC-based power-rail ESD                   | 73 |

|           | clamp circuit, the new proposed power-rail ESD clamp circuits, and the                |    |

|           | single ESD clamp nMOS transistor.                                                     |    |

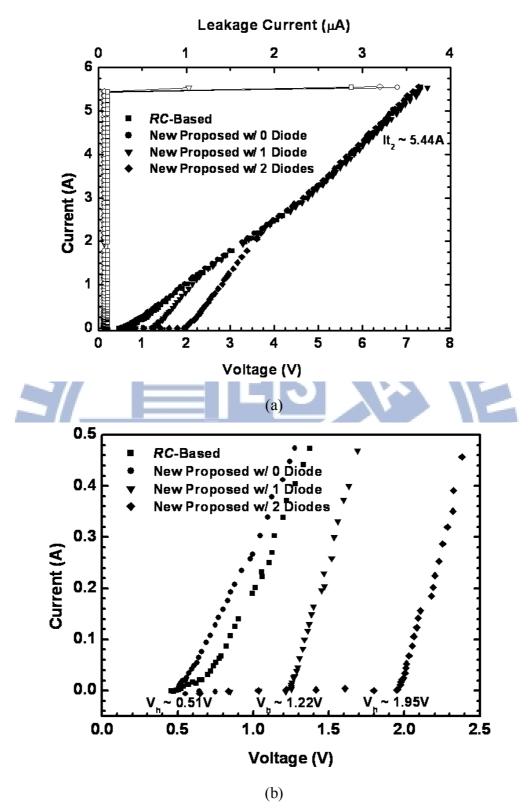

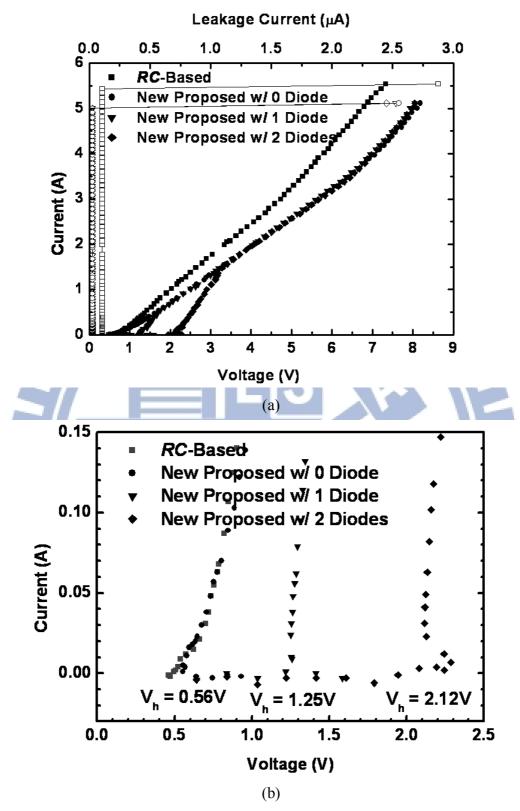

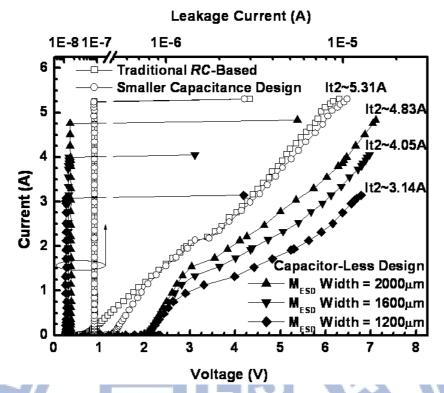

| Fig. 3.9  | TLP measured I-V curves of (a) the power-rail ESD clamp circuits with the             | 74 |

|           | RC-based, the new proposed ESD-transient detection circuit, and (b) the               |    |

|           | zoom-in illustration for the holding voltages $(V_h)$ .                               |    |

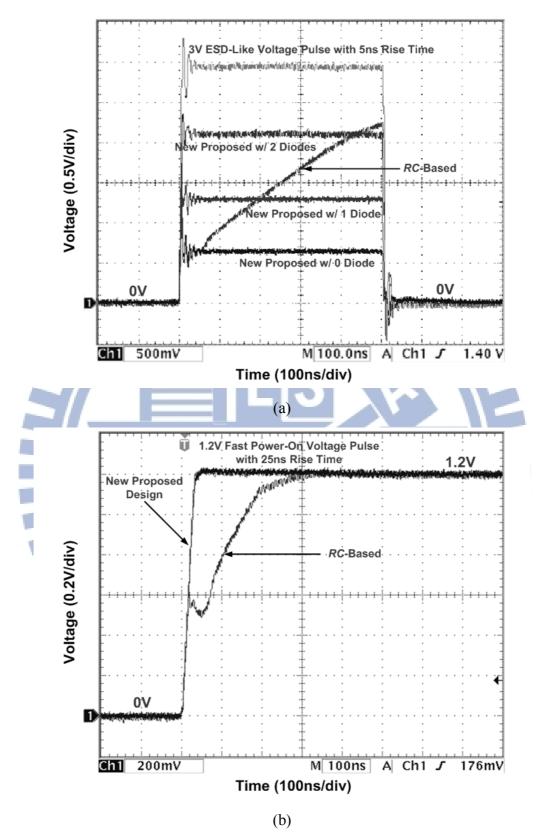

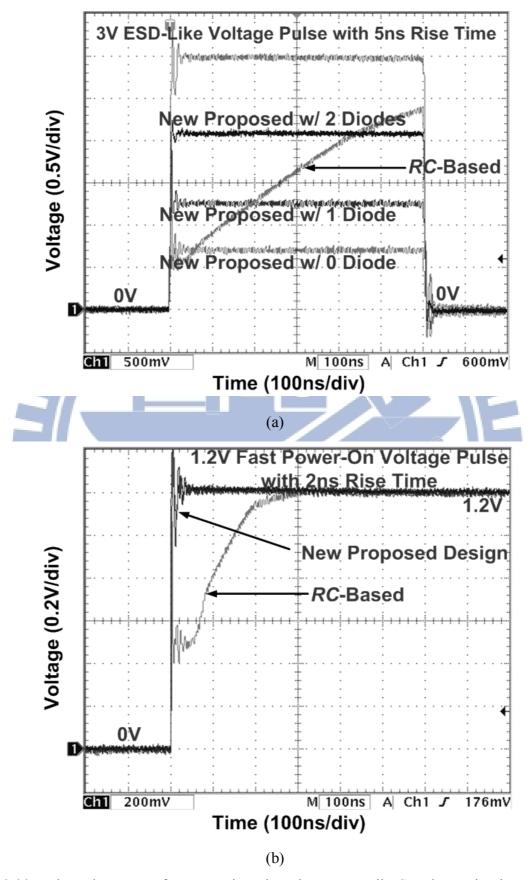

| Fig. 3.10 | The voltage waveforms under (a) ESD-transient-like condition with 3V                  | 75 |

|           | voltage pulse and 5ns rise time, (b) fast power-on condition with 1.2V                |    |

|           | voltage pulse and 25ns rise time.                                                     |    |

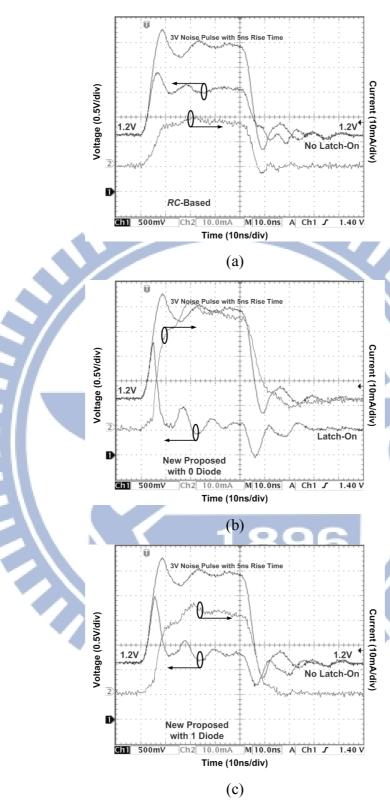

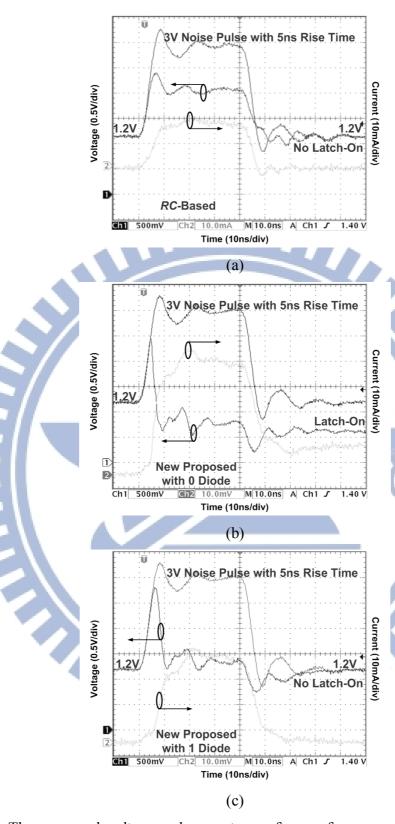

| Fig. 3.11 | The measured voltage and current waveforms of power-rail ESD clamp                    | 76 |

|           | circuit, realized with (a) the traditional RC-based ESD-transient detection           |    |

|           | circuit, (b) the proposed ESD-transient detection circuit with no diode, and          |    |

|           | (c) the proposed ESD-transient detection circuit with one diode, under                |    |

|           | transient noise condition.                                                            |    |

|           |                                                                                       |    |

ESD-transient detection circuit with two diodes.

77

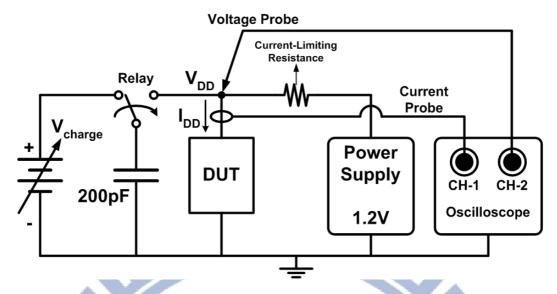

Fig. 3.12 The setup for transient-induced latch-up (TLU) measurement [44], [45].

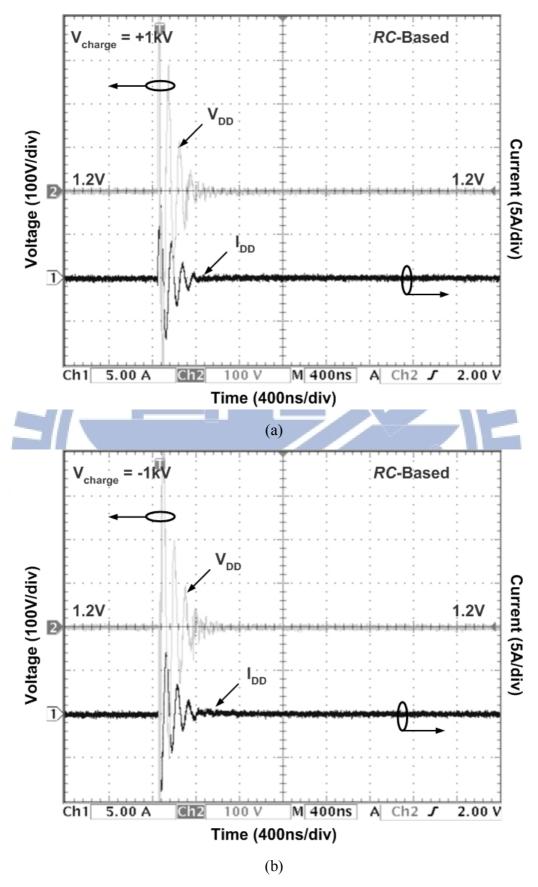

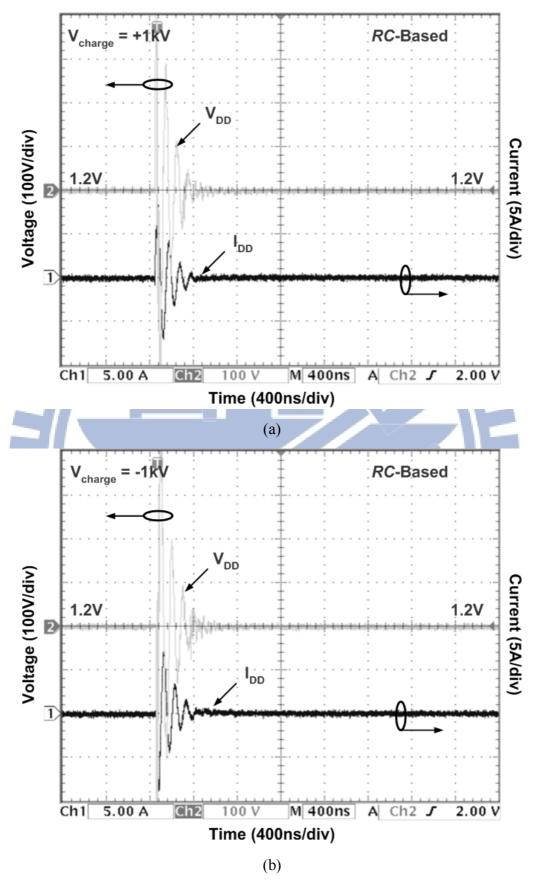

- Fig. 3.13 Measured  $V_{DD}$  and  $I_{DD}$  waveforms on the traditional RC-based power-rail ESD clamp circuit under TLU measurement with  $V_{charge}$  of (a) +1kV and (b) -1kV.

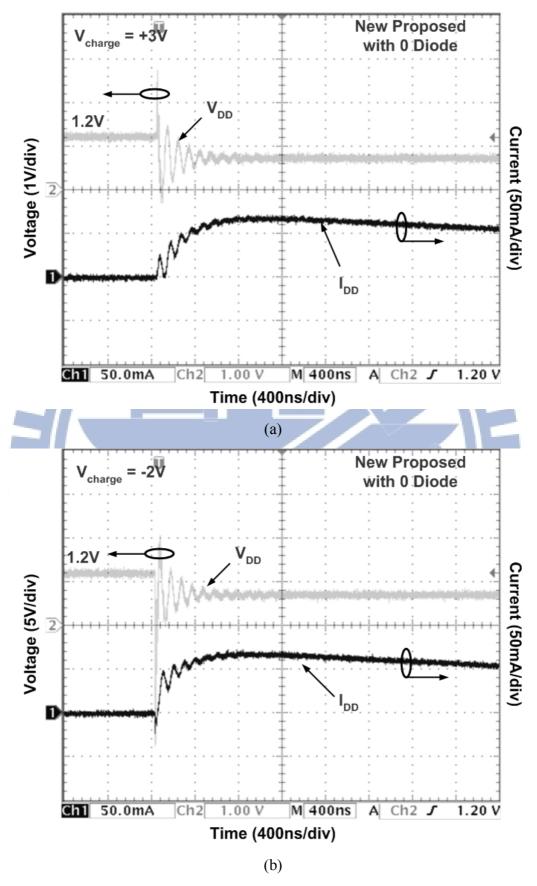

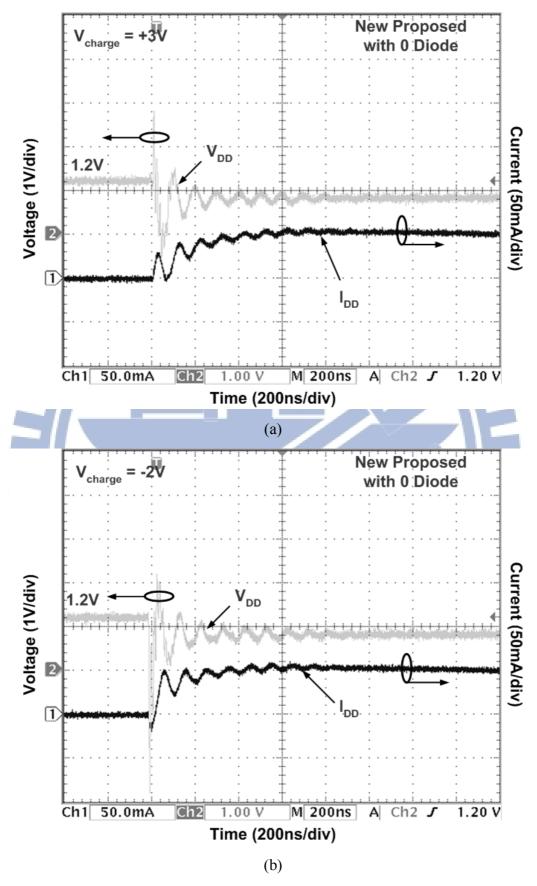

- Fig. 3.14 Measured  $V_{DD}$  and  $I_{DD}$  waveforms on the new proposed power-rail ESD 79 clamp circuit with no diode under TLU measurement with  $V_{charge}$  of (a) +3V and (b) -2V.

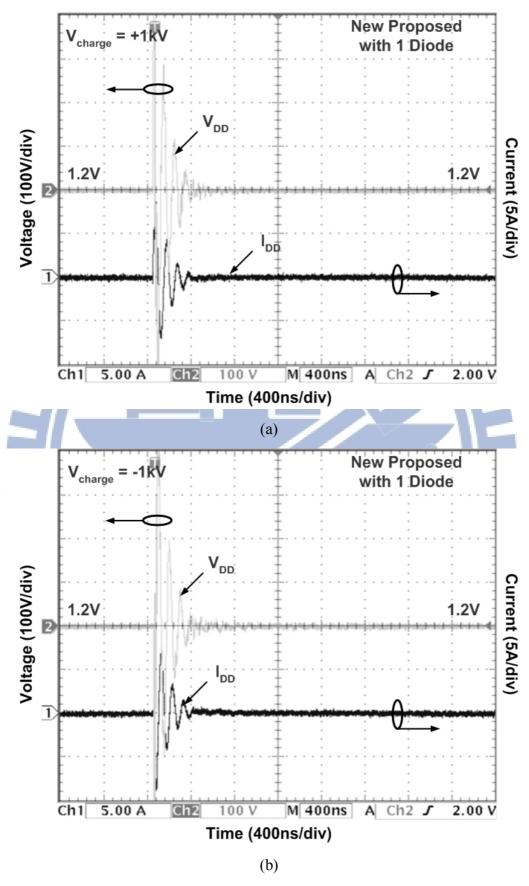

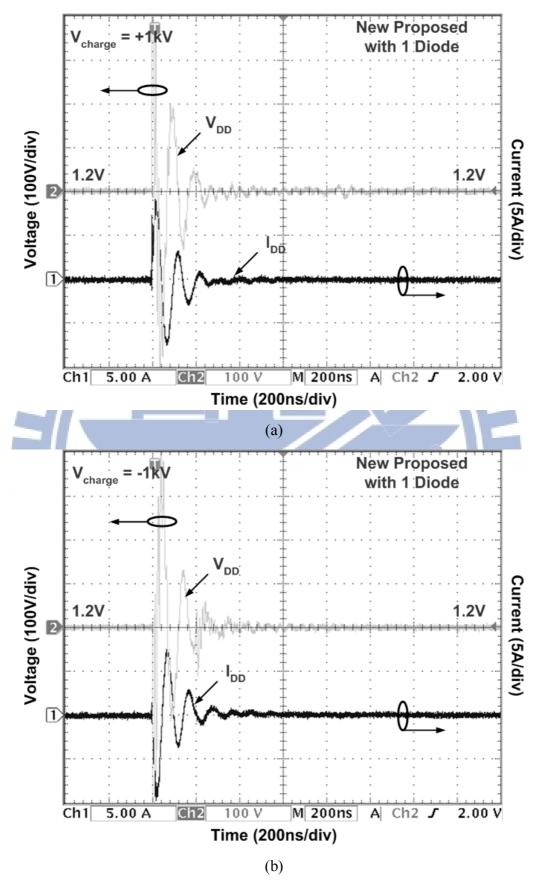

- Fig. 3.15 Measured  $V_{DD}$  and  $I_{DD}$  waveforms on the new proposed power-rail ESD clamp circuit with one diode under TLU measurement with  $V_{charge}$  of (a) +1kV and (b) -1kV.

- Fig. 3.16 New proposed power-rail ESD clamp circuit with ESD clamp pMOS 81 transistor and diode string in the ESD-transient detection circuit.

82

- Fig. 3.17 Comparison on the layout areas among the four power-rail ESD clamp circuits. The M<sub>clamp</sub> is drawn in a BigFET layout style with the same W/L=2000μm/0.1μm, which is triggered by (a) the traditional *RC*-based ESD-transient detection circuit, (b) the proposed ESD-transient detection circuit with one diode, (c) the proposed ESD-transient detection circuit with two diodes.

- Fig. 3.18 The simulation results of the voltage transient on  $V_{DD}$  and node A under a 3V voltage pulse with a rise time of 5ns. (a) The voltage waveforms in the period of rising transition, and (b) the voltage waveforms during the whole voltage pulse of 500ns.

- Fig. 3.19 Chip microphotographs of (a) the traditional *RC*-based power-rail ESD clamp circuit and (b) the proposed power-rail ESD clamp circuit with two diodes in its ESD-transient detection circuit.

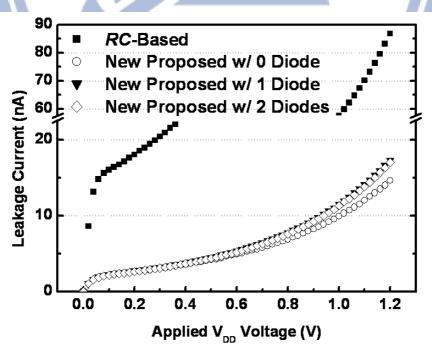

| Fig. 3.20 | The measured standby leakage current of the traditional RC-based and the                   | 84  |

|-----------|--------------------------------------------------------------------------------------------|-----|

|           | proposed power-rail ESD clamp circuits at room temperature.                                |     |

| Fig. 3.21 | TLP measured <i>I-V</i> curves of (a) the power-rail ESD clamp circuits and (b)            | 85  |

|           | the zoomed-in illustration for the holding voltages.                                       |     |

| Fig. 3.22 | The voltage waveforms monitored on the power-rail ESD clamp circuits                       | 86  |

|           | under (a) ESD-transient-like condition and (b) fast power-on condition.                    |     |

| Fig. 3.23 | The measured voltage and current waveforms of power-rail ESD clamp                         | 87  |

|           | circuit, realized with (a) the traditional RC-based ESD-transient detection                |     |

|           | circuit, (b) the proposed ESD-transient detection circuit with no diode, and               |     |

|           | (c) the proposed ESD-transient detection circuit with one diode, under                     |     |

| 4         | transient noise condition with $3V$ overshooting on $1.2V$ $V_{DD}$ .                      |     |

| Fig. 3.24 | Measured $V_{DD}$ and $I_{DD}$ waveforms on the traditional $RC$ -based power-rail         | 88  |

|           | ESD clamp circuit under TLU measurement with $V_{charge}$ of (a) +1kV and (b)              |     |

|           | -1kV.                                                                                      |     |

| Fig. 3.25 | Measured $V_{DD}$ and $I_{DD}$ waveforms on the new proposed power-rail ESD                | 89  |

|           | clamp circuit with no diode under TLU measurement with $V_{\text{charge}}$ of (a) $\pm 3V$ |     |

|           | and (b) -2V.                                                                               |     |

| Fig. 3.26 | Measured $V_{\text{DD}}$ and $I_{\text{DD}}$ waveforms on the new proposed power-rail ESD  | 90  |

|           | clamp circuit with one diode under TLU measurement with $V_{\text{charge}}$ of (a)         |     |

|           | +1kV and (b) -1kV.                                                                         |     |

|           |                                                                                            |     |

| Chapter   | 4                                                                                          |     |

| Fig. 4.1  | Traditional RC-based power-rail ESD clamp circuit with ESD-transient                       | 104 |

|           | detection circuit and ESD clamp nMOS transistor [8].                                       |     |

| Fig. 4.2  | Power-rail ESD clamp circuit with smaller capacitance in ESD-transient                     | 104 |

|           | detection circuit [36].                                                       |     |

|-----------|-------------------------------------------------------------------------------|-----|

| Fig. 4.3  | Capacitor-less power-rail ESD clamp circuit with (a) ESD clamp nMOS           | 105 |

|           | transistor [47] and (b) ESD clamp pMOS transistor [48].                       |     |

| Fig. 4.4  | The (a) circuit schematic and the (b) cross-sectional view of the new         | 106 |

|           | proposed power-rail ESD clamp circuit with ESD clamp nMOS transistor.         |     |

| Fig. 4.5  | Simulated voltage waveforms of the new proposed power-rail ESD clamp          | 107 |

|           | circuit with ESD clamp nMOS transistor under the ESD-like transition.         |     |

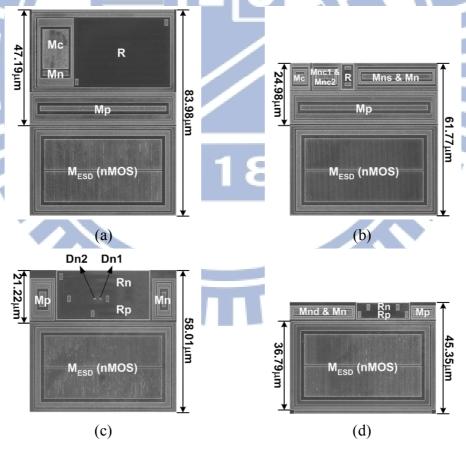

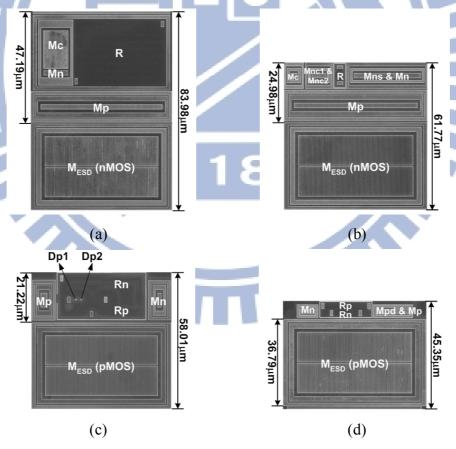

| Fig. 4.6  | Chip microphotograph of the (a) traditional RC-based, (b) smaller             | 107 |

|           | capacitance, (c) capacitor-less, and (d) new proposed power-rail ESD clamp    |     |

|           | circuits with ESD clamp nMOS transistor.                                      |     |

| Fig. 4.7  | The measured standby leakage currents of the new proposed power-rail          | 108 |

|           | ESD clamp circuits with ESD clamp nMOS transistor.                            |     |

| Fig. 4.8  | Measured TLP <i>I-V</i> curves of the (a) prior arts, (b) new proposed design | 109 |

|           | with ESD clamp nMOS transistor, and (c) the zoom-in illustration of (b).      |     |

| Fig. 4.9  | The voltage waveforms under (a) TLP transition with 4V voltage pulse and      | 110 |

|           | (b) fast power-on transition.                                                 |     |

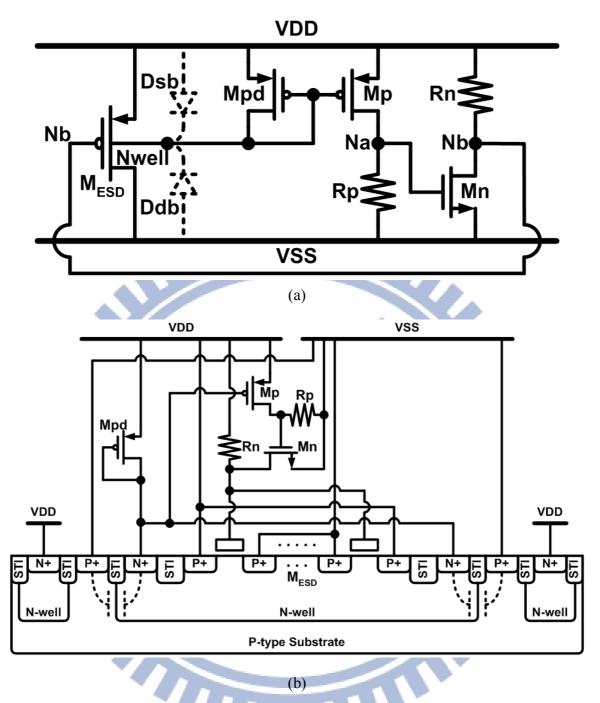

| Fig. 4.10 | The (a) circuit schematic and the (b) cross-sectional view of the new         | 111 |

|           | proposed ESD-transient detection circuit with ESD clamp pMOS transistor.      |     |

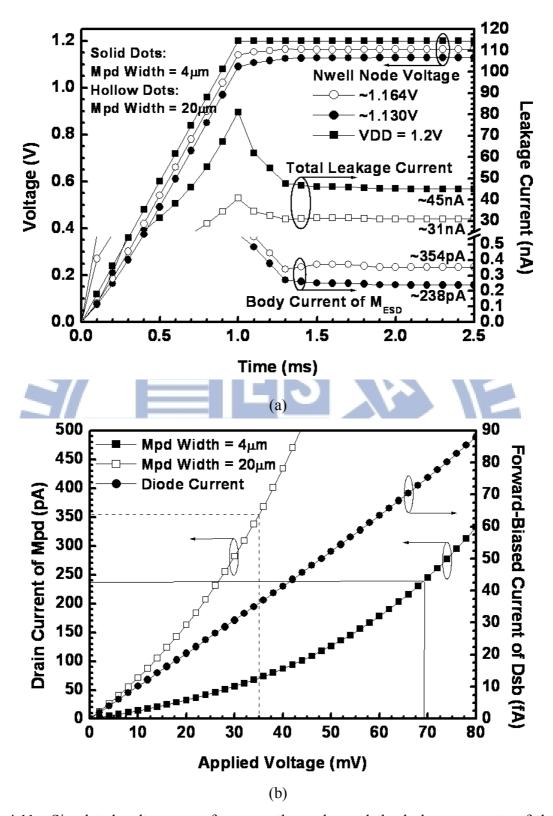

| Fig. 4.11 | Simulated voltage waveforms on the nodes and the leakage currents of the      | 112 |

|           | (a) proposed power-rail ESD clamp circuit with ESD clamp pMOS                 |     |

|           | transistor under the normal power-on transition and (b) diode-connected       |     |

|           | transistor Mpd and forward-biased diode Dsb.                                  |     |

| Fig. 4.12 | Simulated voltage waveforms on the nodes of the new proposed power-rail       | 113 |

|           | ESD clamp circuit with ESD clamp pMOS transistor under the ESD-like           |     |

|           | transition                                                                    |     |

| Fig. 4.13 | Chip microphotograph of the fabricated power-rail ESD clamp circuits with      | 113 |

|-----------|--------------------------------------------------------------------------------|-----|

|           | the (a) traditional RC-based, (b) smaller capacitance, (c) capacitor-less, and |     |

|           | (d) new proposed ultra-area-efficient ESD-transient detection circuits with    |     |

|           | ESD clamp pMOS transistor.                                                     |     |

| Fig. 4.14 | The measured standby leakage currents of the fabricated power-rail ESD         | 114 |

|           | clamp circuits with (a) prior art designs and (b) new proposed design with     |     |

|           | ESD clamp pMOS transistor.                                                     |     |

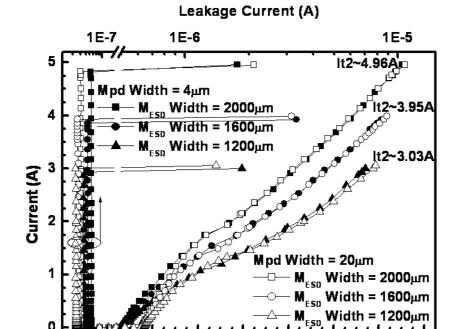

| Fig. 4.15 | TLP measured I-V curves of the power-rail ESD clamp circuits with the          | 115 |

|           | traditional <i>RC</i> -based and the smaller capacitance designs.              |     |

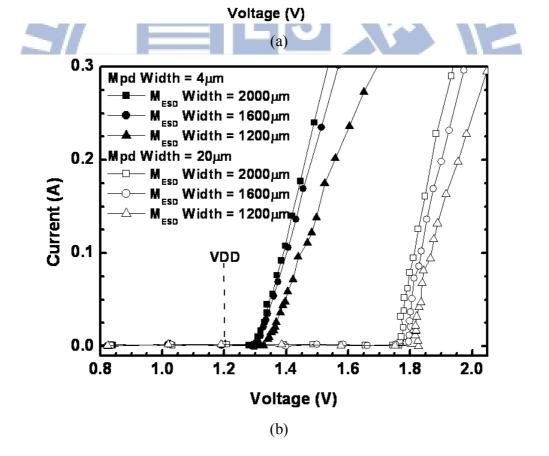

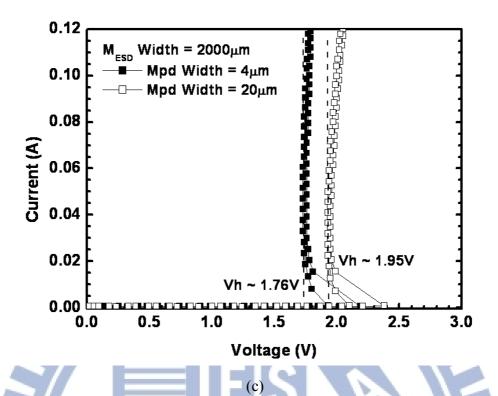

| Fig. 4.16 | Measured I-V curves of the new proposed power-rail ESD clamp circuits          | 117 |

|           | under (a) the TLP measurement, (b) the zoom-in illustration of TLP <i>I-V</i>  |     |

|           | curves for observing the holding voltages, and (c) the DC I-V measurement      |     |

|           | by curve tracer.                                                               |     |

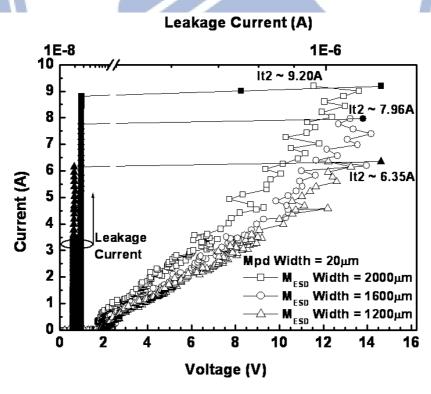

| Fig. 4.17 | VF-TLP measured <i>I-V</i> curves of the ultra-area-efficient power-rail ESD   | 117 |

|           | clamp circuits with Mpd width of 20µm under positive VDD-to-VSS ESD            |     |

|           | stress. 1896                                                                   |     |

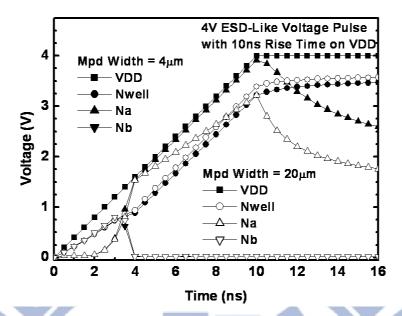

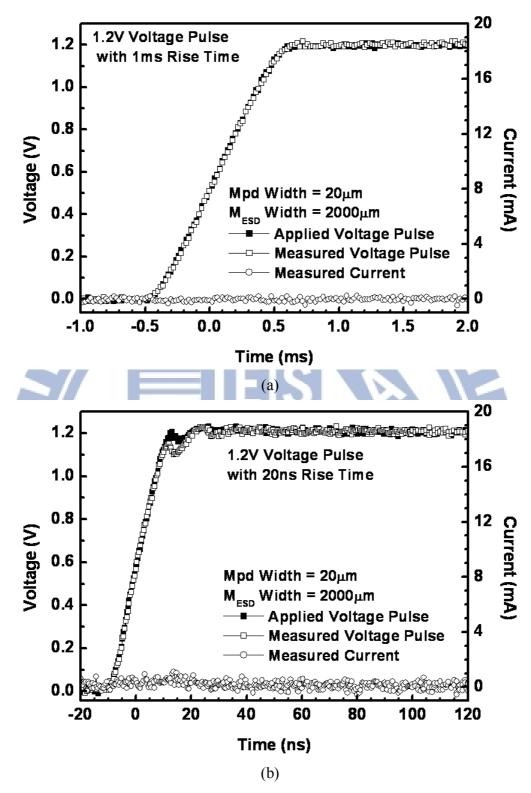

| Fig. 4.18 | The measured transient voltage and current waveforms of the                    | 118 |

|           | ultra-area-efficient power-rail ESD clamp circuit under the 1.2V power-on      |     |

|           | transition with the rise time of (a) 1ms and (b) 20ns.                         |     |

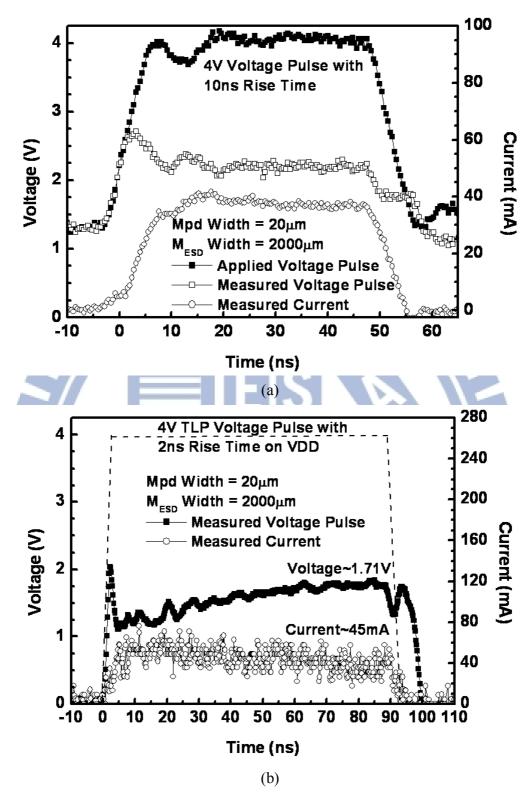

| Fig. 4.19 | Measured voltage and current waveforms of the new proposed power-rail          | 119 |

|           | ESD clamp circuit with ultra-area-efficient ESD-transient detection circuit    |     |

|           | under (a) transient noise condition and (b) TLP transition with 4V voltage     |     |

|           | pulse.                                                                         |     |

|           |                                                                                |     |

113

#### Chapter 5

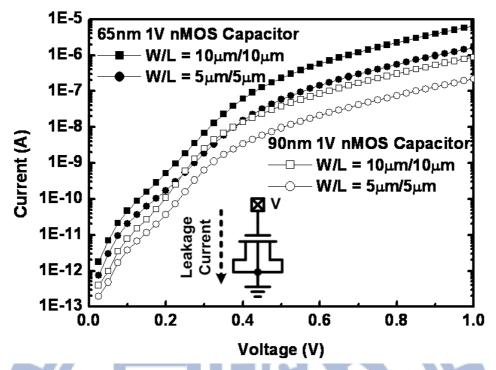

| Fig. 5.1 | Simulated gate currents of the nMOS capacitors in 65nm and 90nm CMOS         | 140 |

|----------|------------------------------------------------------------------------------|-----|

|          | technologies.                                                                |     |

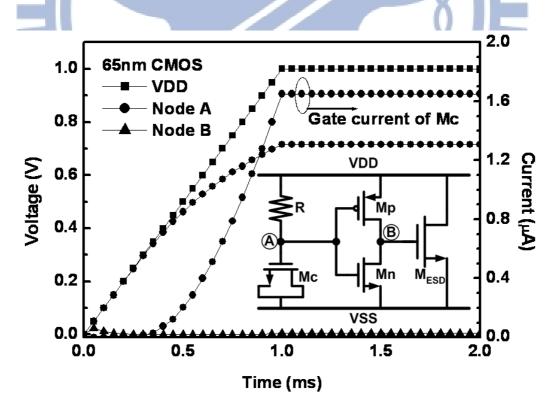

| Fig. 5.2 | Simulated node voltages of the traditional RC-based power-rail ESD clamp     | 140 |

|          | circuit [8] and the gate current flowing through the MOS capacitor Mc        |     |

|          | under the normal power-on condition with a rise time of 1ms in a 65nm        |     |

|          | CMOS process.                                                                |     |

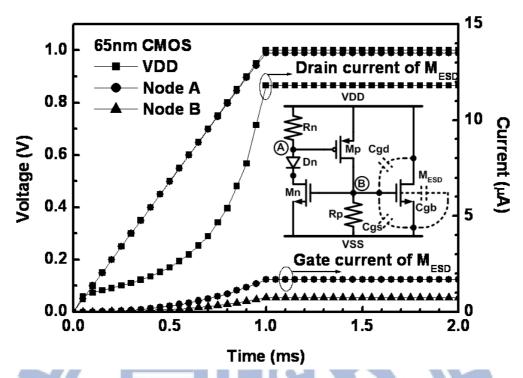

| Fig. 5.3 | Simulated node voltages of the capacitor-less power-rail ESD clamp circuit   | 141 |

|          | [47], the drain current, and the gate current flowing through the clamp      |     |

|          | device M <sub>ESD</sub> under the normal power-on transition.                |     |

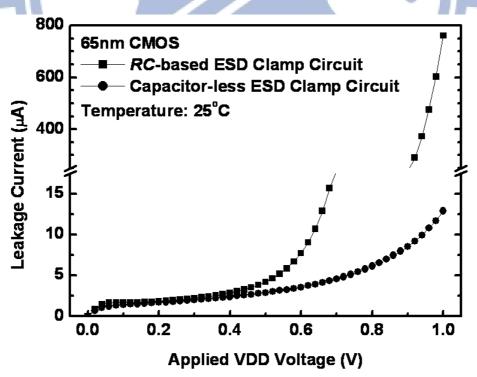

| Fig. 5.4 | The measured standby leakage currents of the traditional RC-based and the    | 141 |

|          | capacitor-less power-rail ESD clamp circuits.                                |     |

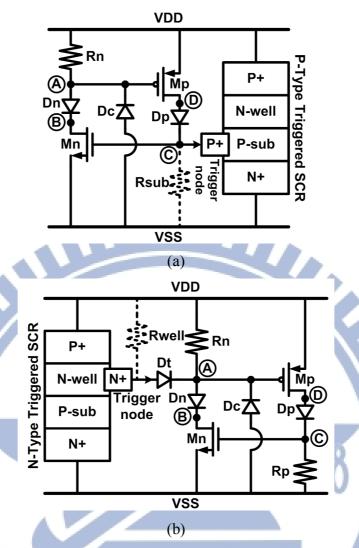

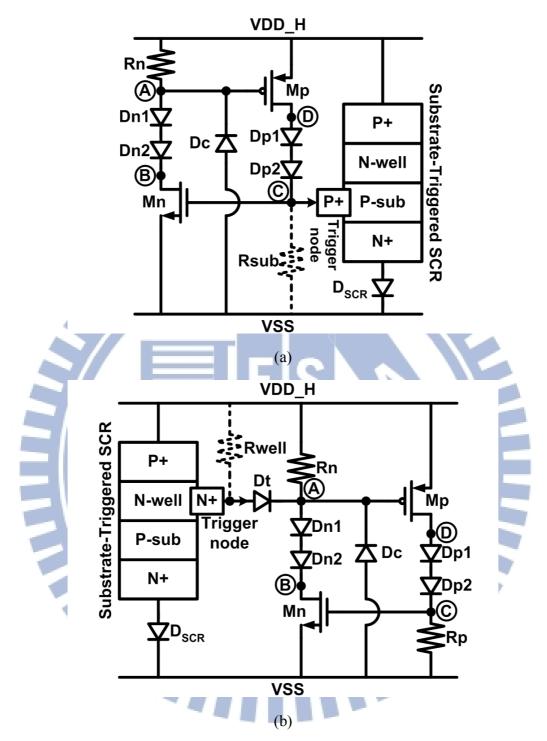

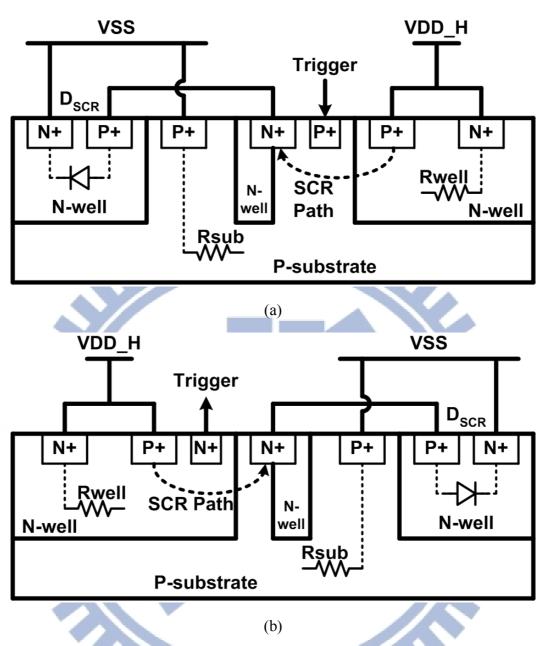

| Fig. 5.5 | The proposed low standby leakage power-rail ESD clamp circuits with (a)      | 142 |

|          | the p-type triggered SCR device, (b) the n-type triggered SCR device, as the |     |

|          | ESD clamp devices.                                                           |     |

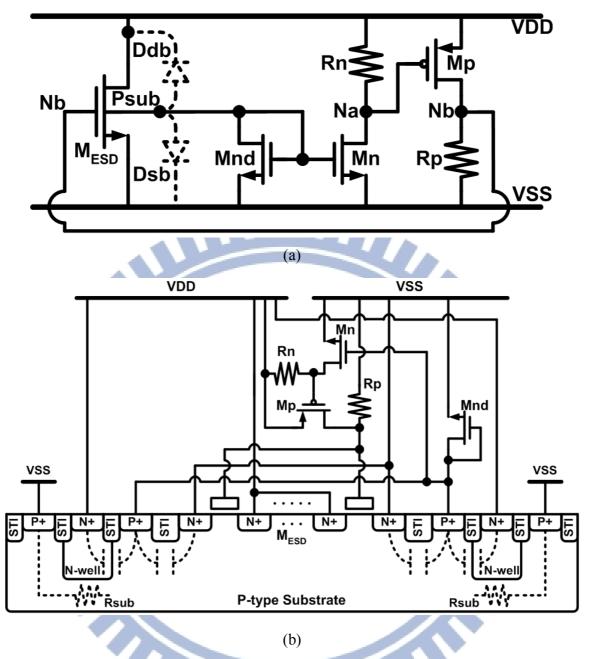

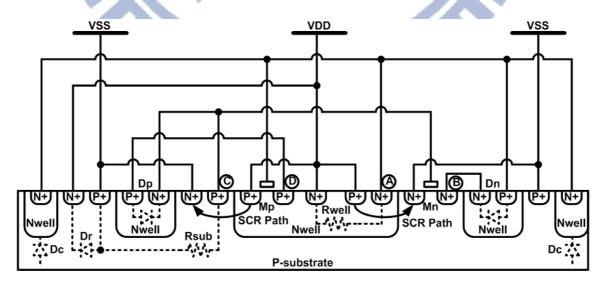

| Fig. 5.6 | Cross-sectional view of the proposed power-rail ESD clamp circuit with       | 142 |

|          | embedded ESD-transient detection circuit.                                    |     |

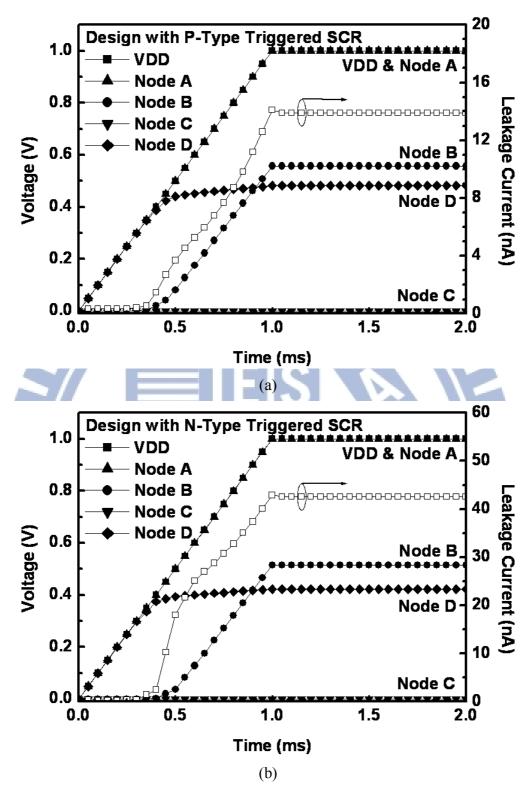

| Fig. 5.7 | Simulated voltage waveforms on the nodes and the leakage current of the      | 143 |

|          | ESD-transient detection circuit with (a) the p-type, and (b) the n-type,     |     |

|          | triggered SCR devices in 65nm 1V CMOS process under the normal               |     |

|          | power-on transition.                                                         |     |

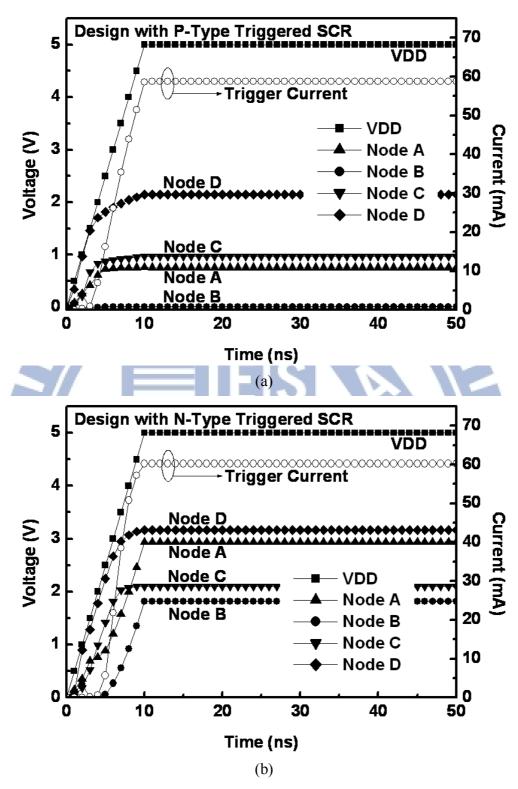

| Fig. 5.8 | Simulated voltages on the nodes and the trigger current of the               | 144 |

|          | ESD-transient detection circuit with (a) the p-type, and (b) the n-type,     |     |

|          | triggered SCR devices in 65nm 1V CMOS process under the ESD-like             |     |

|          | transition.                                                                  |     |

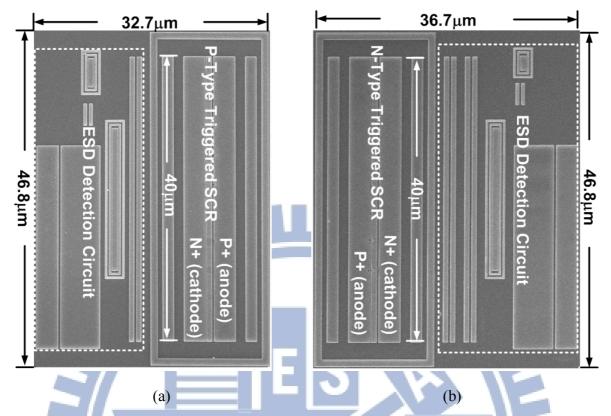

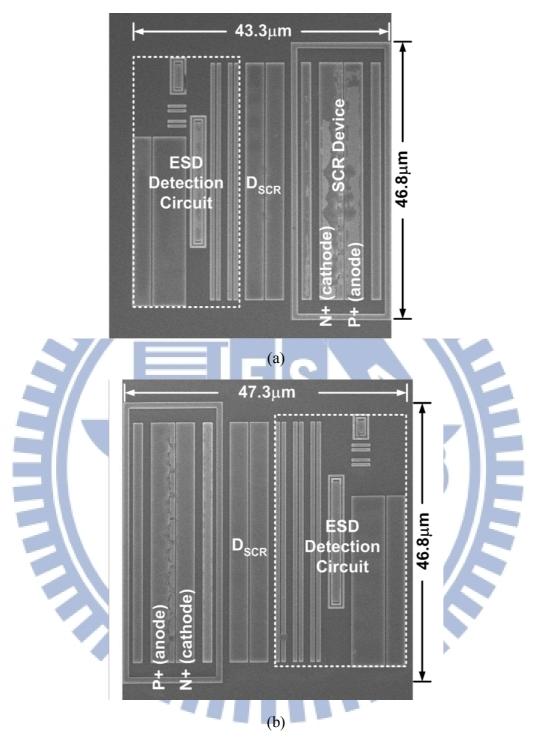

| Fig. 5.9 | 9  | The microphotograph of the fabricated power-rail ESD clamp circuits with    | 145 |

|----------|----|-----------------------------------------------------------------------------|-----|

|          |    | (a) the p-type triggered SCR and (b) the n-type triggered SCR, as the ESD   |     |

|          |    | clamp devices.                                                              |     |

| Fig. 5.  | 10 | The microphotograph of the fabricated power-rail ESD clamp circuit with     | 145 |

|          |    | the SCR device of 35 µm in width. (a) Embedded ESD-transient detection      |     |

|          |    | circuit design and (b) the p-type triggered design.                         |     |

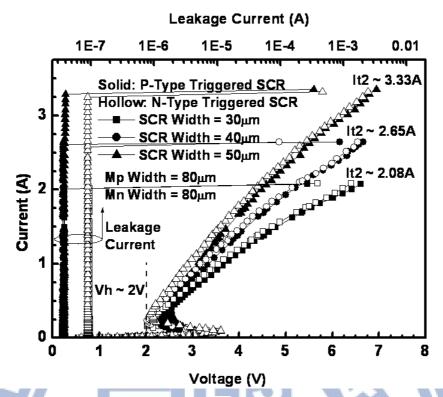

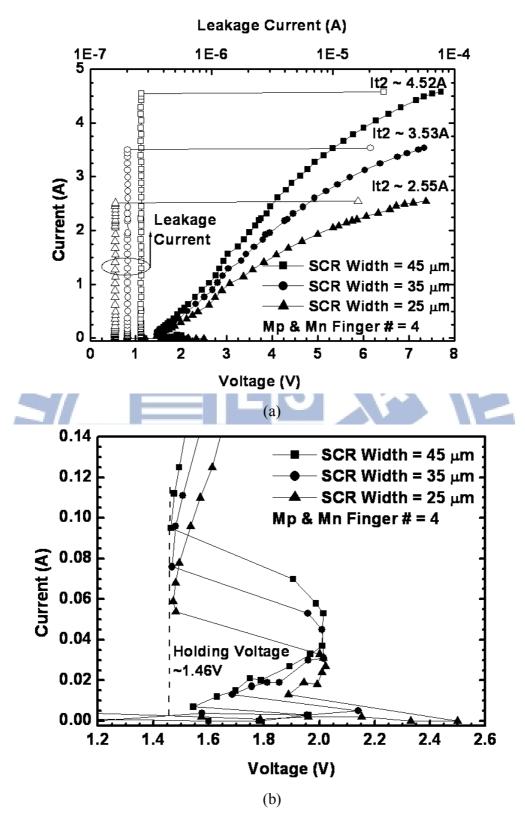

| Fig. 5.  | 11 | TLP measured I-V curves of the fabricated power-rail ESD clamp circuits     | 146 |

|          |    | with the SCR devices of different widths under positive VDD-to-VSS ESD      |     |

|          |    | stress for the p-type and n-type triggered SCR designs.                     |     |

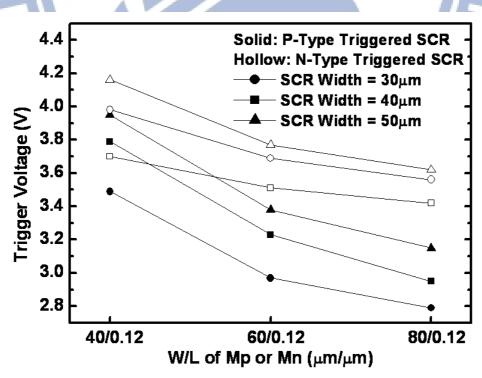

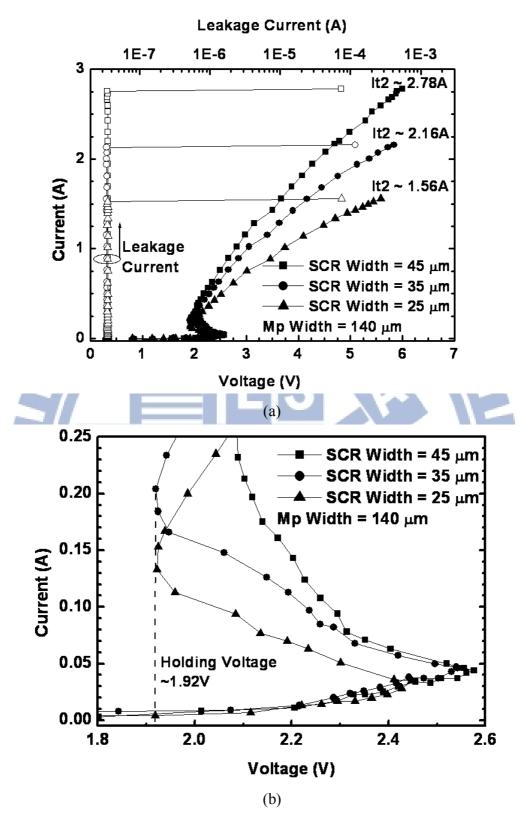

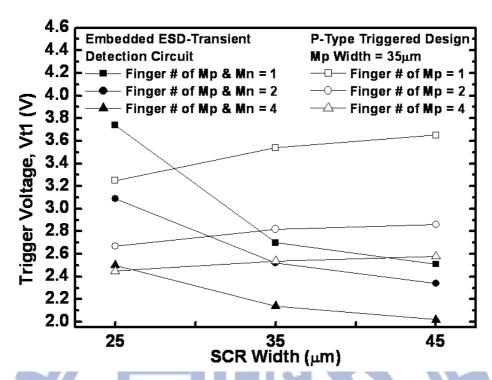

| Fig. 5.  | 12 | TLP measured trigger voltage of the p-type and n-type triggered design with | 146 |

|          |    | different width of Mp, Mn, and SCR device.                                  |     |

| Fig. 5.  | 13 | TLP measured curves of (a) the p-type triggered design with different SCR   | 147 |

|          |    | widths and (b) the zoom-in illustration for the holding voltage (Vh).       |     |

| Fig. 5.  | 14 | TLP measured curves of (a) the embedded ESD-transient detection circuit     | 148 |

|          | 1  | with different SCR widths and (b) the zoom-in illustration for the holding  |     |

|          | 1  | voltage (Vh). 1896                                                          |     |

| Fig. 5.  | 15 | The dependence of the TLP measured trigger voltages on the device           | 149 |

|          |    | dimensions of SCR.                                                          |     |

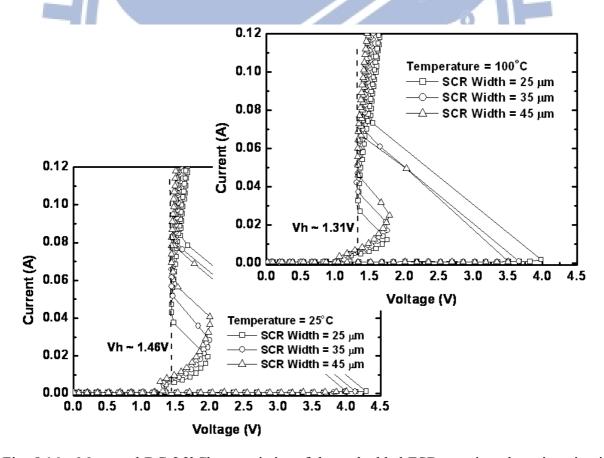

| Fig. 5.  | 16 | Measured DC I-V Characteristics of the embedded ESD-transient detection     | 149 |

|          |    | circuit at different temperatures.                                          |     |

| Fig. 5.  | 17 | The measured DC <i>I-V</i> curves of the fabricated power-rail ESD clamp    | 150 |

|          |    | circuits with SCR devices of different widths.                              |     |

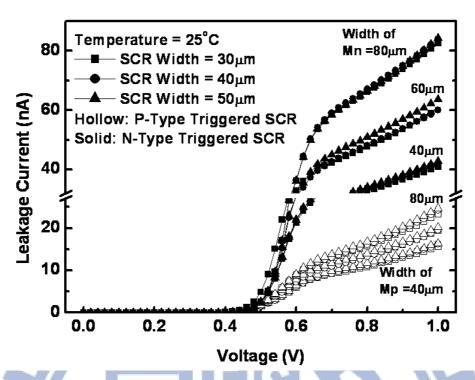

| Fig. 5.  | 18 | The measured leakage currents of the power-rail ESD clamp circuits with     | 150 |

|          |    | different SCR widths for p-type triggered design and embedded               |     |

|          |    | ESD-transient detection circuit design.                                     |     |

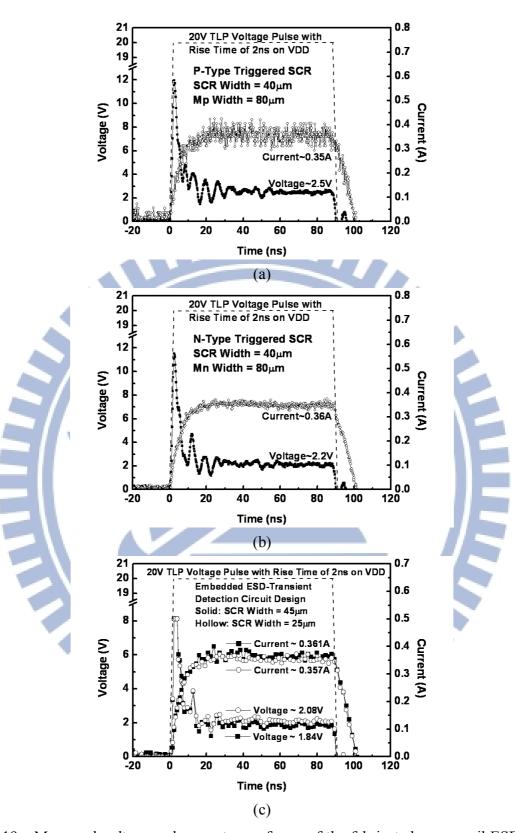

| rig. 3.19 Measured voltage and current waveforms of the fabricated power-ran ESD     | 131 |

|--------------------------------------------------------------------------------------|-----|

| clamp circuits with the SCR devices under TLP transition with different              |     |

| voltage pulse height, (a) the p-type triggered SCR, (b) the n-type triggered         |     |

| SCR, and (d) the embedded ESD-transient detection circuit design.                    |     |

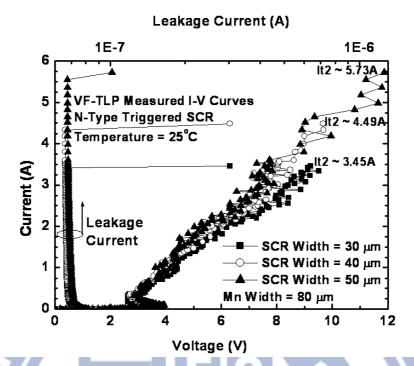

| Fig. 5.20 VF-TLP measured <i>I-V</i> curves of the fabricated power-rail ESD clamp   | 152 |

| circuits with the n-type triggered SCR device of different widths under              |     |

| positive VDD-to-VSS ESD stress. The VF-TLP is with a pulse width of                  |     |

| 10ns and a rise time of 200ps.                                                       |     |

| Fig. 5.21 ESD protection scheme with on-chip ESD bus for high-voltage-tolerant       | 152 |

| mixed-voltage I/O buffer.                                                            |     |

| Fig. 5.22 The proposed low-leakage 2×VDD-tolerant power-rail ESD clamp circuits      | 153 |

| with the (a) p-type and the (b) n-type triggered SCR as the ESD clamp                |     |

| devices.                                                                             |     |

| Fig. 5.23 Cross-sectional view of the ESD clamp devices composed of the (a) p-type   | 154 |

| and the (b) n-type triggered SCR devices with the cascode diode $\mathrm{D}_{SCR}$ . |     |

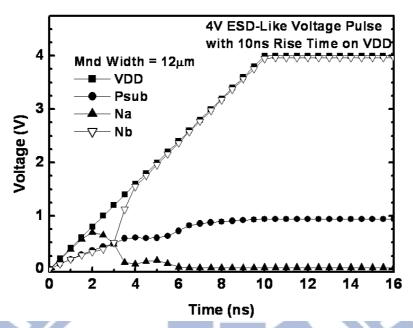

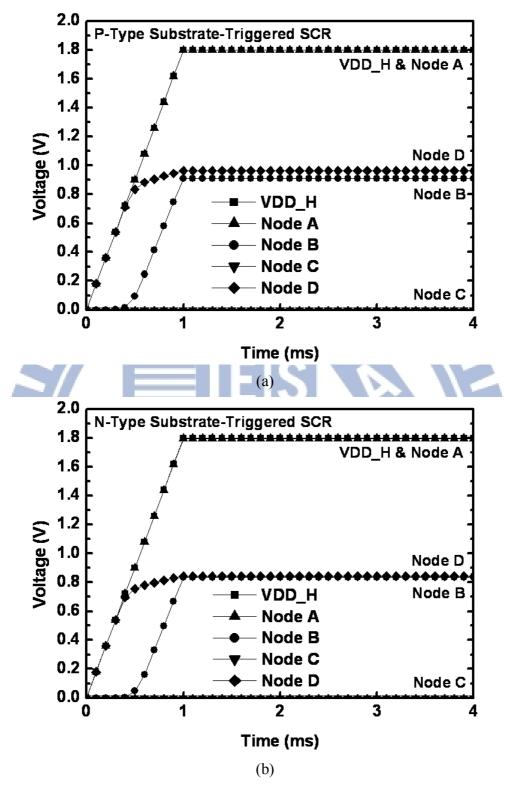

| Fig. 5.24 HSPICE-simulated voltages at the nodes of the ESD-transient detection      | 155 |

| circuit with (a) the p-type, and (b) the n-type, substrate-triggered SCR             |     |

| devices in 65nm CMOS process under the normal power-on condition with                |     |

| VDD_H of 1.8V and a rise time of 1ms.                                                |     |

| Fig. 5.25 HSPICE-simulated voltages at all nodes and the trigger current of the      | 156 |

| ESD-transient detection circuit with (a) the p-type, and (b) the n-type,             |     |

| substrate-triggered SCR devices in 65nm CMOS process under the                       |     |

| ESD-like transition condition with VDD_H raising from 0V to 5V and a                 |     |

| rise time of 10ns.                                                                   |     |

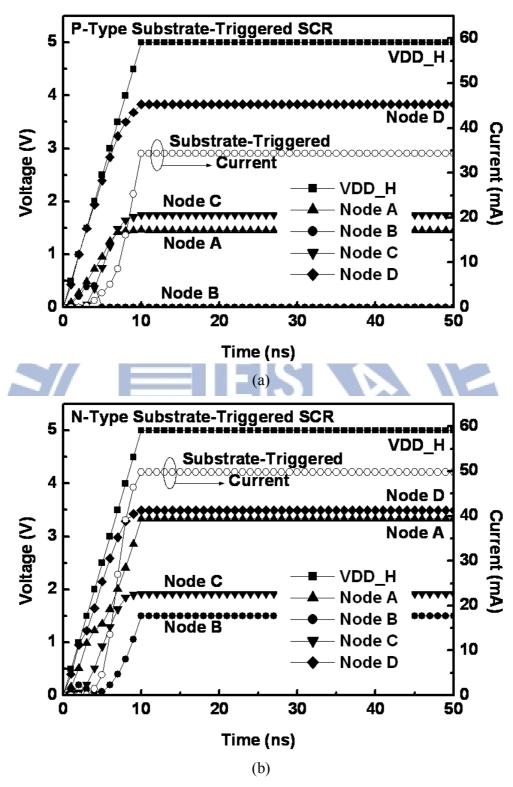

| Fig. 5.26 The proposed 2×VDD-tolerant power-rail ESD clamp circuits with the (a)     | 157 |

|           | is drawn with a width of 40μm.                                                |     |

|-----------|-------------------------------------------------------------------------------|-----|

| Fig. 5.27 | The measured DC <i>I-V</i> curves of the fabricated 2×VDD-tolerant power-rail | 158 |

|           | ESD clamp circuits with (a) the p-type and (b) the n-type                     |     |

|           | substrate-triggered SCR devices in 65nm CMOS process.                         |     |

| Fig. 5.28 | TLP measured <i>I-V</i> curves of the 2×VDD-tolerant power-rail ESD clamp     | 159 |

|           | circuit with (a) the p-type and (b) the n-type substrate-triggered SCR        |     |

|           | devices.                                                                      |     |

| Fig. 5.29 | Measured voltage waveforms of the fabricated 2×VDD-tolerant ESD clamp         | 160 |

|           | circuit with (a) the p-type and (b) the n-type substrate-triggered SCR        |     |

| 4         | devices under ESD-like condition with 5V voltage pulse and 10ns rise time.    |     |

|           |                                                                               |     |

| Chapter   | 6 8 =                                                                         |     |

| Fig. 6.1  | The simulated voltages on the nodes of the traditional RC-based power-rail    | 171 |

|           | ESD clamp circuit [8] and the gate current flowing through the MOS            |     |

|           | capacitor Mc under the normal power-on condition with a rise time of 1ms      |     |

|           | in a 65nm CMOS process.                                                       |     |

| Fig. 6.2  | The simulated voltages on the nodes of the capacitor-less power-rail ESD      | 171 |

|           | clamp circuit [47], the drain current, and the gate current flowing through   |     |

|           | the ESD clamp device $M_{\rm ESD}$ under the normal power-on transition.      |     |

| Fig. 6.3  | The measured standby leakage currents of the traditional RC-based and the     | 172 |

|           | capacitor-less power-rail ESD clamp circuits.                                 |     |

| Fig. 6.4  | The proposed resistor-less ESD detection circuit with the p-type              | 172 |

|           | substrate-triggered SCR device as the ESD clamp device.                       |     |

| Fig. 6.5  | Simulated voltage waveforms on the nodes and the leakage current of the       | 173 |

|           |                                                                               |     |

p-type and the (b) n-type substrate-triggered SCR devices, where the SCR

| transition with VDD of 1V and a rise time of 1ms in 65nm 1V CMOS                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| process.                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

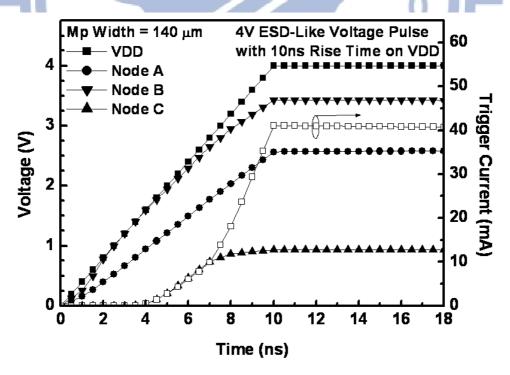

| Simulated voltage waveforms on the nodes and the trigger current of the                   | 173                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| proposed ESD-transient detection circuit under the ESD-like transition with               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VDD of 4V and a rise time of 10ns in 65nm 1V CMOS process.                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

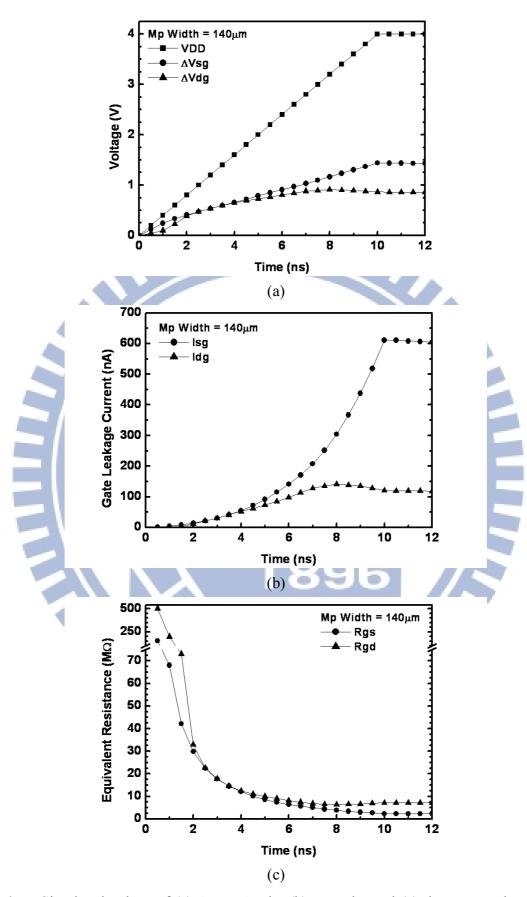

| Simulated values of (a) $\Delta Vsg$ , $\Delta Vdg$ , (b) Isg, Idg, and (c) the extracted | 174                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| equivalent resistances of Rgs and Rgd under the ESD-like transition.                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

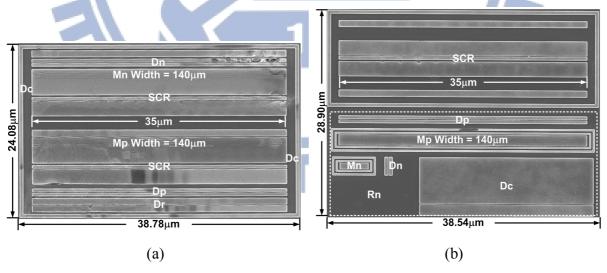

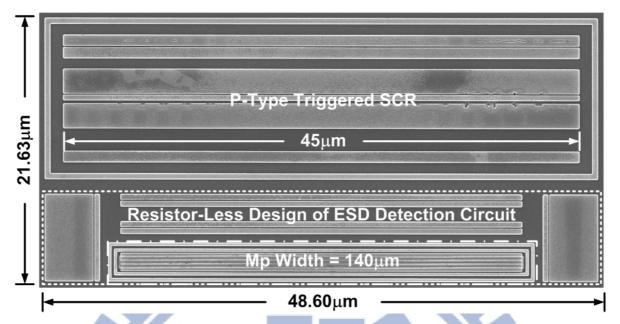

| Chip microphotograph of the fabricated power-rail ESD clamp circuit                       | 175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| realized with the resistor-less design of ESD-transient detection circuit.                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TLP measured <i>I-V</i> curves of the power-rail ESD clamp circuits with the              | 175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| resistor-less design of ESD detection circuit.                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

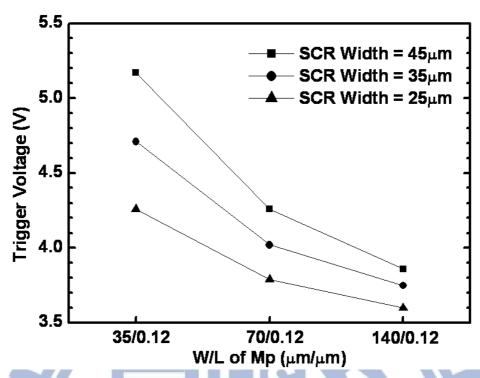

| The dependence of the TLP measured trigger voltages on the device                         | 176                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |