# 國立交通大學

電子工程學系 電子研究所碩士班

碩士論文

具有低輸入電流峰值抽載特性之 正負高壓產生器及其在生醫晶片上之應用

1896

Design of High-Voltage Generator with Low Supply Peak Current for Biomedical Applications

研究生: 鄭莞學 (Wan-Hsueh Cheng)

指導教授: 柯明道教授 (Prof. Ming-Dou Ker)

中華民國一〇四年十月

# 具有低輸入電流峰值抽載特性之 正負高壓產生器及其在生醫晶片上之應用

# Design of High-Voltage Generator with Low Supply Peak Current for Biomedical Applications

研究生: 鄭莞學 Student: Wan-Hsueh Cheng

指導教授:柯明道教授 Advisor: Prof. Ming-Dou Ker

國立交通大學 電子工程學系 電子研究所 碩士論文

#### A Thesis

Submitted to Department of Electronics Engineering and

Institute of Electronics

College of Electrical and Computer Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of

Master of Science

in

Electronics Engineering

October 2015

中華民國一〇四年十月

Hsinchu, Taiwan

# 具有低輸入電流峰值抽載特性之 正負高壓產生器及其在生醫晶片上之應用

學生: 鄭 莞 學 指導教授: 柯 明 道 教授

#### 國立交通大學

電子工程學系 電子研究所碩士班

近年來,由於生醫科學與半導體電子的快速發展,電刺激技術已被證明可藉 由電流訊號刺激神經來恢復身體的某些功能,例如視網膜、癲癇抑制、電子耳等。 在輸出電流刺激時,由於生物組織的阻抗較高,所以在刺激時在組織兩端會有高 電壓,故在生醫晶片中需要產生一高電壓與可耐高壓之刺激器。

電荷幫浦(charge pump)依據不同的架構可由低電壓產生正高壓與負高壓,此 篇論文提出一正高壓電荷幫浦與一負高壓電荷幫浦,並使用低壓製程製作,使用 之電荷幫浦架構沒有閘極可靠度(gate-reliability issue)的問題,量測分別可產生 10.8V與-10.3V高電壓,並使用回授控制使輸出電壓穩定,最大可輸出 3.5mA 電 流。改變電荷幫浦每級控制訊號,使 3.3V 之最大輸入瞬間抽載變小,且用四個 不同相位之控制訊號可減小電荷幫浦之漏電流(return-back leakage current)的影響, 改善電荷幫浦之效率。全電路皆實現在晶片上,不需要外掛電容,適合與其他電路整合在生醫單晶片上,此電路在 TSMC 0.18μm 1.8-V/3.3-V CMOS 製程下實現。

# Design of High-Voltage Generator with Low Supply Peak Current for Biomedical Applications

Student: Wan-Hsueh Cheng Advisor: Prof. Ming-Dou Ker

Department of Electronics Engineering & Institute of Electronics

National Chiao-Tung University

#### **Abstract**

Nowadays, due to the development of biomedical science and electronics, electrical stimulation had been proven can recover some physical functions of patients by current stimulation such as retinal stimulation, cochlear implant and suppression of epileptic seizure. Because the impedance of tissues is large, the voltage between tissues would be high when the stimulator driver deliver stimulus current. Therefore, we need to generate high voltage and high voltage tolerant stimulus drivers.

Charge pump can generate high positive voltage or high negative voltage from low voltage by different charge pump circuit. A positive charge pump and a negative charge pump has been designed to generate high voltage and negative without gate-reliability

issues in low voltage CMOS process. By measurement, the charge pumps can output regulated voltage about 10.8V and maximum current 3.5mA. The output voltage is regulated by PFM control feedback. The maximum output current is 3.5mA. The clock of each charge pump stage has phase shift different from each other, which can reduce the maximum peak current from 3.3V supply. The charge pump also adopt 4-phase clock scheme, which can reduce the return-back leakage and increase the charge pump's efficiency. The charge pump circuit is fully on chip and had been fabricated in TSMC  $0.18\mu m$  1.8-V/3.3-V CMOS process.

### **Contents**

| 摘要            |                                                                 |

|---------------|-----------------------------------------------------------------|

| Abstract      | II                                                              |

| Acknowledg    | mentVI                                                          |

| List of Table | s VIII                                                          |

| List of Figur | es                                                              |

| Chapter 1 In  | troduction                                                      |

| 1.1 N         | Motivation                                                      |

| 1.2           | Thesis Organization2                                            |

| Chapter 2 Pa  | rior Arts of Charge pump Circuits                               |

| <b>2.1</b> A  | Applications of Charge Pump Circuits for Biomedical Implants    |

| 2.2 I         | Positive Charge Pump Circuit                                    |

| 2.2           | 1 Dickson Charge Pump                                           |

| 2.2           | 2 Charge Transfer Switches Charge Pump                          |

| 2.2.          | 3 Cross-Couple Charge Pump                                      |

| <b>2.3</b> N  | Negative Charge Pump Circuit                                    |

|               | 1 4-phase Negative Charge Pump with PMOS Charge Transfer        |

|               | itches                                                          |

|               | 2 Cross-Couple Negative Charge Pump10                           |

|               | 3 4-phase Negative Charge Pump with NMOS Charge Transfer        |

|               | itches12                                                        |

| _             | esign of Positive Charge Pump Regulator with Low Input Peak     |

|               | rrent15                                                         |

|               | Design of Positive Charge Pump Regulator15                      |

|               | 1 Circuit Block Diagram of Proposed Positive Charge Pump        |

|               | gulator15                                                       |

|               | 2 Charge Pump Circuit and 4-phase Clock Generator18             |

| 3.1           | 3 Bandgap Reference, Error Amplifier, VCO and Phase Shift Clock |

|               | nerator20                                                       |

|               | Simulation Results22                                            |

| 3.3 N         | Measurement Results24                                           |

| <b>3.4</b> A  | Application on Biomedical Stimulation Circuit32                 |

| 3.5 \$        | Summary34                                                       |

| Chapter 4 D   | esign of Negative Charge Pump Regulator with Low Input Peak     |

| Cu            | rrent                                                           |

| 4.1 I         | Design of Negative Charge Pump Regulator35                      |

| 4.1.          | 1 Circuit Block Diagram of Proposed Charge Pump Regulator3      |

| 4.1.2 Negative Charge Pump and 4-phase Clock Generator     | 37 |

|------------------------------------------------------------|----|

| 4.1.3 Error Amplifier, VCO and Phase Shift Clock Generator | 42 |

| 4.2 Simulation Results                                     | 43 |

| 4.3 Measurement Results                                    | 45 |

| 4.4 Summary                                                | 56 |

| Chapter 5 Conclusions and Future Works                     | 57 |

| 5.1 Conclusions                                            | 57 |

| 5.1.1 Positive Charge Pump                                 | 57 |

| 5.1.2 Negative Cross-Couple Charge Pump                    | 57 |

| 5.2 Future Works                                           | 57 |

| 5.2.1 Charge Sharing                                       | 57 |

| 5.2.2 Negative Charge Pump                                 | 58 |

| References                                                 | 60 |

| Vita                                                       | 62 |

### Acknowledgment

感謝柯明道老師在這兩年的教導,讓我學到了非常多的東西,不僅僅是在專業領域上的精進,更學到了許多做事的態度。此外,也感謝老師讓我參與癲癇計畫及電子耳計畫,可以接觸到一些電子領域外的東西,也要感謝交大眾多教授的指教,每一堂課都對我的研究有很大的助益。

還有實驗室的同伴們,廖顯峰、黃義傑、劉睿閱、楊子毅,學習的過程中一同扶持與成長,能與大家一起渡過的這段時間,將會是我一生中美好回憶之一。以及實驗室的學長姐,林群祐學長、羅志聰學長、戴嘉岑學長、陳界廷學長、林倍如學姐、蔡惠雯學姐,在研究遇到問題時給予幫助。也感謝吳重雨校長實驗室的陳煒明博士、錢信宏學長、鄭丞翔學長、林子涵、陳志鑫、何家雄,在合作計畫時給予幫助與指導。感謝 CIC 給的 shuttle 下線機會與癲癇與電子耳計畫的下線機會,更要感謝交大土地公保庇讓晶片能動且成績可以順利 pass。

最後感謝爸我的父母,從小到大給予栽培與經濟支持,讓我能無憂無慮的 成長與順利的完成學業。

### **List of Tables**

| Table. 3.1 | Comparison of post-simulation and measurement31 |

|------------|-------------------------------------------------|

| Table, 4.1 | Comparison of post-simulation and measurement52 |

## **List of Figures**

| Fig. 2.1        | Architecture of epileptic stimulation SoC3                                                      |

|-----------------|-------------------------------------------------------------------------------------------------|

| Fig. 2.2        | Dickson charge pump with diode4                                                                 |

| Fig. 2.3        | Dickson charge pump with NMOS5                                                                  |

| Fig. 2.4        | Circuit of charge transfer switches (CTS's) charge pump6                                        |

| Fig. 2.5        | High voltage (HV) clock generator6                                                              |

| Fig. 2.6        | The cross-couple charge pump                                                                    |

| Fig. 2.7        | The negative charge pump with PMOS switches9                                                    |

| Fig. 2.8        | The 4-phase clock scheme of the negative charge pump with PMOS                                  |

|                 | switches10                                                                                      |

| Fig. 2.9        | Cross-couple negative charge pump11                                                             |

| Fig. 2.10       | (a) The deep N-well tied to source of PMOS. (b) The deep N-well tied to                         |

|                 | ground. [9]                                                                                     |

| Fig. 2.11       | Negative charge pump with NMOS switches14                                                       |

| Fig. 2.12       | 4-phase clock control scheme of the negative charge pump with NMOS switches                     |

|                 | switches14                                                                                      |

| Fig. 3.1        | The proposed charge pump regulator consists of error amplifier, phase                           |

|                 | shift clock generator, level shifter, 4 phase clock generator, and 3 stage                      |

|                 | charge pump16                                                                                   |

| Fig. 3.2        | (a) The clock waveform of clkd_1, clkd_2, and clkd_3 when $V_{\text{ctrlp}}$ is                 |

|                 | logic high. (b) The clock waveform of clkd_1, clkd_2, and clkd_3 when                           |

|                 | V <sub>ctrlp</sub> is logic low16                                                               |

| Fig. 3.3        | Current flow when clkbub is $V_{DDH}$                                                           |

| Fig. 3.4        | (a) Current flow from $V_{\text{DDH}}$ when $V_{\text{ctrlp}}$ logic low. (b) Current flow from |

|                 | $V_{DDH}$ when $V_{ctrlp}$ is logic high                                                        |

| Fig. 3.5        | The circuit of 3-stage charge pump19                                                            |

| <b>Fig. 3.6</b> | 4-phase clock waveforms which is generated from 4-phase clock                                   |

|                 | generator19                                                                                     |

| Fig. 3.7        | 4-phase clock generator                                                                         |

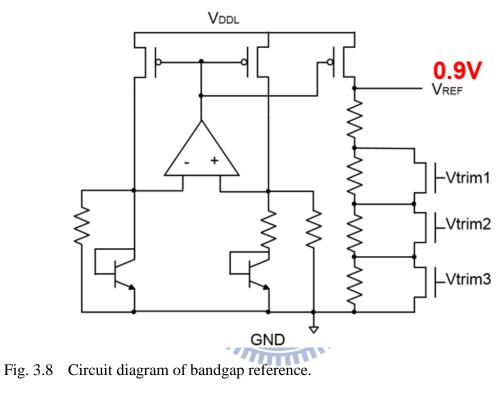

| Fig. 3.8        | Circuit diagram of bandgap reference20                                                          |

| Fig. 3.9        | Circuit diagram of error amplifier20                                                            |

| Fig. 3.10       | $Circuit\ diagram\ of\ current\ starve\ voltage\ control\ ring\ oscillator.\21$                 |

| Fig. 3.11       | Circuit diagram of phase shift clock generator and level shifter22                              |

| Fig. 3.12       | Simulation results of charge pump when (a) $V_{ctrlp}$ =0 and $I_{load}$ =3.5mA                 |

|                 | (b) $V_{ctrlp}$ =1 and $I_{load}$ =3.5mA23                                                      |

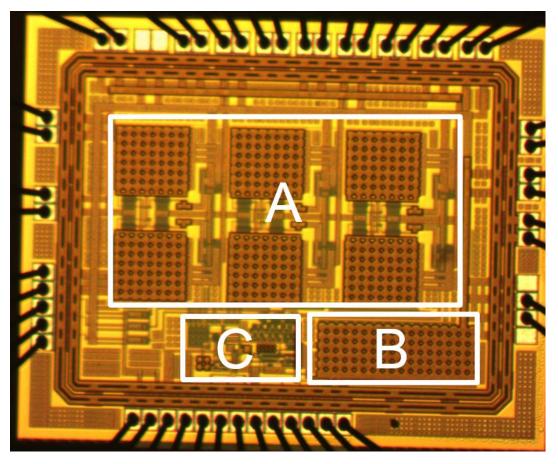

| Fig. 3.13 | Die photograph with A: 3-stage charge pump and 4-phase clock                                |

|-----------|---------------------------------------------------------------------------------------------|

|           | generator, B: output capacitor of charge pump, and C: bandgap                               |

|           | reference, VCO, error amplifier and phase shift clock generator24                           |

| Fig. 3.14 | (a) Measurement setup of power supply, oscilloscope and test chip. (b)                      |

|           | Measurement environment                                                                     |

| Fig. 3.15 | The measurement result of power on time26                                                   |

| Fig. 3.16 | Waveforms of OT1, OT2 and OT3 when I <sub>load</sub> is 0.5mA26                             |

| Fig. 3.17 | The measurement result of output voltage (V $_{\rm CC}$ ) when $I_{load}$ is 3.5mA27        |

| Fig. 3.18 | The measurement result of output voltage ( $V_{\rm CC}$ ) versus different                  |

|           | loading current (I <sub>load</sub> )28                                                      |

| Fig. 3.19 | The measurement result of efficiency versus different loading current                       |

|           | (I <sub>load</sub> )                                                                        |

| Fig. 3.20 | The measurement result of output ripple versus different loading                            |

|           | current (I <sub>load</sub> )                                                                |

| Fig. 3.21 | The measurement setup for measuring IVDDH30                                                 |

| Fig. 3.22 | The measurement result of input current (IVDDH) from $V_{DDH}$ when $I_{load}$              |

|           | is 1.5mA30                                                                                  |

| Fig. 3.23 | The measurement result of input current (I_{VDDH}) from $V_{DDH}$ when $I_{load}$           |

|           | is 3.5mA30                                                                                  |

| Fig. 3.24 | The measurement result of IVDDHmax in three different chip31                                |

| Fig. 3.25 | Block diagram of cochlear SoC                                                               |

| Fig. 3.26 | Die photograph with A: stimulator driver, B: DSP, C: positive charge                        |

|           | pump circuit, D: demodulator and back telemetry, and E: rectifier and                       |

|           | regulator33                                                                                 |

| Fig. 3.27 | Measurement result of stimulator and charge pump in cochlear SoC. 33                        |

| Fig. 4.1  | Block diagram of negative charge pump36                                                     |

| Fig. 4.2  | (a)The clock waveform of clkd_1, clkd_2, clkd_3 and clkd_4 when $V_{\text{ctrlp}}$          |

|           | is low (0). (b) The clock waveform of clkd $_1$ , clkd $_2$ , clkd $_3$ and clkd $_4$       |

|           | when V <sub>ctrlp</sub> is high (1)37                                                       |

| Fig. 4.3  | One stage of proposed negative charge pump40                                                |

| Fig. 4.4  | 4-phase clock waveforms of clk1, clk2, clk3 and clk440                                      |

| Fig. 4.5  | 4-phase clock generator40                                                                   |

| Fig. 4.6  | 4-stage cross couple negative charge pump41                                                 |

| Fig. 4.7  | Connection of deep N-well in the charge pump circuit42                                      |

| Fig. 4.8  | Circuit of phase shift clock generator43                                                    |

| Fig. 4.9  | Simulation result of charge pump when (a)V <sub>ctrlp</sub> =0 and I <sub>load</sub> =3.5mA |

|           | (b) $V_{ctrln}=1$ and $I_{load}=3.5$ mA44                                                   |

| <b>Fig. 4.10</b> | Die photograph with A: 4-stage charge pump and 4-phase clock                      |

|------------------|-----------------------------------------------------------------------------------|

|                  | generator, B: output capacitor of charge pump, and C: VCO, error                  |

|                  | amplifier and phase shift clock generator45                                       |

| Fig. 4.11        | Measurement setup of test chip46                                                  |

| Fig. 4.12        | Measurement of power on time                                                      |

| Fig. 4.13        | Measurement of phase shift clock generator47                                      |

| Fig. 4.14        | Measurement of V <sub>LL</sub> when I <sub>load</sub> is 3.5mA                    |

| Fig. 4.15        | Measurement of output voltage (V <sub>LL</sub> ) versus different loading current |

|                  | (I <sub>load</sub> )48                                                            |

| Fig. 4.16        | Measurement of efficiency versus different loading current (I <sub>load</sub> )49 |

| Fig. 4.17        | Measurement of output ripple versus different loading current ( $I_{load}$ ). 49  |

| Fig. 4.18        | The measurement setup for measuring IVDDH50                                       |

| Fig. 4.19        | The measurement result of input current (IVDDH) from VDDH when Iload              |

|                  | is 1.5mA51                                                                        |

| Fig. 4.20        | The measurement result of input current (IVDDH) from $V_{DDH}$ when $I_{load}$    |

|                  | is 3.2mA51                                                                        |

| Fig. 4.21        | is 3.2mA                                                                          |

|                  | three different chip                                                              |

| Fig. 4.22        | Transient response of regulator                                                   |

| Fig. 4.23        | The measurement setup to observe the influence of lower peak                      |

|                  | current53                                                                         |

| Fig. 4.24        | The measurement environment to observe output voltage of LM31753                  |

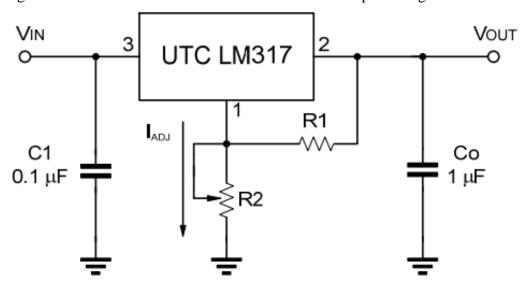

| Fig. 4.25        | The circuit diagram of LM31753                                                    |

| Fig. 4.26        | The waveform of $V_{DDH}$ when charge pump is turned off54                        |

| Fig. 4.27        | The waveform of $V_{DDH}$ in different control voltage ( $V_{ctrlp}$ )54          |

| Fig. 4.28        | The measurement result of MIM capacitor55                                         |

| Fig. 5.1         | The charge sharing concept [20]58                                                 |

| Fig. 5.2         | The circuit of negative charge pump59                                             |

### Chapter 1

#### Introduction

#### 1.1 Motivation

As bioelectronics developed, many stimulators have been investigated and demonstrated. For biomedical stimulation circuit, we need to generate a high voltage to drive stimulator and the stimulus chip need to be small for implantation. So, the stimulus circuits are designed fully on-chip. However, the on-chip inductor is about ~nH, which is difficult to be used in boost converter.

Charge pump circuit use capacitors and switches to pump charge and can generate high voltage which is higher than the supply voltage from low voltage. Moreover, charge pump can generate high voltage by high switching frequency with capacitors fully on-chip. So, it is suitable for implantation circuit in low voltage process.

Some problems of conventional charge pump circuit had been studied, such as body effect, gate-reliability issues, threshold voltage drop, and return-back leakage current.

In this work, by adopting 4-pahse charge pump and PFM feedback, we designed a positive charge pump and a negative charge pump can output regulated voltage without the problems of conventional charge pump circuit. Moreover, we apply phase shift clock control scheme. The control clock of each charge pump stage has phase shift different from each other, which can decrease the peak input current from supply and can enhance the transient response of the front dc-dc converter.

#### 1.2 Thesis Organization

This thesis is organized into five chapters and this introduction is the first one. Chapter 2 introduces the applications and the prior arts of charge pump circuits. In chapter 3, a charge pump circuit which can generate 11V is presented, and the measurement results are also shown in this chapter. In chapter 4, a new cross-couple negative charge pump circuit without the gate-oxide reliability issues and reducing the return-back leakage current is presented, and the measurement results are also shown in this chapter. Chapter 5 is the conclusions of this thesis and the future works of charge pump circuits.

### Chapter 2

### **Prior Arts of Charge pump Circuits**

#### 2.1 Applications of Charge Pump Circuits for Biomedical Implants

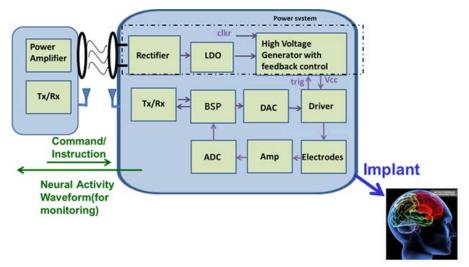

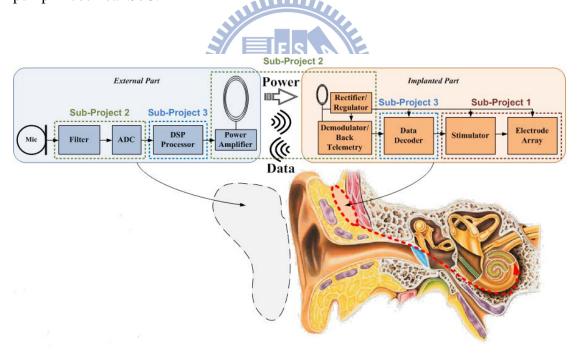

Nowadays, biphasic stimulators are generally used for retinal, cochlear, and neural [1]~[3]. The biphasic stimulators can output anodic and cathodic stimulus current. Because tissue has high impedance, the supply voltage of stimulators need to be high. Some biphasic stimulators use both high positive voltage and high negative voltage for stimulus drivers [1]. For biomedical implants, the area of implanted chip should be small and the use of off-chip elements should be decreased, so CMOS technologies are suitable to realize the system on a chip (SoC). Therefore, the charge pump circuits should be realized in low-voltage CMOS processes and better be fully on-chip. Fig.2.1 depicts the architecture of epileptic stimulation SoC. It use wireless power to supply the implant part. The high voltage generator is integrated with other circuits in single chip.

Fig. 2.1 Architecture of epileptic stimulation SoC.

#### 2.2 Positive Charge Pump Circuit

#### 2.2.1 Dickson Charge Pump

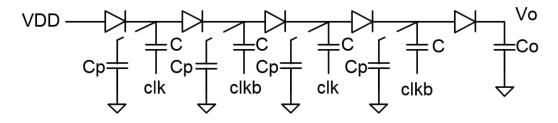

Fig. 2.2 depicts the Dickson charge pump [4], which consists of diodes and pumping capacitor (C). C<sub>P</sub> is parasitic capacitor and C<sub>O</sub> is output capacitor. When clk is logic high (clkb is logic low), the even stage diodes are turn on, the odd stage diodes are turn off. Also, when clk is logic low (clkb is logic high), the even stage diodes are turn off, the odd stage diodes are turn on. The charge can be delivered from front stage to the next stage. Due to the parasitic capacitor (C<sub>P</sub>), the voltage swing of each node is the clock swing (V<sub>clk</sub>) divided by capacitance divider. Since the total charge pumped by diode during each clock cycle is output loading current (I<sub>load</sub>) multiply by the clock period (1/f), the voltage drop of each stage can be shown as (2.1). Also, each stage has the diode forward voltage drop (V<sub>D</sub>), the voltage fluctuation of each stage can be shown as (2.2). For N stage Dickson charge pump, the output voltage is shown as (2.3).

$$\Delta V_{\text{drop}} = \frac{I_{\text{load}}}{f(C + C_{\text{P}})}$$

(2.1)

$$\Delta V = V_{\text{clk}} \times \frac{c}{c + c_P} - \frac{I_{\text{load}}}{f(c + c_P)} - V_D$$

(2.2)

$$V_{O} = N \left( V_{clk} \times \frac{C}{C + C_{P}} - \frac{I_{load}}{f(C + C_{P})} - V_{D} \right) - V_{D}$$

(2.3)

Fig. 2.2 Dickson charge pump with diode.

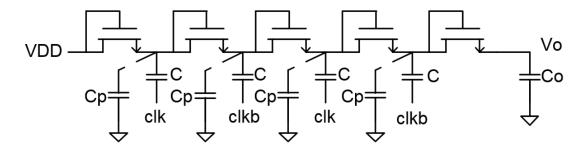

Fig. 2.3 is the Dickson charge pump with NMOS [5], which consists of diode connected NMOS, pumping capacitor and output capacitor. The same as the conventional charge pump, each stage has the voltage drop of MOS threshold voltage  $(V_t)$ . In this circuit, if the MOS body don't connect with MOS source, it has body effect,

which may increase conduction loss of MOS switch. Therefore, the efficiency of this circuit is decreased as the stage increases. Besides, the maximum voltage difference between MOS source and drain is  $2V_{clk}$ - $V_t$ . In low voltage process, the MOS may have gate-reliability issues.

Fig. 2.3 Dickson charge pump with NMOS.

#### 2.2.2 Charge Transfer Switches Charge Pump

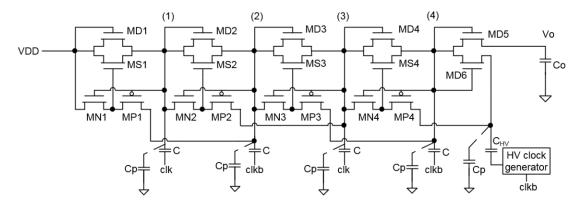

Fig. 2.4 depicts the charge transfer switches (CTS's) charge pump [6], which consists of diode connected MOS (MD1~MD6), charge transfer switch (MS1~MS4), pass transistors (MN1~MN4 and MP1~MP4), pumping capacitor (C) and high-voltage (HV) clock generator. The CTS's in this circuit can be turned off completely and each stage doesn't have forward voltage drop and threshold voltage drop as the conventional Dickson charge pump.

When clk is logic low (clkb is logic high), MP1 is turned on and then MS1 is turned on to transfer  $V_{DD}$  to node 1 without threshold voltage drop. At the same time, MN2 is turned on to cut off MS2 for reducing leakage from node 2 to node 1. Similarly, when clk is logic high (clkb is logic low), the voltage of node 1 is  $2V_{DD}$ . MP2 is turned on and then MS2 is turned on to transfer  $2V_{DD}$  to node 2 without threshold voltage drop. At the same time, MN1 is turned on to cut off MS1 for reducing leakage from node 1 to  $V_{DD}$ .

Following this operation, the voltage can be pumped high with high efficiency, but there is a threshold voltage drop ( $V_t$ ) at the last stage (MD5). In order to generate control waveform to control MS4, MD6 and  $C_{HV}$  are added. Besides, the HV clock generator is added to let MS4 can turn on in low supply voltage operation. The HV clock generator can generate  $0 \sim 2V_{DD}$  clock and the circuit is shown as Fig. 2.5.

This charge pump circuit utilizes charge transfer switches to transfer charge without threshold voltage drop, but it still has the threshold voltage drop at the last stage.

Besides, the maximum voltage difference across MOS is  $2V_{DD}$ , which cause gate-reliability issues. Due to the parasitic capacitor ( $C_P$ ) and loading current ( $I_{load}$ ), the output voltage is shown as (2.4).

$$V_{O} = N \left( V_{clk} \times \frac{C}{C + C_{P}} - \frac{I_{load}}{f(C + C_{P})} \right) - V_{t}$$

(2.4)

Fig. 2.4 Circuit of charge transfer switches (CTS's) charge pump.

Fig. 2.5 High voltage (HV) clock generator.

#### 2.2.3 Cross-Couple Charge Pump

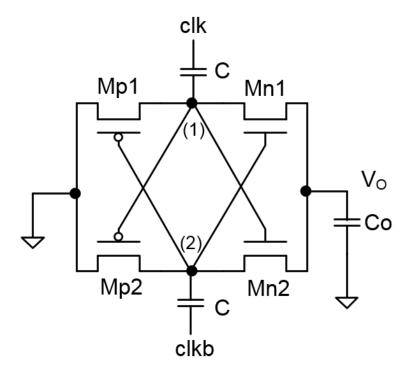

Some modified charge pump circuits based on Dickson charge pump were invented to overcome threshold voltage drop and to improve pumping gain and efficiency. However, those charge pump circuits have gate-oxide reliability issues because of the gate-source voltages and gate-drain voltages exceed normal operating voltage of MOS. In order to overcome gate-oxide reliability issues, some charge pump circuits were proposed. Fig 2.6 depicts the cross-couple charge pump [7], which was

designed without overstress voltage across MOS and realized in low voltage CMOS process.

When clk is logic low (clkb is logic high), the voltage of node 1 become  $V_{DD}$  and the voltage of node 2 become  $2V_{DD}$  due to clkb. At the same time, Mn1 is turned on and Mp1 is turned off. Mn2 is turned off and Mp2 is turned on. The voltage of node 4 become  $2V_{DD}$ .

Similarly, when clk is logic high (clkb is logic low), the voltage of node 2 become  $V_{DD}$  and the voltage of node 1 become  $2V_{DD}$  due to clk. At the same time, Mn2 is turned on and Mp2 is turned off. Mn1 is turned off and Mp1 is turned on. The voltage of node 3 become  $2V_{DD}$ . By these operations, the voltage can be pumped high without gate-oxide reliability issues. Moreover, this circuit doesn't have threshold voltage drop by using MOS switches to transfer charge. Besides, this circuit used two branches, which can have less output voltage ripple at the output.

Fig. 2.6 The cross-couple charge pump.

#### 2.3 Negative Charge Pump Circuit

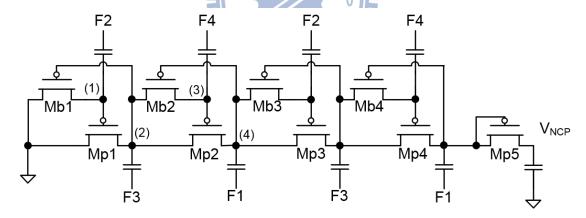

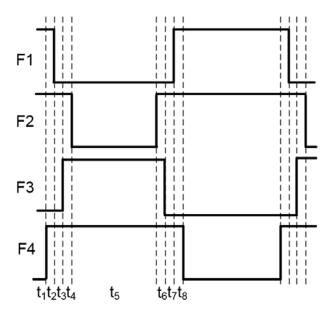

#### 2.3.1 4-phase Negative Charge Pump with PMOS Charge Transfer Switches

Fig.2.7 depicts the negative charge pump [8], which consists of PMOS transfer switches and pumping capacitors. The last stage used diode connected PMOS to prevent

leakage current. This charge pump use 4-phase clock scheme to control PMOS transfer switches, the 4-phase clock is shown as Fig.2.8.

Here, we separate 4-phase clock to eight intervals. At the interval  $t_1$ , the voltage of node 1 is GND and the voltage of node 2 is  $-V_{DD}$ , where  $V_{DD}$  is the voltage swing of clock. The voltage of node 3 is  $-2V_{DD}$  and the voltage of node 4 is  $-V_{DD}$ . Mp1 and Mb1 are turned off, and Mb1 and Mp2 are turned on to transfer charge.

At the interval  $t_2$ , the voltage of F4 is rose to high ( $V_{DD}$ ). The voltage of node 3 is rose to  $-V_{DD}$  to cut off Mp2. The voltage of node 1, node 2 and node 4 are the same as the voltage at interval  $t_1$ . Mp1 and Mp2 keep being turned off and Mb1 keep being turned on.

At the interval t<sub>3</sub>, the voltage of F1 is dropped to low (GND). The voltage of node 4 is dropped to -2V<sub>DD</sub>. The voltage of node 1, node 2 and node 3 are the same as the voltage at time interval t<sub>2</sub>. Mp2 keep being turned off to prevent leakage current from node 2 to node 4 and Mb2 is turned on by the voltage drop of node 4. Mp1 keep being turned off, and Mb1 keep being turned on.

At the interval t<sub>4</sub>, the voltage of F3 is rose to high (V<sub>DD</sub>). The voltage of node 2 is rose to GND to cut off Mb1 and the voltage of node 3 is charged to GND to keep cut off Mp2. The voltage of node 1 and node 4 are the same as the voltage at time interval t<sub>3</sub>. Mp1 keep being turned off and Mb2 keep being turned on to transfer charge from node 2 to node 3.

At the interval t<sub>5</sub>, the voltage of F2 is dropped to low (GND). The voltage of node 1 is dropped to -V<sub>DD</sub> to turn on Mp1 and the voltage of node 2 become GND. The voltage of node 3 and node 4 are the same as the voltage at time interval t<sub>4</sub>. Mp2 keep being turned off and Mb2 keep being turned on.

At the interval  $t_6$ , the voltage of F2 is rose to high ( $V_{DD}$ ). The voltage of node 1 is rose to GND to turn off Mp1. The voltage of node2, node 3 and node 4 are the same as

the voltage at time interval t<sub>5</sub>. Mp2 and Mb1 keep being turned off and Mb2 keep being turned on.

At the interval t<sub>7</sub>, the voltage of F3 is dropped to low (GND). The voltage of node 2 is dropped to -V<sub>DD</sub> and the voltage of node 3 is dropped to -V<sub>DD</sub> as well. The voltage of node 1 and node 4 are the same as the voltage at time interval t<sub>6</sub>. Mp1, Mb1 and Mp2 keep being turned off and Mb2 keep being turned on.

At the interval  $t_8$ , the voltage of F1 is rose to high ( $V_{DD}$ ). The voltage of node 4 is rose to - $V_{DD}$  to turn off Mb2. The voltage of node1, node 2 and node 3 are the same as the voltage at time interval  $t_7$ . Mb1, Mp1 and Mp2 keep being turned off.

By these operations, the voltage of output can pumped to negative high voltage. The advantage of this pump is no leakage current by 4-phase clock scheme. However, the maximum voltage stress on PMOS is as high as 2VDD, which may cause gate-reliability issues in low voltage CMOS process.

Fig. 2.7 The negative charge pump with PMOS switches.

Fig. 2.8 The 4-phase clock scheme of the negative charge pump with PMOS switches.

#### 2.3.2 Cross-Couple Negative Charge Pump

Fig.2.9 is cross-couple negative charge pump [9], which consist of NMOS and PMOS charge transfer switches and pumping capacitor. This charge pump use two non-overlap clock to operate this circuit.

When clk is logic low (clkb is logic high), the voltage of node 1 is dropped to -  $V_{DD}$  and the voltage of node 2 is rose to GND, where  $V_{DD}$  is the voltage swing of clock. Then, Mn1 is turned on to transfer charge and Mp1 is turned off. Mn2 is turned off and Mp2 is turned on. The voltage of output become - $V_{DD}$ , which is the same as node 1.

Similarly, when clk is logic high (clkb is logic low), the voltage of node 1 is rose to GND and the voltage of node 2 is dropped to  $-V_{DD}$ . Then, Mn1 is turned off to and Mp1 is turned on transfer charge. Mn2 is turned on and Mp2 is turned off. The voltage of output become  $-V_{DD}$ , which is the same as node 2.

By this operation, the voltage can be pumped to negative high. Moreover, the maximum voltage stress of MOS switches is VDD, which may not cause gate-oxide reliability issues in low voltage CMOS process.

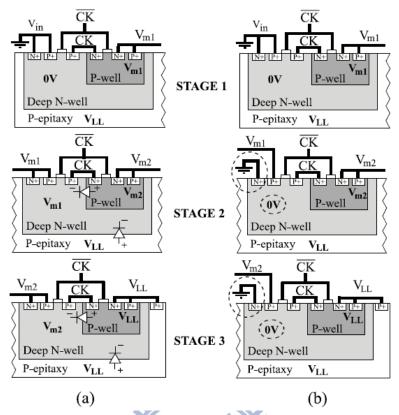

Fig.2.10 is adopted from [9]. In this work, it use three stage charge pump. If the deep N-wells connect to source of PMOS, there is some P-N junctions which shown as Fig.2.10 (a). These junctions may have leakage during circuit operation, which may degrade the efficiency of charge pump or may cause latch-up issues. So, the deep N-wells are connect to ground to prevent this, which depicts as Fig.2.10 (b). However, the PMOS switches may have body effect, which may increase the conduction loss of charge pump.

Fig. 2.9 Cross-couple negative charge pump.

Fig. 2.10 (a) The deep N-well tied to source of PMOS. (b) The deep N-well tied to ground. [9]

#### 2.3.3 4-phase Negative Charge Pump with NMOS Charge Transfer Switches

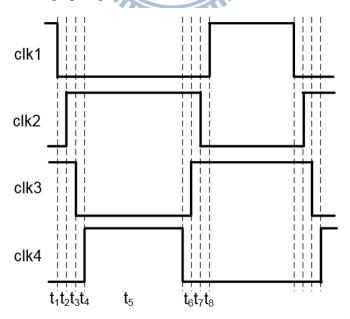

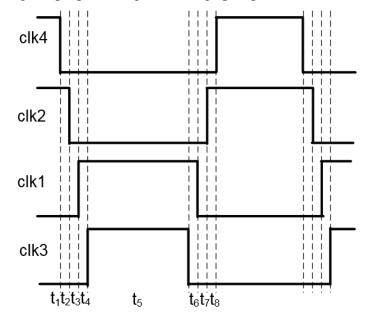

In triple well process, the PMOS switches of negative charge pump may have body effect, to prevent this, the circuit which depict as Fig.2.11 had been proposed [10]. The charge pump circuit consists of NMOS transfer switches and pumping capacitors. The bulk of NMOS switches can be tied to source without leakage of P-N junctions and latch up issues. Compare to the all PMOS negative charge pump, the last stage doesn't use diode connected MOS, which may not cause forward voltage drop. The clock control scheme is similar to all PMOS negative charge pump. This charge pump use 4-phase clock scheme to control NMOS transfer switches, the 4-phase clock is shown as Fig.2.12.

Here, we separate 4-phase clock to eight intervals. At the interval  $t_1$ , the voltage of node 1 is GND and the voltage of node 2 is -2 $V_{DD}$ , where  $V_{DD}$  is the voltage swing of

clock. The voltage of node 3 is  $V_{DD}$  and the voltage of node 4 is  $-2V_{DD}$ . Mn1 and Mb2 are turned on, and Mb1 and Mn2 are turned off.

At the interval t<sub>2</sub>, the voltage of clk1 is dropped to low (GND). The voltage of node 3 is dropped to GND to cut off Mn1. The voltage of node 1, node 2 and node 4 are the same as the voltage at interval t<sub>1</sub>. Mb1 and Mn2 keep being turned off and Mb1 keep being turned on.

At the interval  $t_3$ , the voltage of clk2 is rose to high  $(V_{DD})$  to turn on Mb1. The voltage of node 2 is rose to  $-V_{DD}$  and the voltage of node 4 is rose to  $-V_{DD}$  as well. The voltage of node 1 and node 3 are the same as the voltage at time interval  $t_2$ . Mn1 and Mn2 keep being turned off to prevent leakage current from the front stage and Mb2 keep being turned on.

At the interval t<sub>4</sub>, the voltage of clk3 is dropped to low (GND). The voltage of node 1 is dropped to -V<sub>DD</sub> to cut off Mb2 and the voltage of node 3 is dropped to -V<sub>DD</sub> as well. The voltage of node 2 and node 4 are the same as the voltage at time interval t<sub>3</sub>. Mn1 and Mn2 keep being turned off and Mb1 keep being turn on to cut off Mn1.

At the interval t<sub>5</sub>, the voltage of clk4 is rose to high (V<sub>DD</sub>). The voltage of node 4 is rose to GND to turn on Mn2, and the voltage of node 1 and node 2 become -V<sub>DD</sub>. The voltage of node 3 keep -V<sub>DD</sub>. Mn1 and Mb2 keep being turned off and Mb1 keep being turn on to cut off Mn1.

At the interval t<sub>6</sub>, the voltage of clk4 is dropped to low (GND). The voltage of node 4 is dropped to -VDD to cut off Mn1. The voltage of node1, node 2 and node 3 are the same as the voltage at time interval t<sub>5</sub>. Mn1 and Mb2 keep being turned off and Mb1 keep being turn on to cut off Mn1.

At the interval  $t_7$ , the voltage of clk3 is rose to high ( $V_{DD}$ ). The voltage of node 1 is rose to GND to turn on Mb2 and the voltage of node 3 is rose to GND as well. The

voltage of node 2 and node 4 are the same as the voltage at time interval t<sub>6</sub>. Mn1 and Mn2 keep being turned off and Mb1 keep being turned on.

At the interval t<sub>8</sub>, the voltage of clk2 is dropped to low (GND) to turn off Mb1. The voltage of node 2 and node 4 are dropped to -2V<sub>DD</sub>. The voltage of node1 and node 3 are the same as the voltage at time interval t<sub>7</sub>. Mn1 and Mn2 keep being turned off to prevent leakage and Mb1 keep being turned on.

By these operations, the output voltage can be pumped to negative high voltage without body effect. The advantage of this pump is no leakage current by 4-phase scheme. However, the maximum voltage stress on NMOS is as high as 2VDD, which may cause gate-reliability issues in low voltage CMOS process.

Fig. 2.11 Negative charge pump with NMOS switches.

Fig. 2.12 4-phase clock control scheme of the negative charge pump with NMOS switches.

### Chapter 3

# Design of Positive Charge Pump Regulator with Low Input Peak Current

#### 3.1 Design of Positive Charge Pump Regulator

#### 3.1.1 Circuit Block Diagram of Proposed Positive Charge Pump Regulator

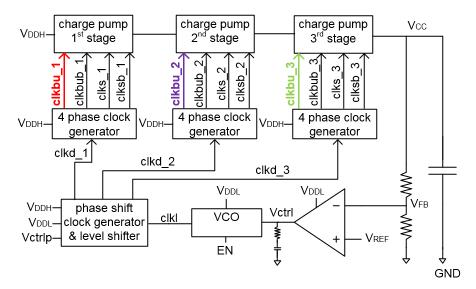

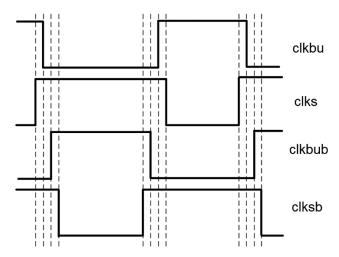

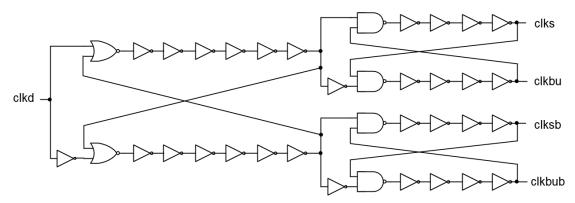

The proposed charge pump regulator consists of error amplifier, phase shift clock generator, level shifter, 4-phase clock generator and 3-stage charge pump, as shown in Fig. 3.1. For the charge pump, the higher output voltage is, the higher clock frequency should be. Therefore, the proposed charge pump used the PFM feedback to generate regulated output voltage V<sub>CC</sub> [11]~[12]. The PFM feedback consist of voltage divider, error amplifier and voltage control oscillator (VCO). The PFM feedback consists of voltage divider, error amplifier and voltage control oscillator (VCO). The output voltage (V<sub>ctrl</sub>) of amplifier is adjusted by the voltage difference between V<sub>FB</sub> and V<sub>REF</sub>. The clock frequency of clkl is controlled by V<sub>ctrl</sub>. When V<sub>CC</sub> is lower than 11V, controlled voltage ( $V_{ctrl}$ ) become higher and the frequency of clkl arise until  $V_{CC} = 11V$ . In contrast, when V<sub>CC</sub> is higher than 11V, controlled voltage (V<sub>ctrl</sub>) become lower and the frequency of clkl become slower until  $V_{CC} = 11V$ . The 4-phase clock generator provides the charge pump with the adaptive control signals. The phase shift clock generator can generate clkd\_1, clkd\_2 and clkd\_3. When control signal V<sub>ctrlp</sub> is logic low, the clock waveforms of clkd\_1, clkd\_2 and clkd\_3 depict as Fig. 3.2 (a). Otherwise, when control signal V<sub>ctrlp</sub> is logic high, the clock waveforms of clkd\_1, clkd\_2 and clkd\_3 depict as Fig. 3.2 (b). The peak current from V<sub>DDH</sub> can be reduced by the three phase shift clock waveforms. Lower peak current from V<sub>DDH</sub> may improve transient

response of the dc regulator which provide  $V_{DDH}$  to charge pump, and can inject less noise into other circuit in biomedical SoC [13].

Fig. 3.1 The proposed charge pump regulator consists of error amplifier, phase shift clock generator, level shifter, 4 phase clock generator, and 3 stage charge pump.

Fig. 3.2 (a) The clock waveform of clkd\_1, clkd\_2, and clkd\_3 when V<sub>ctrlp</sub> is logic high. (b) The clock waveform of clkd\_1, clkd\_2, and clkd\_3 when V<sub>ctrlp</sub> is logic low.

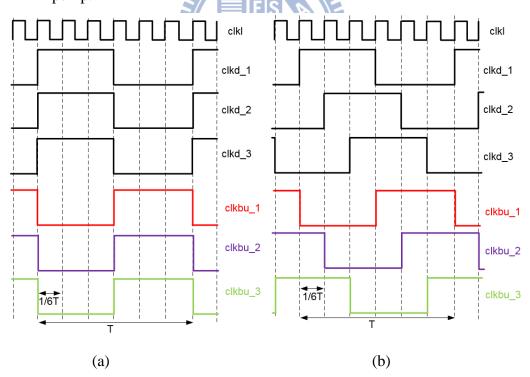

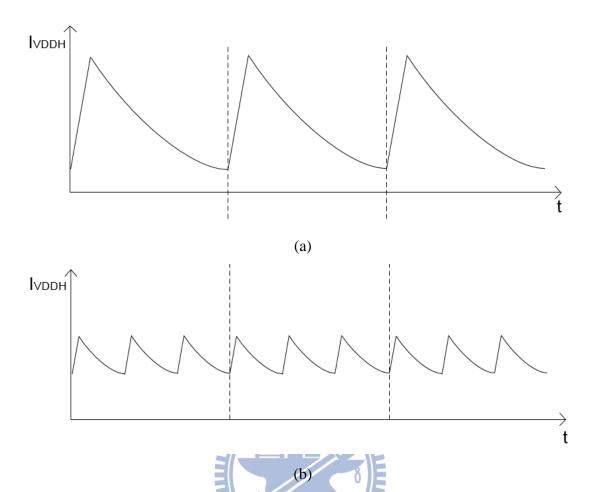

Fig. 3.3 depicts a 4-phase cross couple charge pump. It shows the current flow from  $V_{DDH}$  when clock signal clkbub is high. Fig. 3.4 (a) depicts the waveform of current flow when control signal  $V_{ctrlp}$  is low. Because MOS like resistance when it is in triode region, the waveform of current flow likes RC discharge circuit. Fig. 3.4 (b) depicts the waveform of current flow when control signal  $V_{ctrlp}$  is high. The peak current in Fig. 3.4 (b) is lower than the peak current in Fig. 3.4 (a).

Fig. 3.3 Current flow when clkbub is V<sub>DDH</sub>.

Fig. 3.4 (a) Current flow from  $V_{DDH}$  when  $V_{ctrlp}$  logic low. (b) Current flow from  $V_{DDH}$  when  $V_{ctrlp}$  is logic high.

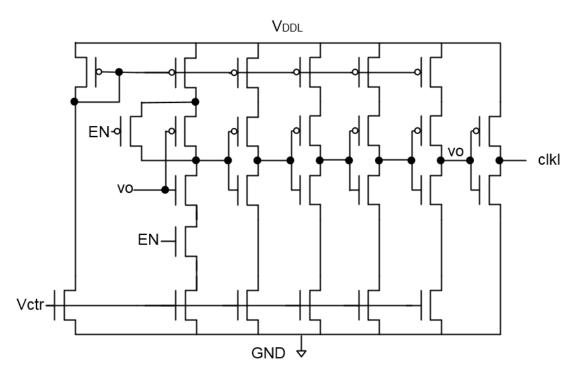

#### 3.1.2 Charge Pump Circuit and 4-phase Clock Generator

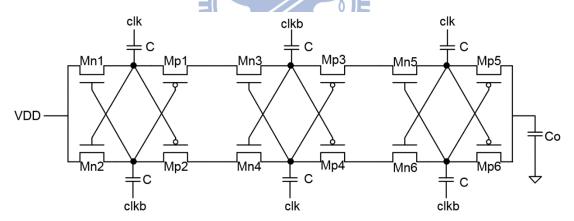

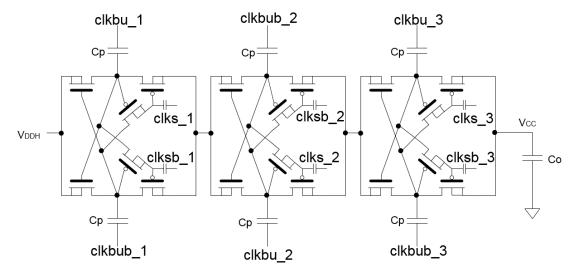

Fig. 3.5 shows the 3-stage charge pump. It can output high voltage level without the issues of electrical overstress and gate-oxide reliability [14]. Compare to conventional two phase cross-couple charge pump, this 4-phase cross-couple charge pump can reduce the return-back leakage current. Therefore, this pump has higher efficiency and higher pumping gain than conventional charge pump. Fig. 3.6 shows the 4-phase clock waveforms and Fig. 3.7 shows the circuit of 4-phase clock generator.

Fig. 3.5 The circuit of 3-stage charge pump.

Fig. 3.6 4-phase clock waveforms which is generated from 4-phase clock generator.

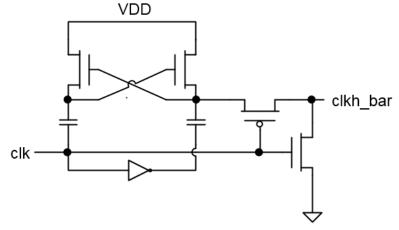

Fig. 3.7 4-phase clock generator.

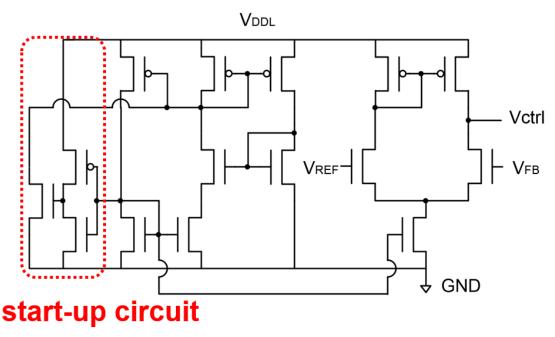

#### 3.1.3 Bandgap Reference, Error Amplifier, VCO and Phase Shift Clock Generator

Fig. 3.8 shows the bandgap reference [15], which generate reference voltage  $V_{\text{REF}}$ to error amplifier. Fig. 3.9 shows the error amplifier [16]. Fig. 3.10 shows the current starve voltage control ring oscillator. The first stage of VCO is nand gate which provide the initial condition for VCO.

Fig. 3.9 Circuit diagram of error amplifier.

Fig. 3.10 Circuit diagram of current starve voltage control ring oscillator.

Fig. 3.11 shows the circuit diagram of phase shift clock generator and level shifter. The level shifter can transfer 1.8V clock signal to 3.3V clock signal. When control signal  $V_{ctrlp}=1$ , the output clock signal (clkd\_1, clkd\_2 and clkd\_3) have phase shift like Fig. 3.2. When control signal  $V_{ctrlp}=0$ , the output clock signal (clkd\_1, clkd\_2 and clkd\_3) don't have phase shift. It means that the waveform of clkd\_1, clkd\_2 and clkd\_3 are the same.

Fig. 3.11 Circuit diagram of phase shift clock generator and level shifter.

#### 3.2 Simulation Results

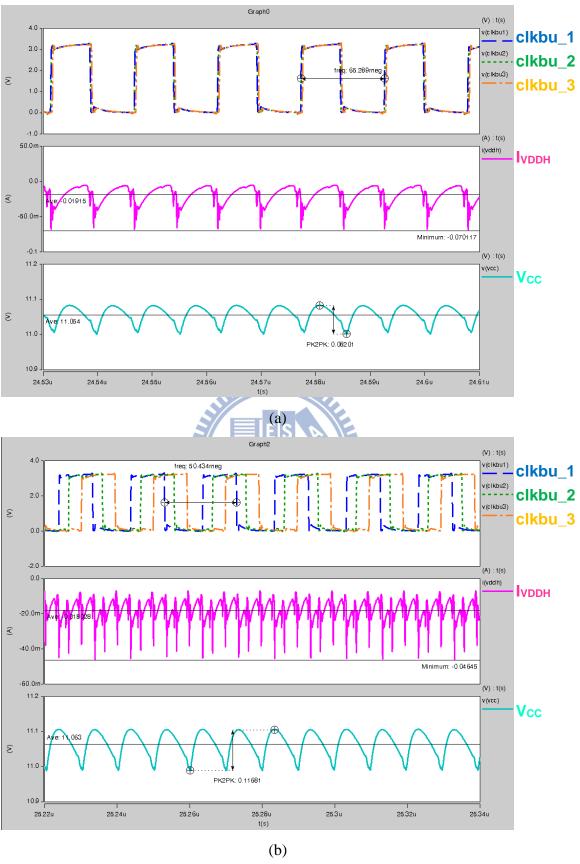

This work have been simulated in HSPICE with TSMC 0.18- $\mu$ m 1.8-V/3.3-V CMOS process. Fig. 3.12 (a) depicts the simulation result of charge pump when V<sub>ctrlp</sub>=0 and I<sub>load</sub>=3.5mA. The clock signals (clkbu\_1, clkbu\_2, and clkbu\_3) charge pump don't have phase shift. The pumping frequency is 65.28MHz. The input peak current (I<sub>VDDH(max)</sub>) is 70mA and the average output voltage (V<sub>CC</sub>) is about 11.054V. The efficiency of charge pump is 61.5%.

Fig. 3.12 (b) depicts the simulation result of charge pump when  $V_{ctrlp}=1$  and  $I_{load}=3.5 mA$ . The clock signals (clkbu\_1, clkbu\_2, and clkbu\_3) charge pump have phase shift. The pumping frequency is 50.43MHz. The input peak current ( $I_{VDDH(max)}$ ) is 46mA and the average output voltage ( $V_{CC}$ ) is about 11.063V. The efficiency of charge pump is 65.68%. As the simulation result, we can reduce the input peak current with phase shift clock control.

Fig. 3.12 Simulation results of charge pump when (a)  $V_{ctrlp}=0$  and  $I_{load}=3.5 mA$  (b)  $V_{ctrlp}=1$  and  $I_{load}=3.5 mA$ .

### 3.3 Measurement Results

This work have been fabricated in TSMC 0.18-µm 1.8-V/3.3-V CMOS process. The charge pump aims to output voltage 11V and maximum current 3.5mA. The pumping capacitors (C<sub>P</sub>) of charge pump are 50pF and the output capacitor (C<sub>O</sub>) is 100pF. All capacitors of the positive charge pump are fully on-chip. Fig. 3.13 depicts the die photo of test chip, which includes the 3-stage charge pump and 4-phase clock generator (A), output capacitor of charge pump (B), and bandgap reference, VCO, error amplifier and phase shift clock generator (C). The test chip area is 1.87 x 1.48mm<sup>2</sup>.

Fig. 3.13 Die photograph with A: 3-stage charge pump and 4-phase clock generator, B: output capacitor of charge pump, and C: bandgap reference, VCO, error amplifier and phase shift clock generator.

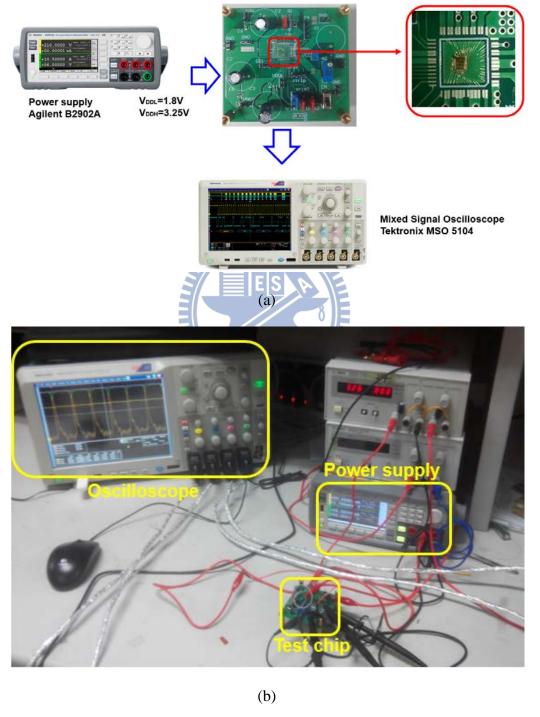

Fig. 3.14 (a) shows the measurement setup. Agilent B2902A is used to provide voltage  $1.8V\ V_{DDL}$  and  $3.25V\ V_{DDH}$ , which is also used to measurement power consumption of the charge pump. Tektronix MSO 5104 is used to observe the waveforms of the charge pump. Fig. 3.14 (b) shows the measurement environment.

Fig. 3.14 (a) Measurement setup of power supply, oscilloscope and test chip. (b) Measurement environment.

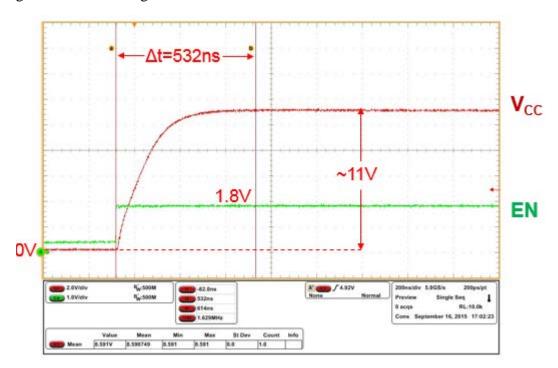

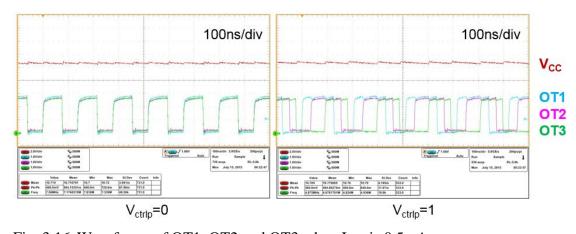

Fig. 3.15 depicts the measurement result of power on time at I<sub>load</sub> is 3.5mA and V<sub>ctrlp</sub> is logic 1, which is about 532nsec. Fig. 3.16 depicts the waveforms to check the phase shift clock generator function. V<sub>ctrlp</sub>=0 means the clock signal of each stage doesn't have phase shift. V<sub>ctrlp</sub>=1 means the clock signals of each stage has phase shift. The signals OT1, OT2 and OT3 are generated by clkd\_1, clkd\_2 and clkd\_3 via some buffers respectively. As the measurement result, the function of phase shift clock generator is working.

Fig. 3.15 The measurement result of power on time.

Fig. 3.16 Waveforms of OT1, OT2 and OT3 when  $I_{load}$  is 0.5mA.

Fig. 3.17 depicts the measurement result of  $V_{CC}$  when  $I_{load}$  is 3.5mA. The efficiency is calculated by Eq. (3.1), where  $P_{VCC}$  is the power of  $V_{CC}$ .

$$Efficiency = \frac{P_{VCC}}{P_{VDDH} + P_{VDDL}}$$

(3.1)

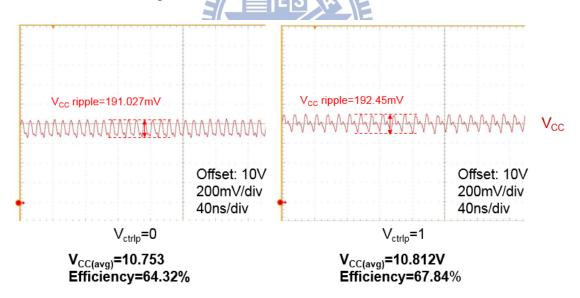

When  $V_{ctrlp}$  is logic low ( $V_{DDL}$ ), the average voltage of  $V_{CC}$  is 10.753V. The efficiency of charge pump is 64.32%. The ripple of  $V_{CC}$  is about 191.027mV.

When  $V_{ctrlp}$  is logic high ( $V_{DDL}$ ), the average voltage of  $V_{CC}$  is 10.812V. The efficiency of charge pump is 67.84% when  $I_{load}$  is 3.5mA. The ripple of  $V_{CC}$  is about 192.54mV.

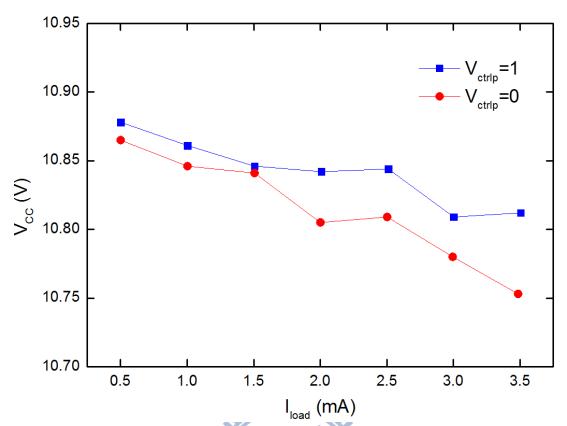

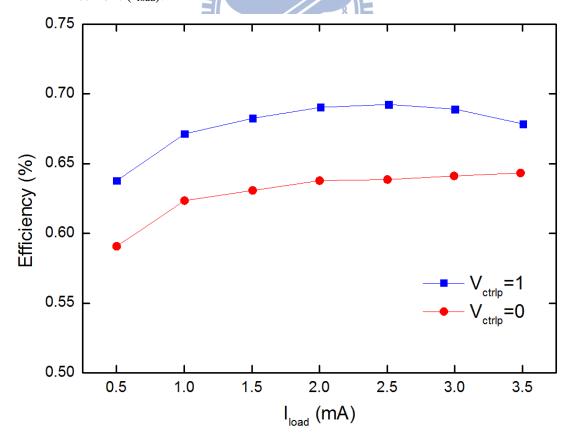

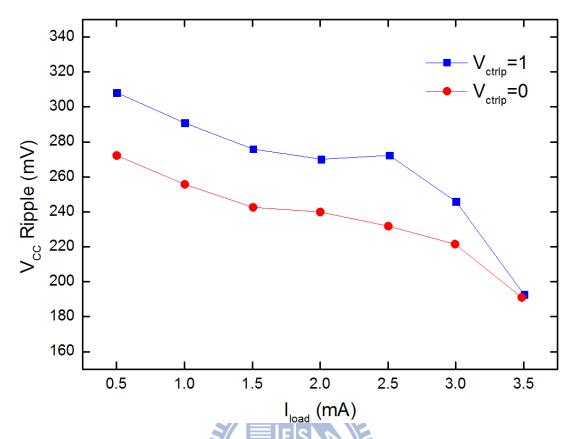

Fig. 3.18 shows the measurement result of output voltage ( $V_{CC}$ ) versus different loading current ( $I_{load}$ ). Fig. 3.19 shows the measurement result of efficiency versus different loading current ( $I_{load}$ ). Fig. 3.20 shows the measurement result of output ripple versus different loading current ( $I_{load}$ ).

Fig. 3.17 The measurement result of output voltage (V<sub>CC</sub>) when I<sub>load</sub> is 3.5mA

Fig. 3.18 The measurement result of output voltage ( $V_{CC}$ ) versus different loading current ( $I_{load}$ ).

Fig. 3.19 The measurement result of efficiency versus different loading current (I<sub>load</sub>).

Fig. 3.20 The measurement result of output ripple versus different loading current (I<sub>load</sub>).

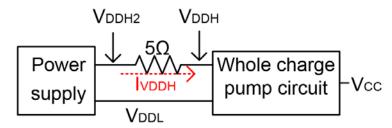

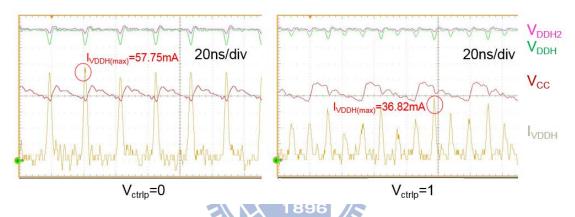

In order to measurement input peak current ( $I_{VDDH(max)}$ ) from  $V_{DDH}$ , we add a 5  $\Omega$  resistance between node  $V_{DDH2}$  and  $V_{DDH2}$  and measure the voltage difference between  $V_{DDH2}$  and  $V_{DDH}$ . Fig 3.21 shows the measurement setup. Fig. 3.22 depicts the measurement result of input current ( $I_{VDDH}$ ) from  $V_{DDH}$  when  $I_{load}$  is 1.5mA. When  $V_{ctrlp}$  is logic low (GND), the maximum input peak current ( $I_{VDDH(max)}$ ) is 57.7mA. When  $V_{ctrlp}$  is logic high ( $V_{DDL}$ ), the maximum input peak current ( $I_{VDDH(max)}$ ) is 36.8mA.

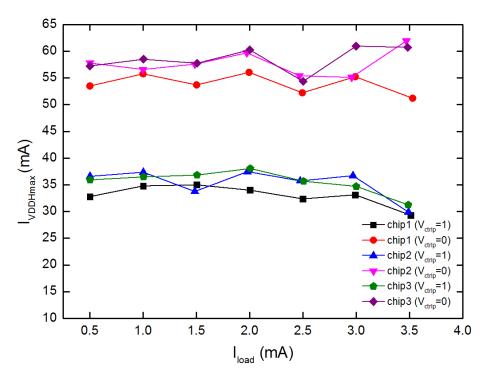

Fig. 3.23 depicts the measurement result of input current ( $I_{VDDH}$ ) from  $V_{DDH}$  when  $I_{load}$  is 3.5mA. When  $V_{ctrlp}$  is logic low (GND), the maximum input peak current ( $I_{VDDHmax}$ ) is 60.7mA. When  $V_{ctrlp}$  is logic high ( $V_{DDL}$ ), the maximum input peak current ( $I_{VDDHmax}$ ) is 31.2mA. Fig 3.24 shows the measurement result of  $I_{VDDH(max)}$  versus different loading current in three different chips. In the measurement result, the maximum input peak current can be reduced by applying phase shift clock (clkd\_1,

clkd\_2 and clkd\_3) to the charge pump. Table 3.1 is the comparison of post-simulation and measurement.

Fig. 3.21 The measurement setup for measuring I<sub>VDDH</sub>.

Fig. 3.22 The measurement result of input current ( $I_{VDDH}$ ) from  $V_{DDH}$  when  $I_{load}$  is 1.5mA.

Fig. 3.23 The measurement result of input current ( $I_{VDDH}$ ) from  $V_{DDH}$  when  $I_{load}$  is 3.5mA.

Fig. 3.24 The measurement result of  $I_{\text{VDDHmax}}$  in three different chip.

Table. 3.1 Comparison of post-simulation and measurement.

|                                                                                                     |       | Post-layout simulation (TT)        | Measurement       |  |

|-----------------------------------------------------------------------------------------------------|-------|------------------------------------|-------------------|--|

| Power supply<br>V <sub>DDL</sub> / V <sub>DDH</sub>                                                 |       | 1.8V / 3.25V                       | 1.8V / 3.25V      |  |

| I <sub>VDDHmax</sub> @ I <sub>load</sub> = 3.5mA<br>V <sub>ctrlp</sub> = 0 / V <sub>ctrlp</sub> = 1 |       | 70.11mA / 46.5mA                   | 60.74mA / 31.25mA |  |

| V <sub>CC</sub> /<br>Efficiency<br>(V <sub>ctrip</sub> = 1)                                         | 0.5mA | 11.098V / 66.283%                  | 10.878V / 63.778% |  |

|                                                                                                     | 1mA   | 11.089V / 68.578%                  | 10.861V / 67.131% |  |

|                                                                                                     | 1.5mA | 11.085V / 69.175%                  | 10.846V / 68.246% |  |

|                                                                                                     | 2mA   | 11.081V / 69.161%                  | 10.842V / 69.04%  |  |

|                                                                                                     | 2.5mA | 11.076V / 68.683%                  | 10.844V / 69.245% |  |

|                                                                                                     | 3mA   | 11.069V / 67.703%                  | 10.809V / 68.904% |  |

|                                                                                                     | 3.5mA | 11.067V / 65.688%                  | 10.812V / 67.847% |  |

| Process                                                                                             |       | TSMC 0.18µm 1.8V/3.3V CMOS Process |                   |  |

# 3.4 Application on Biomedical Stimulation Circuit

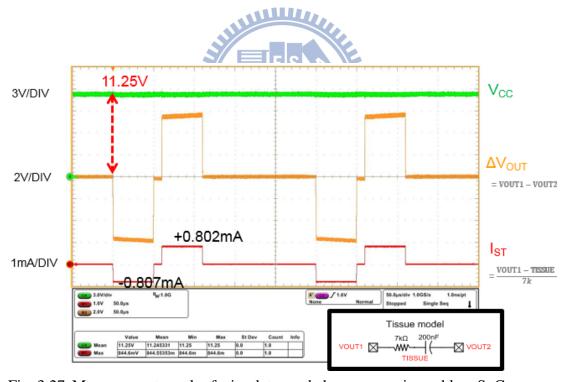

In this work, we had used charge pump circuit on cochlear stimulation circuit. Fig. 3.25 depicts the circuit block diagram of cochlear stimulation circuit. All chips had been fabricated in TSMC 0.18-µm 1.8-V/3.3V CMOS process. The charge pump is used in implanted part to generate high voltage to provide stimulator. By measurement, the charge pump can regulate at high voltage and the stimulator can work successfully. The die photo of implanted part is shown as Fig. 3.26, which include A: stimulator driver, B: DSP, C: positive charge pump circuit, D: demodulator and back telemetry, and E: rectifier and regulator. Fig. 3.27 is the measurement result of stimulator and charge pump in cochlear SoC.

Fig. 3.25 Block diagram of cochlear SoC.

Fig. 3.26 Die photograph with A: stimulator driver, B: DSP, C: positive charge pump circuit, D: demodulator and back telemetry, and E: rectifier and regulator.

Fig. 3.27 Measurement result of stimulator and charge pump in cochlear SoC.

### 3.5 Summary

Design of a positive charge pump regulator for biomedical implant is investigated and verified in this chapter. The circuit design have been fabricated in TSMC 0.18-μm 1.8-V/3.3V CMOS process. The proposed design can output 10.8V high voltage and maximum output current 3.5mA without the issues of electrical overstress and gate-oxide reliability. The 4-phase cross couple positive charge pump is used for reducing the return-back leakage current. Each stage of charge pump has its own clock signal which has phase shift different from each other. By the measurement, the clock control scheme can reduce the maximum peak current which flow from power supply V<sub>DDH</sub>. The function of this charge pump design have been success fully verified in silicon chip, which can successfully provide high voltage to the output load.

# **Chapter 4**

# Design of Negative Charge Pump Regulator with Low Input Peak Current

### 4.1 Design of Negative Charge Pump Regulator

#### 4.1.1 Circuit Block Diagram of Proposed Charge Pump Regulator

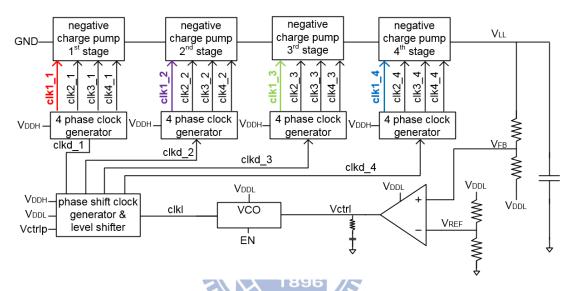

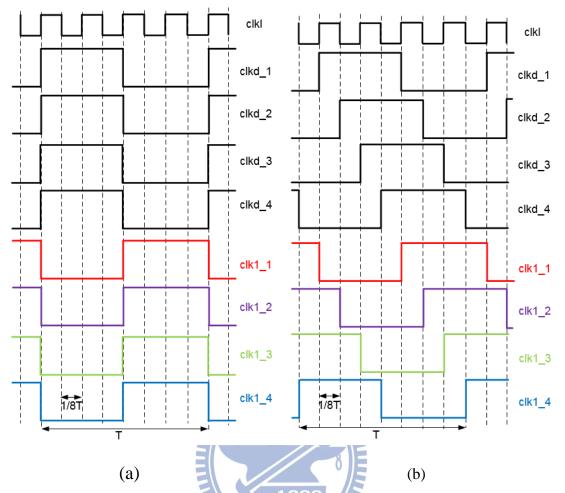

The proposed negative charge pump regulator is composed of error amplifier, bandgap reference circuit, voltage-controlled oscillator (VCO), phase shift clock generator, level shifter, 4-phase clock generator and 4-stage negative charge pump, as shown in Fig. 4.1. For the charge pump, when output current become higher, the clock frequency should be higher to keep the voltage level of output voltage. Therefore, the proposed charge pump used the PFM feedback to generate regulated output voltage  $V_{\rm LL}$ . The PFM feedback consist of voltage divider, error amplifier and voltage control oscillator (VCO). When the control signal EN of VCO is logic high, VCO start working and charge pump generate negative high voltage V<sub>LL</sub>. When the control signal EN of VCO is logic low, VCO do not work and the output voltage V<sub>LL</sub> of charge pump is zero. The output voltage (V<sub>ctrl</sub>) of amplifier is adjusted by the voltage difference between V<sub>FB</sub> and V<sub>REF</sub>. The clock frequency of clkl is controlled by V<sub>ctrl</sub>. When V<sub>LL</sub> is higher than -10V, controlled voltage ( $V_{ctrl}$ ) become higher and the frequency of clkl arise until  $V_{LL}$ = -10V. In contrast, when  $V_{LL}$  is lower than -10V, controlled voltage ( $V_{ctrl}$ ) become lower and the frequency of clkl become slower until  $V_{LL} = -10V$ . The 4-phase clock generator provides the charge pump with the adaptive control signal. The phase shift clock generator can generate clkd\_1, clkd\_2, clkd\_3 and clkd\_4. When control signal V<sub>ctrlp</sub> is logic 0, the clock waveforms of clkd\_1, clkd\_2, clkd\_3 and clkd\_4 depict as

Fig. 4.2 (a). Otherwise, when control signal  $V_{ctrlp}$  is logic 1, the clock waveforms of clkd\_1, clkd\_2, clkd\_3 and clkd\_4 depict as Fig. 4.2 (b). The same as the positive charge pump in chapter 3, the peak current from  $V_{DDH}$  can be reduced by the three phase shift clock waveform. Lower peak current from  $V_{DDH}$  may improve transient response of the dc regulator which provide  $V_{DDH}$  to charge pump.

Fig. 4.1 Block diagram of negative charge pump

Fig. 4.2 (a)The clock waveform of clkd\_1, clkd\_2, clkd\_3 and clkd\_4 when V<sub>ctrlp</sub> is low (0). (b) The clock waveform of clkd\_1, clkd\_2, clkd\_3 and clkd\_4 when V<sub>ctrlp</sub> is high (1).

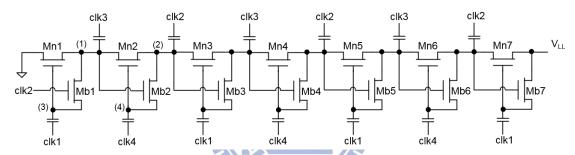

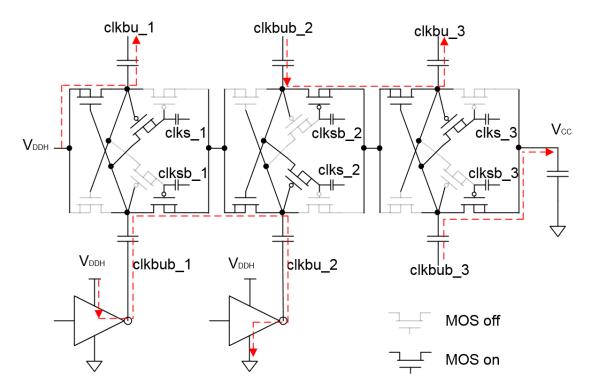

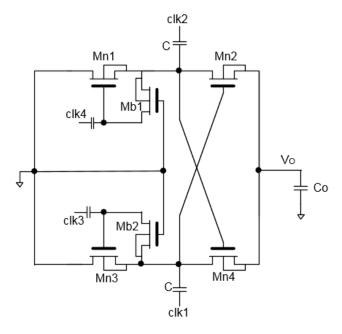

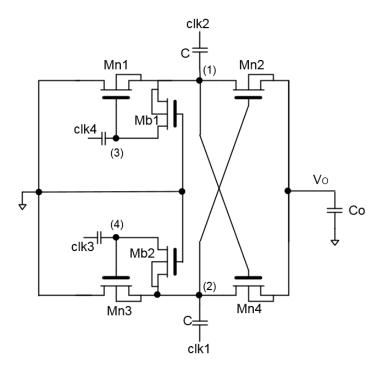

### 4.1.2 Negative Charge Pump and 4-phase Clock Generator

Fig. 4.3 shows the 4-phase cross couple negative charge pump circuit which is modified from [17]. The 4-phase cross-couple negative charge pump can reduce the output ripple and has no gate-oxide reliability issues. The negative charge pump consists of NMOS switches with deep N-Well which can isolate P-well of each NMOS from P-substrate. The bulk of each NMOS switch is connected to the source of NMOS. In this way, the NMOS switches don't have body effect and substrate leakage. All NMOS are 3.3V IO devices in 0.18-um 1.8-V/3.3-V CMOS process. Fig. 4.4 shows the

4-phase clock waveform (clk1, clk2, clk3 and clk4) and Fig. 4.5 shows the circuit of 4-phase clock generator.

Here, we separate 4-phase clock to eight intervals. At the interval  $t_1$ , the voltage of node 1 is GND and the voltage of node 2 is - $V_{DD}$ . The voltage of node 3 is  $V_{DD}$ - $V_t$  and the voltage of node 4 is - $V_{DD}$ , where  $V_{DD}$  is the voltage swing of clock and  $V_t$  is the threshold voltage of NMOS. Mb1, Mn2 and Mn3 are turned off and Mn1, Mb2 and Mn4 are turned on. The voltage of  $V_0$  become - $V_{DD}$  through Mn4.

At the interval  $t_2$ , the voltage of clk4 is dropped to low (GND). The voltage of node 3 is dropped to  $-V_t$  to cut off Mn1. The voltage of node1, node 2 and node 4 are the same as the voltage at interval  $t_1$ . At the same time, Mb1, Mn2 and Mn3 keep being turned off and Mb2 and Mn4 keep being turned on.

At the interval  $t_3$ , the voltage of clk2 is dropped to low (GND). The voltage of node 1 is dropped to  $-V_{DD}$  to turn on Mb1 and to turn off Mn4, and the voltage of node 3 is dropped to  $-V_{DD}$  through Mb1. The voltage of node 2 and node 4 keep the same as the voltage at interval  $t_2$ . At the same time, Mn1, Mn2 and Mn3 keep being turned off and Mb2 keeps being turned on.

At the interval  $t_4$ , the voltage of clk1 is rose to high ( $V_{DD}$ ). The voltage of node 2 is rose to GND to turn on Mn2 and to cut off Mb2, and the voltage of node 4 is rose to -  $V_t$  as the voltage of node 2 was rose. The voltage of  $V_0$  become - $V_{DD}$  through Mn2, and the voltage of node 1 and node 3 are the same as the voltage at time interval  $t_3$ . Mn1 and Mn2 keep being turned off and Mb1 keep being turned on to cut off Mn1.

At the interval  $t_5$ , the voltage of clk3 is rose to high ( $V_{DD}$ ). The voltage of node 4 is rose to  $V_{DD}$ - $V_t$  to turn on Mn3, and the voltage of node 2 is the same as GND. The voltage of node 1 and node 3 keep - $V_{DD}$ . Mn1, Mb2 and Mn4 keep being turned off and Mb1 and Mn2 keep being turned on.

At the interval t<sub>6</sub>, the voltage of clk3 is dropped to low (GND). The voltage of node 4 is dropped to -V<sub>t</sub> to cut off Mn3. The voltage of node1, node 2 and node 3 are the same as the voltage at time interval t<sub>5</sub>. Mn1, Mb2 and Mn4 keep being turned off and Mb1 and Mn2 keep being turned on.

At the interval  $t_7$ , the voltage of clk1 is dropped to low (GND). The voltage of node 2 is dropped to  $-V_{DD}$  to cut off Mn2 and to turn on Mb1, and the voltage of node 3 is dropped to  $-V_{DD}$  as well. The voltage of node 2 and node 4 are the same as the voltage at time interval  $t_6$ . Mn1, Mn3 and Mn4 keep being turned off and Mb2 keep being turned on.

At the interval t<sub>8</sub>, the voltage of clk2 is rose to high (V<sub>DD</sub>) to turn on Mn4 and Mb1 is turned off at the same time. The voltage of node 3 is rose to -V<sub>t</sub>. The voltage of V<sub>0</sub> become -V<sub>DD</sub> through Mn4, and the voltage of node 2 and node 3 are the same as the voltage at time interval t<sub>7</sub>. Mn1, Mn2 and Mn3 keep being turned off and Mb2 keep being turned on.

By these operations, the output voltage can be pumped to negative high voltage without body effect. Because the NMOS switches have been cut off before the voltage of node is changed, there is no return-back leakage current. Moreover, this negative charge pump can operate without gate-oxide reliability issues.

Fig. 4.3 One stage of proposed negative charge pump.

Fig. 4.4 4-phase clock waveforms of clk1, clk2, clk3 and clk4.

Fig. 4.5 4-phase clock generator.

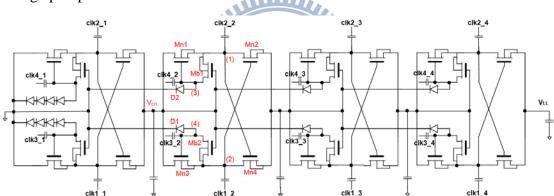

Fig. 4.6 depicts the 4-stage cross-couple negative charge pump with some diodes which is used for start-up protection. When start-up, if both  $clk1_2$  and  $clk3_2$  are high, MN1 will be turned on and the voltage of node 2 will be equal to the voltage of  $V_{01}$ . If the voltage of node 4  $(V_4)$  is much higher the voltage of node 2  $(V_2)$  which is express as Eq. (4-1), Mb2 will not be turned on all the time.

$$V_4 - V_{DD} - V_2 > V_{tn} \tag{4-1}$$

In this condition, the voltage of node 2 will be much lower and the voltage of node 4 will keep high after some clock cycles, which may cause overstress between node 2 and node 4 and damage the gate oxide of NMOS. So, we add some diode to discharge the node voltage during start-up. Fig. 4.7 depicts the connection of deep N-well in the charge pump circuit.

Fig. 4.6 4-stage cross couple negative charge pump.

Fig. 4.7 Connection of deep N-well in the charge pump circuit.

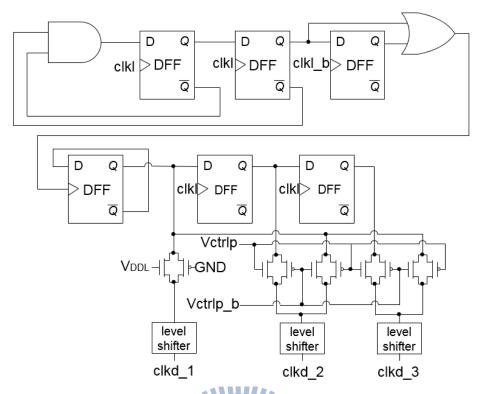

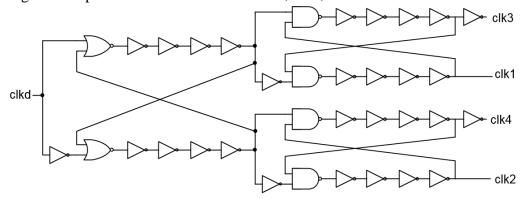

### 4.1.3 Error Amplifier, VCO and Phase Shift Clock Generator

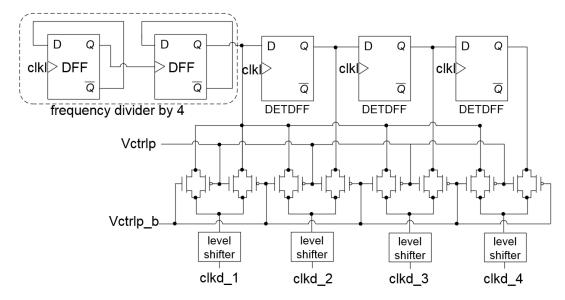

The error amplifier and VCO are the same as that are used in chapter 3. Fig. 4.8 shows the circuit diagram of phase shift clock generator, which consists of frequency divider, double edge trigger D flip-flop (DETFF), level shifter and some transmission gates. The frequency divider can divide frequency of clk by 4 and output clock to DETDFF. The transmission gates are used to control if the phase of clkd\_1, clkd\_2, clkd\_3 and clkd\_4 has phase shift different from each other. The level shifter can transfer 1.8V clock signal to 3.3V clock signal. When control signal V<sub>ctrlp</sub> is logic 0, the output clock signals (clkd\_1, clkd\_2, clkd\_3 and clkd\_4) are the same phase like Fig. 4.2 (a). When control signal V<sub>ctrlp</sub> is logic 1, the output clock signals (clkd\_1, clkd\_2, clkd\_3 and clkd\_4) have phase shift like Fig. 4.2 (b).

Fig. 4.8 Circuit of phase shift clock generator.

### 4.2 Simulation Results

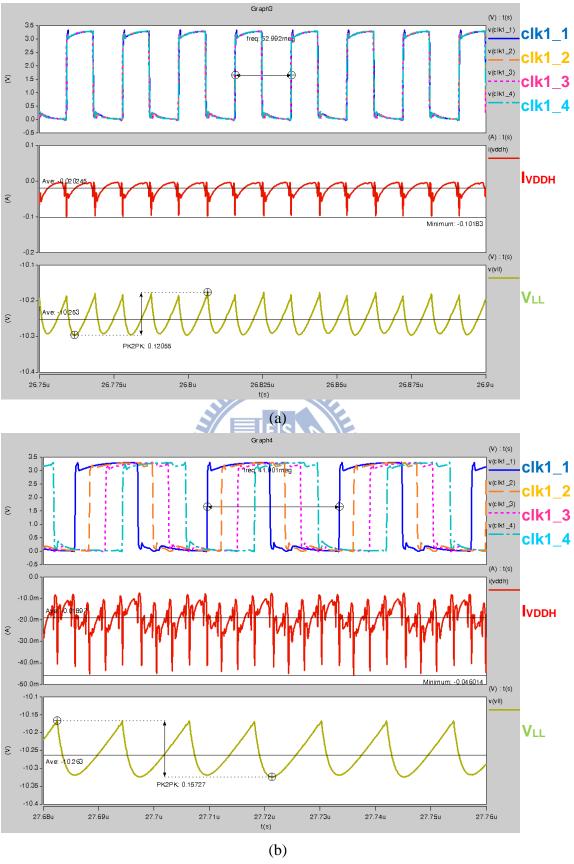

This work have been simulated in HSPICE with TSMC 0.18- $\mu$ m 1.8-V/3.3-V CMOS process. Fig. 4.9 (a) depicts the simulation result of charge pump when  $V_{ctrlp}=0$  and  $I_{load}=3.5$ mA. The clock signals (clk\_1, clk\_2, clk1\_3, and clk1\_4) charge pump don't have phase shift. The pumping frequency is 53MHz. The input peak current ( $I_{VDDH(max)}$ ) is 101.83mA and the average output voltage ( $V_{CC}$ ) is about -10.253V. The efficiency of charge pump is 53.31%.

Fig. 4.9 (b) depicts the simulation result of charge pump when  $V_{ctrlp}=1$  and  $I_{load}=3.5 mA$ . The clock signals (clk\_1, clk\_2, clk1\_3, and clk1\_4) charge pump have phase shift. The pumping frequency is 41.9MHz. The input peak current ( $I_{VDDH(max)}$ ) is 46mA and the average output voltage ( $V_{CC}$ ) is about -10.263V. The efficiency of charge pump is 54.15%. As the simulation result, we can reduce the input peak current with phase shift clock control.

Fig. 4.9 Simulation result of charge pump when (a)  $V_{ctrlp}$ =0 and  $I_{load}$ =3.5mA (b)  $V_{ctrlp}$ =1 and  $I_{load}$ =3.5mA.

### **4.3 Measurement Results**

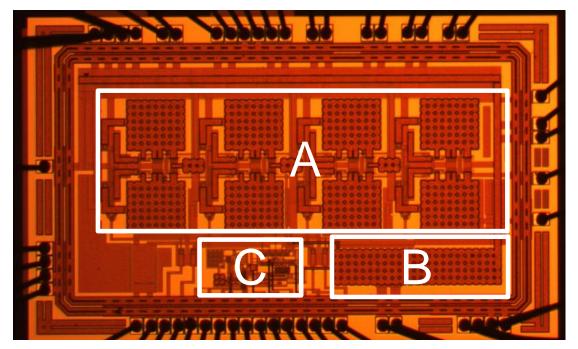

This work have been simulated by HSPICE and have been fabricated in TSMC 0.18-µm 1.8-V/3.3-V CMOS process. The charge pump aims to output voltage about - 10V and maximum current 3.5mA. The pumping capacitors of charge pump are 50pF and the output capacitor is 100pF. All capacitors of the negative charge pump are fully on-chip. Fig. 4.10 depicts the die photo of test chip, which includes the 4-stage charge pump and 4-phase clock generator (A), output capacitor of charge pump (B), and VCO, error amplifier and phase shift clock generator (C). The test chip area is 2.45 x 1.48mm<sup>2</sup>.

Fig. 4.10 Die photograph with A: 4-stage charge pump and 4-phase clock generator, B: output capacitor of charge pump, and C: VCO, error amplifier and phase shift clock generator.

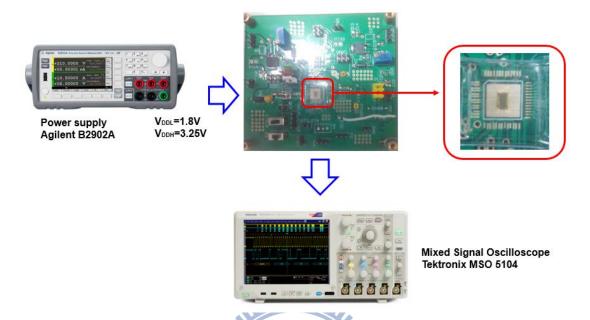

Fig. 4.11 depicts the measurement setup of test chip. The same as the measurement setup of the positive charge pump, Agilent B2902A is used to provide voltage 1.8V  $V_{DDL}$  and 3.25V  $V_{DDH}$ , which is also used to measurement power consumption of the

charge pump. Tektronix MSO 5104 is used to observe the waveforms of the charge pump.

Fig. 4.11 Measurement setup of test chip.

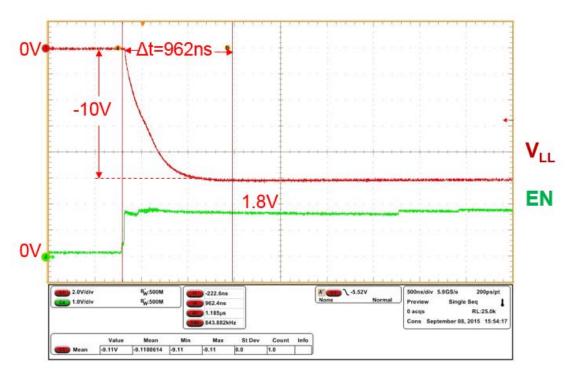

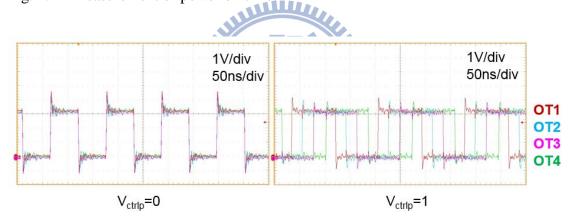

Fig. 4.12 depicts the measurement result of power on time at  $I_{load}$  is 3.5mA and  $V_{ctrlp}$  is logic 1, which is about 962nsec. Fig. 4.13 depicts the waveforms to check the phase shift clock generator function.  $V_{ctrlp}$ =0 means the clock signal of each stage doesn't have phase shift.  $V_{ctrlp}$ =1 means the clock signals of each stage has phase shift. The signals OT1, OT2, OT3 and OT4 are generated by clkd\_1, clkd\_2, clkd\_3 and clkd\_4 via some buffers respectively. As the measurement result, the function of phase shift clock generator is working.

Fig. 4.12 Measurement of power on time.

Fig. 4.13 Measurement of phase shift clock generator.

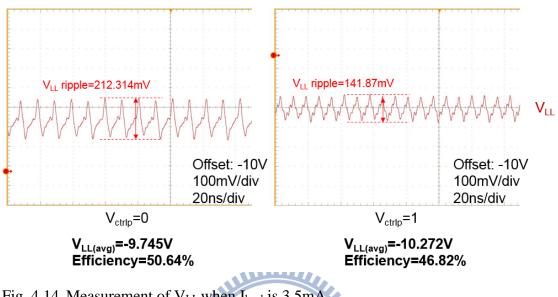

Fig. 4.14 depicts the measurement result of  $V_{LL}$  when  $I_{load}$  is 3.5mA. The efficiency is calculated by Eq. (4.2), where  $P_{VLL}$  is the power of  $V_{LL}$ .

$$Efficiency = \frac{P_{VLL}}{P_{VDDH} + P_{VDDL}}$$

(4.2)

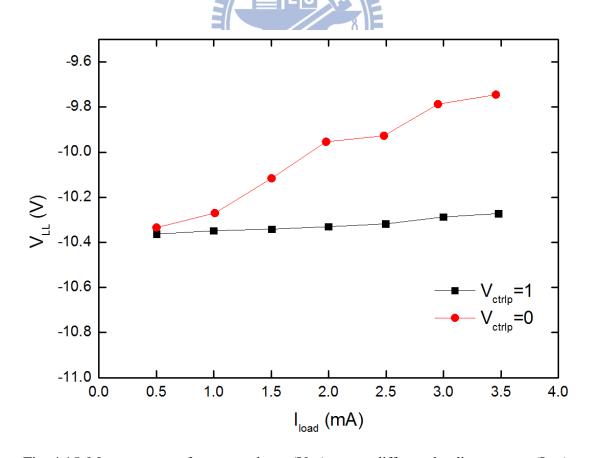

When  $V_{ctrlp}$  is logic low (GND), the average voltage of  $V_{LL}$  is -9.745V, the ripple of  $V_{LL}$  is 141.87mV, and the efficiency is 50.64%. When  $V_{ctrlp}$  is logic high ( $V_{DDL}$ ), the average voltage of  $V_{LL}$  is -10.272V, the ripple of  $V_{LL}$  is 141.87mV, and the efficiency is 46.82%. Fig. 4.15 show the measurement result of output voltage ( $V_{LL}$ ) versus

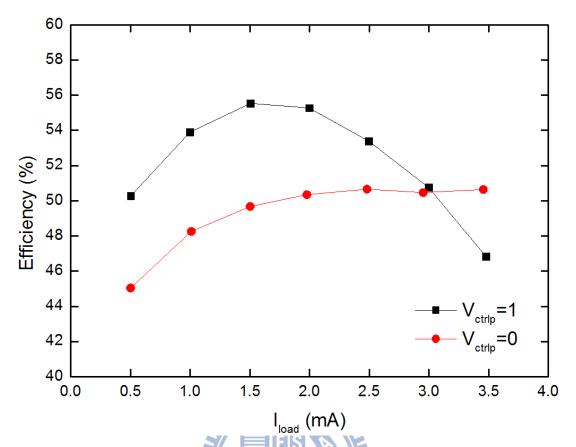

different loading current (I<sub>load</sub>). Fig. 4.16 show the measurement result of efficiency versus different loading current (I<sub>load</sub>). Fig. 4.17 show the measurement result of output ripple versus different loading current (I<sub>load</sub>).

Fig. 4.14 Measurement of V<sub>LL</sub> when I<sub>load</sub> is 3.5m

Fig. 4.15 Measurement of output voltage (V<sub>LL</sub>) versus different loading current (I<sub>load</sub>).

Fig. 4.16 Measurement of efficiency versus different loading current (I<sub>load</sub>).

Fig. 4.17 Measurement of output ripple versus different loading current ( $I_{load}$ ).

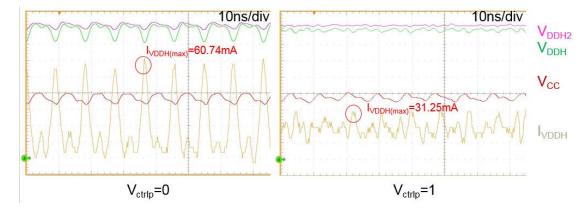

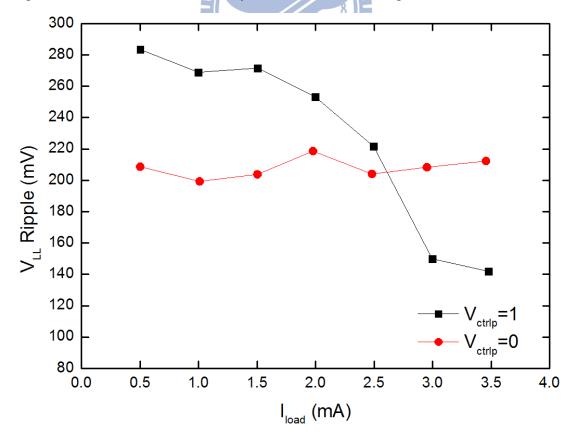

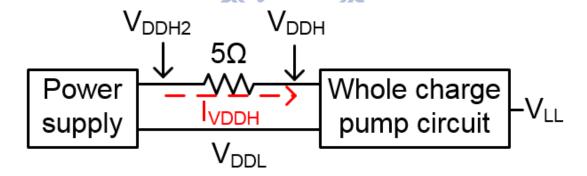

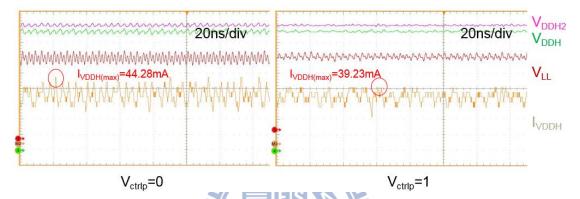

In order to measurement input peak current ( $I_{VDDH(max)}$ ) from  $V_{DDH}$ , we add a 5  $\Omega$  resistance between node  $V_{DDH2}$  and  $V_{DDH2}$  and measure the voltage difference between  $V_{DDH2}$  and  $V_{DDH}$ . Fig 4.18 shows the measurement setup. Fig. 4.19 depicts the measurement result of input current ( $I_{VDDH}$ ) from  $V_{DDH}$  when  $I_{load}$  is 1.5mA. When  $V_{ctrlp}$  is logic low (GND), the maximum input peak current ( $I_{VDDH(max)}$ ) is 59.25mA. When  $V_{ctrlp}$  is logic high ( $V_{DDL}$ ), the maximum input peak current ( $I_{VDDH(max)}$ ) is 29.3mA.

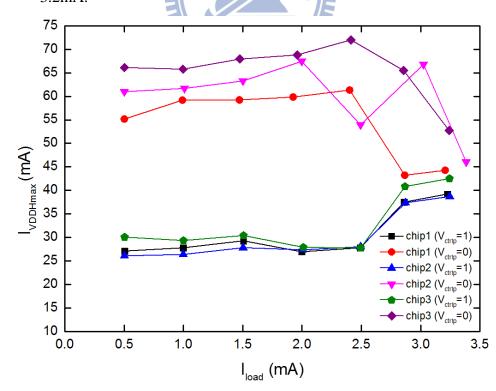

Fig. 4.20 depicts the measurement result of input current (I<sub>VDDH</sub>) from V<sub>DDH</sub> when I<sub>load</sub> is 3.2mA. When V<sub>ctrlp</sub> is logic low (GND), the maximum input peak current (I<sub>VDDH(max)</sub>) is 44.28mA. When V<sub>ctrlp</sub> is logic high (V<sub>DDL</sub>), the maximum input peak current (I<sub>VDDH(max)</sub>) is 39.23mA. Fig. 4.21 shows the measurement result of I<sub>VDDH(max)</sub> versus different loading current in three different chip. In the measurement result, the maximum input peak current can be reduce by applying phase shift clock (clkd\_1, clkd\_2, clkd\_3 and clkd\_4) to the charge pump. Table 4.1 is the comparison of post-simulation and measurement.

Fig. 4.18 The measurement setup for measuring IVDDH.

Fig. 4.19 The measurement result of input current ( $I_{VDDH}$ ) from  $V_{DDH}$  when  $I_{load}$  is 1.5mA.

Fig. 4.20 The measurement result of input current (I<sub>VDDH</sub>) from V<sub>DDH</sub> when I<sub>load</sub> is 3.2mA.

Fig. 4.21 The measurement result of  $I_{VDDHmax}$  versus different loading current in three different chip.

Table. 4.1 Comparison of post-simulation and measurement.

|                                                                      |       | Post-layout simulation (TT)                | Measurement                                  |

|----------------------------------------------------------------------|-------|--------------------------------------------|----------------------------------------------|

| Power supply V <sub>DDL</sub> / V <sub>DDH</sub>                     |       | 1.8V / 3.25V                               | 1.8V / 3.25V                                 |

| I <sub>VDDHmax</sub> V <sub>ctrip</sub> = 0 / V <sub>ctrip</sub> = 1 |       | 101.83mA / 46mA (I <sub>load</sub> =3.5mA) | 44.28mA / 39.23mA (I <sub>load</sub> =3.2mA) |

| V <sub>CC</sub> /<br>Efficiency<br>(V <sub>ctrip</sub> = 1)          | 0.5mA | -10.31V / 57.208%                          | -10.363V / 50.27%                            |

|                                                                      | 1mA   | -10.297V / 59.45%                          | -10.348V / 53.9%                             |

|                                                                      | 1.5mA | -10.293V / 60.06%                          | -10.341V / 55.54%                            |

|                                                                      | 2mA   | -10.283V / 60.05%                          | -10.33V / 55.27%                             |

|                                                                      | 2.5mA | -10.278V / 59.56%                          | -10.31V / 53.39%                             |

|                                                                      | 3mA   | -10.272V / 58.68%                          | -10.287V / 50.75%                            |

|                                                                      | 3.5mA | -10.263V / 57.15%                          | -10.272V / 46.82%                            |

| Process                                                              |       | TSMC 0.18µm 1.8V/3.3V CMOS Process         |                                              |

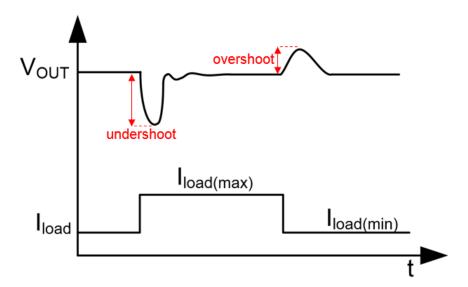

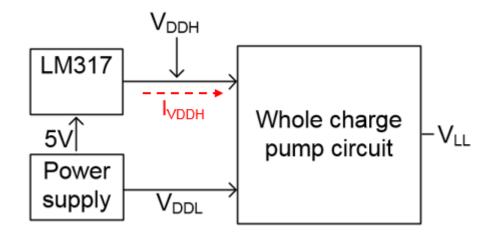

Fig. 4.22 depicts the transient response of a regulator. Theoretically, the lower peak loading current, the better transient response the regulator has. In this work, in order to observe the influence of lower peak current, we use a commercial dc-dc converter LM317 instead of power supply to supply 3.25V (V<sub>DDH</sub>). The measurement setup is shown as Fig. 4.23. We use LM317 to generate V<sub>DDH</sub> (3.25V) instead of using power supply. Fig. 4.24 depicts the measurement environment. Fig. 4.25 depicts the circuit diagram of LM317. The charge pump and LM317 are on the same PCB broad, and we probe the output voltage (V<sub>DDH</sub>) of LM317 to observe the waveform.

Fig. 4.22 Transient response of regulator.

Fig. 4.23 The measurement setup to observe the influence of lower peak current.

Fig. 4.24 The measurement environment to observe output voltage of LM317.

Fig. 4.25 The circuit diagram of LM317.

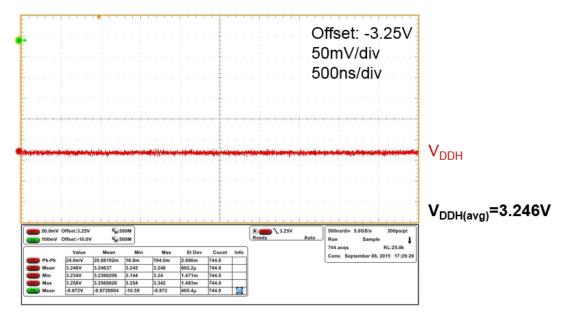

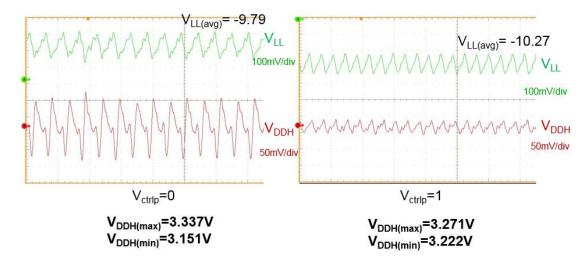

Fig. 4.26 depicts the waveform of  $V_{DDH}$  which is generated by LM317 when charge pump is turned off. The average voltage is 3.246V. Fig. 4.27 depicts the waveforms of  $V_{DDH}$  in different control voltage. When  $V_{ctrlp}$  is logic low (GND), the overshoot voltage of  $V_{DDH}$  is 3.337V and the undershoot voltage of  $V_{DDH}$  is 3.151V. When  $V_{ctrlp}$  is logic high ( $V_{DDL}$ ), the overshoot voltage of  $V_{DDH}$  is 3.271V and the undershoot voltage of  $V_{DDH}$  is 3.222V. By the measurement result, we can observe that the lower input current of  $V_{DDH}$  can enhance the transient response of LM317.

Fig. 4.26 The waveform of  $V_{\text{DDH}}$  when charge pump is turned off.

Fig. 4.27 The waveform of  $V_{DDH}$  in different control voltage ( $V_{ctrlp}$ ).

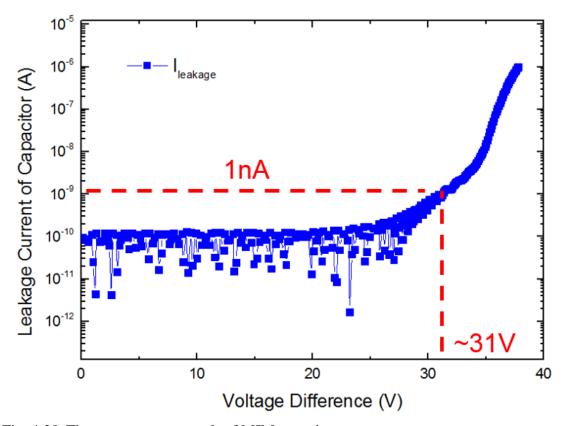

Moreover, we measure the leakage current of MIM capacitor in TSMC 0.18μm 1.8-V/3.3-V CMOS process by Agilent B1505A. Fig.4.28 depicts the measurement result. The capacitor is 25pF and the effective area is 22500μm². When the voltage difference across MIM capacitor reach about 31V, the leakage current is 1nA. In this work, the maximum voltage difference across MIM capacitor is about 10V~12V, and the leakage current is about 100pA. By this measurement, the MIM capacitor would not breakdown during circuit operation of charge pumps.

Fig. 4.28 The measurement result of MIM capacitor.

# 4.4 Summary

Design of a negative charge pump regulator for biomedical implant is investigated and verified in this chapter. The circuit design have been fabricated in TSMC 0.18-μm 1.8-V/3.3V CMOS process. The proposed design can output about -10.3V high voltage and maximum output current 3.5mA without the issues of electrical overstress and gate-oxide reliability. The 4-phase cross-couple negative charge pump is used. Each stage of charge pump has its own clock signal which has phase shift different from each other. By the measurement, the clock control scheme can reduce the maximum peak current which flow from power supply V<sub>DDH</sub>, and we also used a dc-dc converter LM317 to test this function.

# Chapter 5

# **Conclusions and Future Works**

#### **5.1 Conclusions**

#### 5.1.1 Positive Charge Pump

The positive charge pump can generate high voltage which is about 10.8V, and can output 3.5mA maximum loading current without gate-oxide reliability issues. By the phase shift clock control scheme, this circuit can reduce the maximum peak input current. This circuit is fabricated in TSMC 0.18µm 1.8-V/3.3-V CMOS process and die area is 1.87 x 1.48mm<sup>2</sup>. All charge pump circuit are realized fully on chip. The charge pump also had been fabricated in SoC for cochlear stimulation and could generate high voltage to stimulus driver.

### 5.1.2 Negative Cross-Couple Charge Pump

A negative cross-couple charge pump has been proposed and fabricated in TSMC 0.18µm 1.8-V/3.3-V CMOS process. All circuit are realize fully on chip, and die area is 2.45 x 1.48mm². The proposed design can generate negative high which is about -10.3V, and can output 3.5mA maximum loading current. This circuit can operate without gate-oxide reliability issues and return-back leakage current. We also used LM317 to observe the effect of peak loading current, and the transient response can be enhance by the lower peak loading current. Moreover, we measure the leakage of MIM capacitor to check the reliability of this charge pump circuit.

#### **5.2 Future Works**

#### 5.2.1 Charge Sharing

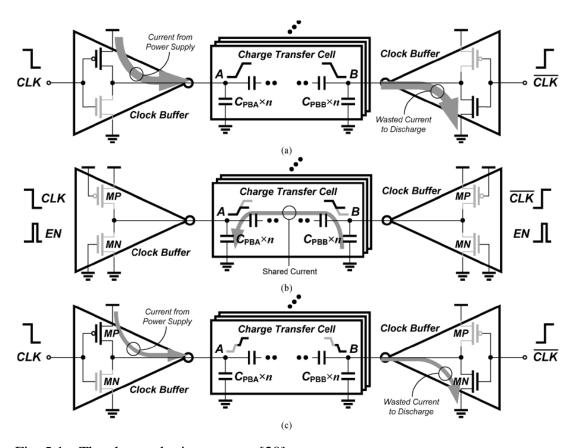

Some methods to enhance the efficiency of charge had been proposed, such as charge sharing concept [18] $\sim$ [21]. By recycling wasted charges in clock buffers of charge pump, the power consumption of charge pump can be reduce. Fig. 5.1 depicts the charge sharing concept. In Fig 5.1 (a), the charges on parasitic capacitance  $C_{PBB}$  are

dumped to ground and wasted. In charge sharing clock scheme, there is an intermediate voltage level before clock buffer outputs, some charges on  $C_{PBB}$  can be stored on  $C_{PBA}$  before the charges on  $C_{PBB}$  are dumped as shown in Fig. 5.1 (b). Then, the voltage on  $C_{PBA}$  is charged to  $V_{DD}$  and the voltage on  $C_{PBB}$  is discharged to GND as shown in Fig. 5.1 (c). By this method, the voltage swing of the buffer output which is charge by the current from the power supply become half, and can reduce the loss of charge pump.

Fig. 5.1 The charge sharing concept [20].

### 5.2.2 Negative Charge Pump

Fig. 5.2 depicts the circuit of negative charge pump. As the circuit operation in charter 4, the maximum voltage of node 3 and node 4 are  $V_{DDH}$ - $V_t$ , where the voltage drop ( $V_t$ ) is cause by Mb1 and Mb2. When Mn1 or Mn3 is tuned on, the  $V_{GS}$  of the MOS switch is  $V_{DDH}$ - $2V_t$ . This would cause more conduction loss on MOS switches and degrade the efficiency of charge pump. This problem need to be solve in the future.

Fig. 5.2 The circuit of negative charge pump.

# References

- [1] K. Chen, Z. Yang, L. Hoang, J. Weiland, M. Humayun, and W. Liu, "An integrated 256-channel epiretinal prosthesis," *IEEE J. Solid-State Circuits*, vol. 45, no. 9, pp. 1946–1956, Sep. 2010.

- [2] K.-Y. Lin, M.-D. Ker and C.-Y. Lin "A high-voltage-tolerant stimulator realized in the low-voltage CMOS process for cochlear implant," in Proc. *IEEE Int. Symp. Circuits Syst.*, May. 2014, pp. 237-240.

- [3] W.-M. Chen et al., "A fully integrated 8-channel closed-loop neuralprosthetic CMOS SoC for real-time epileptic seizure control," *IEEE J. Solid-State Circuits*, vol. 49, no. 1, pp. 232–247, Jan. 2014.

- [4] J. F. Dickson, "On chip high-voltage generation in MNOS integrated circuits using an improved voltage multiplied technique," *IEEE J. Solid-State Circuits*, vol. 1, pp. 374-378, Jun. 1976.

- [5] J. S. Witters, G. Groeseneken, and H. E. Maes, "Analysis and modeling of on-chip high-voltage generator circuits for use in EEPROM circuits," *IEEE J. Solid-State Circuits*, vol. 24, pp. 1372-1380, Oct. 1989.

- [6] J.-T. Wu and K.-L. Chang, "MOS charge pump for low-voltage operation," *IEEE J. Solid-State Circuits*, vol. 33, pp. 592–597, Apr. 1998.

- [7] M.-D. Ker, S.-L. Chen, and C.-S. Tsai, "Design of charge pump circuit with consideration of gate oxide reliability in low-voltage CMOS process," *IEEE J. Solid-State Circuits*, vol. 41, pp. 1100–1107, May. 2006.

- [8] A. Umezawa, S. Atsumi, M. Kuriyama, H. Banba, K. Imamiya, K. Naruke, S. Yamada, E. Obi, M. Oshikiri, T. Suzuki, and S. Tanaka, "A 5-V-only operation 0.6-μm flash EEPROM with row decoder scheme in triple-well structure," *IEEE J. Solid-State Circuits*, vol. 27, no. 11, pp. 1540-1546, Nov. 1992.

- [9] S. Ethier, M. Sawan, E. Aboulhamid, and M. El-Gamal, "A ±9V fully integrated CMOS electrode driver for high-impedance microstimulation," in *Proc. IEEE International Midwest Symposium on Circuits and Systems*, pp. 192-195, 2009.

- [10] Y.-C. Huang, M.-D. Ker, and C.-Y. Lin, "Design of Negative High Voltage Generator for Biphasic Stimulator with SoC Integration Consideration", in *Proc. IEEE Biomedical Circuits and Systems Conf.*, 2012.

- [11] J.-Y. Lee, S.-E. Kim, S.-J. Song, J.-K. Kim, S. Kim, and H.-J. Yoo, "A regulated charge pump with small ripple voltage and fast start-up," *IEEE J. Solid-State Circuits*, vol. 41, no. 2, pp. 425–432, Feb. 2006.

- [12] L. Aaltonen and K. Halonen, "On-chip charge-pump with continuous frequency regulation for precision high-voltage generation," in *Proc. IEEE Prime* '09, pp. 68–71, Jul. 2009.

- [13] J.-M. Baek, D.-J. Seo, J.-H. Chun, and K.-W. Kwon, "A dual charge pump for quiescent touch sensor power supply," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 59, no. 11, pp. 780–784, Nov. 2012.