# 國立交通大學

電子工程學系 電子研究所碩士班 碩士論文

高壓製程之靜電放電防護元件設計

# Study of Electrostatistic Discharge Protection Devices in High-Voltage BCD Processes

研究生: 黃橋晴 (Yu-Ching Huang)

指導教授: 柯明道教授 (Prof. Ming-Dou Ker)

中華民國一〇三年三月

# 高壓製程之靜電放電防護元件設計

# Study of Electrostatistic Discharge Protection Device in High-Voltage BCD Processes

研究生:黃楀晴 Student: Yu-Ching Huang

指導教授:柯明道教授 Advisor: Prof. Ming-Dou Ker

國立交通大學

電子工程學系 電子研究所

碩士論文

### **A** Thesis

Submitted to Department of Electronics Engineering and Institute of Electronics College of Electrical and Computer Engineering

NationalChiao-TungUniversity

in Partial Fulfillment of the Requirements

for the Degree of

Master of Science

in

Electronics Engineering

Electronics Engineering March2014 Hsinchu, Taiwan

中華民國一〇三年三月

# 高壓製程之靜電放電防護元件設計

學生: 黃楀晴指導教授: 柯明道教授

國立交通大學

電子工程學系電子研究所碩士班

# 摘要

高壓元件已在各種產品(電腦、消費性、通訊、和車用電子產品)中被廣泛的運用,LED、車用安全控制晶片、電源管理晶片、觸碰螢幕控制晶片和太陽能元件都是很好的例子,將來這樣的應用將會與IC產業的緊密結合。隨著高壓元件市場需求量日與劇增,連帶的對於高壓元件的靜電放電防護可靠度設計的需求也非常高。在積體電路製造、封裝及測時的時候,都有可能受到靜電的轟擊,隨著元件尺寸縮小,這樣的危害更為明顯。現今,靜電放電所造成的可靠度議題漸漸的被重視。為了避免靜電來襲將會導致元件不正常工作甚至損壞,添加或更改元件結構使其滿足靜電防護的標準將是一個十分重要的課題。

在高壓製程中靜電防護的研究尤為困難。因為高壓的靜電放電防護元件需同時滿足耐高壓及大電流的能力,又要防止閂鎖效應 (latch up)的發生。橫向擴散電晶體(LDMOS) 常在高壓互補式金氧半製程中被使用,倘若其能同時工作和當作靜電防護元件將會省去許多面積。然而,在高壓製程中有諸多變因會導致靜電防護能力的下降,例如克爾克效應 (Kirk-effect)導致保持電壓(holding voltage)太低、元件的不均勻導通:導致電流過於集中某處所造成永久性的損害、氧化層的載子侷限效應(oxide charge trapping)等等造成其高壓元件本身難有良好之靜電放電防護能力,在這個因素之下,即使將靜電放護元件布局面積放大,

也不一定會獲得耐受度的提升。不均勻導通的原因,有可能是因為其保持電壓太低的緣故,提升元件的保持電壓,既可能可以改善不均勻導通的現象,也能夠防止雜訊導致的閂鎖效應,但由於熱的效應,提升電壓很容易導致可排放之靜電放電電流下降。因此如何在不減損原本靜電防護能力的前提之下提高其保持電壓,也是高壓靜電防護元件設計的一大課題。

如何設計最佳化的高壓靜電放電防護元件,是本論文的探討重點。在這次碩士論文,提出了許多不同結構形式的橫向擴散電晶體(LDMOS),希冀能透過研究,找出橫向擴散電晶體的最佳結構能夠滿足同時正常工作和自我保護的要求。其透過第三章的研究結果可以發現,在汲極端加以改良設計過後的元件能成功的使寄生的矽控整流器(SCR)成功的出現,也因此該元件的靜電耐受度能夠過人體放電測試 2kV 的靜電防護標準。另外,先前提到的不均勻導通及閂鎖效應均歸因於保持電壓太低,這個問題尤以含有寄生矽控整流器的元件中最為明顯。因此有許多提升保持電壓的方法將在本論文的第四章中被提出,透過實際下線量測的結果可以發現,在源極中多加上一個寄生雙極性電晶體的結構能夠使保持電壓有效的提升,搭配其他參數的變化,就能夠發展出許多不同的靜電防護元件。本碩士論文所提出結構也已經有相對應的國際期刊與會議論文發表。

# Study of Electrostatistic Discharge Protection Device in High-Voltage BCD Processes

Student: Yu-Ching Huang Advisor: Prof. Ming-Dou Ker

Department of Electronics Engineering &Institute of Electronics College of Electrical and Computer Engineering NationalChiao-TungUniversity

# **Abstract**

Nowadays, with a rapid increase in demand, such as motor drivers, LED lighting, solar energy and display driver circuits, high voltage integrated process technologies have been developed and become commercially available. The lateral DMOS (LDMOS) is a common device for high-voltage output driver. Thus, LDMOS was expected for self-protection electrostatic discharge (ESD) device. ESD is an inevitable event during fabrication, packaging and testing processes of integrated circuits. ESD protection design is therefore necessary to protect ICs from being damaged by ESD stress.

In the last two decades, some studies shows that ESD robustness of nLDMOS is not good in the results of Kirk-effect-induced holding voltage lowering, multi-finger non-uniformity issue and isolation oxide charge trapping issue. Though the ESD performance is not good enough, gate-grounded-LDMOS in ESD condition is widely used due to straightforward implementation and sufficient high current

capabilities. Developing a HV-LDMOS that can meet the acceptable ESD level without scarifying the IV characteristics and dimension of the device will be a big challenge for smart power technologies.

In this work, many different structures of nLDMOS have been realized in 0.25-µm 60-V BCD process including source-side and drain-side engineering. Also stretch the layout parameter and style to optimize the nLDMOS's ESD robustness. The structure that combines the concepts of changing the layout space and embedded SCR inside LDMOS with additional p+ and n+ implantation regions between its drain and poly-gate to make sure that it can keep stably in the high-current holding region and meet the typical ESD specification of commercial IC products.

Owing to the superior ESD performance of SCR, the device structure in Chapter 4 is based on embedded SCR structure in both HV and LV well. Hoping to figure out a device that can have good ESD levels and latchup immunity, this work investigates the different structures and parameters of HVSCR and LVSCR by many different methods to increase the holding. All the devices are successfully verified in a 0.25-µm 60-V BCD process.

# Acknowledgements

# 致謝

首先我要感謝我的指導教授柯明道老師,謝謝老師在碩士的這兩年中的諄 諄教誨及教導,不辭辛苦地四處爭取研究資源,讓我們擁有許多與業界合作或 下線的機會。此外也常藉由分享生活故事來教導我們許多做事的態度激發我們 對研究的熱忱,這些都是非常寶貴的學習經驗,真的非常謝謝老師!

然而我還要特別感謝「國家晶片系統設計中心」讓我有下線機會對所提出的元件架構進行驗證,還有「閱康科技股份有限公司」協助進行失效分析。

接下來還要感謝同實驗室的學長姐們:絕頂聰明的群祐學長、十分可靠的柏硯學長、為人風趣的小州哥、立煒學長、認真負責的致廷學長、認真努力的惠雯學姊、美麗大方的倍如學姊、帶我的筱晴學姊、宛彥學姊、一起量測的品宏學長、指導我的嘉岑學長、很強很可愛的雅君學姊、還有一直說可以幫我改英文的艾飛學長,感謝大家一路的照顧與鼓勵,謝謝你們。跟我同屆的好夥伴珊綺,謝謝你幫我分擔一些事情以及聽我的抱怨;也要謝謝十分好學的俊瑋以及謝謝實驗室的學弟妹們:林冠宇、湯凱能、張品歆、范美蓮、曾建豪,謝謝你們這些日子來的鼓勵與陪伴,因為你們讓生活變得更加有趣。當然還有最後在工研院中認識的志明與詠智,透過討論讓我對靜電防護又有更全面性的體會,也謝謝你們給我的包容與鼓勵。

最後,特別感謝我的父母及哥哥,無論在經濟上或是精神上都能給予我支持和鼓勵,使我在兩年的研究生活當中得以心無旁鶩地致力於研究。要感謝的 人還有好多好多,在此一併謝上每個在我求學的路途中曾經幫助過我陪伴過我 的各位,謝謝你們。

> 黄楀晴 謹誌於竹塹交大 民國一零二年六月

# **Contents**

| Abstract (Chinese)                                 | i   |

|----------------------------------------------------|-----|

| Abstract (English)                                 | iii |

| Acknowledgment                                     | v   |

| Contents                                           | vi  |

| Table Captions                                     | ix  |

| Figure Captions                                    | X   |

| Chapter 1Introduction                              | 1   |

| 1.1 Motivation                                     | 1   |

| 1.2 Introduction of Electrostatic Discharge (ESD)  | 2   |

| 1.3 Thesis Organization                            | 5   |

| Chapter 20verview for High Voltage ESD Protections | 6   |

| 2.1 Common ESD Protection Device in High Voltage   |     |

| <u>Process</u>                                     | 6   |

| 2.2 <u>Latchup Immunity Issue in HV Process</u>    | 12  |

| 2.3 The Trade-off Between ESD and SOA              | 13  |

| 2.3.1 Introdunction to SOA                         | 13  |

| 2.3.2 Trade-off between SOA and ESD                | 16  |

| Chapter 3Parameter Investigation for Self-Protected         |    |  |  |

|-------------------------------------------------------------|----|--|--|

| nLDMOS Devices in High-Voltage Process                      | 18 |  |  |

| 3.1 Standard nLDMOS Structure in 60-V 0.25 µm BCD           |    |  |  |

| <u>Process</u>                                              | 18 |  |  |

| 3.2 Parameter Investigation of Stand-alone nLDMOS           | 21 |  |  |

| 3.2.1 Stand-alone nLDMOS with different total width         | 22 |  |  |

| 3.2.2Stretch parameter of STI space and drain diffusion     |    |  |  |

| region                                                      | 23 |  |  |

| 3.2.3Changethe NBLtype of stand-alone nLDMOS                | 27 |  |  |

| 3.3 Investigation on Different tpyes of Embeeded SCR in     |    |  |  |

| nLDMOS                                                      | 34 |  |  |

| 3.3.1 Embedded SCR structure in stand-alone LDMOS           | 34 |  |  |

| 3.3.2 Adding more implant layer in the source side          | 34 |  |  |

| 3.3.3 Adding more implant layer in the drain side           | 37 |  |  |

| 3.4 <u>Discussion and Summary</u>                           | 42 |  |  |

| 3.4.1 Discussion and failure analysis                       | 42 |  |  |

| 3.4.2 Summary                                               | 45 |  |  |

| Chapter 4 Modification for LVSCR and HVSCR Structure        | 47 |  |  |

| 4.1 Embedded SCR structure in 60-V 0.25 μm BCD              |    |  |  |

| Process                                                     | 47 |  |  |

| 4.1.1 Investigation for layer effect upon the SCR structure | 47 |  |  |

| 4.1.2Adding more implant in the anode side       | 50 |

|--------------------------------------------------|----|

| 4.1.3 Adding more implant in the cathode side    | 53 |

| 4.2 Device Modification of HVSCR                 | 55 |

| 4.2.1 Layers modification of HVSCR               | 55 |

| 4.2.2 Layers modification of the SCR device with |    |

| cathode-side engineering                         | 59 |

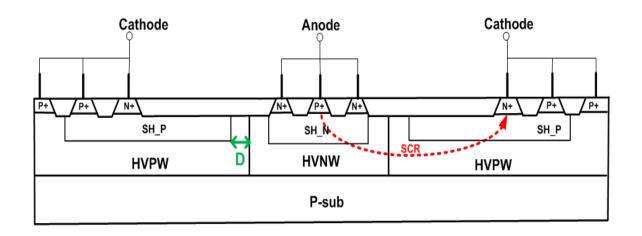

| 4.2.3 Stretching the parameter of the SCR device | 63 |

| 4.3 The Proposed LVSCR Design in HV Process      | 65 |

| 4.3.1 Adding more implant in the cathode side    | 66 |

| 4.3.2 Other Modification of LVSCR                | 68 |

| 4.4 <u>Discussion and Summary</u>                | 72 |

| 4.4.1 Discussion                                 | 72 |

| 4.4.2 Summary                                    | 80 |

| <b>Chapter 5 Conclusions and Future Work</b>     | 82 |

| 5.1 <u>Conclusions</u>                           | 82 |

| 5.2 <u>Future Work</u>                           | 83 |

| References                                       | 85 |

| Vita                                             | 89 |

# **Table Captions**

| Table 3.1. Summarize the ESD robustness of nLDMOS devices with different       |      |

|--------------------------------------------------------------------------------|------|

| parameter S and d                                                              | . 44 |

| Table 3.2. The TLP-measured results and ESD robustness with different embedded |      |

| SCR devices.                                                                   | . 45 |

| Table 4.1. The detail results of anode-engineering HVSCR.                      | . 78 |

| Table 4.2. The comparisons of ESD robustness with in different implantation    |      |

| arrangement in anode                                                           | 78   |

| Table 4.3. The detail results of cathode-engineering in HVSCR.                 | 79   |

| Table 4.4. The detail results of cathode-engineering in LVSCR                  | . 79 |

# **Figure Captions**

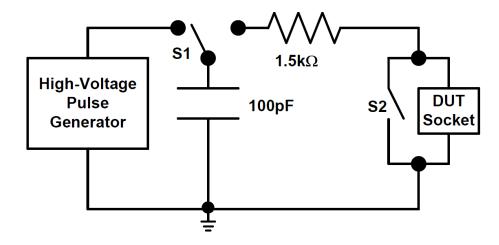

| Fig. 1.1.  | The equivalent circuit of the human body model ESD event [4]           | . 2 |

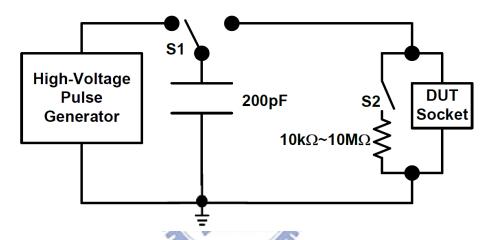

|------------|------------------------------------------------------------------------|-----|

| Fig. 1.2.  | The equivalent circuit of the machine model ESD event [5]              | . 2 |

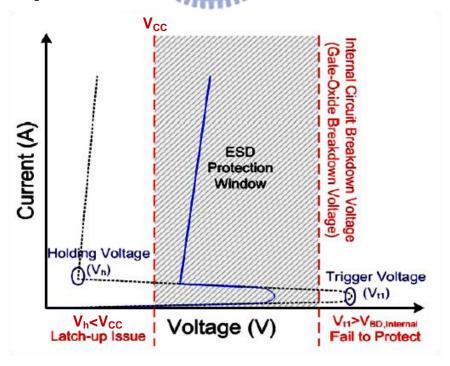

| Fig. 1.3.  | ESD protection design window of ESD protection device [7]              | . 2 |

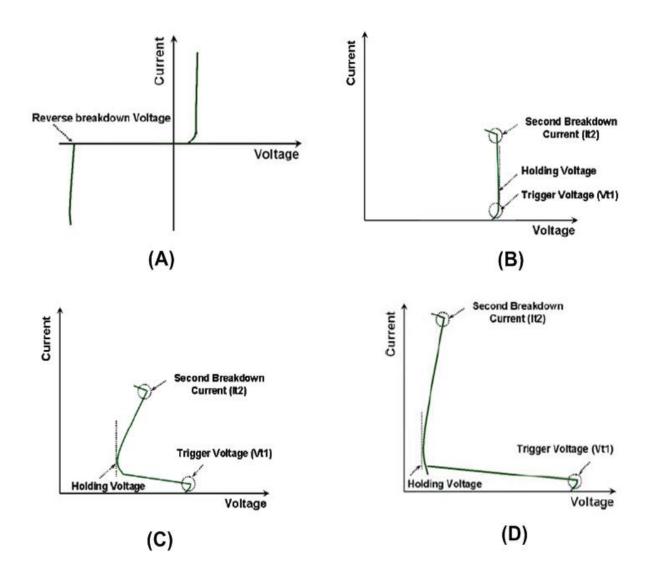

| Fig. 2.1.  | The simplified I-V curves of the common ESD device. (A) Diode, (B)     |     |

|            | P-type MOS or FOD, (C) gate-grounded nLDMOS or N-type FOD, (D)         |     |

|            | Device with SCR path.                                                  | 11  |

| Fig. 2.2.  | The test setup for eSOA measurement by 100-ns TLP pulses [19]          | 15  |

| Fig. 2.3.  | A diagram showing SOA of a high voltage MOSFET [19]                    | 15  |

| Fig. 2.4.  | Equivalent circuit model of NMOS in high voltage process, shown with   |     |

|            | the parasitic bipolar junction [18]                                    | 15  |

| Fig. 2.5.  | Measured SOA boundaries of two nLDMOS transistors by 100-ns TLP        |     |

|            | pulses [18]                                                            | 16  |

| Fig. 2.6.  | The design triangle of power semiconductor devices [18]                | 17  |

| Fig. 3.1.  | The cross-sectional view of standard nLDMOS in a 60-V BCD process      | 20  |

| Fig. 3.2.  | The top view of standard nLDMOS in a 60-V BCD process                  | 20  |

| Fig. 3.3.  | I-V characteristics of standard nLDMOS with minimum rule of all the    |     |

|            | parameter, which is measured by 100-ns TLP system                      | 21  |

| Fig. 3.4.  | I-V characteristics of nLDMOS which has different number of fingers.   |     |

|            | (Each finger is 80μm).                                                 | 23  |

| Fig. 3.5.  | The cross-sectional view of standard nLDMOS in a 60-V BCD process      |     |

|            | with parameter S and d.                                                | 25  |

| Fig. 3.6.  | I-V characteristics of nLDMOS with different parameter d.              | 25  |

| Fig. 3.7.  | I-V characteristics of nLDMOS with different parameter S (when d=1μm). | 26  |

| Fig. 3.8.  | I-V characteristics of nLDMOS with different parameter S (when d=5μm). | 26  |

| Fig. 3.9.  | Compare It2 levels among the single devices under different d and S    | 27  |

| Fig. 3.10. | (A) and (B) Cross-sectional view of LDMOS (S=5μm) in 40V process       |     |

|            | without and with isolate NBL. (C) The current flow contours of LDMOS   |     |

|            | without NBL. (D) The current flow contours of LDMOS with NBL[24]       | 29  |

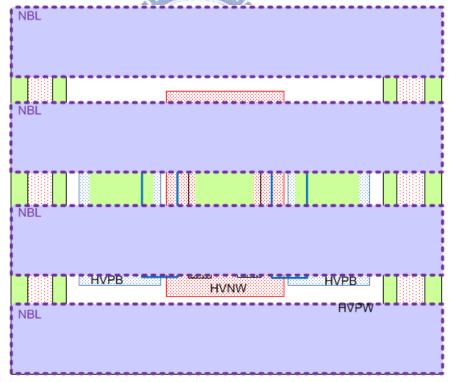

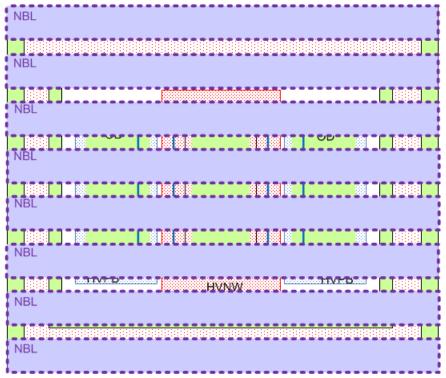

| Fig. 3.11. | The top view of nLDMOS which is covered by one NBL layer (Type 1)      | 30  |

| Fig. 3.12. | The top view of nLDMOS which is covered by four NBL fingers (Type 2)   |     |

|            |                                                                        | 30  |

| Fig. 3.13. | The top view of nLDMOS which is covered by eight NBL fingers (Type     |     |

|            | 3)                                                                     | 31  |

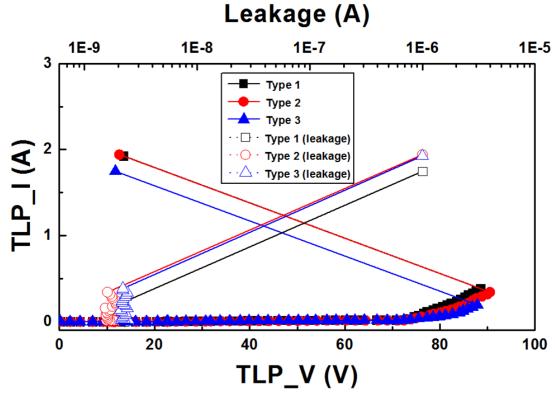

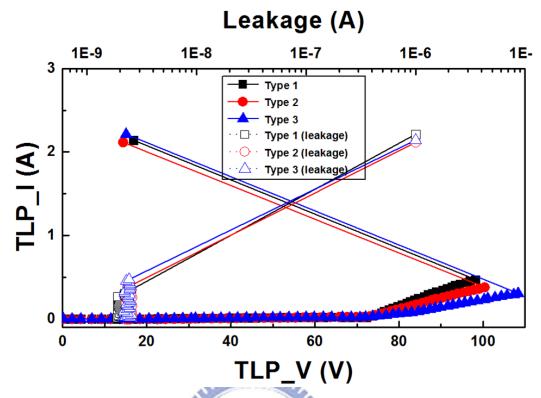

| Fig. 3.14. | The TLP results of the devices with three types of NBL.                |     |

|            | (The space of STI is 3.8μm).                                           | 31  |

| Fig. 3.15. | The TLP results of the devices with three types of NBL.                 |    |

|------------|-------------------------------------------------------------------------|----|

|            | (The space of STI is 5.8µm).                                            | 32 |

| Fig. 3.16. | The TLP results of the devices with three types of NBL.                 |    |

|            | (The space of STI is 7.8µm).                                            | 32 |

| Fig. 3.17. | Compare the trigger voltage (Vt1) of three different types of NBL       | 33 |

| Fig. 3.18. | Compare the maximum current handling ability (It2) of three different   |    |

|            | types of NBL                                                            | 33 |

| Fig. 3.19. | The cross-sectional view of embedded SCR structure with larger          |    |

|            | parameter A in a 60-V BCD process (S-pn-ref)                            | 35 |

| Fig. 3.20. | The cross-sectional view of new proposed embedded SCR structure with    |    |

|            | source side engineering in a 60-V BCD process (S-pn)                    | 36 |

| Fig. 3.21. | The TLP results of S-pn-ref and S-pn. (The space of STI is $3.8 \mu m)$ | 36 |

| Fig. 3.22. | The TLP results of S-pn-ref and S-pn. (The space of STI is $5.8 \mu m)$ | 37 |

| Fig. 3.23. | The cross-sectional view of embedded SCR structure in a 60-V BCD        |    |

|            | process (LDMOSSCR)                                                      | 40 |

| Fig. 3.24. | The cross-sectional view of new proposed embedded SCR structure in the  |    |

|            | drain side in a 60-V BCD process (D-pn-kmin and D-pn-k5)                | 40 |

| Fig. 3.25. | The TLP results of three different type of device with drain-side       |    |

|            | engineering. (The space of STI is 3.8µm)                                | 41 |

| Fig. 3.26. | The TLP results of three different type of device with drain-side       |    |

|            | engineering. (The space of STI is 5.8µm)                                | 41 |

| Fig. 3.27. | The SEM image of embedded SCR LDMOS device (named                       |    |

|            | LDMOSSCR-5.8) after 1.5kV HBM test. (S=5.8µm case)                      | 43 |

| Fig. 3.28. | The SEM image of new proposed device (D-pn-k5-5.8) after 2.5 kV HBM     |    |

|            | test                                                                    | 44 |

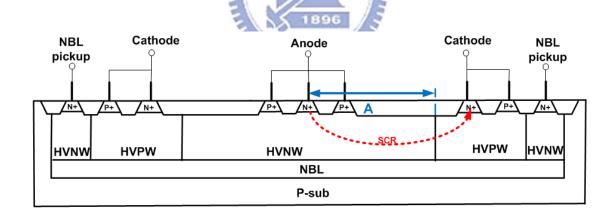

| Fig. 4.1.  | The cross-sectional view of simple SCR structure which is named HVSCR.  |    |

|            |                                                                         | 49 |

| Fig. 4.2.  | The cross-sectional view of simple SCR with additional SH_N and SH_P    |    |

|            | layer structure (which is named HVSCR+SH_P)                             | 49 |

| Fig. 4.3.  | The cross-sectional view of HVSCR+SH_P+HVPB device which is based       |    |

|            | on HVSCR+SH_P device with HVPB layer structure.                         | 49 |

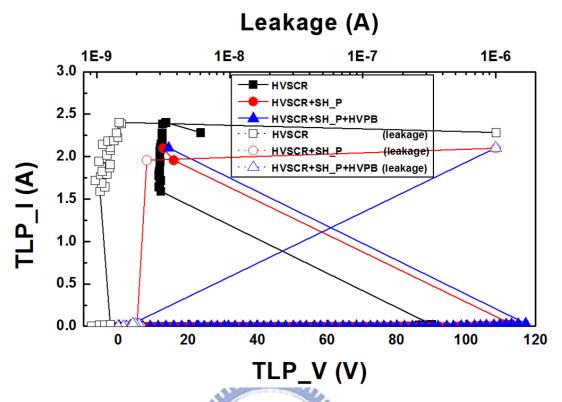

| Fig. 4.4.  | The TLP results of three different HVSCR devices.                       | 50 |

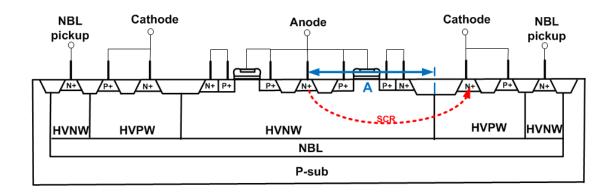

| Fig. 4.5.  | The cross-sectional view of reference HVSCR structure of anode side     |    |

|            | engineering (which is named HVSCR-A-pn-ref).                            | 51 |

| Fig. 4.6.  | The cross-sectional view of HVSCR structure of anode side engineering   |    |

|            | (which is named HVSCR-A-pn)                                             | 52 |

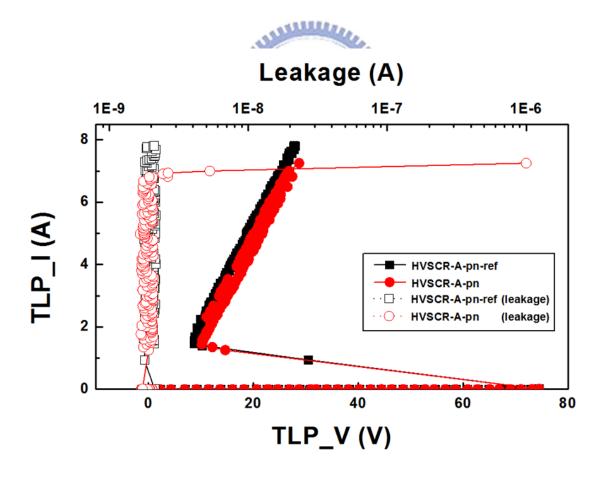

| Fig. 4.7.  | The TLP results of HVSCR devices with Additional implant layer in       |    |

|            | anode                                                                   | 52 |

| Fig. 4.8.  | The cross-sectional view of reference HVSCR structure of cathode side        |    |

|------------|------------------------------------------------------------------------------|----|

|            | engineering (which is named HVSCR-pnp-ref).                                  | 54 |

| Fig. 4.9.  | The cross-sectional view of HVSCR structure of cathode side engineering      |    |

|            | (which is named HVSCR-pnp+pn)                                                | 54 |

| Fig. 4.10. | The TLP results of HVSCR devices with additional implant layer in            |    |

|            | cathode                                                                      | 55 |

| Fig. 4.11. | The cross-sectional view of different arrangement HVSCR in cathode           |    |

|            | (which is named HVSCR-npn).                                                  | 56 |

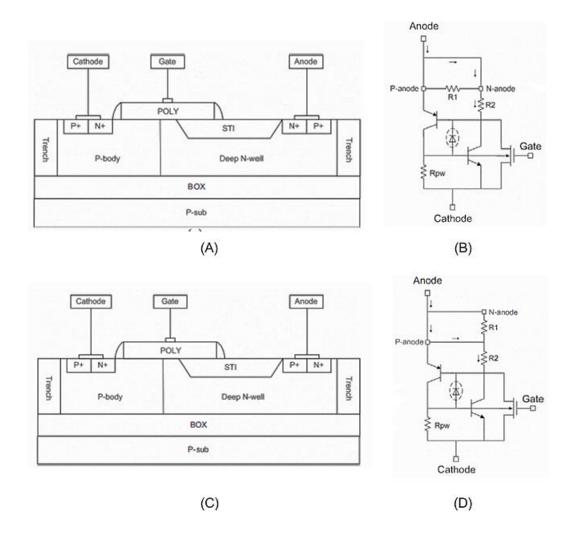

| Fig. 4.12. | The schematics of two different types. (A) and (B) are the cross-sectional   |    |

|            | view and equivalent circuit of HVSCR of the type one, respectively. In       |    |

|            | contrast, (C) and (D) are the cross-sectional view and equivalent circuit of |    |

|            | HVSCR of the type two [25]                                                   | 57 |

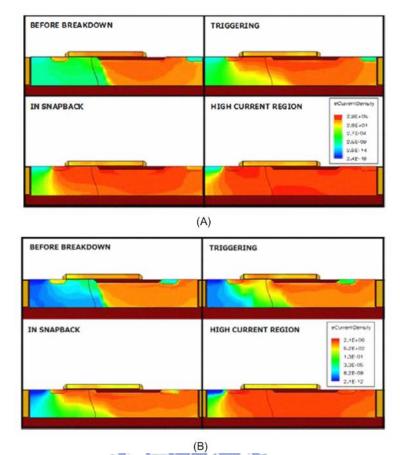

| Fig. 4.13. | The current distribution simulation of two different types [25]              | 58 |

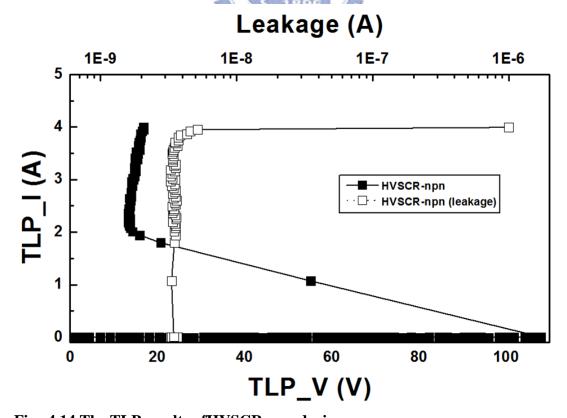

| Fig. 4.14. | The TLP results of HVSCR-npn device.                                         | 58 |

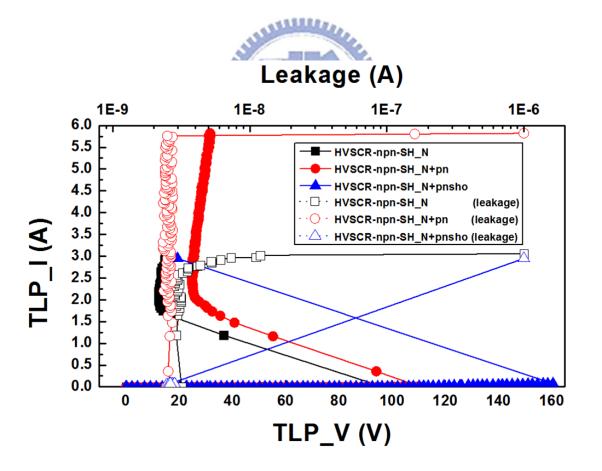

| Fig. 4.15. | The cross-sectional view of HVSCR-npn with additional SH_N and SH_P          |    |

|            | layer in both anode and cathode (which is named HVSCR-npn-SH_N)              | 60 |

| Fig. 4.16. | The cross-sectional view of HVSCR-npn-SH_N+pn, which is                      |    |

|            | HVSCR-npn-SH_N device with addional n+ and p+ in cathode                     | 60 |

| Fig. 4.17. | The cross-sectional view of HVSCR-npn-SH_N+pnsho, which is addional          |    |

|            | n+ and p+ in cathode method and the Schottky emitter technique               | 61 |

| Fig. 4.18. | The TLP results of three different types of HVSCR with SH_N and SH_P         |    |

|            | in the cathode region                                                        | 61 |

| Fig. 4.19. | The cross-sectional view of HVSCR-npn with only SH_P layer in cathode        |    |

|            | (which is named HVSCR-npn-SH_P-D35).                                         | 62 |

| Fig. 4.20. | The cross-sectional view of HVSCR-npn-SH_P+pn-D35 which is the               |    |

|            | HVSCR-npn-SH_P-D35 device with additional n+ and p+ implantation in          |    |

|            | cathode                                                                      | 62 |

| Fig. 4.21. | The TLP results of those devices in group two, which only has SH_P layer     |    |

|            | in cathode region                                                            | 63 |

| Fig. 4.22. | The TLP results of two different devices in group two with different         |    |

|            | parameter D.                                                                 | 64 |

| Fig. 4.23. | The comparison between HVSCR-npn-SH_P-D35 and                                |    |

|            | HVSCR-npn-SH_P-Dmin                                                          | 64 |

| Fig. 4.24. | The cross-sectional view of (A) LVSCR-pnp and (B) LVSCR-pnp+pn               |    |

| _          | The TLP results of LVSCR-pnp and LVSCR-pnp+pn                                |    |

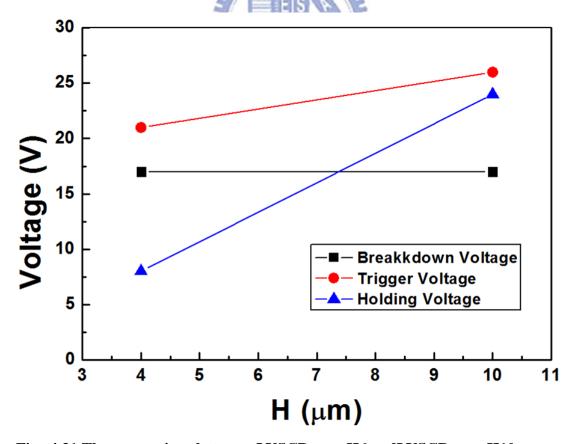

|            | The cross-sectional view of LVSCR-npn. There are two different               |    |

| Č          | parameter H is proposed which name as LVSCR-npn-H6 and                       |    |

|            | LVSCR-npn-H10, respectively                                                  | 69 |

| Fig. 4.27. | The cross-sectional view of LVSCR-npn+pn. There are two different          |   |

|------------|----------------------------------------------------------------------------|---|

|            | parameter H is proposed which name as LVSCR-npn+pn-H6 and                  |   |

|            | LVSCR-npn+pn-H10, respectively                                             | 9 |

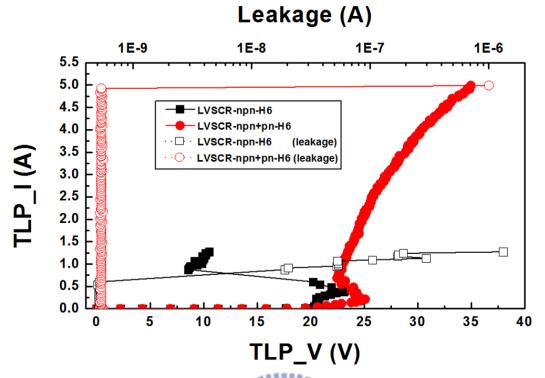

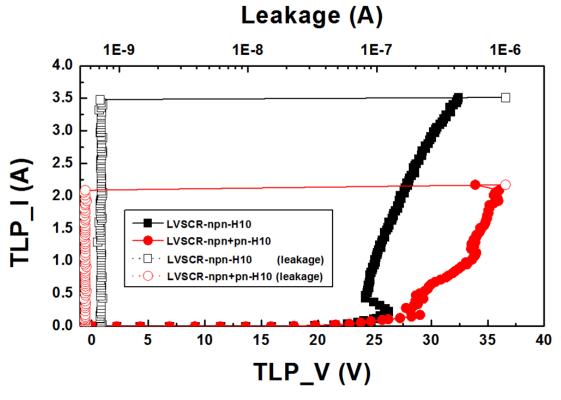

| Fig. 4.28. | The TLP results of two different structures with same parameter H.(H is    |   |

|            | equal to 6.5μm)                                                            | 0 |

| Fig. 4.29. | The TLP results of two different structures with same parameter H.(H is    |   |

|            | equal to 10μm)                                                             | 0 |

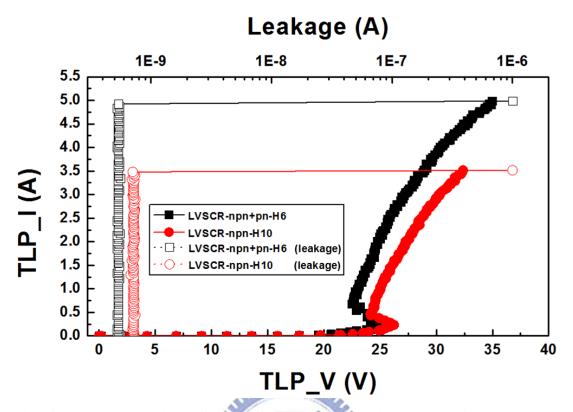

| Fig. 4.30. | The comparison of two different devices which has the highest It2 level 7  | 1 |

| Fig. 4.31. | The comparison between LVSCR-npn-H6 and LVSCR-npn-H10                      | 1 |

| Fig. 4.32. | (A) Cross-sectional view and (B) the equivalent circuit of LVSCR-pnp 7     | 5 |

| Fig. 4.33. | (A) Cross-sectional view and (B) the equivalent circuit of                 |   |

|            | LVSCR-pnp+pn7                                                              | 6 |

| Fig. 4.34. | Measurement setup of transient-induced-latchup (TLU) test [39]7            | 6 |

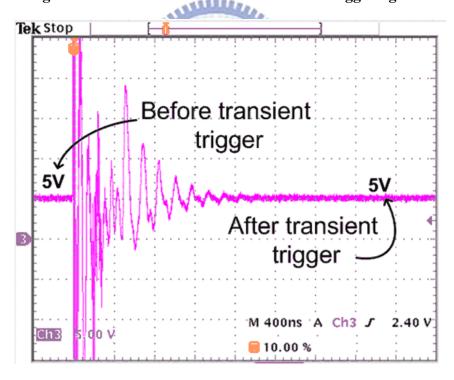

| Fig. 4.35. | Voltage waveforms before/after transient noise triggering on LVSCR-pnp 7   | 7 |

| Fig. 4.36. | Voltage waveforms before/after transient noise triggering on               |   |

|            | LVSCR-pnp+pn7                                                              | 7 |

| Fig. 4.37. | The illustrations of stacking different number of devices and anticipation |   |

|            | of the TLP results8                                                        | 1 |

# **Chapter 1**

# Introduction

#### 1.1 Motivation

High-voltage operations are often used in the industrial applications, such as automotive electronics, green energy, power management ICs, and industrial control. Electrostatic discharge (ESD) protection in smart power technology is a very challenging task due to its high operation voltage and an insufficient ESD design window as shown limited by both operation voltage and the failure voltage of the component to be protected [1]. That means the ideal ESD power clamp should have low trigger-on-voltage,high immunity for latchup and enough margin for reliability under high voltage operation. Typical specification for integrated circuits requires at least 1kV HBM on all pins, according to the recent recommendation of the Industry Council on ESD target levels in HV device while many customers are still requesting the former 2kV HBM level [2].

One of the most popular structures in high-voltage process is the Lateral Diffused MOS (LDMOS) which is widely used as an output driver. LDMOS was expected to have self-protected capability against ESD. However, owing to the high process complexity and fabrication cost in HV process, it is difficult to guarantee the ESD reliability of HV devices. Tough LDMOS doesn't have good ESD robustness initially;the gate-gounded-NMOS is still widely used as ESD protection device due to straightforward implementation and sufficient high current capability. Therefore, developingnLDMOS or other ESD protection devices that can meet the acceptable ESD level without scarifying the IV characteristics and dimension of the device will be a big challenge for smart power technologies.

# 1.2 Introduction of Electrostatic Discharge (ESD)

ESD is critical stress event for semiconductor products, which can encounter during manufacturing, packaging or assembling process [3]. It is an instantaneous discharging of electrostatic charges on IC pins by physical touching of a human body, contacting of manufacturing machines, or discharging of on IC chips itself. According to the different discharge conditions and sources of electrostatic charges, ESD can be classified to human-body model (HBM), machine-model (MM), and charged-device model (CDM).

#### (1)Human Body Model (HBM)

HBM is a common ESD event due to the connection of a charged human body and an IC product. If the electrostatic charge transfers into the IC products, the device may get some damage. To prevent the failure, the human body model is established to simulate this kind of stress by the equivalent schematic in Fig. 1.1 [4]. In the equivalent circuit for HBM ESD event, a 1.5 k $\Omega$  resistor and the 100-pF capacitor are placed to represent the parasitic resistor and capacitor of a human body. Commercial ICs are generally demanded to pass 2-kV HBM level.

#### (2) Machine Model (MM)

The MM ESD event arises from the contact of a machine and IC products. The equivalent circuit diagram of MM ESD event is shown in Fig. 1.2 [5], where there is no equivalent resistor on the equivalent discharging path. Commercial ICs are generally demanded to pass 200-V MM level.

### (3) Charged Device Model (CDM)

The CDM ESD event happens under the condition of the contact of charged IC and external grounded object. During the process, some charge would store in the p-substrate. When this charged IC is touched by an external grounded object, CDM charges in the p-substrate will be discharged from the IC inside to the

grounded object outside. There is no standard equivalent parasitic capacitor and resistor for the CDM ESD stress because different dimension of chips, different form and size of packages result in different values of the parasitic capacitor and resistor of IC chips. A commercial IC is generally requested to pass at least 1-kV CDM ESD stress, which can generate an ESD current with peak current value about 15 A within a rise time less than 200 ps[6].

#### (4) Transmission Line Pulse (TLP) System

The TLP system applies the voltage pulse to the device under test (DUT). The oscilloscope measures the voltage and current during the TLP stress, and then the source-meter measures the leakage under certain bias condition. The steps above are sequentially repeated with increasing TLP pulse amplitude until the device satisfies the failed criteria.

TLP is common system in ESD protection studybecause the system providesmore details about the I-V characteristic of the device. I-V curve measured by TLP systems can give an ESD protection design window to let IC designers choose the right device easily. ESD protection design window of ESD protection device is shown in Fig. 1.3 [7]. Trigger point represents the triggering of parasitical bipolar junction transistor (BJT), which is needed below the gate oxide breakdown voltage to ensure successfully protection. After trigger, the device gets into the snapback region. The lowest voltage after the parasitic device triggering on is called holding voltage. The holding voltage should higher than the normal operation voltage to accomplish a latchup free design [7]. Secondary breakdown current (It<sub>2</sub>) is the maximum current handling ability of the device. In other words, the device willbe fail as after It<sub>2</sub> point. The TLP result of It<sub>2</sub>level is proportional to HBM level.

Fig. 1.1 The equivalent circuit of the human body model ESD event [4].

Fig. 1.2 The equivalent circuit of the machine model ESD event [5].

Fig. 1.3 ESD protection design window of ESD protection device [7].

# 1.3 Thesis Organization

Chapter 1 introduces the motivation of this work, basic background knowledge of ESD protection design and the thesis organization.

Chapter 2 shows some common ESD protection devices and their characteristics in HV process. Furthermore, some restrictions and limitations of those devices and their applications have been reported. Then introduce some background knowledge of SOA which is one of the hot topics in high voltage process. Also report the trade-off between ESD and SOA. Those issues confine the ESD performance in high voltage applications. The following chapters try to find out the optimized solutions in high voltage ESD protection.

In Chapter 3, there are many different structures of nLDMOShave been realizedin 0.25-µm 60-V BCD process. Those devices' ESD robustness will be discussed. Furthermore, failure analysis has been down for some specific device structures.

In Chapter 4, investigating how the different layer and parameter affect the HVSCR and LVSCR. To prevent the latchup issue, many different method of increasing holding voltage have been discussed. All the devices are successfully verified in a 0.25- $\mu$ m 60-V BCD process.

Finally, the conclusions and some suggestions for future investigation have been indicated in Chapter 5.

# Chapter 2

# **Overview for High voltage ESD protections**

# 2.1Common ESD Protection Device in High Voltage Process

To protect integrated circuit to against ESD, IC designers would use several ESD protection devices in HV process. Some of them can protect themselves, which means it can both operate in normal condition and protect itself when ESD happens. Some of them are placed just to protect the integrate circuit without any function. The self-protection device is more straightforward. Some structure may not capable of being self-protected for ESD specification. Then additional ESD protection circuit is one of the possible solutions. In that case, the trigger voltage of ESD protection device should be higher than VDD. On the other hand, the protection mechanism must turn on below the breakdown voltage of the internal circuit or the gate-oxide breakdown voltage. The competition between the ESD protection circuit and output array usually have bad ESD result. Plus the area concern, self-protected device are preferable to HV technologies. This limitation also indicates that the holding voltage should be higher than the operation voltage and therefore cause high power dissipation and lower ESD failure currents[8].

Those ESD protection devices can be categorized into five main types below.

#### (1) Diode

Diode has been used as an ESD protection device for a long time. I-V characteristic of diode behavior during the ESD condition is depicted in Fig. 2.1(A). In the reverse bias region, once the voltage across the device is large enough to breakdown the junction, there forms the path to discharge thecurrent.

This kind of ESD protection devices would not snapback, which means the holding voltage is higher than the breakdown voltage. The success or failure of the affair is all due to the high holding voltage. Higher holding voltage ensures the latchup immunity but let the device has lower ESD robustness. The thermal capacity of the device per micron is fixed. So the higher holding voltage leads to the lower current level. Since the ESD robustness of diode per micron is rather low, enlarge the size of diode is one of the solutions to pass ESD criterion. But drawingthe diode device in a large size not only wastes the chip area but also causes a higher capacitance and leakage currents in normal condition.

#### (2) P-type MOS or FOD

The behavior of P-type devices during the ESD condition is similar to the reverse diode. I-V curve is shown in Fig. 2.1(B). The ESD robustness is very process dependent. In some process, P-type device has the higher ESD levels per micron than the diode. As a result, using the P-type device as an ESD protection can have both relative lower silicon area consumption and leakage with latchup immunity.

Because of the limitation of ESD design window, the non-snapback device such as PMOS and PNP FOD are usually used in high voltage process to fit those constrains of ESD protection window. In this kind of devices, the uniform turn on in such the large size is the main issue.

#### (3) nLDMOS or **N-type** FOD:

The N-type lateral DMOS (nLDMOS) is a common device for high-voltage output driver. nLDMOS can also be the protection device during the ESD due to its parasitic bipolar junction. When the voltage across the MOS is higher than the breakdown voltage of the reverse drain/body junction, drain leakage current

starts to increase apparently due to the avalanche generation. The voltage corresponds to 1-uA leakage current is defined as the breakdown voltage. After breakdown, the LDMOS acts like a diode in reverse bias region. The peak of electrical field lies on the interface between HVPW and HVNW. The voltage across the MOS keeps increase until the avalanche generation current through the junction of body and source is large enough to forward bias the parasitic diode between body and source. Once the parasitic NPN junction turns on, the voltage across the device is clamp down to the holding voltage. This is called device snapback. I-V characteristic behavior of nLDMOSin ESD condition is depicted in Fig. 2.1(C).

In the last two decades, some studies show that nLDMOS ESD robustness is not good enough in the results of some issues such as Kirk-effect-induced holding voltage lowering, multi-finger non-uniformity issue, or low breakdown voltage due to isolation oxide charge trapping [9], especiallyin some applications. Plus, the large difference between the trigger voltage and holding voltage leads to multi-finger non-uniformity issue. As one finger of the nLDMOS turns on first, this fingers would get into the snapback region immediately and pulls down the voltage. Then the electrical fields of the other fingers are too low to turn on the other npn bipolar transistors any more [10]. Commonly this is attributed to non-uniform turn-on behavior. Some techniques have been introduced to improve the ESD robustness of nLDMOS by enhance the uniformity of the multi-finger, such as high-resistance-body shallow trench isolation (STI), source ballasting, substrate/gate biasing [11], weakly snapback method, and so on [12]. The main concept of those techniques are reducing the difference between trigger voltage and holding voltage of the parasitic junction and allocating the current path more uniform. Take the field-oxide device (FOD)structure for example. Nowadays,

somesmart power technology are used N-type FODas test structures for high voltage pin applications [2], which can force the parasitic junction shows up easier.

Tough the stand-alone nLDMOSin high voltage process doesn't have good ESD robustness. Gate-gounded-NMOS is still widely used as ESD protection device due to straightforward implementation and relatively sufficient high current capability[9]. To pass the ESD criterion, it still needs some layer optimization and parameter modulation.

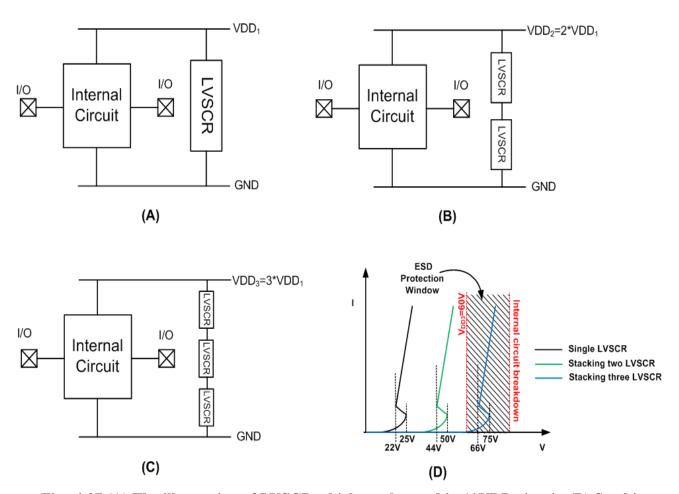

# (4) **Device with SCR path**

I-V characteristic behavior of SCR-basedstructure is shown in Fig. 2.1(D).SCR device is known as an efficient device for electrostatic discharge (ESD) protection since it can have the highest ESD robustness in the smallest layout area. Their excellent clamping capability and high ESD robustness allow designing efficient. On the down side, most of SCR-based protections exhibit low holding voltage, which makes them prone to latchup issue. Application of the SCR device in HV technology will further deteriorate its latchup risk more seriously because of the high supply voltage operation. As a result, mistriggering of the embedded SCR imposes new reliability concerns during normal circuit operating conditions, particularly in some applications that require both high-current and high voltages at the same time [8]. The latchup event could lead to integrated circuit malfunction or even permanent destruction. The basic criterion to improve latch up immunity is to increase the holding voltage above the normal operation voltage to reach latchup-free state. The simplest improvement method is to increasethe spacing from anode to cathode, which directly increase the resistive of voltage drop across SCR [13]. Modulation of the parasitic BJT emitter injection efficiency by reducing the emitter area is another solution. Some approaches are going to adjust the well/substrate shunt resistances [14]. Using the circuit solution, like connecting a diode string in series to raise the holding voltage, is another option.

Once the holding voltage of SCR is higher than the normal supply voltage, it will be free from latchup issue. But increasing holding voltage may decrease the ESD robustness due to the higher heat generation during ESD current discharging. Therefore, it is still a challenge to design an ESD-robust and latchup-immune SCR device within small layout area.

## (5) RC-BigFET

If there is a big MOS in the internal circuit, using the propertyof RC delay to drives the big MOS may become an option of ESD protection. Unlike those four methods, which is mentioned above, this method turns on the MOS device itself instead of breakdown the parasitic junction to shunt the ESD current. Comparing to the operation, the ESD stress happens in a short time. Choosing the proper resistance and capacitance in the circuit can let the delay time fall within the region between the time domain of operation and ESD condition. Thus, RC delay mechanism would let the BigFET turning on to shunt the ESD current and keep off in normal condition. This dynamically triggered MOS transistormethodis commonly used in low voltage process. In high voltage process, the large area consumption of resistance and capacitance is one of concerns that make this method has relative low ESD level per micron. Also, gate coupling is another issue in high voltage applications. Using this protection method in real high voltage application still needs more devices studied and simulation.

Fig. 2.1 The simplified I-V curves of the common ESD device. (A) Diode, (B) P-type MOS or FOD, (C) gate-grounded nLDMOS or N-type FOD, (D) Device with SCR path.

# 2.2LatchupImmunity Issue in HV Process

Ideal ESD device should have low trigger voltage, high immunity for latchup and enough margins for reliability under high voltage operation. In many HV process, the gate-grounded nMOShas much lower holding voltage than the maximum supply voltage, not to mention the embedded SCR structure. The latchup issue is one of the most critical issues in high voltage process, especially for the power camp ESD device which is placed between VCC and VSS. The worst case is that the device cannot recover without a renewed power-up cycle. In the worst case, the high DC supply current could damage the device. That is, the latchup issue prevents the application of snapback device as a power clamp device.

There are two necessary conditions for latchupoccurred. One is that the power supply current should be large enough to support the holding condition [15]. Reducing the operation current can have more latchup immunity. But in some application, lower operation current would reduce the performance. The other condition to immune the latchup issue is that holding voltageshould be higher than the supply voltage (VCC). The difference of those two defines the latchup protection window. The basic criterion to improve latch up immunity is to increase the holding voltage. Some techniques have been proposed to increase the devices' holding voltage, such as using deep trench between drain and source or modulation of the layout spacing[1]. Once the holding is above the power supply voltage, the device would reach latchup-free state.

#### 2.3 The Trade-off Between ESD and SOA

#### 2.3.1 Introduction to SOA

Safe operating area (SOA) isone of the most important factors affecting device reliability[16] because the power devices may have to operate under the condition of high voltage and high current. The SOA region defines the limitation of operating condition including voltage and current. That is, operating outside SOA region may cause some damaging of the IC products.

SOA can be roughly sorted into forward bias SOA (FBSOA) and reversed bias SOA (RBSOA). FBSOA analyzes the on-state devices and RBSOA studies the off-state devices. Unclamped inductive switching (UIS) test presents high current and high voltage across a device when it is off, so it is classified as the reverse-biased SOA (RBSOA) [17]. FBSOA is decided by the factors such as manufacture, material, package, and device structure. Electrical SOA (eSOA) and thermal SOA (tSOA) are two different mechanisms. Most of the time, electrical SOA (eSOA) boundary is important due to thermal effect is not strongly involved during operation [18].

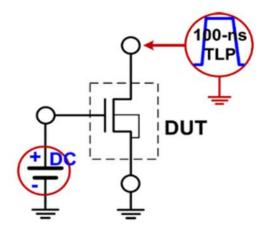

For the device optimization, the concept of safe operation Area (SOA) under pulsed stress conditions is important. Normal operation defines the minimum form of SOA required for the qualification of LDMOS device [3]. To minimize the effect of device self-heating, device under tests (DUTs) are usually stressed by the pulses with a short pulse width. A  $50-\Omega$  transmission line pulsing (TLP) system that delivers square pulses with 100-ns pulse width is usually adopted for the measurement of eSOA[8]. The setup of eSOA measurement is shown in Fig. 2.2 [19].

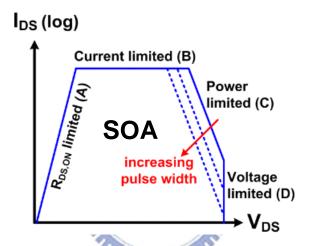

The SOA specification is illustrated in Fig. 2.3 [19]. The SOA is formed by four curves which define respectively as follows.

#### (1) Line A

Line A is limited by the turn-on resistance ( $R_{DS,ON}$ in Fig. 2.3). Decreasing the turn-on resistance, which causes the slope increase, can have larger SOA.

#### (2) Line B

All devices have current carrying capability either from device itself or the wire bonding.

### (3) Line C

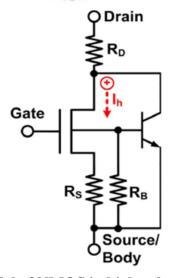

Line C is the physical limitation. This line is determined by the current and voltage across the device with short pulse width by TLP system under fix TLP pulse width and gate bias. The equivalent circuit model of a HV NMOS is shown in Fig. 2.4 [18]. R<sub>D</sub>, R<sub>S</sub>, and R<sub>B</sub> aredrain, source, and body (parasitic) resistors, respectively. If the bias between base and emitter junction, which is generated by the current I<sub>h</sub>, is larger enough, the BJT would be triggered on. When generated heat by P=I×V across the device excess its physical tolerance, the device would fail. Connecting the failure point with different gate bias forms the line C (like in Fig. 2.5).

Because those factors ( $R_D$ ,  $R_S$ , and  $R_B$ ) have positive thermal coefficient. When pulse width increases, Line C moves downward due to the increasing device self-heating and the electrothermal coupling. Furthermore, the increasing TLP pulse width would degrade the SOA boundary.

#### (4) Line D

Line D is defined by the maximum voltage (BV<sub>DSS</sub>) of device.

Fig. 2.2 The test setup for eSOA measurement by 100-ns TLP pulses [19].

Fig. 2.3A diagram showing SOA of a high voltageMOSFET[19].

Fig. 2.4Equivalent circuit model of NMOS in high voltage process, shown with the parasitic bipolar junction [18].

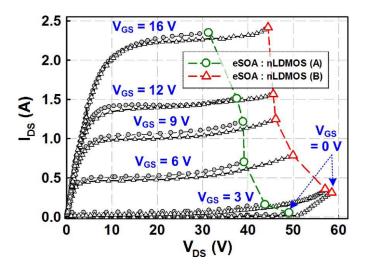

Fig. 2.5Measured SOA boundaries of two nLDMOS transistors by 100-nsTLP pulses[18].

#### 2.3.2 Trade-off between SOA and ESD

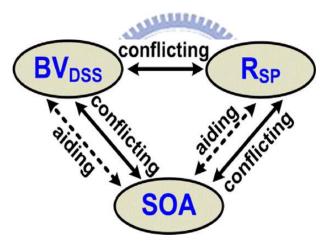

There are three factors which can affect I-V boundary of safely switch. These factors are BV<sub>DSS</sub>, R<sub>SP</sub> and SOA which is known as a design triangle of HV device as in Fig.2.6. Generally, the breakdown voltage and on-resistance is a well-known trade-off in HV process. Plenty of works have addressed and analyzed the tradeoff of SOA enhancement, and turn on resistance and breakdown voltage [17].

A wide SOA can enhance device reliability under load condition. Plenty of works aim in achieving the highest breakdown voltage, lowest turn on resistance, and the widest SOA for a given device size [17]. A wide SOA can sustain the high voltage and high current at the same time that happens across a power MOSFET during the circuit operations with the switching of reactive loads. Aspiring for SOA improvement becomes an increasingly important factor. Higher breakdown voltage would lead to the wider SOA. But as an ESD protection device, higher breakdown voltage may let other internal device be damaged before it shunts the ESD current. Nowadays, some process integrations use a heavily doped body region, an adaptive drift implantation, or a thick plated copper layer to improve intrinsic SOA. The previous study indicates

that additional P-type body layer, which is added to elevate the doping concentration of P-type well, can have the wider SOA when comparing to the regular nLDMOS structure.But this improving may decrease ESD robustness.For example, a heavily doped P-body region, which increases the doping concentration of P-type well in the source side, can also reduce the equivalent resistance of R<sub>B</sub> in Fig. 2.4. Reducing R<sub>B</sub> would result in high power dissipation and relatively weak ESD performance due to the parasitic BJT is difficult to turn on [14].That is, many high-voltage devices suffer from early failure and limitation due to the BJT driven instability [3]. Itisimportant to have a deeper investigation on the structure of HV device to get win-win solution for SOA and ESD robustness.

Fig. 2.6The design triangle of power semiconductor devices[18].

# **Chapter 3**

# Parameter Investigation for Self-Protected LDMOS Devices in High-Voltage Process

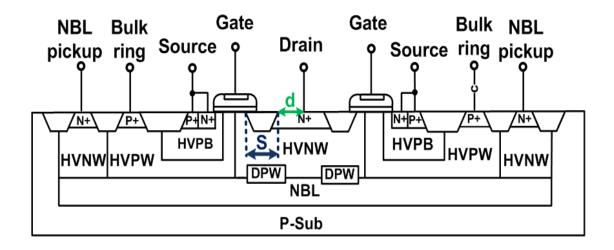

# 3.1 Standard LDMOS Structure in 60-V 0.25 µm BCD Process

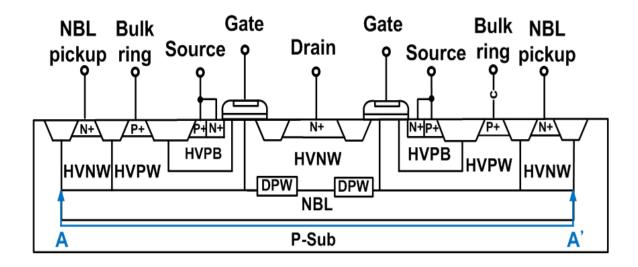

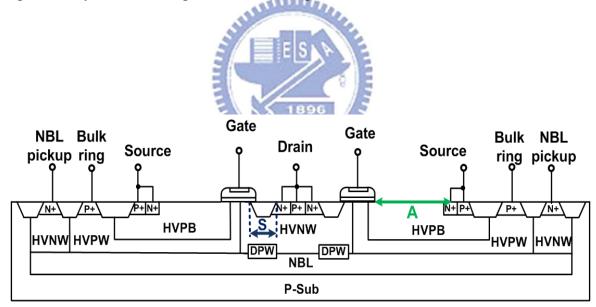

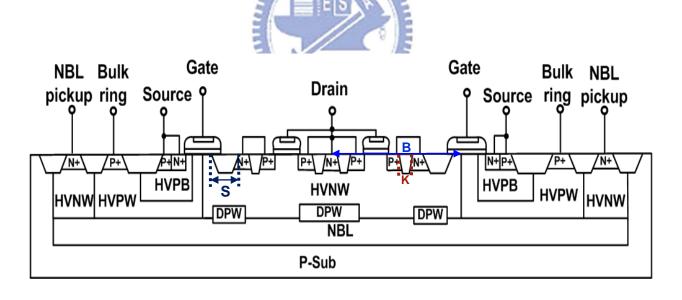

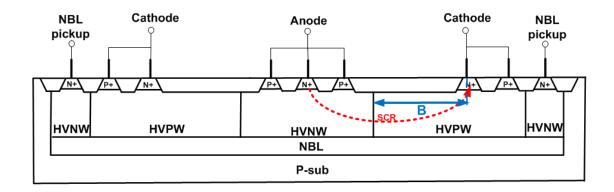

High voltage and high current operations are common requirements for semiconductor devices in HV ICs. To be tolerant of high voltage across the device, there are many different light doping implants and specific structures in different HV process. In 60-V  $0.25\mu m$  BCD process, the cross-section view and top view of standard nLDMOS which foundrygives as a layout sample is shown in Fig. 3.1 and Fig. 3.2, respectively. In Fig. 3.1, the HV device is surrounded by N-buried layer (NBL) to separate HVPW and P-substrate (p-sub). So bulk ring at every source region is required to bias HVPW, the bulk side of the nLDMOS. Each 60-V nLDMOS device isolates from other devices by HVNW and NBL. The channel lengths are defined by the overlapping region of p-body and the poly gate. This device is suggested to be operate in voltage region  $V_{DS} = 0 \sim 60V$  and  $V_{GS} = 0 \sim 5V$ .

One of the special implant layers of standard nLDMOS is the P-body layer. The P-body region is a highly doping layer than HVPW. The gradually doping tech(p+-p-body-HVPW) in the source side have been used to enhance the SOA region by increasing the equivalent base doping concentration of the parasitic bipolar junction transistor (BJT). Besides, the standard nLDMOSin60-V 0.25µm BCD process uses shallow trench isolation(STI) between N+ drain and poly gate instead of the traditional field oxide (FOX) to shun the bird's peak effect. This STI region can avoid the field crowding in the surface region near the drain of nLDMOS, which

increases the device's breakdown voltage. That is, the device can have a shorter length of the drift region is sufficient to maintain the required breakdown voltage.

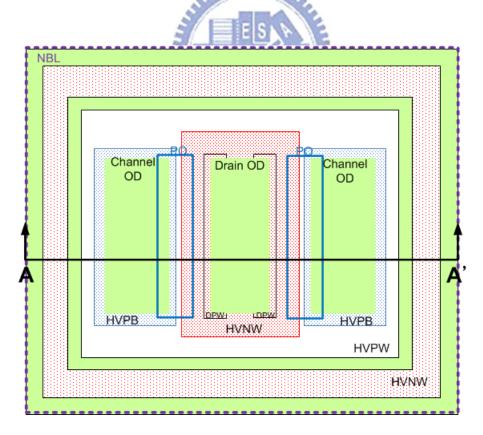

nLDMOS's inherent lateral design makes it compatible with conventional CMOS process[20]. Hence, it would be perfect if nLDMOS could both operate in the normal situation and protect itself during ESD. To analyze the characteristic of standard nLDMOS under HBM ESD stresses, TLP system with 100-ns pulse width is used [21]. The TLP result of the standard nLDMOScell with the minimum rule is shown in Fig. 3.3. The total width of the device in this section is 800 µm.

The breakdown voltage of standard nLDMOS, which is given by foundry, is 75 V. The breakdown voltage (75 V) is around 1.2 times of supply voltage (60 V), which meets the common criteria in high voltage application. So, the standard device can be used as the operation device, but it is not robust enough to protect itself during the ESD condition. According to the TLP result, the ESD level of this device is less than 300 mA. This device would not get into snapback region until 91V. Actually, this device cannot successfully snapback before it failed. That may be the reason why the device failed in such a low ESD level.

The HBM level is around 0.5kV, which meet the experiments result of TLP test. Apparently, the ESD level of the standard nLDMOS in this 60V process is not robust enough to be the self ESD protection device. There still need more optimize design to improve the ESD performance. In the following section, this thesis indicates many different parameter modulation, source engineering and drain engineering. Optimize the nLDMOS structure to get the acceptable performance in both operation and ESD condition.

Fig. 3.1 The cross-sectionalviewof standard nLDMOS in a 60-V BCD process.

Fig. 3.2 Thetop view of standard nLDMOS in a 60-V BCD process.

Fig. 3.3 I-V characteristics of standard nLDMOS with minimum rule of all the parameter, which is measured by 100-ns TLP system.

# 3.2Parameter Investigation of Stand-alone nLDMOS

There are many different ways to enhance the stand-alone nLDMOS's ESD robustness. Some may change the concentration of the doping profile or adding other different layers to change the electric field or charge distribution [22], [23]. Take the deep drain profile engineering for example, in the deep drain case, a deep n+ sinker was implanted below the drain junction with the same effective drift length of the shallow drain one. The sharply localized temperature increases near the drainjunction was thus avoided. Hence, the ESD level of a deep drain device is higher than the shallow ones [22]. The changing layer method is not flexible for applications because the junction depth and concentration is controlled by the foundry. Instead of changing the layer, changing some layout parameter may be another choice. Stretching some parameter of the devices to make the ESD current flow deeper or using a large area to sustain the ESD currentare common techniques in ESD protection design. But

enlarging area need to consider the uniformity issue. To increase the efficiency of ESD performances per micron, embedded SCR structure inside nLDMOS is a popular way to increase ESD robustness. This chapter shows some experimental results for those ideas that have been mention above.

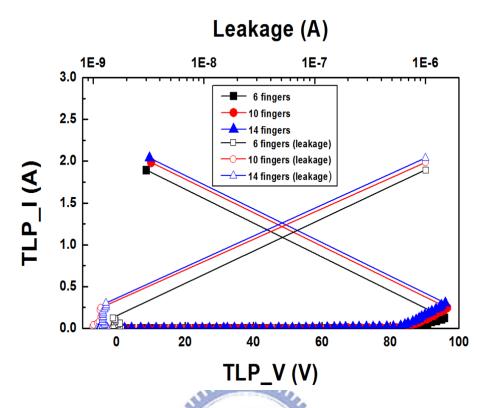

### 3.2.1 Stand-alone nLDMOS with different total width

The stand-alone LDMOS has poor ESD robustness. To improve the ESD level, the conventional method is to increase the device total width though it would need a large area for ESD protection. There are three kinds of nLDMOS with different total widths are studies in this section (480µm, 800µm and 1120µm, respectively). Those devices are almost the same with the standard cell that foundry gives as a layout samples except that the parameter between contacts to the active region edge. To avoid the large current go through the active region, the space between contacts to the active region has been lengthened to 1µm. Each fingeris 80µm in those devices. So the numbers of three different total widths are 6, 10 and14 respectively. The TLP measurement results are shown in Fig. 3.4.

According to the TLP result in Fig. 3.4, the increasing of the total width does increase the maximum current-handlingability (the secondary breakdown current,  $It_2$ ). In fact, increasingfour fingers would increase  $I_{t2}$  level around 100mA. Also, the resistance of the I-V curve in Fig. 3.4 decreases when the total width increases. For those two reasons, non-uniform turn on may not be the main issue of the stand-alone nLDMOS. But even increasing the total width to  $1120\mu m$ , the  $It_2$  level is still not good enoughto protect itself. So, enlarge the total width of nLDMOS would not be an efficient wayto get higher ESD level.

Fig. 3.4 The I-V characteristics of nLDMOS which has different number of fingers.

(Each finger is 80µm)

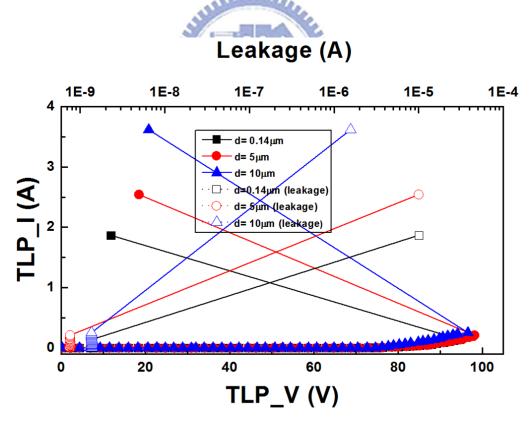

3.2.2Stretchparameter of STI space and drain diffusion region

One way to get better ESD level is to reduce the electric field or local heating in the surface. Drain side engineering is one of the popular ways. Some previous studies use the TCAD simulation to prove that if the isolation between the drain and gate is not large enough, then most current crowded near the surface [10], [24]. Stretching some space in the drain side would let the region, where hot carrier generates, far from the channel. So the currentscan go deeper and more uniform, which also help the parasitic bipolar be triggered [24].

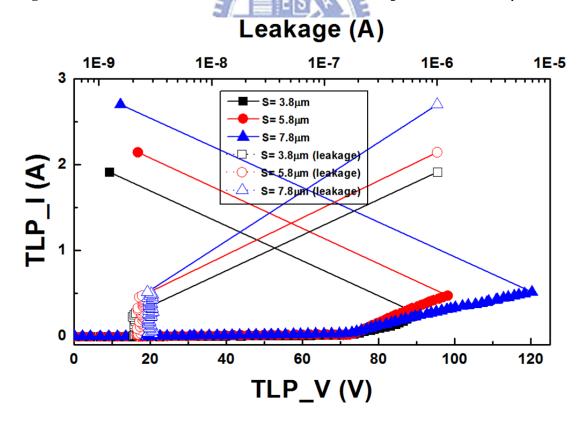

In this section, the parameter of shallow trench isolation (STI) space and drain diffusion region have been studied. Changing the space between active region and the contacts in the drain side is marked as the parameter d in Fig. 3.5. The TLP results of

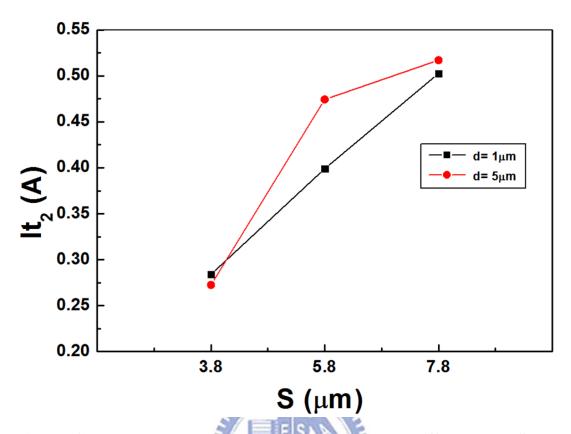

different parameter d are shown in Fig. 3.6. The other parameter S of nLDMOS in this case is kept at 3.8µm which is as same as the length of the device in section 3.2.1. There is no significant improvement on ESD robustness of nLDMOS with different d according to Fig. 3.6. Then consider the parameter of the STI space, which is markedas the parameter S in Fig. 3.5, Fig. 3.7 and Fig. 3.8 are the measurement results of the three different S (which is 3.8µm, 5.8µm, and 7.8µm, respectively) in different parameter d.Figure 3.9 shows the comparisons of It<sub>2</sub> levels among the single devices under different dand S.When d is 1µm,there has a linear relationship between  $I_{t2}$  level and the parameter S. When the d parameter changes to 5 $\mu$ m, the relationship between  $I_{t2}$  level and the parameter S also changes. The  $I_{t2}$  level does not have large difference when the parameter S is 5.8 µm, and 7.8 µm. Considering the size and the ESD performance, the device, which d equals to 5µm and S equals to 5.8µm may be the best solution among those six devices. Even though stretchingthe parameter S and d in the sectiondo increase the ESD performance, the device still cannot pass the HBM 2kV level. According to Fig. 3.7 and Fig. 3.8, none of those devices can get into snapback region before it failed maybe the reason. Changing the spacing can delay the damage inthe channel of nLDMOS, but it can't help the device snapbacks. If the device doesn't get into the snapback region, high voltage across the device may cause thethermal damage and resultin the low It<sub>2</sub> levelin  $0.25\mu m$  60V process.

Fig. 3.5 The cross-sectional view of standard nLDMOS in a 60-V BCD process with parameter S and d.

Fig. 3.6 I-V characteristics of nLDMOS with different parameter d. (d=0.14 $\mu$ m, 5 $\mu$ m and 10 $\mu$ m, respectively.)

Fig. 3.7 I-V characteristics of nLDMOS with different parameter S (d=1 $\mu$ m).

Fig. 3.8 I-V characteristics of nLDMOS with different parameter S (d=5μm).

Fig. 3.9 CompareIt<sub>2</sub> levels among the single devices under different dand S.

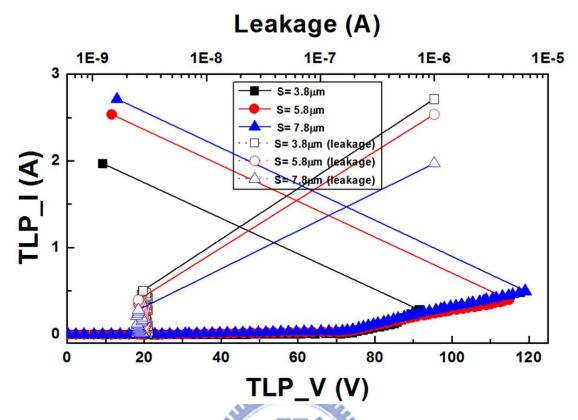

### 3.2.3Change the NBL type of stand-alone nLDMOS

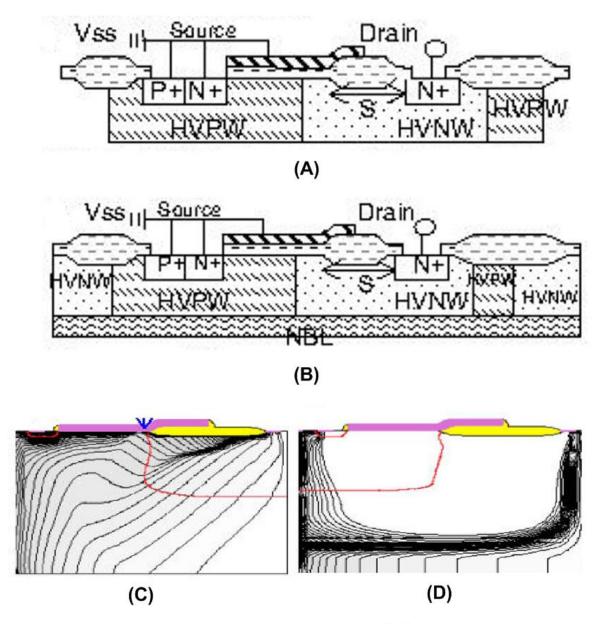

The bipolar's unable to turn on and current crowding effects are the rootsthat cause the device failed at the low-voltage ESD zap. Separating the bulk away the source can help the parasitic bipolar be triggered on easier by increasing the parasitic resistance between source and bulk. This method is not good for ESD improvement due to the space between source and bulk should be large enough [10]. Moreover, in reference [24], the most currents flow from drain to NBL underneath and then into source by the TCAD simulation which is shown in Fig. 3.10. Hence, there comes an idea that splitting NBL into little pieces. Changing the shape of NBL can help to control the current distribution. If the device failed because of current crowed, splitting NBL may force the currents distribute more uniformly. There are three types of NBL are studied in this section. The top views of these three types device are

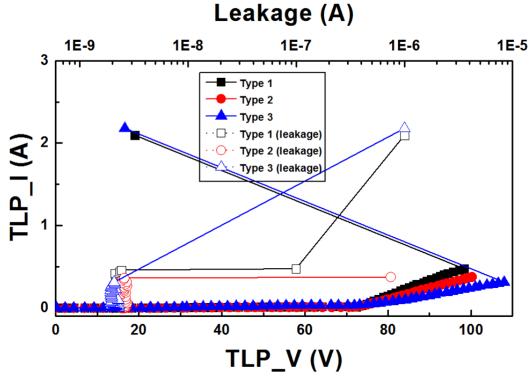

shown from Fig. 3.11 to Fig. 3.13. In Fig. 3.11, the whole device is covered by NBL layer. In Fig. 3.12, the one NBL splits into four fingers with the minimum space between two fingers. Moreover, there are eight NBL fingers in Fig. 3.13. The spacesbetween two fingers are kept in the minimum rule. The TLP measurement results of these three types of NBL with different STI spaces are shown in Fig. 3.14, Fig. 3.15 and Fig. 3.16, respectively.

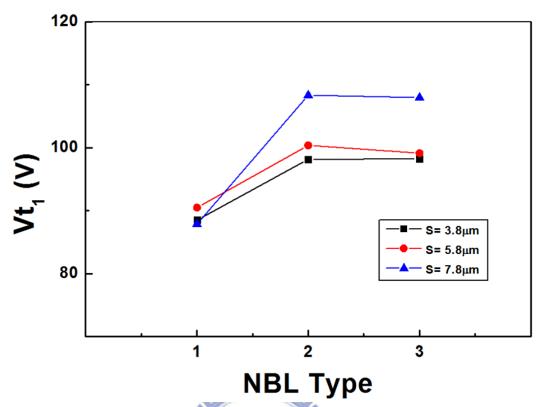

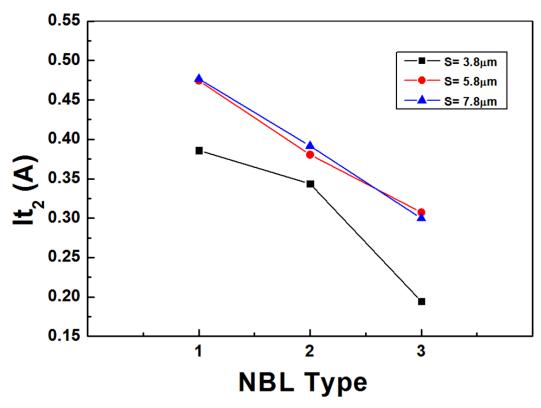

Comparing the trigger voltage (Vt<sub>1</sub>) of three different types of NBL is shown in Fig. 3.17. With fully isolated NBL, the device has the lowest trigger voltage. The trigger maintains the same with different parameter S. No matter how many fingers that NBL splits into, the trigger voltage of these two cases are both higher than that of the full isolation in the same parameter S. Splitting one NBL layers into many fingers can change the devices' trigger voltage. In other words, changing the layout style of NBL can change the devices' triggering point. Non-fully isolate NBL can have a higher trigger voltage which may have better SOA and more weakly snapback. Fig. 3.18 indicates the comparison of maximum current handling ability (It<sub>2</sub>) of three different types of NBL. The It<sub>2</sub> current reduce with the finger increased. The number of the fingers increases means the total area cover by NBL layer decreases. Through this experimental result, splitting the NBL into little pieces can't improve the ESD level. To improve the ESD performances, more investigations are needed.

Fig. 3.10 (A) and (B) Cross-sectional view of LDMOS (S=5 $\mu$ m) in 40V process without and with isolate NBL.

- (C) The current flow contours of LDMOS without NBL.

- (D) The current flow contours of LDMOS with NBL.[24]

Fig. 3.11 The top view of nLDMOS which is covered by one NBL layer (Type 1).

Fig. 3.12 Thetop view of nLDMOSdevice which is covered by four NBL fingers (Type 2).

Fig. 3.13Thetop view of nLDMOS device which is covered by eight NBL fingers (Type 3).

Fig. 3.14 The TLP results of the devices with three types of NBL. (The space of STI is 3.8 $\mu$ m).

Fig. 3.15 The TLP results of the devices with three types of NBL. (The space of STI is 5.8µm).

Fig. 3.16 The TLP results of the devices with three types of NBL. (The space of STI is 7.8μm).

Fig. 3.17 Compare the trigger voltage (Vt<sub>1</sub>) of three different types of NBL.

Fig. 3.18 Compare the maximum current handling ability ( $It_2$ ) of three different types of NBL.

### 3.3 Investigation on Different Typesof Embedded SCR in nLDMOS

#### 3.3.1 Embedded SCR structure in stand-alone LDMOS

There are several solutions proposed to increase the ESD robustness of nLDMOS. The most popular way to improve ESD robustness is inserting silicon controlled rectifier (SCR) into the LDMOS [25],[26]. SCR is known as an area-efficient method to improve ESD robustness. But it may have higher trigger voltage than that of stand-alone LDMOS. Under ESD stress, since the stand-alone nLDMOS cannot be triggered with many different parameter and different layout style which has been reported in section 3.2, the embedded SCR LDMOS will fail before the embedded SCR is triggered on to discharge ESD current. The following work combines the concepts of changing thelayout space and embedded SCR inside LDMOS todevelop some new structure of self-protected LDMOS

# 3.3.2 Adding more implant layer in the source side

The bipolar's unable to turn on and current crowding effects are the roots of the HV-LDMOS failed at the low-voltage ESD zap. If the two causes can be eliminated, the ESD performance of the HV-LDMOS will be improved. To decrease the trigger voltage, several ways, such as increasing the emitter space and adjust the well/substrate resistance of the MOS, had been studied in previous work.

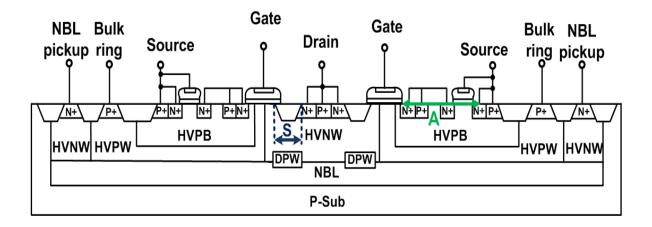

Although separating the bulkawaythe source can increase the resistance, the ESD performance of the device still cannot be improved it does not have enough space between source and bulk[10]. In this process, the high doping concentration of HVPB layer maybe the critical reason that cause parasitic BJT cannot turning on. Therefore, source side engineering can be considered. Fig. 3.19 is the embedded SCR structure with a larger space between source contact and gate. This structure is named S-pn-ref. Increasing the resistance between the substrate and

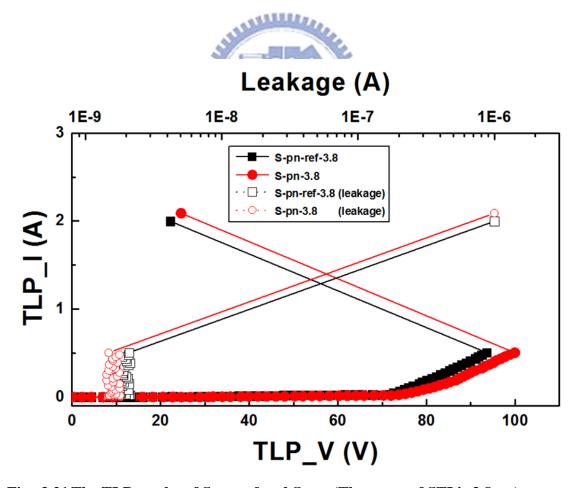

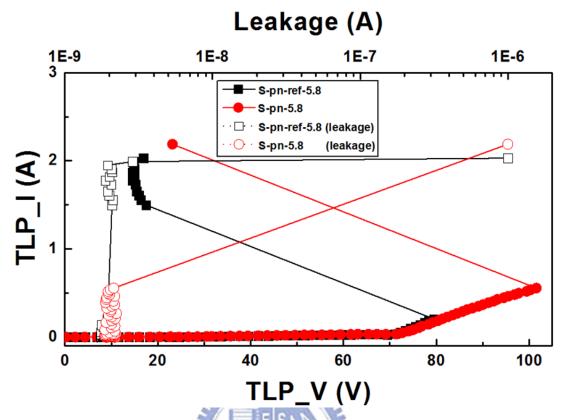

bulk by increase the space from source contact to HVNW edge may be a good solution for helping the parasitic bipolar be triggered. Fig. 3.20 is a new proposed structure, named S-pn. This device has an additional p+ and n+ implant between the source contact and gate. The total area that device occupied of those two structure are the same. On the other hand the space between source contact and gate, which is the parameter A is remain the same. Fig 3.21 and Fig. 3.22 compare those two structures with different S. Though in Fig. 3.21, two devices are not snapback before the device failed. But when the parameter S is large enough (S=5.8µm), the S-pn-ref can get into a snapback region successfully (Fig. 3.22). Adding more p+ and n+ implants would let the device more difficult to be triggered. This argument will be discussed particularly in a more simple structure in chapter 4.

Fig. 3.19 The cross-sectional view ofembedded SCR structurewith larger parameter A in a 60-V BCD process (S-pn-ref).

Fig. 3.20 The cross-sectional view of new proposed embedded SCR structurewith source side engineering in a 60-V BCD process (S-pn).

Fig. 3.21 The TLP results of S-pn-ref and S-pn. (The space of STI is 3.8μm).

Fig. 3.22 The TLP results of S-pn-ref and S-pn. (The space of STI is 5.8μm).

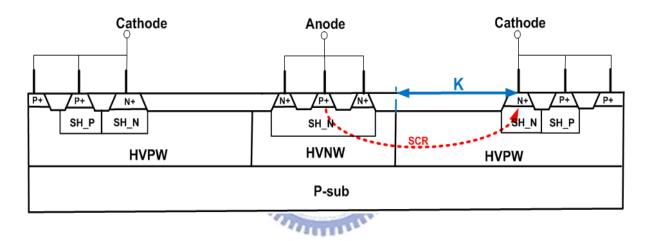

## 3.3.3 Adding more implant layer in the drain side

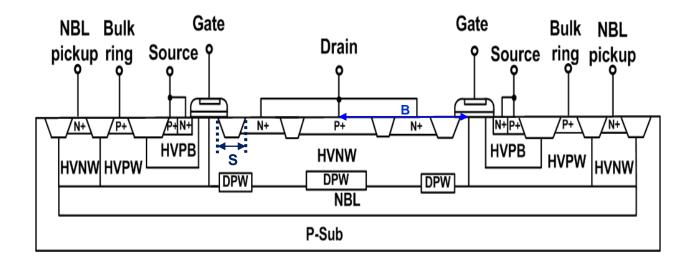

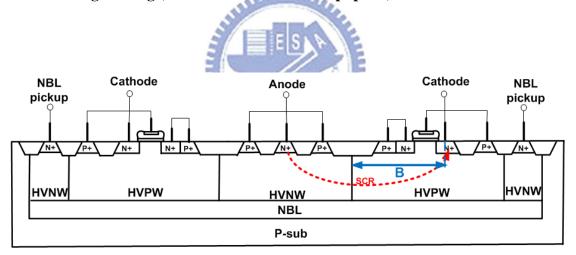

The drain-side engineering has attracted many people to research HV devices recently. It prevents the kirk effect and avoids reliability problem[22],[27]-[29]. Somestudies indicate that higher dosage can improve the reliability of nLDMOS transistors. Also, the junction depth increasing in the drain-side will result in the higher holding voltage of an nLDMOS[30]. Some of them report that filamentation can be avoided in conventional LDMOS structure in the snapback region when the ballast resistance during snapback is large enough. During the experimental results of the nLDMOS device in 0.25µm 60V BCD process in section 3.2.2, only stretching the layout parameters in drain region can'ttrigger on the parasitic bipolar junction, not to mention the embedded SCR structure. Fig. 3.23 is named LDMOSSCR, which is modified from LDMOS byinserting p+ implantation region in drain active region

tocreate the parasitic SCR path. Also rearrange the implant order to meet the DRC rule. EmbeddedSCR inside LDMOS is the simplest way to improve ESDlevel if the parasitic device can betriggered on before it failed. Both stand-alone LDMOS and embeddedSCR structure failed before snapback in this high voltage process, so thecurrent-handling ability of those two devices isvery low. Besides, the breakdownvoltage of the embedded SCR LDMOS is down to 59V, which is lower than the maximum supply voltage of 60V. The reason of this phenomenon may be the increasing of minority carrier. The p+ implantation provide some hole in the drain side in the embedded SCR structure. The punch through of the hole may result in the lowering of the breakdown voltage and make the device can't be used in the normal situation.

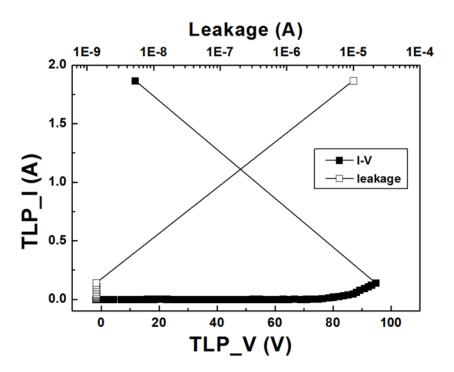

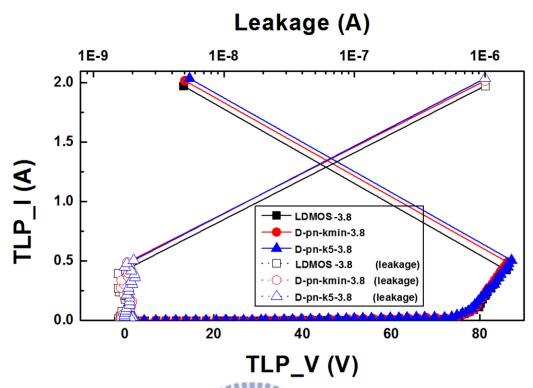

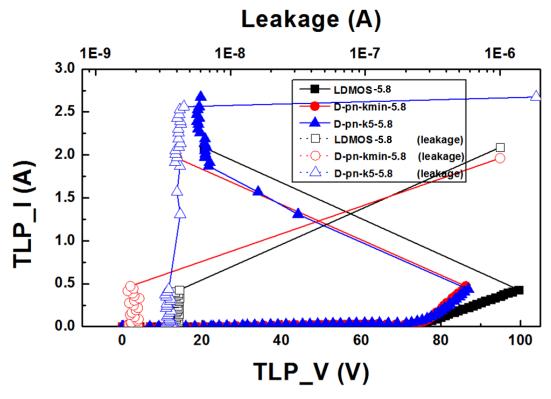

Fig. 3.24 is a new proposed structure inserting more n+ and p+ implant layers between the gate contacts and STI. In this structure, there is adummy gate between two p+ regions for reducing thetotal space and increasing the gain of the parasitic BJT.To make sure that the parasitic pMOS being kept off, thedummy gate is connected to the drain. The new proposed structure is fully process compatible to high voltageprocess without additional mask layer or process step. Those two structures have the same parameter B. The TLP measurement results of drain engineering in different parameter S is shown in Fig. 3.25 and Fig. 3.26, respectively. When the parameter S is equal to 3.8μm, there is no notable difference between drain-extend nLDMOS and the new proposed one. But when the parameter S is 5.8μm, the new proposed device sometimes can be triggered on. The I-V curve in Fig. 3.26 indicates that new proposed structure can be triggered on around 86V and get into the snapback region. Separating the space of additional p+ and n+ implantation layers would let the device get into snapback region stably. The device that additional p+ layer is close to the n+ layer (which the parameter k=0μm) is called D-pn-kmin. The device with

separating p+ layerand n+ layer (which the parameter  $k\neq 0\mu m$ ) is called D-pn-k5. This optimized structuresuccessfully reduces the trigger voltage by doing those drain engineering. Consequently, it has a higher It2 (> 2A) than others. Moreover, the breakdown voltage of this device maintains in 75V, which is similar to the stand-alone LDMOS. This device can be used as a self-protected ESD device in 60 V circuit. The HBM robustness of the new proposed device is also improved. The measurement result of the stand-alone LDMOS is 1.5kV. The news structure can pass more than 2kV level which is the best one among these three devices investigated in this work.

There are two ways to explain the improvement in the new proposed structure. First, the current path of the new proposed structure wouldgo deeper than the LDMOS-SCR. Because the NBL is higher doping concentration layer compare with HVNW. The deeper of current distribution would results in the larger total current. Those current would let the parasitic BJT be trigger easier and faster. The more time or energy that the device needed to snapback the more easily result in unrecovered thermal failure. That prevents the new proposed structure failed before the parasitic BJT path has been triggered on. On the other way, the new proposed structure would increase the ESD robustness by reducing the surface electrical field. When inserting the p+ implant layer in the drain side, there would form a neutral region in the interface between p type and n type doping. This region can also avert the electrical field to distribute more vertically. High surface electrical field may stress the gate oxide and cause the unrecoverable damage. These physical understandings can explain the reason why the new proposed structure successfullysnapback and having better I<sub>12</sub> levels when comparing to other devices. Plus the modulation of the parameter k, the device named D-pn-k5-5.8 has better ESD levelamong other devices in this chapter.

Fig. 3.23 The cross-sectional view of embedded SCR structure in a 60-V BCD process (LDMOSSCR).

Fig. 3.24 The cross-sectional view of new proposed embedded SCR structurein the drain sidein a 60-V BCD process (D-pn-kmin and D-pn-k5).

Fig. 3.25 The TLP results of three different type of device with drain-side engineering. (The space of STI is  $3.8\mu m$ ).

Fig. 3.26 The TLP results of three different type of device with drain-side engineering. (The space of STI is 5.8µm).

### **3.4 Discussion and Summary**

## 3.4.1 Discussionand failure analysis

In this work, the parasitic BJT of 60-V nLDMOS still cannot be triggered on even ifthe space of STI or the space between the drain contacts to gatestretches. The detail of the experimental results of parameter S and d have been summarized in Table.

3.1. The ESD levels included It<sub>2</sub> and HBM levels have a little bit improved. Because NBL is a highly doping N-type layer, which constructs a low impedance current path to shunt the ESD current through the vertical NPN BJT, changing the layout style of NBL causes different trigger voltage without changing the device breakdown voltage. Because those devices with different type of NBL can't get into the snapbackregion, the It<sub>2</sub> level decreasesas the trigger voltage increases. That is, the total slot area of NBL and the It<sub>2</sub> level are roughlyininverse proportion. However, stretching the source active region would turn on the parasitic bipolar junction when S is enough large. Plus some additional implant layer between the source and gate will increase its trigger voltage in both S cases.

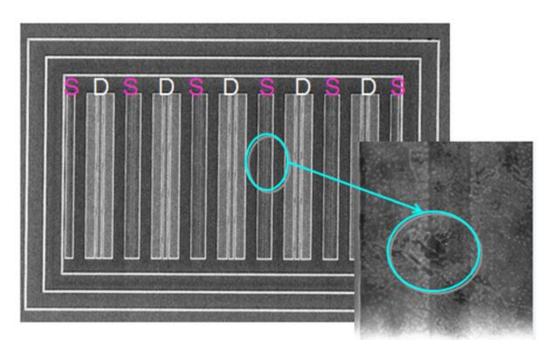

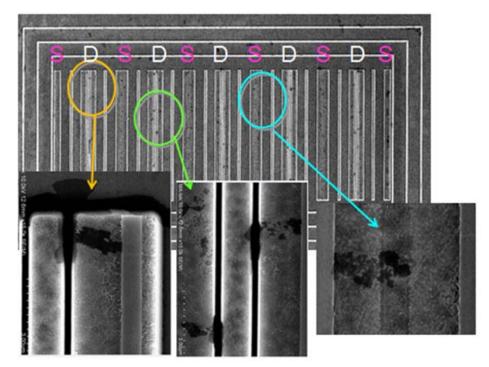

Even though stretching the space between drain contact and STI cannot let the parasitic BJT or SCR turn on, new proposed structure with large parameter S and drain side engineering can get into the snapback region before it failed. Consequently, it has a higher It<sub>2</sub>level than others. Thebreakdown voltage of the new proposed structure, which is embedded SCRin LDMOS with larger STI space (named D-pn-k5-5.8),is75V.That device maintains the same breakdown voltage as the stand-alone LDMOS (named LDMOS-5.8) in the same conditions (S=5.8μm, d=5μm).The human-body-model (HBM) ESD robustness of thefabricated devices are all characterized by the ESD tester. Themeasurement result of the stand-alone LDMOS is 1.5kV.The embedded SCR structure only passes 1kV during theHBM test. The new proposed LDMOS-SCR(named D-pn-k5-5.8) can passmore than 2.5kV level

which is the best one among thesethree devices investigated in this work. The failure analysis can also prove those physical understandings, which are mentioned in the last section. The SEM pictures of the embedded SCR LDMOS (LDMOSSCR-5.8) and the new proposed LDMOS-SCR (named D-pn-k5-5.8) structure after HBM testare shown in Fig. 3.27 and Fig. 3.28, respectively. In Fig. 3.27, the damage isn't obvious comparing to Fig. 3.28. This phenomenon may result from the low failure current. Conversely, the failure locations after HBM stress on the new proposed LDMOS-SCR is clear and uniform. Every finger has ESD damage in Fig. 3.28. The uniform ESD dissipation current causes the increase of the self-protection ability of the new proposed LDMOS-SCR during the ESD test.

All the experimental results are summarized in Table 3.2. The total width of each nLDMOS device in this chapter is 800 µm except the section 3.2.1.

Fig. 3.27 The SEM image of embedded SCR LDMOS device (named LDMOSSCR-5.8) after 1.5kVHBM test. (S=5.8µm case)

Fig. 3.28 The SEM image of new proposed device (D-pn-k5-5.8) after 2.5 kVHBM test. (S=5.8 $\mu$ m case)

TABLE 3.1

Summarize the ESD robustness of nLDMOS devices with different S and d.

|          | 1890                              | d=1 μm | d=5 μm |  |

|----------|-----------------------------------|--------|--------|--|

| S=3.8 μm | Breakdown voltage (V)             | 75 V   | 75 V   |  |

|          | Trigger voltage (V) 91 V          |        | 88 V   |  |

|          | It <sub>2</sub> level (mA) 278 mA |        | 378 mA |  |

|          | HBM (kV)                          | 0.5 kV | 0.5 kV |  |

| S=5.8 μm | Breakdown voltage (V)             | 75 V   | 75 V   |  |

|          | Trigger voltage (V)               | 114 V  | 96 V   |  |

|          | It <sub>2</sub> level (A)         | 404 mA | 480 mA |  |

|          | HBM (kV)                          | 0.5 kV | 1 kV   |  |

| S=7.8 μm | Breakdown voltage (V)             | 75 V   | 75 V   |  |

|          | Trigger voltage (V)               | 119 V  | 96 V   |  |

|          | It <sub>2</sub> level (A)         | 510 mA | 472 mA |  |

|          | HBM (kV)                          | 1 kV   | 1.5 kV |  |

TABLE 3.2

The TLP-measured results and ESD robustness with different embedded SCR devices

| Device name   | Breakdown<br>Voltage | Trigger<br>Voltage (Vt <sub>1</sub> ) | $ \begin{tabular}{ll} Holding \\ Voltage (V_h) \\ \end{tabular}$ | It <sub>2</sub> Level | НВМ      |

|---------------|----------------------|---------------------------------------|------------------------------------------------------------------|-----------------------|----------|

| S-pn-ref-3.8  | 73 V                 | 78 V                                  | none                                                             | 200 mA                | < 0.5 kV |

| S-pn-3.8      | 74 V                 | 93 V                                  | none                                                             | 505 mA                | 1 kV     |

| S-pn-ref-5.8  | 74 V                 | 79 V                                  | 14.5 V                                                           | 1.8 A                 | 2 kV     |

| S-pn-5.8      | 74 V                 | 101 V                                 | none                                                             | 556 mA                | 1.5 kV   |

| LDMOS-3.8     | 75 V                 | 86 V                                  | none                                                             | 378 mA                | < 0.5 kV |

| D-pn-kmin-3.8 | 75 V                 | 86 VES                                | none                                                             | 460 mA                | 0.5 kV   |

| D-pn-k5-3.8   | 75 V                 | 86 V                                  | none                                                             | 507 mA                | 1 kV     |

| LDMOS-5.8     | 75 V                 | 87 V                                  | none                                                             | 480 mA                | 0.5 kV   |

| D-pn-kmin-5.8 | 75 V                 | 87 V                                  | none                                                             | 430 mA                | 1 kV     |

| D-pn-k5-5.8   | 75 V                 | 87 V                                  | 22.7 V                                                           | 1.9 A                 | 2.5 kV   |

# **3.4.2Summary**

The test devices for study of self-protected HV MOSFET have been investigated in a 60-V BCD process. One of the conventional methods to enhance the ESD robustness of stand-alone LDMOS is to increase the device's total width. But in this 60 V process, even though the total width increases to 1120µm, the HBM level of

nLDMOS is still only 0.5kV, which is far away from the specification (2kV). According to the measurement results, increasing the total width is not an efficient way to improve the ESD performance. Non-fully isolate NBL can have a higher trigger voltage which may have better SOA and more weakly snapback. If the device successfully snapback, changing the layout style of the NBL may modify the trigger point to meet the application. In this process, the nLDMOS cannot get into the snapback region by changing the layout style of NBL. Changing the parameter of STI space and drain contacts to STI region can only let the device bear more heat. Those devices with larger S and d may have the unrecoverable thermal damaged in the higher TLP step. However, only changing the parameter of STI space and drain contacts to STI region still cannot trigger the parasitic junction. Increasing the source active region may help the parasitic device turning on. The larger space between source contacts to the polygatewould decrease the trigger voltage. Adding additionalp+ and n+ layersin source side would let the parasitic SCR become difficult to be triggered or even unable to snapback. This concept would be discussed in the next chapter.

Many previous works havedone some engineering in drain for improve ESD robustness. The new proposed structure (D-pn-k5-5.8) is based on the embedded SCR in nLDMOSwith large parameter S and d. This device can get into its snapback region successfully. Hence, this device not only increases its It<sub>2</sub>level to more than 2A but also improves the HBM levelto over 2.5kV, which can meet the typical ESDspecification of commercial IC products. Besides, this structure (D-pn-k5-5.8) keeps the same electrical safeoperation area due to the breakdown voltage unchanged. The new proposed LDMOS-SCR structure, which is namedD-pn-k5-5.8, will be theuseful self-protection solution against ESD events inhigh-voltage applications.

# **Chapter 4**

# **Modification for LVSCR and HVSCR Structure**

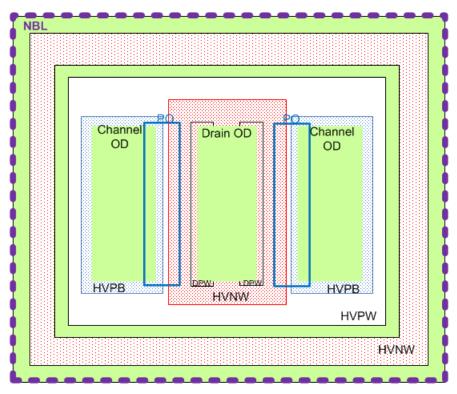

### 4.1Embedded SCR structure in 60-V 0.25 µm BCD Process

As mentioned in Chapter 3, nLDMOSdid nothave enough self-protected abilityto againstESD stresses. Therefore, an additional ESD protection designisneeded in HV applications. To simplify the HV device and remove the gate oxide damage issue, many different SCR structures are studied in this chapter. During the ESD condition, the leakage current of SCR flows deeper to prevent the current crowed effect. So it becomes one of the popular ESD protection devices in HV process.

This work not only uses the concept of layers investigation and stretching the layout parameters but also combines the new proposed technique by adding additional n+ and p+ layers and Schottky emitter method to increase the holding voltage of SCR. Those ESD protection devices have been proposed in a 0.25-µm 60-V BCD process. The detail of those devices structures and ESD performances will be introduced in the following.

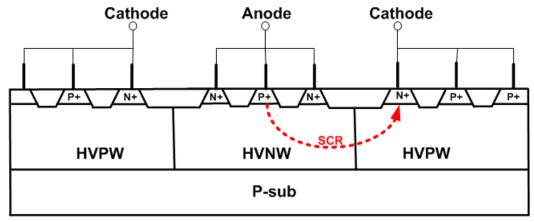

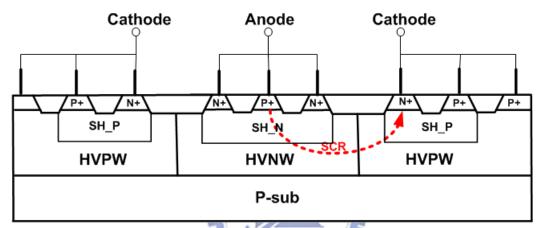

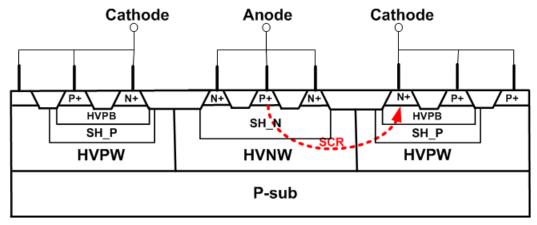

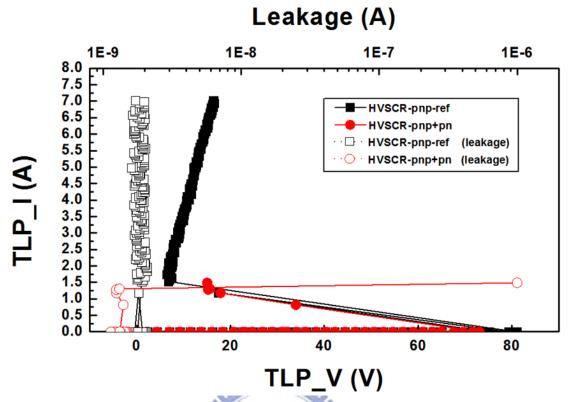

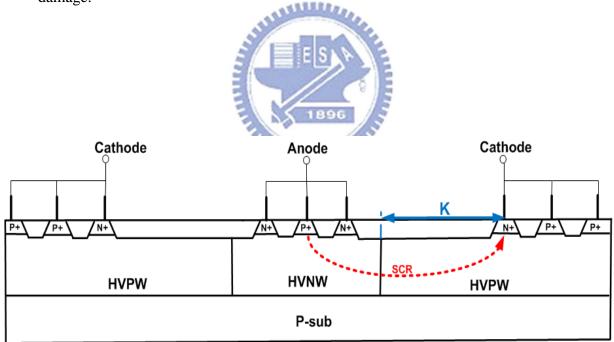

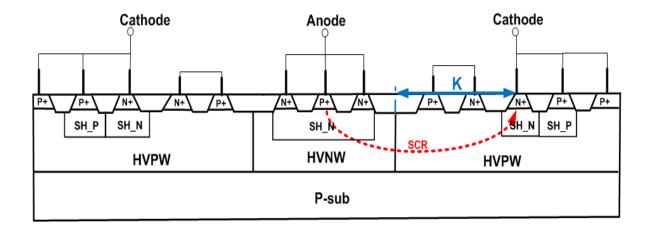

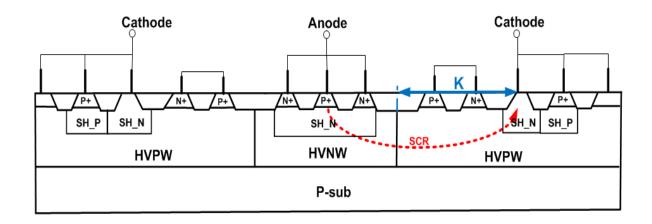

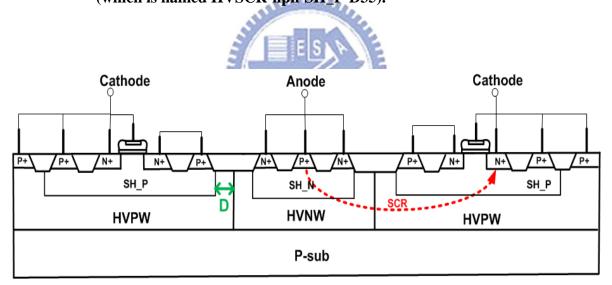

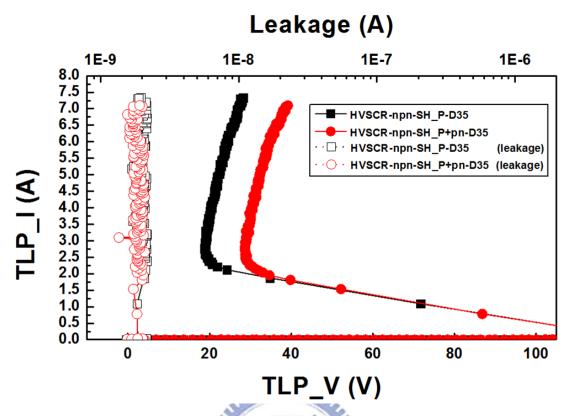

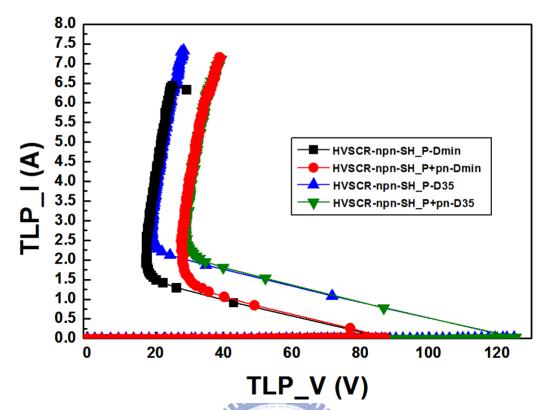

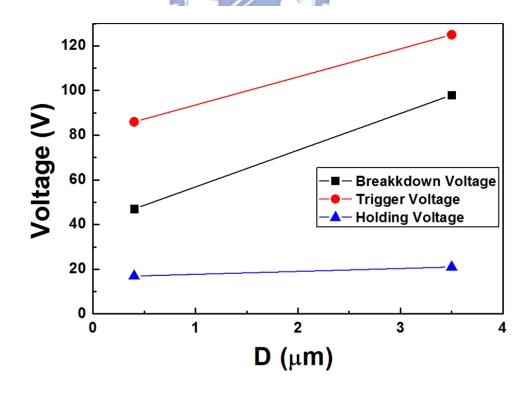

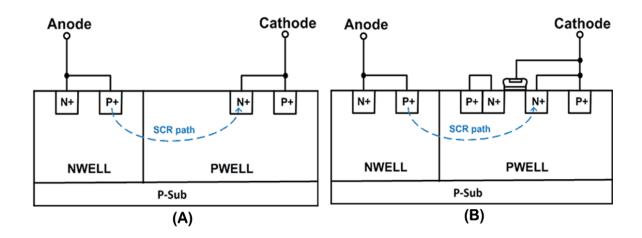

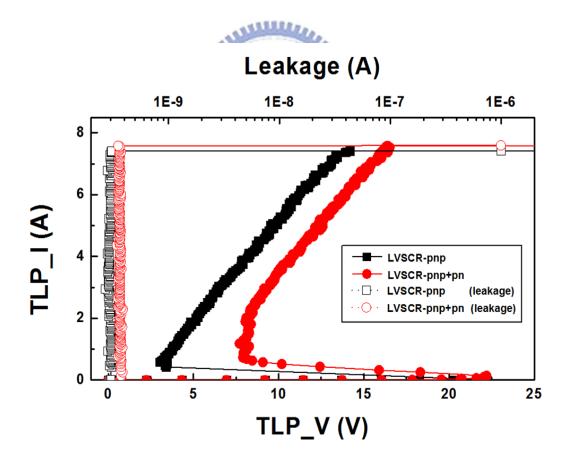

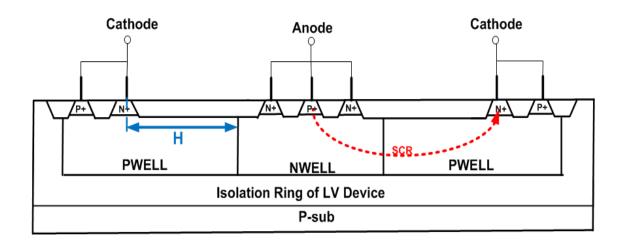

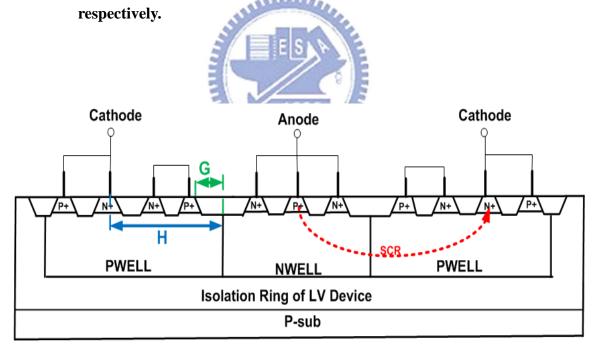

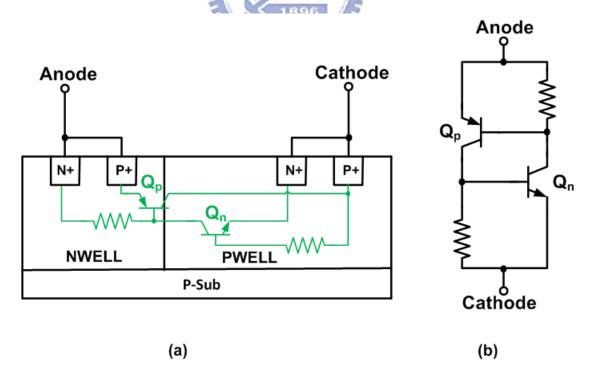

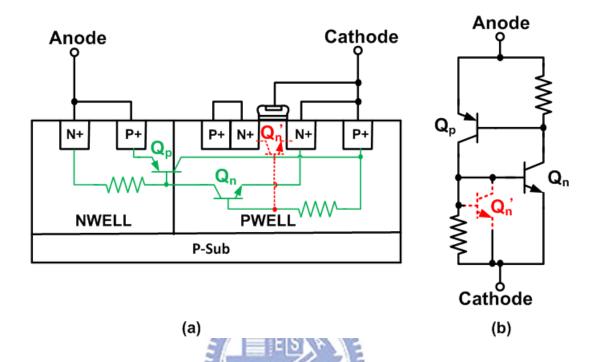

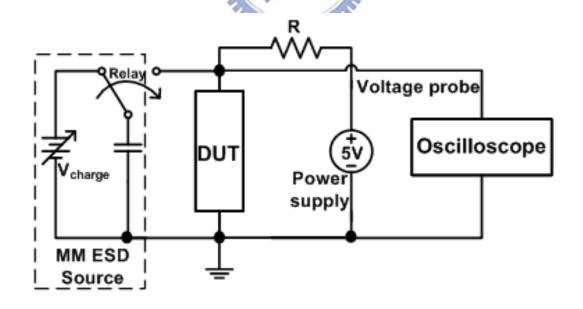

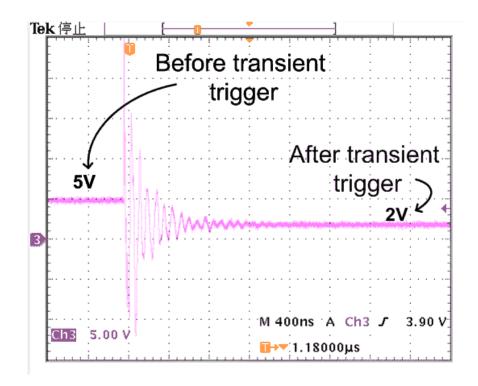

### 4.1.1 Investigation for layer effect upon the SCR structure